집적회로

Integrated circuit집적회로 또는 모노리식 집적회로(IC, 칩 또는 마이크로칩이라고도 함)는 반도체 재료(일반적으로 실리콘)의 작은 편평한 조각(또는 "칩") 위에 있는 전자 회로 세트입니다.다수의 작은 MOSFET(금속 산화물 반도체 전계효과 트랜지스터)가 작은 칩에 통합되어 있습니다.그 결과 회로는 개별 전자 부품으로 구성된 회로보다 크기가 작고 속도가 빠르며 비용이 적게 듭니다.IC의 대량 생산 능력, 신뢰성 및 집적회로 설계에 대한 빌딩 블록 접근 방식은 이산 트랜지스터를 사용한 설계 대신 표준화된 IC를 신속하게 채택할 수 있도록 보장했습니다.IC는 현재 거의 모든 전자 기기에 사용되고 있으며 전자제품의 세계에 혁명을 가져왔다.컴퓨터, 휴대전화 및 기타 가전제품은 현대 사회의 구조에서 분리할 수 없는 부분이 되었으며, 현대 컴퓨터 프로세서와 마이크로 컨트롤러와 같은 IC의 작은 크기와 저렴한 비용으로 가능해졌다.

금속산화물실리콘(MOS) 반도체 소자 제작의 기술적 진보로 대규모 집적화가 실현되었습니다.1960년대 이후 칩의 크기, 속도 및 용량은 같은 크기의 칩에 점점 더 많은 MOS 트랜지스터를 장착하는 기술적 진보에 의해 크게 발전했습니다. 현대 칩은 사람의 손톱만한 면적에 수십억 개의 MOS 트랜지스터를 가지고 있을 수 있습니다.이러한 발전은 무어의 법칙에 따라 오늘날의 컴퓨터 칩은 1970년대 초반의 컴퓨터 칩보다 수백만 배, 수천 배 더 빠른 용량을 가지고 있습니다.

IC에는 개별 회로에 비해 비용과 성능이라는 두 가지 주요 이점이 있습니다.칩은 한 번에 하나의 트랜지스터가 아닌 포토 리소그래피로 하나의 유닛으로 인쇄되기 때문에 비용이 저렴합니다.게다가 패키지화된 IC는 이산 회로보다 훨씬 적은 재료를 사용합니다.IC의 부품은 크기가 작고 근접하기 때문에 빠르게 전환되고 상대적으로 적은 전력을 소비하기 때문에 성능이 높습니다.IC의 주요 단점은 설계 및 필요한 포토마스크 제작 비용이 높다는 것입니다.이 높은 초기 비용은 IC가 대량 생산이 예상되는 경우에만 상업적으로 실행 가능하다는 것을 의미합니다.

용어.

집적회로는 다음과 [1]같이 정의됩니다.

회로 소자의 전부 또는 일부가 분리할 수 없고 전기적으로 상호 접속되어 건설 및 상업상 분리할 수 없는 것으로 간주되는 회로.

이 정의를 충족하는 회로는 박막 트랜지스터, 박막 기술 또는 하이브리드 집적회로 등 다양한 기술을 사용하여 구성할 수 있습니다.그러나 일반적으로 집적회로는 원래 단일 실리콘 [2][3]조각 위에 조립된 일체형 집적회로라고 알려진 단일 피스 회로 구조를 지칭하게 되었습니다.

역사

(현대 IC와 같은) 하나의 장치에 여러 구성 요소를 결합하려는 초기 시도는 1920년대의 Loewe 3NF 진공 튜브였습니다.IC와 달리, 독일에서와 같이, 라디오 수신기는 라디오 수신기의 튜브 홀더 수에 따라 세금이 부과되는 것을 목적으로 설계되었다.그것은 라디오 수신기가 하나의 튜브 홀더를 가질 수 있게 했다.

집적회로의 초기 개념은 1949년 독일 엔지니어 베르너[4] 야코비(시멘스 AG)[5]가 3단 증폭기 배열로 공통 기판 위에 5개의 트랜지스터를 보여주는 집적회로 형태의 반도체 증폭기[6] 특허를 출원한 때로 거슬러 올라간다.Jacobi는 작고 저렴한 보청기를 특허의 전형적인 산업적 응용 분야로 공개했다.그의 특허의 즉각적인 상업적 사용은 보고되지 않았다.

이 개념의 또 다른 초기 제안자는 영국 국방부의 왕립 레이더 기구에 근무하는 레이더 과학자 제프리 더머(1909–2002)였다.더머는 1952년 [7]5월 7일 워싱턴 D.C.에서 열린 품질 전자 부품의 진보에 관한 심포지엄에서 이 아이디어를 대중에게 발표했습니다.그는 자신의 생각을 널리 알리기 위해 많은 심포지엄을 공개적으로 열었고 1956년에 그러한 회로를 건설하려고 시도했지만 실패했다.1953년에서 1957년 사이에 시드니 달링턴과 야수오 타루이(Yasuo Tarui)는 여러 트랜지스터가 공통 활성 영역을 공유할 수 있는 유사한 칩 설계를 제안했지만, 서로 [4]분리할 전기적 절연은 없었습니다.

일체형 집적회로 칩은 Jean Hoerni에 의한 평면 공정의 발명과 Kurt Lehovec에 의한 p-n 접합 단리에 의해 가능해졌다.회니의 발명품은 모하메드 M. 위에 지어졌다. 아탈라의 표면 부동화 연구, 풀러와 디첸버거의 실리콘으로의 붕소 및 인 불순물 확산 연구, 칼 프로쉬와 링컨 데릭의 표면 보호 연구, 치 탕 사의 [8]산화물 확산 연구.

제1집적회로

IC의 선구적인 아이디어는 작은 세라믹 기판(이른바 마이크로모듈)[9]을 만드는 것이었습니다. 각 기판에는 하나의 소형화된 부품이 들어 있습니다.그런 다음 구성요소를 2차원 또는 3차원 콤팩트 그리드에 통합하고 배선할 수 있습니다.1957년에 매우 유망해 보였던 이 아이디어는 잭 킬비에[9] 의해 미군에 제안되었고 1951년의 팅커토이 [9][10][11]프로젝트와 유사하게 단명한 마이크로모듈 프로그램으로 이어졌다.그러나 프로젝트가 탄력을 받으면서 킬비는 새롭고 혁신적인 디자인인 IC를 생각해냈다.

텍사스 인스트루먼트에 의해 새롭게 고용된 킬비는 1958년 7월에 집적회로에 대한 그의 초기 아이디어를 기록했고,[12] 1958년 9월 12일에 집적회로의 첫 번째 작동 예를 성공적으로 시연했다.1959년 [13]2월 6일 특허 출원서에서 킬비는 자신의 새로운 장치를 "전자 회로의 모든 부품이 완전히 [14]집적된 반도체 재료의 집합체"라고 표현했습니다.새로운 발명의 첫 고객은 미국 [15]공군이었다.킬비는 집적회로를 [16]발명한 공로로 2000년 노벨 물리학상을 수상했다.그러나 킬비의 발명은 모노리식 집적회로([17]Monolithic IC) 칩이 아닌 하이브리드 집적회로(Hybrid IC)였다.킬비의 IC는 외부 배선 연결부가 있어 [18]양산에 어려움을 겪었다.

킬비로부터 반년 후, 페어차일드 세미컨덕터의 로버트 노이스가 최초의 진정한 모노리식 IC칩을 [19][18]발명했습니다.이것은 Kilby의 구현보다 더 실용적인 새로운 종류의 집적회로였습니다.노이스의 디자인은 실리콘으로 만들어졌고 킬비의 칩은 게르마늄으로 만들어졌다.노이스의 모노리식 IC는 실리콘 칩 위에 모든 부품을 올려놓고 [18]구리선으로 연결했다.노이스의 모노리식 IC는 1959년 초 그의 동료인 Jean Hoerni에 의해 개발된 평면 공정을 사용하여 제작되었습니다.현대의 IC칩은 킬비의 하이브리드 [17]IC가 아닌 노이스의 모노리식 [19][18]IC를 기반으로 한다.

NASA의 아폴로 프로그램은 1961년부터 [20]1965년까지 집적회로의 단일 소비 중 가장 큰 규모였다.

TTL 집적회로

트랜지스터-트랜지스터 로직(TTL)은 James L.에 의해 개발되었습니다. 1960년대 초반 TRW Inc.의 Buie.TTL은 1970년대부터 1980년대 [21]초반까지 지배적인 집적회로 기술이 되었습니다.

수십 개의 TTL 집적회로는 미니컴퓨터와 메인프레임 컴퓨터의 프로세서를 위한 표준 구조 방식이었다.IBM 360 메인프레임, PDP-11 미니컴퓨터 및 데스크톱 Datapoint 2200과 같은 컴퓨터는 TTL 또는 훨씬 더 빠른 ECL(Emitter-Coupled Logic)의 양극성 [22]집적회로에서 구축되었습니다.

MOS 집적회로

거의 모든 최신 IC 칩은 MOSFET(금속 산화물-실리콘 전계효과 트랜지스터)[23]로 제조된 금속 산화물-반도체(MOS) 집적회로입니다.MOSFET(MOS 트랜지스터라고도 함)는 모하메드 M에 의해 발명되었습니다. 1959년 [24]Bell Labs의 Atalla와 Dawon Kahng은 고밀도 [25]집적회로를 구축할 수 있게 되었습니다.칩 상의 트랜지스터의 p-n 접합 단리에 많은 단계가 필요했던 바이폴라 트랜지스터와 달리, MOSFET는 그러한 단계가 필요하지 않았지만 서로 [26]쉽게 분리될 수 있었다.집적회로의 장점은 1961년 [27]Dawon Khang에 의해 지적되었다.IEEE 이정표 목록에는 1958년 [28]Kilby의 첫 집적회로, 1959년 Hoerni의 평면 프로세스와 Noyce의 평면 IC, 1959년 [29]Atalla와 Kahng의 MOSFET가 포함되어 있습니다.

최초의 실험용 MOS IC는 1962년 [30]RCA에서 프레드 하이만과 스티븐 호프스타인에 의해 제조된 16 트랜지스터 칩이었다.제너럴마이크로일렉트로닉스(General Microelectronics)는 [31]1964년 로버트 [30]노먼(Robert Norman)이 개발한 120 트랜지스터 시프트 레지스터인 최초의 상업용 MOS 집적회로를 선보였다.1964년까지 MOS 칩은 바이폴라 칩보다 높은 트랜지스터 밀도와 낮은 제조 비용에 도달했습니다.MOS 칩은 무어의 법칙에 의해 예측된 속도로 복잡성이 더욱 증가하여 1960년대 [32]후반까지 단일 MOS 칩에 수백 개의 트랜지스터와 대규모 집적(LSI)이 이루어졌습니다.

1967년 [33]Bell Labs에서 Robert Kerwin, Donald Klein 및 John Sarace가 자체 정렬 게이트(Silicon-Gate) MOSFET를 개발한 데 이어 1968년 [34]Federico Faggin에 의해 Fairchild Semiconductor에서 모든 현대 CMOS 집적 회로의 기초가 되는 최초의 실리콘 게이트 MOS IC 기술이 개발되었습니다.엔지니어들이 하나의 MOS LSI 칩에 완전한 컴퓨터 프로세서를 담을 수 있다는 것을 인식하기 시작하면서, 컴퓨팅에 MOS LSI 칩을 적용한 것이 최초의 마이크로프로세서의 기초가 되었습니다.이것은 1970년대 [32]초 마이크로프로세서와 마이크로컨트롤러의 발명으로 이어졌다.1970년대 초 MOS 집적회로 기술은 단일 [35]칩에 10,000개 이상의 트랜지스터를 포함하는 매우 큰 규모의 집적(VLSI)을 가능하게 했습니다.

처음에 MOS 기반의 컴퓨터는 항공우주나 포켓 계산기 같은 고밀도가 필요할 때만 의미가 있었습니다.1970년 Datapoint 2200과 같은 TTL로 완전히 구축된 컴퓨터는 1980년대 [22]초반까지 1972년 Intel 8008과 같은 싱글 칩 MOS 마이크로프로세서보다 훨씬 빠르고 강력했습니다.

IC 기술의 진보, 주로 더 작은 특징과 더 큰 칩으로 집적회로의 MOS 트랜지스터 수가 2년마다 두 배씩 증가했는데, 이러한 경향은 무어의 법칙으로 알려져 있습니다.무어는 원래 매년 두 배가 될 것이라고 말했지만,[36] 1975년에 2년마다 청구권을 변경했다.이러한 용량 증가는 비용 절감과 기능 향상에 사용되었습니다.일반적으로 피처 사이즈가 작아지면 IC 동작의 거의 모든 측면이 개선됩니다.Dennard 스케일링(MOSFET 스케일링)[37]에 의해 정의된 관계를 통해 트랜지스터당 비용과 트랜지스터당 스위칭 전력 소비는 감소하지만 메모리 용량과 속도는 증가합니다.최종 사용자에게는 속도, 용량 및 전력 소비의 이점이 명백하기 때문에 제조업체 간에는 보다 미세한 구조를 사용하기 위한 경쟁이 치열합니다.수년간 트랜지스터 크기는 1970년대 초 수십 미크론에서 2017년 10[38] 나노미터로 감소했으며, 단위 면적당 트랜지스터 크기는 이에 상응하는 수백만 배 증가했습니다.2016년 기준, 일반적인 칩 면적은 수 평방 밀리미터에서 약 6002 밀리미터이며,[39] mm당 최대2 2,500만 개의 트랜지스터가 있습니다.

기능 사이즈의 감소와 관련 분야에서의 필요한 진전은 수년간 국제반도체기술로드맵(ITRS)에 의해 예측되고 있습니다.최종 ITRS는 2016년에 발표되었으며, 국제 기기 [40]및 시스템 로드맵으로 대체되고 있습니다.

처음에 IC는 완전히 전자 기기였다.IC의 성공은 작은 크기와 낮은 비용이라는 동일한 이점을 얻기 위해 다른 기술들의 통합으로 이어졌다.이러한 기술에는 기계 장치, 광학 장치, 센서가 포함됩니다.

- 전하 결합 소자와 밀접하게 관련된 액티브 픽셀 센서는 빛에 민감한 칩입니다.과학, 의료 및 소비자 응용 분야에서 사진 필름을 크게 대체했습니다.이러한 장치 중 수십억 개가 현재 휴대폰, 태블릿 및 디지털 카메라와 같은 애플리케이션을 위해 매년 생산되고 있습니다.IC의 이 하위 분야는 [41]2009년에 노벨상을 수상했습니다.

- 전기로 구동되는 매우 작은 기계 장치들은 마이크로 전기 기계 시스템으로 알려진 기술인 칩에 통합될 수 있습니다.이 장치는 1980년대 후반에[42] 개발되었으며 다양한 상업 및 군사 용도로 사용됩니다.예를 들어 DLP 프로젝터, 잉크젯 프린터, 자동차 에어백을 전개하는 데 사용되는 가속도계 및 MEMS 자이로스코프 등이 있습니다.

- 2000년대 초부터 실리콘 칩으로의 광학 기능(광학 컴퓨팅)의 통합은 학술 연구 및 업계 양면에서 활발하게 추진되어 왔으며, 그 결과 광학 디바이스(변조기, 검출기, 라우팅)와 CMOS 기반 전자장치를 결합한 실리콘 기반 통합 광 트랜시버가 성공적으로 상용화되었습니다.cs.[43] 광자를 사용하는 포토닉 집적회로도 광자로 알려진 물리학의 신흥 분야를 이용하여 개발되고 있다.

- 집적회로 또한 의료용 임플란트 또는 기타 생체 전자 [44]장치의 센서 적용을 위해 개발되고 있다.노출된 반도체 [45]재료의 부식이나 생분해 방지를 위해 이러한 생물 발생 환경에서 특수 밀봉 기술을 적용해야 한다.

2018년 현재[update] 트랜지스터의 대부분은 실리콘 칩의 한쪽 면에 평면 2차원 평면 공정으로 단층으로 제작된 MOSFET입니다.연구자들은 다음과 같은 여러 가지 유망한 대안들의 프로토타입을 제작했습니다.

- 3차원 집적회로(3DIC)를 만들기 위해 트랜지스터의 여러 층을 쌓는 다양한 접근법, 예를 들어 스루실리콘 비아, 모노리식 3D,[46] 적층 와이어 [47]본딩 및 기타 방법론.

- 그래핀 트랜지스터, 몰리브덴 트랜지스터, 카본 나노튜브 전계효과 트랜지스터, 질화 갈륨 트랜지스터, 트랜지스터 유사 나노와이어 전자 소자, 유기 전계효과 트랜지스터 등 기타 재료로 제조된 트랜지스터

- 실리콘으로 [48][49]된 작은 구체의 표면 전체에 트랜지스터를 제작하는 것.

- 일반적으로 플렉시블 디스플레이 또는 기타 플렉시블 전자기기용 "하이브리드 트랜지스터"를 만들기 위해 기판을 개조하여 롤어웨이 컴퓨터를 만들 수 있습니다.

소형 트랜지스터의 제조가 점점 어려워짐에 따라 기업들은 멀티칩 모듈, 3차원 집적회로, 패키지 온 패키지, 고대역폭 메모리 및 다이 스태킹 기능이 있는 스루실리콘 비어를 사용하여 트랜지스터의 크기를 줄이지 않고도 성능을 높이고 크기를 줄이고 있습니다.이러한 기술은 집합적으로 고급 패키징으로 [50]알려져 있습니다.고급 패키징은 주로 2.5D 패키징과 3D 패키징으로 구분됩니다. 2.5D는 멀티칩 모듈 등의 접근방식을 기술하고, 3D는 패키지 상의 패키지, 고대역폭 메모리 등 여러 방법으로 다이를 적층하는 접근방식을 기술합니다.모든 접근방식은 단일 [51][52][53][54][55]패키지에 2개 이상의 다이와 관련되어 있습니다.또는 3D NAND와 같은 접근 방식은 단일 다이에 여러 층을 쌓습니다.

설계.

복잡한 집적회로를 설계하고 개발하는 데 드는 비용은 보통 수천만 [56][57]달러로 상당히 높습니다.따라서 생산량이 많은 집적회로 제품을 생산하는 것은 경제적 의미가 있기 때문에 Non-Recurring Engineering(NRE; 비재귀 엔지니어링) 비용은 일반적으로 수백만 개의 생산 유닛에 분산됩니다.

현대의 반도체 칩은 수십억 개의 부품을 가지고 있으며 손으로 설계하기에는 너무 복잡하다.디자이너를 돕기 위한 소프트웨어 도구는 필수적입니다.EDA([58]Electronic Design Automation)는 집적회로를 포함한 전자 시스템을 설계하기 위한 소프트웨어 도구의 카테고리입니다.이 툴은 설계 흐름에서 함께 작동하며 엔지니어는 반도체 칩 전체를 설계하고 분석합니다.

종류들

집적회로는 아날로그 신호[60],[59] 디지털 신호 [61]및 혼합 신호로 크게 분류할 수 있으며, 동일한 IC 상의 아날로그 신호와 디지털 신호로 구성됩니다.

디지털 집적회로에는 수십억 개의 논리 게이트, 플립 플랍, 멀티플렉서 및 기타 회로를 몇 평방 밀리미터 안에 포함할[39] 수 있습니다.이러한 회선의 사이즈가 작기 때문에, 보드 레벨의 집적화에 비해, 고속으로 전력 소모를 억제해, 제조 코스트를 삭감할 수 있습니다.이러한 디지털 IC(일반적으로 마이크로프로세서, DSP 및 마이크로 컨트롤러)는 "1" 및 "제로" 신호를 처리하기 위해 부울 대수를 사용합니다.

가장 진보된 집적회로로는 개인용 컴퓨터, 휴대전화, 전자레인지 등에 사용되는 마이크로프로세서 또는 "코어"가 있습니다.여러 개의 코어가 하나의 IC 또는 칩에 함께 통합될 수 있습니다.디지털 메모리 칩과 애플리케이션 고유의 집적회로(ASIC)는 다른 집적회로 패밀리의 예입니다.

1980년대에 프로그램 가능한 논리 소자가 개발되었습니다.이러한 디바이스에는 논리적인 기능과 접속성을 집적회로 제조원에 의해 고정되는 것이 아니라 사용자가 프로그래밍할 수 있는 회로가 포함되어 있습니다.이를 통해 로직 게이트, 가산기, 레지스터 등 다양한 LSI 타입의 기능을 하도록 칩을 프로그래밍할 수 있습니다.프로그래머빌리티에는 다양한 형태가 있습니다.한 번만 프로그래밍할 수 있는 장치, UV를 사용하여 지웠다가 다시 프로그래밍할 수 있는 장치, 플래시 메모리를 사용하여 (재) 프로그래밍할 수 있는 장치, 작동 중에도 언제든지 프로그래밍할 수 있는 Field-Programmable Gate Array(FPGA; 필드 프로그래밍 가능 게이트 어레이) 등입니다.현재 FPGA는 (2016년 기준) 수백만 개의 게이트를 구현할 수 있으며 최대 1GHz의 [62]주파수에서 작동할 수 있다.

센서, 전원관리회로, 연산증폭기(op-amp) 등의 아날로그 IC는 연속신호를 처리하고 증폭, 액티브필터링, 복조, 혼합 등의 아날로그 기능을 수행합니다.

IC는 아날로그와 디지털 회로를 칩에 결합해 아날로그-디지털 변환기, 디지털-아날로그 변환기 등의 기능을 만들 수 있다.이러한 혼합 신호 회선은 크기가 작아지고 비용이 절감되지만 신호 간섭을 고려해야 합니다.1990년대 후반 이전에는 마이크로프로세서와 같은 저비용 CMOS 프로세스로 무선을 제작할 수 없었습니다.그러나 1998년부터 RF CMOS 프로세스를 사용하여 무선 칩이 개발되었습니다.예를 들면, 인텔의 DECT 무선 전화나, Atheros와 그 외의 [63]기업이 개발한802.11 (Wi-Fi) 칩이 있습니다.

현대의 전자 부품 디스트리뷰터에서는 집적회로를 하위 분류하는 경우가 많습니다.

- 디지털 IC는 논리 IC(마이크로프로세서나 마이크로컨트롤러 등), 메모리 칩(MOS 메모리나 플로팅 게이트 메모리 등), 인터페이스 IC(레벨 시프터, 시리얼라이저/디시리얼라이저 등), 전원 관리 IC 및 프로그래머블 디바이스로 분류됩니다.

- 아날로그 IC는 선형 집적 회로와 RF 회로(무선 주파수 회로)로 분류됩니다.

- 혼합 신호 집적회로는 데이터 수집 IC(A/D 변환기, D/A 변환기, 디지털 전위차계 포함), 클럭/타이밍 IC, 스위치드 캐패시터(SC) 회로 및 RF CMOS 회로로 분류됩니다.

- 3차원 집적회로(3D IC)는 TSV(Through-Silicon via) IC와 Cu-Cu 연결 IC로 분류됩니다.

제조업

제조

화학 원소의 주기율표의 반도체는 고체 진공관에 가장 적합한 물질로 확인되었다.산화동부터 게르마늄, 실리콘 순으로 1940년대와 1950년대에 체계적으로 연구되었다.오늘날, 갈륨 비소와 같은 주기율표의 III-V 화합물은 LED, 레이저, 태양전지 및 최고속 집적회로와 같은 특수한 용도로 사용되지만, 단결정 실리콘은 IC에 사용되는 주요 기판입니다.반도체 재료의 결정 구조에 최소한의 결함이 있는 결정을 만드는 방법을 완성하는 데 수십 년이 걸렸다.

반도체 IC는 사진 석판, 증착(화학 증기 증착 등) 및 식각의 세 가지 주요 공정 단계를 포함하는 평면 공정으로 제작됩니다.주요 공정 단계는 도핑 및 세척으로 보완됩니다.최신 또는 고성능 IC에서는 22nm 노드(Intel) 또는 16/14nm [64]노드부터 시작하여 평면형 트랜지스터 대신 멀티게이트 FinFET 또는 GAFET 트랜지스터를 사용할 수 있습니다.

단결정 실리콘 웨이퍼는 대부분의 용도에 사용됩니다(또는 특수 용도에는 갈륨 비소와 같은 다른 반도체가 사용됩니다).웨이퍼가 완전히 실리콘일 필요는 없습니다.포토 리소그래피는 도핑할 기판의 다양한 영역을 표시하거나 폴리실리콘, 절연체 또는 금속(일반적으로 알루미늄 또는 구리) 트랙을 부착하는 데 사용됩니다.도판트는 반도체의 전자 특성을 변조하기 위해 의도적으로 반도체에 도입된 불순물이다.도핑은 반도체 재료에 도판트를 첨가하는 과정이다.

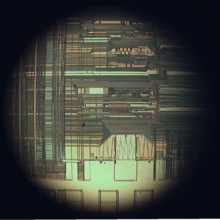

- 집적회로는 여러 겹의 층으로 구성되어 있으며, 각 층은 포토 리소그래피로 정의되어 있으며, 보통 다른 색상으로 표시됩니다.어떤 층은 다양한 도판트가 기질에 확산되는 위치를 표시하고(확산층이라고 함), 어떤 층은 추가 이온이 주입되는 위치(임플란트층), 어떤 층은 도체(도프 폴리실리콘 또는 금속층)를 정의하며, 어떤 층은 도체층(또는 접촉층) 사이의 연결을 정의합니다.모든 컴포넌트는 이러한 레이어의 특정 조합으로 구성됩니다.

- 자기정렬 CMOS 프로세스에서는 게이트층([65]: p.1 (see Fig. 1.1) 폴리실리콘 또는 금속)이 확산층을 교차하는 위치에 트랜지스터가 형성된다.

- 전통적인 전기 캐패시터의 병렬 도체 판과 매우 유사한 형태의 용량성 구조는 "판"의 면적에 따라 형성되며, 판 사이에 절연 재료가 있습니다.다양한 크기의 콘덴서는 IC에서 흔히 볼 수 있습니다.

- 대부분의 논리 회로에는 저항이 필요하지 않지만 길이가 다른 사행 스트라이프가 온칩 저항을 형성하기 위해 사용되는 경우가 있습니다.저항 구조물의 폭에 대한 길이의 비율과 시트 저항률이 결합되어 저항을 결정합니다.

- 드물게 유도 구조는 작은 온칩 코일로 제작되거나 회전자에 의해 시뮬레이션될 수 있습니다.

CMOS 디바이스는 로직스테이트간의 전이시에만 전류를 소비하기 때문에 CMOS 디바이스는 바이폴라 접합 트랜지스터 디바이스보다 훨씬 적은 전류를 소비합니다.

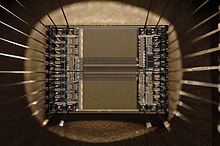

랜덤 액세스 메모리는 집적회로의 가장 일반적인 타입입니다.따라서 고밀도 디바이스는 메모리입니다.단, 마이크로프로세서에서도 칩에 메모리가 탑재됩니다.(첫 번째 이미지 하단에 있는 일반 어레이 구조를 참조해 주세요.)[which?]수십 년 동안 축소되어 온 폭과 함께 구조가 복잡하지만, 레이어는 장치 폭보다 훨씬 얇은 상태로 유지됩니다.가시 스펙트럼의 광파는 특징에 비해 너무 크기 때문에 재료의 층을 "노출"하는 데 사용할 수 없지만 재료 층은 사진 공정과 매우 유사하게 제작된다.따라서 고주파(일반적으로 자외선)의 광자는 각 층의 패턴을 만드는 데 사용됩니다.각 기능은 매우 작기 때문에 제조 프로세스를 디버깅하는 프로세스 엔지니어에게 전자 현미경은 필수 도구입니다.

각 장치는 자동 테스트 장비(ATE)를 사용하여 포장하기 전에 웨이퍼 테스트 또는 웨이퍼 프로빙으로 알려진 프로세스에서 테스트됩니다.그런 다음 웨이퍼를 직사각형 블록으로 절단하고, 각 블록을 다이라고 합니다.그런 다음 각 양호한 다이스(복수 다이스, 다이스 또는 다이스)를 알루미늄(또는 금) 본드 와이어를 사용하여 패키지에 연결합니다. 이 와이어는 보통 다이스 가장자리 주변에 있는 패드에 열경화적으로[66] 접합됩니다.서모소닉 본딩은 A에 의해 처음 도입되었습니다.쿠쿨라는 외부와의 중요한 전기 접속을 형성하기 위한 신뢰할 수 있는 수단을 제공했습니다.포장 후 장치는 웨이퍼 프로빙 시 사용된 것과 같거나 유사한 ATE에 대한 최종 테스트를 거칩니다.산업용 CT 스캔도 사용할 수 있습니다.테스트 비용은 저비용 제품 제조 비용의 25% 이상을 차지할 수 있지만, 저수익률, 대형 또는 고비용 디바이스에서는 무시할 수 있습니다.

2016년 현재[update] 제조 시설([67]일반적으로 반도체 팹으로 알려져 있음)을 건설하는 데 80억 달러 이상이 소요될 수 있습니다.신제품의 복잡성이 증가하기 때문에 제조 설비의 비용은 시간이 지남에 따라 상승합니다.이것은 Rock의 법칙이라고 불립니다.이러한 시설의 특징은 다음과 같습니다.

- 최대 직경이 300mm인 웨이퍼(일반 디너 플레이트보다 넓음)

- 2016년 기준[update], 14 nm 트랜지스터.[68][신규 갱신]

- 구리 배선이 상호 접속용 알루미늄을 대체하는 구리 인터커넥트.

- 저전압 유전체 절연체

- 실리콘 온 인슐레이터(SOI).

- IBM이 SSDOI(Strained silicon on insoluter)로 알려진 공정에서 사용하는 변형 실리콘입니다.

- 트라이게이트 트랜지스터 등의 멀티게이트 장치.

IC는 통합 장치 제조업체(IDM)에 의해 자체 제조되거나 주조 공장 모델을 사용하여 제조될 수 있습니다.IDM은 수직적으로 통합된 기업(Intel이나 Samsung 등)으로, 독자적인 IC를 설계, 제조, 판매하는 기업이며, 다른 기업(Fabless 기업)에 설계 및/또는 제조(Foundry) 서비스를 제공할 수 있습니다.주조 공장 모델에서는 (Nvidia와 같은) 팹리스 업체가 IC를 설계 및 판매하고 모든 제조를 TSMC와 같은 순수 재생 주조 공장에 아웃소싱합니다. 이러한 주조 공장은 IC 설계 서비스를 제공할 수 있습니다.

패키징

최초의 집적회로는 세라믹제 플랫팩으로 포장되어 있었으며, 신뢰성과 작은 크기 때문에 군에서 수년간 계속 사용되었습니다.상용 회로 패키징은 처음에는 세라믹으로, 나중에는 플라스틱으로 된 이중 인라인 패키지(DIP)로 빠르게 이동했습니다. 이 패키지는 일반적으로 크레졸 폼알데히드 노볼락입니다.1980년대에는 VLSI 회로의 핀 수가 DIP 패키징의 실제 제한을 초과하여 핀 그리드 어레이(PGA) 및 무연 칩 캐리어(LCC) 패키지가 되었습니다.표면 실장 패키징은 1980년대 초에 등장하여 1980년대 후반에 인기를 끌었으며, SOIC(Small-Outline Integrated Circuit) 패키지에서 볼 수 있듯이 리드와 함께 가는 리드 피치를 사용하는 것이 일반적입니다.이 패키지에는 2개의 긴 측면에서 돌출된 "걸 날개" 리드와 0.050인치의 리드 간격이 있습니다.

1990년대 후반에는 플라스틱 쿼드 플랫 팩(PQFP) 및 Thin Small-Outline Package(TSOP) 패키지가 하이 핀 카운트의 디바이스에 가장 많이 사용되었지만, PGA 패키지는 여전히 하이엔드 마이크로프로세서에 사용되고 있습니다.

볼 그리드 어레이(BGA) 패키지는 1970년대부터 존재해 왔습니다.다른 패키지 유형보다 핀 수가 훨씬 많은 플립칩 볼 그리드 어레이 패키지는 1990년대에 개발되었습니다.FCBGA 패키지에서 다이는 거꾸로 장착(플립)되며 와이어가 아닌 프린트 회로 기판과 유사한 패키지 기판을 통해 패키지 볼에 접속된다.FCBGA 패키지는 다이 주변부에 국한되지 않고 다이 전체에 걸쳐 입출력 신호 배열(영역 I/O)을 분산시킬 수 있습니다.BGA 디바이스는 전용 소켓이 필요 없다는 장점이 있지만 디바이스 장애 시 교환이 훨씬 어렵습니다.

인텔은 2004년부터 PGA에서 Land Grid Array(LGA) 및 BGA로 전환하여 2014년 모바일 플랫폼용 마지막 PGA 소켓을 출시하였습니다.2018년 현재[update] AMD는 메인스트림 데스크톱 [70]프로세서에 PGA 패키지를, 모바일 [71]프로세서에 BGA 패키지를,[72] 하이엔드 데스크톱 및 서버 마이크로프로세서에 LGA 패키지를 사용하고 있습니다.

다이를 나가는 전기 신호는 다이를 패키지에 전기적으로 연결하는 재료를 통과해야 하며, 패키지의 전도성 트레이스(경로)를 통과해야 하며, 패키지와 프린트 회로 기판의 전도성 트레이스를 연결하는 리드를 통과해야 합니다.이러한 전기 신호가 이동해야 하는 경로에 사용되는 재료와 구조는 동일한 다이의 다른 부분으로 이동하는 재료와 구조와 비교하여 매우 다른 전기적 특성을 가집니다.그 결과 신호가 손상되지 않도록 하기 위한 특별한 설계 기술이 필요하며, 다이 자체에 국한된 신호보다 훨씬 더 많은 전력을 필요로 합니다.

하나의 패키지에 여러 개의 다이(die)를 넣으면 패키지화된 시스템(system in package,MCM 약어)이 됩니다.다이스 모듈()은 세라믹으로 만들어지는 경우가 많은 작은 기판 위에 여러 개의 다이(die)를 조합하여 생성됩니다.대형 MCM과 소형 프린트 기판의 구별이 애매할 수 있습니다.

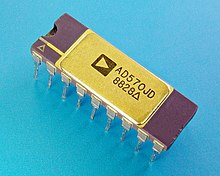

패키지화된 집적회로는 보통 식별정보를 포함할 수 있을 정도로 충분히 큽니다.제조원의 이름 또는 로고, 부품 번호, 부품 생산의 배치 번호와 시리얼 번호, 칩의 제조 시기를 식별하는 4자리 날짜 코드 등 4개의 공통 섹션이 있습니다.초소형 표면 실장 테크놀로지 부품에는 집적회로의 특성을 찾기 위해 제조원의 룩업테이블에 사용되는 번호만 기재되어 있는 경우가 많습니다.

제조일은 일반적으로 두 자리 연도 뒤에 두 자리 주 코드가 이어지는 것으로 나타나며, 코드 8341이 있는 부품이 1983년 41주차 또는 약 1983년 10월에 제조되었습니다.

지적 재산.

집적회로의 각 층을 촬영해, 얻은 사진을 기초로 제조용 포토마스크를 준비하는 것으로 카피할 수 있는 것이, 레이아웃 설계의 보호를 위한 법제도의 도입의 이유다.1984년 미국 반도체 칩 보호법은 [73]집적회로를 생산하는 데 사용되는 포토마스크에 대한 지적 재산 보호를 확립했습니다.

1989년 워싱턴 D.C.에서 열린 외교 회의에서 집적회로에 [74]관한 지적재산권 조약(워싱턴 조약 또는 IPIC 조약)이 채택되었다.이 조약은 현재 유효하지는 않지만 TRIPS [75]협정에 부분적으로 통합되었다.

IC 배치 디자인을 보호하는 국내법은 일본,[76] EC,[77] 영국, 호주, 한국 등 여러 국가에서 채택되었습니다.영국은 처음에 저작권법이 칩 지형을 완전히 보호한다는 입장을 취한 후 1988년 저작권, 디자인 및 특허법, c. 48, § 213을 제정했다.영국 레이랜드 자동차 회사 대 암스트롱 특허 회사 참조.

미국 칩업계가 인식하고 있는 영국 저작권 접근법의 부적절성에 대한 비판은 칩 권리 개발에 [78]요약되어 있습니다.

호주는 칩 [citation needed]보호의 형태로서 1989년의 회선 레이아웃법을 통과시켰습니다.한국은 반도체 [citation needed]집적회로의 레이아웃 설계에 관한 법률을 통과시켰다.

세대

단순한 집적회로의 초창기에는 이 기술의 대규모로 각 칩을 몇 개의 트랜지스터로 제한했고, 집적도가 낮다는 것은 설계 프로세스가 비교적 간단하다는 것을 의미했습니다.제조업의 수율도 오늘날 기준으로 볼 때 상당히 낮았다.금속 산화물 반도체(MOS) 기술이 발전함에 따라, 수백만, 그리고 수십억 개의 MOS 트랜지스터를 하나의 [79]칩에 배치할 수 있게 되었고, 우수한 설계에는 철저한 계획이 필요하여 전자 설계 자동화(EDA) 분야가 탄생했습니다.일부 SSI 및 MSI 칩은 이산 트랜지스터와 같이 오래된 장비를 유지하고 몇 개의 게이트만 필요로 하는 새로운 장치를 만들기 위해 여전히 대량 생산됩니다.예를 들어 7400 시리즈 TTL 칩은 사실상의 표준이 되어 현재 생산되고 있습니다.

| 약자 | 이름. | 연도 | 트랜지스터 카운트[80] | 로직 게이트[81] 번호 |

|---|---|---|---|---|

| SSI | 소규모 집적 | 1964 | 1~10 | 1~12 |

| MSI | 중규모 집적 | 1968 | 10 ~ 500 | 13 ~ 99 |

| LSI | 대규모 집적 | 1971 | 500 ~ 20,000 | 100 ~ 9999 |

| VLSI | 대규모 집적 | 1980 | 20,000 ~ 100,000 | 10,000 ~ 999 |

| ULSI | 초대형 집적 | 1984 | 1,000,000 이상 | 10만 이상 |

소규모 통합(SSI)

첫 번째 집적회로에는 몇 개의 트랜지스터만 포함되어 있었습니다.수십 개의 트랜지스터를 포함하는 초기 디지털 회로는 몇 개의 로직 게이트를 제공했으며 Plesey SL201 또는 Philips TAA320과 같은 초기 선형 IC에는 2개의 트랜지스터가 있었습니다.그 이후로 집적회로의 트랜지스터 수는 극적으로 증가했습니다.LSI(대규모 통합)라는 용어는 IBM 과학자 Rolf Landauer가 이론 개념을 [82]설명할 때 처음 사용했는데, 이 용어로 인해 "소규모 통합"(SSI), "중규모 통합"(MSI), "초대규모 통합"(VLSI) 및 "초대규모 통합"(UL)이라는 용어가 생겨났습니다.초기 집적회로는 SSI였습니다.

SSI 회로는 초기 항공우주 프로젝트에 매우 중요했으며 항공우주 프로젝트는 기술 개발에 영감을 주는 데 도움이 되었습니다.미니트맨 미사일과 아폴로 프로그램 모두 관성 유도 시스템을 위해 경량 디지털 컴퓨터가 필요했다.비록 아폴로 유도 컴퓨터가 집적회로 [83]기술을 주도하고 동기부여를 했지만, 그것을 대량 생산하도록 강요한 것은 미니트맨 미사일이었다.미니트맨 미사일 프로그램과 기타 다양한 미국 해군 프로그램은 1962년 총 400만 달러의 집적회로 시장을 차지했으며, 1968년까지 미국 정부의 우주 및 방위 지출은 총 생산액 3억 1,200만 달러의 37%를 여전히 차지했습니다.

미국 정부의 요구는 IC 회사들이 산업 시장과 최종적으로는 소비자 시장에 진출할 수 있을 만큼 비용이 떨어질 때까지 초기 집적회로 시장을 지지했다.집적회로당 평균 가격은 1962년 50.00달러에서 1968년 [84]2.33달러로 떨어졌다.집적회로는 1970년대 초에 소비자 제품에 등장하기 시작했다.전형적인 애플리케이션은 텔레비전 수신기에서의 FM 반송파 간 사운드 처리였습니다.

첫 번째 응용 프로그램인 MOS 칩은 소규모 집적회로(SSI)[85] 칩이었습니다.모하메드 M에 이어 1960년 [86]아탈라가 제안한 MOS 집적회로 칩은 1962년 [30]RCA에서 프레드 하이만과 스티븐 호프스타인에 의해 제조된 16개의 트랜지스터 칩이었다.MOS SSI 칩의 첫 번째 실용적 적용은 NASA [85]위성을 위한 것이었다.

중간 규모 통합(MSI)

집적회로 개발의 다음 단계는 "중규모 집적"(MSI)이라고 불리는 각 칩에 수백 개의 트랜지스터를 포함하는 장치를 도입했습니다.

MOSFET 스케일링 기술을 통해 고밀도 [25]칩을 구축할 수 있었다.1964년까지 MOS 칩은 바이폴라 [32]칩보다 높은 트랜지스터 밀도와 낮은 제조 비용에 도달했습니다.

1964년 Frank Wanlass는 단일 [85][87]칩에 120개의 MOS 트랜지스터를 탑재한 싱글 칩 16비트 시프트 레지스터를 시연했습니다.같은 해 제너럴마이크로일렉트로닉스(General Microelectronics)는 120개의 P채널 MOS [31]트랜지스터로 구성된 최초의 상업용 집적회로 칩을 출시했습니다.그것은 로버트[30] 노먼과 프랭크 [88]완라스가 개발한 20비트 시프트 레지스터였다.MOS 칩은 무어의 법칙에 의해 예측된 속도로 복잡성이 더욱 증가하여 1960년대 [32]후반까지 칩 하나에 수백 개의 MOSFET를 탑재한 칩으로 이어졌다.

대규모 통합(LSI)

동일한 MOSFET 스케일링 기술과 경제적 요인에 의해 추진된 추가 개발은 1970년대 중반까지 "대규모 집적"(LSI)으로 이어졌으며,[89] 칩당 수만 개의 트랜지스터를 사용했습니다.

SSI, MSI 및 초기 LSI 및 VLSI 장치(예: 1970년대 초의 마이크로프로세서)의 처리 및 제조에 사용된 마스크는 대부분 수작업으로 제작되었으며, 종종 Rubylith-tape 또는 [90]그와 유사한 것을 사용했다.대규모 또는 복잡한 IC(예: 메모리 또는 프로세서)의 경우, 이는 회로 배치를 담당하는 특수 고용된 전문가에 의해 수행되었으며, 엔지니어 팀은 회로 설계자와 함께 각 마스크의 정확성과 완전성을 검사하고 검증합니다.

1970년대 초에 적당한 양으로 생산되기 시작한 1K비트 RAM, 계산기 칩, 최초의 마이크로프로세서 같은 집적회로는 4,000개 미만의 트랜지스터를 가지고 있었다.1만 개의 트랜지스터에 가까운 진정한 LSI 회로는 1974년경 컴퓨터 메인 메모리와 2세대 마이크로프로세서를 위해 생산되기 시작했습니다.

초대형 통합(VLSI)

'초대규모 집적'(VLSI)은 1980년대 초 수십만 개의 트랜지스터로 시작된 발전으로 2016년 현재 트랜지스터 수는 칩당 100억 개 이상으로 계속 증가하고 있습니다.

이러한 밀도를 높이기 위해서는 여러 가지 개발이 필요했습니다.제조업체들은 더 작은 MOSFET 설계 규칙과 더 깨끗한 제조 시설로 이전했습니다.프로세스 개선의 경로는 국제 반도체 기술 로드맵(ITRS)으로 요약되며, 이후 IRDS(International Roadmap for Devices and Systems)로 계승되고 있습니다.전자 설계 도구가 개선되어 합리적인 시간에 설계를 완료할 수 있게 되었습니다.에너지 효율이 높은 CMOS는 NMOS와 PMOS를 대체하여 전력 소비의 급격한 증가를 회피했습니다.현대 VLSI 장치의 복잡성과 밀도 때문에 마스크를 확인하거나 원래의 디자인을 손으로 하는 것이 더 이상 불가능해졌다.대신 엔지니어는 도구를 사용하여 대부분의 기능 검증 [91]작업을 수행합니다.

1986년에는 백만 개 이상의 트랜지스터를 포함하는 1메가비트 RAM 칩이 도입되었습니다.마이크로프로세서 칩은 1989년에 백만 트랜지스터, [92]2005년에 10억 트랜지스터 고지를 돌파했습니다.이러한 추세는 2007년에 소개된 칩에는 수백억 개의 메모리 [93]트랜지스터가 포함되어 있어 거의 수그러들지 않고 있습니다.

ULSI, WSI, SoC 및 3D-IC

복잡성의 증가를 반영하기 위해 100만 개 이상의 트랜지스터를 [94]가진 칩에 대해 "초대규모 집적"을 의미하는 ULSI라는 용어가 제안되었다.

웨이퍼 스케일 집적회로(WSI)는 실리콘 웨이퍼 전체를 사용하여 단일 "슈퍼 칩"을 생산하는 매우 큰 집적회로를 구축하는 방법입니다.WSI는 대형과 패키징을 조합하여 일부 시스템, 특히 대규모 병렬 슈퍼컴퓨터의 비용을 대폭 절감할 수 있습니다.이 이름은 WSI가 [95]개발되었을 때의 최신 기술인 초대규모 통합이라는 용어에서 따왔다.

시스템 온 어 칩(SoC 또는 SOC)은 컴퓨터나 다른 시스템에 필요한 모든 컴포넌트가 하나의 칩에 포함된 집적회로입니다.이러한 디바이스의 설계는 복잡하고 비용이 많이 들 수 있으며, 필요한 모든 컴포넌트를 하나의 다이로 통합함으로써 성능상의 이점을 얻을 수 있지만, 단일 다이 머신의 라이센스 및 개발 비용은 별도의 디바이스를 사용하는 것보다 훨씬 더 많이 듭니다.적절한 라이선스를 취득하면, 이러한 단점은 제조 및 조립 코스트의 삭감과 전력 버젯의 대폭 삭감에 의해서 상쇄됩니다.컴포넌트간의 신호가 온다이 상태로 유지되기 때문에, 필요한 전력은 큰폭으로 삭감됩니다( 「패키징」[96]을 참조).또한 신호원과 수신처가 다이 상에서 물리적으로 가까워져 배선의 길이, 즉 레이텐시, 전송 전력 비용 및 동일 칩 상의 모듈 간 통신에서 발생하는 폐열이 감소합니다.이로 인해 기존의 버스 아키텍처와는 달리 디지털 통신 네트워크에 시스템 온 칩 설계 방법론을 적용하는 이른바 Network-on-Chip(NoC; 네트워크 온 칩) 장치가 개발되었습니다.

3차원 집적회로(3D-IC)는 1개의 회로에 수직 및 수평으로 집적된 2층 이상의 활성 전자부품을 가진다.레이어간의 통신에는 온다이 시그널링이 사용되기 때문에 소비전력은 동등한 개별회선보다 훨씬 낮습니다.짧은 수직 와이어를 적절히 사용하면 전체 와이어 길이를 크게 줄여 보다 빠르게 [97]작동할 수 있습니다.

실리콘 라벨 및 그래피티

생산 시 식별이 가능하도록 대부분의 실리콘 칩은 한쪽 구석에 일련 번호가 있습니다.제조원의 로고를 추가하는 것도 일반적입니다.IC가 만들어진 이후, 일부 칩 설계자들은 실리콘 표면 영역을 은밀한, 기능하지 않는 이미지나 단어에 사용해 왔습니다.이것들은 때때로 칩 아트, 실리콘 아트, 실리콘 그래피티 또는 실리콘 [citation needed]낙서라고 불립니다.

IC 및 IC 패밀리

- 555 타이머 IC

- 연산 증폭기

- 7400 시리즈 집적회로

- 4000 시리즈 집적회로, 7400 시리즈에 대응하는 CMOS(「74」도 참조)HC00 시리즈)

- 일반적으로 상용화된 최초의 마이크로프로세서로 여겨지는 인텔 4004는 유명한 8080 CPU와 IBM PC의 8088, 80286, 486 등으로 이어졌다.

- MOS Technology 6502 및 Zilog Z80 마이크로프로세서는 1980년대 초반 가정용 컴퓨터에 많이 사용되었습니다.

- 68000 및 88000 시리즈로 이어지는 Motorola 6800 시리즈 컴퓨터 관련 칩(일부 Apple 컴퓨터 및 1980년대 Commodore Amiga 시리즈에 사용됨)

- 아날로그 집적회로의 LM 시리즈

「 」를 참조해 주세요.

- 칩셋

- 통합 주입 로직

- 이온 주입

- 마이크로일렉트로닉스

- 모노리식 마이크로파 집적회로

- 멀티 임계값 CMOS

- 실리콘 게르마늄

- 사운드 칩

- 향신료

- 칩 캐리어

- 다크 실리콘

- 내장 패시브 디바이스

- 고온 동작 수명

- 집적회로의 열 시뮬레이션

- 집적회로에서의 발열

레퍼런스

- ^ "Integrated circuit (IC)". JEDEC.

- ^ Wylie, Andrew (2009). "The first monolithic integrated circuits". Retrieved 14 March 2011.

Nowadays when people say 'integrated circuit' they usually mean a monolithic IC, where the entire circuit is constructed in a single piece of silicon.

- ^ Horowitz, Paul; Hill, Winfield (1989). The Art of Electronics (2nd ed.). Cambridge University Press. p. 61. ISBN 978-0-521-37095-0.

Integrated circuits, which have largely replaced circuits constructed from discrete transistors, are themselves merely arrays of transistors and other components built from a single chip of semiconductor material.

- ^ a b "Who Invented the IC?". @CHM Blog. Computer History Museum. 20 August 2014.

- ^ "Integrated circuits help Invention". Integratedcircuithelp.com. Retrieved 13 August 2012.

- ^ DE 833366 W. Jacobi/SIEMens AG: 1949년 4월 14일 "Halbleiterverstérker" 우선순위 신청, 1952년 5월 15일 발행.

- ^ "The Happless Tale of Geoffrey Dummer"는 2013년 5월 11일 Wayback Machine (n.d.) (HTML)에서 아카이브되었으며, Electronic Product News는 2008년 7월 8일에 접속했다.

- ^ Saxena, Arjum (2009). Invention of Integrated Circuits: Untold Important Facts. World Scientific. pp. 95–103.

- ^ a b c Rostky, George. "Micromodules: the ultimate package". EE Times. Archived from the original on 7 January 2010. Retrieved 23 April 2018.

- ^ "The RCA Micromodule". Vintage Computer Chip Collectibles, Memorabilia & Jewelry. Retrieved 23 April 2018.

- ^ Dummer, G.W.A.; Robertson, J. Mackenzie (16 May 2014). American Microelectronics Data Annual 1964–65. Elsevier. pp. 392–397, 405–406. ISBN 978-1-4831-8549-1.

- ^ 잭이 만든 칩, (c. 2008), (HTML), Texas Instruments, 2008년 5월 29일 취득.

- ^ Kilby, Jack S. 미국 특허 3,138,743은 1959년 2월 6일에 출원하여 1964년 6월 23일에 발행되었다.

- ^ Winston, Brian (1998). Media Technology and Society: A History: From the Telegraph to the Internet. Routledge. p. 221. ISBN 978-0-415-14230-4.

- ^ "Texas Instruments – 1961 First IC-based computer". Ti.com. Retrieved 13 August 2012.

- ^ '2000 노벨 물리학상', nobelprize.org (2000년 10월 10일)

- ^ a b Saxena, Arjun N. (2009). Invention of Integrated Circuits: Untold Important Facts. World Scientific. p. 140. ISBN 9789812814456.

- ^ a b c d "Integrated circuits". NASA. Retrieved 13 August 2019.

- ^ a b "1959: Practical Monolithic Integrated Circuit Concept Patented". Computer History Museum. Retrieved 13 August 2019.

- ^ 홀, 엘든 C(1996년)"달 여행: '아폴로 안내 컴퓨터의 역사'입니다.미국항공우주연구소, 페이지 18-19.ISBN 9781563471858

- ^ "Computer Pioneers – James L. Buie". IEEE Computer Society. Retrieved 25 May 2020.

- ^ a b 켄 쉬리프.「Texas Instruments TMX 1795: (거의) 최초의 잊혀진 마이크로프로세서」. 2015년.

- ^ Kuo, Yue (1 January 2013). "Thin Film Transistor Technology—Past, Present, and Future" (PDF). The Electrochemical Society Interface. 22 (1): 55–61. Bibcode:2013ECSIn..22a..55K. doi:10.1149/2.F06131if.

- ^ "1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated". Computer History Museum.

- ^ a b Laws, David (4 December 2013). "Who Invented the Transistor?". Computer History Museum.

- ^ Bassett, Ross Knox (2002). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. pp. 53–4. ISBN 978-0-8018-6809-2.

- ^ Bassett, Ross Knox (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. pp. 22–25. ISBN 9780801886393.

- ^ "Milestones:First Semiconductor Integrated Circuit (IC), 1958". IEEE Global History Network. IEEE. Retrieved 3 August 2011.

- ^ "Milestones:List of IEEE Milestones – Engineering and Technology History Wiki". ethw.org.

- ^ a b c d "Tortoise of Transistors Wins the Race – CHM Revolution". Computer History Museum. Retrieved 22 July 2019.

- ^ a b "1964 – First Commercial MOS IC Introduced". Computer History Museum.

- ^ a b c d Shirriff, Ken (30 August 2016). "The Surprising Story of the First Microprocessors". IEEE Spectrum. Institute of Electrical and Electronics Engineers. 53 (9): 48–54. doi:10.1109/MSPEC.2016.7551353. S2CID 32003640.

- ^ "1968: Silicon Gate Technology Developed for ICs". Computer History Museum. Retrieved 22 July 2019.

- ^ "1968: Silicon Gate Technology Developed for ICs". The Silicon Engine. Computer History Museum. Retrieved 13 October 2019.

- ^ Hittinger, William C. (1973). "Metal–Oxide–Semiconductor Technology". Scientific American. 229 (2): 48–59. Bibcode:1973SciAm.229b..48H. doi:10.1038/scientificamerican0873-48. JSTOR 24923169.

- ^ Kanellos, Michael (11 February 2003). "Moore's Law to roll on for another decade". CNET.

- ^ Davari, Bijan, Robert H. Dennard, and Ghavam G. Shahidi (1995). "CMOS scaling for high performance and low power-the next ten years" (PDF). Proceedings of the IEEE. Vol. 83, no. 4. pp. 595–606.

{{cite news}}: CS1 maint: 여러 이름: 작성자 목록(링크) - ^ "Qualcomm and Samsung Collaborate on 10nm Process Technology for the Latest Snapdragon 835 Mobile Processor". news.samsung.com. Retrieved 11 February 2017.

- ^ a b "Inside Pascal: NVIDIA's Newest Computing Platform". 5 April 2016.. 610mm에2 15,300,000개의 트랜지스터.

- ^ "International Roadmap for Devices and Systems" (PDF). IEEE. 2016.

- ^ 를 클릭합니다The Nobel Prize in Physics 2009, Nobel Foundation, 6 October 2009, retrieved 6 October 2009.

- ^ Fujita, H. (1997). A decade of MEMS and its future. Tenth Annual International Workshop on Micro Electro Mechanical Systems. doi:10.1109/MEMSYS.1997.581729.

- ^ Narasimha, A.; et al. (2008). "A 40-Gb/s QSFP optoelectronic transceiver in a 0.13 µm CMOS silicon-on-insulator technology". Proceedings of the Optical Fiber Communication Conference (OFC): OMK7.

- ^ Birkholz, M.; Mai, A.; Wenger, C.; Meliani, C.; Scholz, R. (2016). "Technology modules from micro- and nano-electronics for the life sciences". WIREs Nanomed. Nanobiotech. 8 (3): 355–377. doi:10.1002/wnan.1367. PMID 26391194.

- ^ Graham, Anthony H. D.; Robbins, Jon; Bowen, Chris R.; Taylor, John (2011). "Commercialisation of CMOS Integrated Circuit Technology in Multi-Electrode Arrays for Neuroscience and Cell-Based Biosensors". Sensors. 11 (5): 4943–4971. Bibcode:2011Senso..11.4943G. doi:10.3390/s110504943. PMC 3231360. PMID 22163884.

- ^ Zvi의 Or-Bach(2013년 12월 23일)."SOI가 반도체의 미래 기술인 이유." semimd.com Wayback Machine에서 2014년 11월 29일 아카이브.2013.

- ^ "애플 아이폰4에 삼성의 8스택 플래시가 등장" sst.semiconductor-digest.com2010년 9월 13일

- ^ Yamatake Corporation (2002). "Spherical semiconductor radio temperature sensor". Nature Interface. 7: 58–59. Archived from the original on 7 January 2009.

- ^ Takeda, Nobuo, MEMS applications of Ball Semiconductor Technology (PDF), archived from the original (PDF) on 1 January 2015

- ^ "Advanced Packaging".

- ^ "2.5D". Semiconductor Engineering.

- ^ "3D ICs". Semiconductor Engineering.

- ^ Wikichip (2018) Chiplet. wikichip.org은 IEDM 2017, Dr. Lisa Su accessdate=2019-05-26을 인용하고 있습니다.

- ^ "To Keep Pace With Moore's Law, Chipmakers Turn to 'Chiplets'". Wired. 11 June 2018.

- ^ Schodt, Christopher(2019년 4월 16일) 업스케일: 올해는 CPU '칩렛'의 해입니다.가젯 종료

- ^ LaPedus, Mark (16 April 2015). "FinFET Rollout Slower Than Expected". Semiconductor Engineering.

- ^ Basu, Joydeep (9 October 2019). "From Design to Tape-out in SCL 180 nm CMOS Integrated Circuit Fabrication Technology". IETE Journal of Education. 60 (2): 51–64. arXiv:1908.10674. doi:10.1080/09747338.2019.1657787. S2CID 201657819.

- ^ "About the EDA Industry". Electronic Design Automation Consortium. Archived from the original on 2 August 2015. Retrieved 29 July 2015.

- ^ Gray, Paul R.; Hurst, Paul J.; Lewis, Stephen H.; Meyer, Robert G. (2009). Analysis and Design of Analog Integrated Circuits. Wiley. ISBN 978-0-470-24599-6.

- ^ Rabaey, Jan M.; Chandrakasan, Anantha; Nikolic, Borivoje (2003). Digital Integrated Circuits (2nd ed.). Pearson. ISBN 978-0-13-090996-1.

- ^ Baker, Jacob (2008). CMOS: Mixed-Signal Circuit Design. Wiley. ISBN 978-0-470-29026-2.

- ^ "Stratix 10 Device Overview" (PDF). Altera. 12 December 2015.

- ^ Nathawad, L.; Zargari, M.; Samavati, H.; Mehta, S.; Kheirkhaki, A.; Chen, P.; Gong, K.; Vakili-Amini, B.; Hwang, J.; Chen, M.; Terrovitis, M.; Kaczynski, B.; Limotyrakis, S.; Mack, M.; Gan, H.; Lee, M.; Abdollahi-Alibeik, B.; Baytekin, B.; Onodera, K.; Mendis, S.; Chang, A.; Jen, S.; Su, D.; Wooley, B. "20.2: A Dual-band CMOS MIMO Radio SoC for IEEE 802.11n Wireless LAN" (PDF). IEEE Entity Web Hosting. IEEE. Retrieved 22 October 2016.

- ^ 쉬, 치핑(2013년 1월 17일).16nm/14nm FinFET: 새로운 일렉트로닉스 프런티어 실현.전자 설계

- ^ 미드, 카버 A;콘웨이, 린(1980) VLSI 시스템 읽기 입문, 매스:Addison-Wesley: ISBN 2-201-04358-0

- ^ "열간 작업 초음파 본딩 – 복원 프로세스를 통한 금속 흐름 촉진 방법", Proc. 20번째 IEEE 전자 부품 Conf.워싱턴 D.C., 1970년 5월, 페이지 549-556]

- ^ Chafkin, Max; King, Ian (9 June 2016). "How Intel Makes a Chip". Bloomburg Businessweek.

- ^ Lapedus, Mark (21 May 2015). "10 nm Fab Watch". Semiconductor Engineering.

- ^ "145 series ICs (in Russian)". Retrieved 22 April 2012.

- ^ Moammer, Khalid (16 September 2016). "AMD Zen CPU & AM4 Socket Pictured, Launching February 2017 – PGA Design With 1331 Pins Confirmed". Wccftech. Retrieved 20 May 2018.

- ^ "Ryzen 5 2500U – AMD – WikiChip". wikichip.org. Retrieved 20 May 2018.

- ^ Ung, Gordon Mah (30 May 2017). "AMD's 'TR4' Threadripper CPU socket is gigantic". PCWorld. Retrieved 20 May 2018.

- ^ "Federal Statutory Protection for Mask Works" (PDF). United States Copyright Office. United States Copyright Office. Retrieved 22 October 2016.

- ^ "Washington Treaty on Intellectual Property in Respect of Integrated Circuits". www.wipo.int.

- ^ 1995년 1월 1일, 무역 관련 지적재산권(TRIPs) 협정(세계무역기구(WTO) 협정 부속서 1C)이 발효되었다.TRIPs 제2부 제6항은 반도체 칩 제품을 보호하고 있으며, SCPA 제902조 (a) (2)에 따라 1995년 3월 23일 대통령 포고 제6780호의 기초가 되어 현재 및 미래의 모든 WTO 회원국으로 보호를 확대했다.

- ^ 일본은 1985년 반도체 집적회로의 회로배치에 관한 법률인 SCPA를 최초로 제정했다.

- ^ 1986년 EC는 회원들에게 반도체 지형을 보호하기 위한 국내 법률을 채택하도록 요구하는 지침을 발표했다.1986년 12월 16일 반도체 제품의 지형적 법적 보호에 관한 이사회 지침 1987/54/EEC, 제1조 (1)(b), 1987년 O.J. (L 24) 36.

- ^ Stern, Richard (1985). "MicroLaw". IEEE Micro. 5 (4): 90–92. doi:10.1109/MM.1985.304489.

- ^ Peter Clarke, 인텔, 10억 트랜지스터 프로세서 시대 진입, EE Times, 2005년 10월 14일 2013년 5월 10일 Wayback Machine에서 아카이브

- ^ 달마우, M. Les Microceseurs.바욘느 대학교

- ^ Bulletin de la Société fribourgeoise des sciences naturelles, Volumes 62 à 63 (in French). 1973.

- ^ Safir, Ruben (March 2015). "System on Chip – Integrated Circuits". NYLXS Journal. ISBN 9781312995512.

- ^ Mindell, David A. (2008). Digital Apollo: Human and Machine in Spaceflight. The MIT Press. ISBN 978-0-262-13497-2.

- ^ Ginzberg, Eli (1976). Economic impact of large public programs: the NASA Experience. Olympus Publishing Company. p. 57. ISBN 978-0-913420-68-3.

- ^ a b c Johnstone, Bob (1999). We were burning: Japanese entrepreneurs and the forging of the electronic age. Basic Books. pp. 47–48. ISBN 978-0-465-09118-8.

- ^ Moskowitz, Sanford L. (2016). Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. pp. 165–167. ISBN 9780470508923.

- ^ Boysel, Lee (12 October 2007). "Making Your First Million (and other tips for aspiring entrepreneurs)". U. Mich. EECS Presentation / ECE Recordings.

- ^ Kilby, J. S. (2007). "Miniaturized electronic circuits [US Patent No. 3,138, 743]". IEEE Solid-State Circuits Society Newsletter. 12 (2): 44–54. doi:10.1109/N-SSC.2007.4785580.

- ^ Hittinger, William C. (1973). "Metal-Oxide-Semiconductor Technology". Scientific American. 229 (2): 48–59. Bibcode:1973SciAm.229b..48H. doi:10.1038/scientificamerican0873-48. JSTOR 24923169.

- ^ Kanellos, Michael (16 January 2002). "Intel's Accidental Revolution". CNET.

- ^ O'Donnell, C.F. (1968). "Engineering for systems using large scale integration" (PDF). Afips 1968: 870. doi:10.1109/AFIPS.1968.93.

- ^ Clarke, Peter (14 October 2005). "Intel enters billion-transistor processor era". EETimes.com. Retrieved 23 May 2022.

- ^ "Samsung First to Mass Produce 16Gb NAND Flash Memory". phys.org. 30 April 2007. Retrieved 23 May 2022.

- ^ Meindl, J.D. (1984). "Ultra-large scale integration". IEEE Transactions on Electron Devices. 31 (11): 1555–1561. Bibcode:1984ITED...31.1555M. doi:10.1109/T-ED.1984.21752. S2CID 19237178.

- ^ Shanefield, Daniel (1985). "Wafer scale integration". google.com/patents. Retrieved 21 September 2014.

- ^ Klaas, Jeff (2000). "System-on-a-chip". google.com/patents. Retrieved 21 September 2014.

- ^ Topol, A.W.; Tulipe, D.C.La; Shi, L; et., al (2006). "Three-dimensional integrated circuits". IBM Journal of Research and Development. 50 (4.5): 491–506. doi:10.1147/rd.504.0491. S2CID 18432328.

추가 정보

- Veendrick, H.J.M. (2017). Nanometer CMOS ICs, from Basics to ASICs. Springer. ISBN 978-3-319-47595-0.

- Baker, R.J. (2010). CMOS: Circuit Design, Layout, and Simulation (3rd ed.). Wiley-IEEE. ISBN 978-0-470-88132-3.

- Marsh, Stephen P. (2006). Practical MMIC design. Artech House. ISBN 978-1-59693-036-0.

- Camenzind, Hans (2005). Designing Analog Chips (PDF). Virtual Bookworm. ISBN 978-1-58939-718-7. Archived from the original (PDF) on 12 June 2017.

Hans Camenzind invented the 555 timer

- Hodges, David; Jackson, Horace; Saleh, Resve (2003). Analysis and Design of Digital Integrated Circuits. McGraw-Hill. ISBN 978-0-07-228365-5.

- Rabaey, J.M.; Chandrakasan, A.; Nikolic, B. (2003). Digital Integrated Circuits (2nd ed.). Pearson. ISBN 978-0-13-090996-1.

- Mead, Carver; Conway, Lynn (1980). Introduction to VLSI systems. Addison Wesley Publishing Company. ISBN 978-0-201-04358-7.

외부 링크

이 문서의 외부 링크 사용은 Wikipedia의 정책 또는 지침을 따르지 않을 수 있습니다. 2021년 6월 (이를 에 대해 설명합니다) |

Wikimedia Commons 집적회로 관련 매체

Wikimedia Commons 집적회로 관련 매체

일반

특허

- US3,138,743 – 소형 전자회로 – J.S. Kilby

- US3,138,747 – 집적 반도체 회로 장치 – R.F. Stewart

- US3,261,081 –소형 전자회로 제조방법– J.S. Kilby

- US3,434,015 – 전자회로 소형화 등용 콘덴서– J. Kilby

집적회로 다이 제조