멤리스터

Memristor | |

| 발명된 | 레온 추아 (1971) |

|---|---|

| 전자기호 | |

멤리스터(/ˈm ɛmr ɪst ər/; 메모리 저항의 혼성어)는 전하 및 자속 링크와 관련된 비선형 2단자 전기 구성 요소입니다.1971년 Leon Chua(레온 추아)가 설명하고 이름을 붙여 저항기, 커패시터 및 인덕터로 구성된 기본적인 전기 구성 요소의 이론적인 4중주를 완성했습니다.[1]

Chua와 Kang은 나중에 그 개념을 멤리스티브 시스템으로 일반화했습니다.[2]이러한 시스템은 여러 개의 종래 구성 요소로 구성된 회로로 구성되며, 이 회로는 이상적인 멤리스터 구성 요소의 주요 특성을 모방하며 흔히 멤리스터라고도 합니다.이러한 멤리스터 시스템 기술, 특히 ReRAM이 개발되어 있습니다.

전자 장치에서 멤리스티브 특성을 식별하는 것은 논란을 불러 일으켰습니다.실험적으로, 이상적인 멤리스터는 아직 증명되지 않았습니다.[3][4]

기본적인 전기 구성 요소로서

Chua는 1971년 논문에서 비선형 저항(전압 대 전류), 비선형 커패시터(전압 대 전하) 및 비선형 인덕터(자속 링크 대 전류) 간의 이론적 대칭을 확인했습니다.이 대칭으로부터 그는 자속과 전하를 연결하는 네 번째 기본적인 비선형 회로 소자의 특성을 추론했고, 이를 멤리스터라고 불렀습니다.선형(또는 비선형) 저항과 달리 멤리스터는 과거 전압 또는 전류의 메모리를 포함하여 전류와 전압 사이에 동적 관계를 갖습니다.다른 과학자들은 Bernard Widrow의 멤리스터와 같은 동적 기억 저항기를 제안했지만 Chua는 수학적 일반성을 도입했습니다.

유도 및 특성

멤리스터는 원래 자속 연결 φ(t)와 흐르는 전하량 q(t) 사이의 비선형 함수 관계로 정의되었습니다.

자속 링크인 φ는 인덕터의 회로 특성에서 일반화됩니다.여기서는 자기장을 나타내는 것이 아닙니다.그것의 물리적 의미에 대해서는 아래에서 논의합니다.φ 기호는 시간 경과에 따른 전압의 적분으로 간주될 수 있습니다.

φ와 q 사이의 관계에서, 다른 것에 대한 하나의 도함수는 하나 또는 다른 것의 값에 의존하므로, 각 멤리스터는 전하에 따른 전하 의존적 플럭스 변화율을 기술하는 멤리스터 함수를 특징으로 합니다.

플럭스를 전압의 시간적분으로, 전하를 전류의 시간적분으로 대입하면 더 편리한 형태가 됩니다.

멤리스터를 저항, 커패시터, 인덕터와 연관시키기 위해서는 소자를 특징짓는 항 M(q)를 분리하여 미분방정식으로 쓰는 것이 좋습니다.

| 장치 | 특성(단위) | 미분방정식 |

|---|---|---|

| 저항기(R) | 저항(V/A 또는 옴, ω) | R = dV / dI |

| 축전기 (C) | 정전용량(C/V 또는 패러드) | C = dq / dV |

| 인덕터(L) | 인덕턴스(Wb/A 또는 헨리) | L = D φ / dI |

| 멤리스터(M) | 멤리스턴스(Wb/C 또는 옴) | M = D φ / dq |

위의 표는 I, q, φ, V의 모든 의미 있는 미분 비율을 다룹니다.I는 q의 도함수이고 φ은 V의 적분이기 때문에 어떤 장치도 I를 dq에, D φ를 dV에 연관시킬 수 없습니다.

이를 통해 멤저항이 전하 의존적 저항이라는 것을 추론할 수 있습니다.M(q(t))이 상수이면 옴의 법칙 R(t) = V(t)/I(t)를 얻습니다.그러나 M(q(t))이 사소하지 않은 경우 q(t)와 M(q(t))이 시간에 따라 변할 수 있기 때문에 방정식은 동등하지 않습니다.전압을 시간의 함수로 푸는 것은 다음을 만듭니다.

이 방정식은 M이 전하에 따라 변하지 않는 한, 전류와 전압 사이의 선형 관계를 정의한다는 것을 보여줍니다.0이 아닌 전류는 시간에 따라 변하는 전하를 의미합니다.그러나 q의 최대 변화가 M에 큰 변화를 일으키지 않는 한 교류는 순 전하 이동 없이 측정 가능한 전압을 유도함으로써 회로 작동의 선형 의존성을 드러낼 수 있습니다.

또한 전류가 인가되지 않으면 멤리스터는 정적입니다.I(t) = 0이면 V(t) = 0이고 M(t)은 일정합니다.이것이 기억 효과의 본질입니다.

마찬가지로, ( ϕ( t)W를 menductance로 정의할 수 있습니다.

전력 소비 특성은 저항기인 IR의2 특성을 떠올립니다.

M(q(t))이 교류 전류 하와 같이 거의 변하지 않는 한 멤리스터는 일정한 저항으로 나타납니다.그러나 M(q(t))이 급격하게 증가하면 전류 및 전력 소모가 빠르게 중단됩니다.

M(q)은 q의 모든 값에 대해 양의 값으로 물리적으로 제한됩니다(장치가 수동적이고 일부 q에서 초전도성이 되지 않는다고 가정).음의 값은 교류로 작동할 때 지속적으로 에너지를 공급한다는 것을 의미합니다.

모델링 및 검증

멤리스터 기능의 본질을 이해하기 위해서는 소자 모델링의 개념부터 시작하여 회로 이론적 기본 개념에 대한 지식이 어느 정도 유용합니다.[6]

공학자들과 과학자들은 원래 형태의 물리적 시스템을 거의 분석하지 않습니다.대신 시스템의 동작을 근사화하는 모델을 구성합니다.모형의 거동을 분석함으로써 실제 시스템의 거동을 예측하고자 합니다.모델을 구성하는 가장 큰 이유는 물리적 시스템이 너무 복잡하여 실제적인 분석에 적용할 수 없기 때문입니다.

20세기에는 연구자들이 멤리스티브 특성을 인식하지 못하는 장치에 대한 연구가 이루어졌습니다.이로 인해 그러한 장치는 멤리스터로 인정되어야 한다는 의견이 제기되었습니다.[6]퍼신과 디 벤트라는[3] 이상적인 멤리스터가 실제로 존재하는지 순수하게 수학적인 개념인지에 대한 오랜 논란을 해결하는 데 도움을 줄 수 있는 테스트를 제안했습니다.

2008년 이후 대부분의 작업이 이 분야에 집중되어 있기 때문에 이 글의 나머지 부분은 주로 ReRAM 장치와 관련된 구성원을 다루고 있습니다.

초전도 멤리스터 구성 요소

폴 펜필드 박사는 1974년 MIT 기술 보고서에서[7] 조셉슨 접합과 관련하여 멤리스터를 언급했습니다.이것은 회로 장치의 맥락에서 "멤리스터"라는 단어를 초기에 사용한 것입니다.

조셉슨 접합을 통과하는 전류의 용어 중 하나는 다음과 같습니다.

여기서 ϵ }은는) 물리적 초전도 물질을 기반으로 한 상수이며, {\은(는) 접점 양단의 전압이고 은(는) 접점을 통과하는 전류입니다.

조지프슨 접합에서 이러한 위상의존적 전도도에 대한 연구는 20세기 후반까지 진행되었습니다.[8][9][10][11]이러한 위상 의존적 컨덕턴스를 추출하기 위한 보다 포괄적인 접근법은 2014년에 Peotta와 DiVentra의 세미나 논문을 통해 나타났습니다.[12]

멤리스터 회로

이상적인 멤리스터를 연구하는 현실적인 어려움 때문에 멤리스터를 사용하여 모델링할 수 있는 다른 전기 장치에 대해 설명합니다.멤리스티브 장치(시스템)에 대한 수학적 설명은 이론을 참조하십시오.

방전 튜브는 멤리스티브 장치로 모델링할 수 있으며, 저항은 전도 전자 의 함수입니다[2]

은 방전관 양단의 전압이고, {\은 방전관에 흐르는 전류이며, 은 전도 전자의 수이다.단순 멤리스턴스 함수는 = }) = {\ . beta } F{\는 튜브의 치수 및 가스 충전물에 따라 파라미터가 됩니다.멤리스티브 동작의 실험적 식별은 평면에서의 "핀치 히스테리시스 루프"입니다.공통 방전관에 대한 이러한 특성을 보여주는 실험은 "A physical memristor Lissajous pigure"(유튜브)를 참조하십시오.또한 이 비디오는 물리적 멤리스터의 핀치 히스테리시스 특성의 편차를 이해하는 방법을 설명합니다.[13][14]

서미스터는 멤리스티브 장치로 모델링할 수 있습니다.[14]

eta }은(는) 물질상수, T은 서미스터의 절대체온, T_{은(두 온도 모두 켈빈 단위) 주변온도, () T_은는) T에서의냉온저항을 나타냅니다. 는 열용이고 는 서미스터의 방열 상수입니다.

거의 연구되지 않은 근본적인 현상은 pn-접합에서의 멤리스티브 행동입니다.[15]멤리스터는 다이오드 베이스의 전하 저장 효과를 모방하는 데 중요한 역할을 하며, 전도도 변조 현상(순방향 과도 상태에서 매우 중요함)에도 책임이 있습니다.

비평

2008년 HP Labs의 한 팀은 이산화티타늄 박막 분석을 바탕으로 Chua의 멤리스터에 대한 실험적 증거를 발견하여 ReRAM 장치의 작동을 멤리스터 개념에 연결시켰습니다.HP Labs에 따르면 멤리스터는 다음과 같은 방식으로 작동합니다. 멤리스터의 전기 저항은 일정하지 않고 이전에 장치를 통해 흐르는 전류, 즉 전류에 따라 달라집니다.현재 저항은 이전에 얼마나 많은 전하가 전기를 통해 흘렀는지와 어떤 방향으로 흘러갔는지에 따라 달라집니다. 장치는 그 이력을 기억합니다. 이른바 비 volat 특성입니다.전원 공급 장치가 꺼지면 멤리스터는 다시 켜질 때까지 최근 저항을 기억합니다.[17][18]

HP Labs의 연구 결과는 과학 저널 네이처에 발표되었습니다.[17][19]이 주장에 따라, Leon Chua는 멤리스터 정의가 저항 스위칭 효과에 기초하여 모든 형태의 2-단자 비휘발성 메모리 디바이스를 포함하도록 일반화될 수 있다고 주장했습니다.[16]Chua는 또한 멤리스터가 가장 오래된 알려진 회로 소자이며, 그 효과가 저항, 커패시터, 인덕터보다 앞선다고 주장했습니다.[20]그러나 진짜 멤리스터가 실제로 물리적 현실에 존재할 수 있는지에 대해서는 심각한 의문이 있습니다.[21][22][23][24]또한, 저항 스위칭 메모리에서 비-패시브 나노 배터리 효과가 관찰되므로 Chua의 일반화와 모순되는 실험적 증거도 있습니다.[25]Pershin과 Di Ventra에[3] 의해 그러한 이상적인 또는 일반적인 멤리스터가 실제로 존재하는지 순수하게 수학적인 개념인지를 분석하기 위한 간단한 테스트가 제안되었습니다.현재까지 테스트를 통과할 수 있는 실험용 저항 스위칭 소자(ReRAM)는 없는 것으로 보입니다.[3][4]

이 장치들은 나노전자 메모리 장치, 컴퓨터 로직 및 뉴로모픽/뉴로모픽 컴퓨터 아키텍처의 응용을 위해 고안되었습니다.[26][27]2013년에 Hewlett-Packard CTO Martin Fink는 멤리스터 메모리가 이르면 2018년에 상용화될 수 있다고 제안했습니다.[28]2012년 3월, HRL 연구소와 미시간 대학교의 연구원들은 CMOS 칩 위에 만들어진 최초의 기능하는 멤리스터 어레이를 발표했습니다.[29]

원래 1971년 정의에 따르면, 멤리스터는 전하와 자속 연결 사이의 비선형 관계를 형성하는 네 번째 기본 회로 소자입니다.2011년 Chua는 저항 스위칭에 기반한 모든 2단자 비휘발성 메모리 장치를 포함하는 더 넓은 정의를 주장했습니다.[16]Williams는 MRAM, 상변화 메모리 및 ReRAM이 멤리스터 기술이라고 주장했습니다.[32]일부 연구원들은 혈액과[33] 피부와[34][35] 같은 생물학적 구조가 이 정의에 부합한다고 주장했습니다.다른 사람들은 HP Labs와 다른 형태의 ReRAM이 개발 중인 메모리 장치가 멤리스터가 아니라 더 넓은 부류의 가변 저항 시스템의 일부이며,[36] 멤리스터에 대한 더 넓은 정의는 HP의 멤리스터 특허를 선호하는 과학적으로 정당화할 수 없는 랜드그랩이라고 주장했습니다.[37]

2011년, 뮤펠스와 슈뢰더는 초기 멤리스터 논문 중 하나에 이온 전도에 관한 잘못된 가정이 포함되어 있다고 언급했습니다.[38]2012년, Muffels와 Soni는 멤리스터의 실현에 있어서 몇 가지 근본적인 문제와 문제점을 논의했습니다.[21]그들은 전압 또는 전류 스트레스 하에서 금속-TiO-금속2−x 구조의 거동에 대한 농도 분극 효과의 영향을 고려하지 않았기 때문에 Nature 기사 "Missing memristor found"[17]에 제시된 전기화학 모델링에서 부적절한 점을 지적했습니다.이 비평은 2013년 Valov et al.[25]에 의해 언급되었습니다.

일종의 사고 실험에서, 뮤펠스와 소니는[21] 더 나아가 심각한 불일치를 드러냈습니다.소위 비휘발성 특성을[16] 가진 전류 제어 멤리스터가 물리적 현실에 존재한다면, 그 동작은 시스템의 "정보" 상태를 변화시키는 데 필요한 최소 에너지량에 제한을 두는 란다우어의 원리에 위배될 것입니다.이 비평은 마침내 2013년에 디 벤트라와 퍼신에[22] 의해 채택되었습니다.

이러한 맥락에서, 뮤펠스와 소니는[21] 근본적인 열역학적 원리를 언급했습니다: 비휘발성 정보 저장은 시스템의 별개의 내부 기억 상태들을 서로 분리하는 자유 에너지 장벽의 존재를 요구합니다; 그렇지 않으면, 한 사람은 "무관심" 상황에 직면하게 될 것입니다.그리고 시스템은 열 변동의 영향을 받는 한 메모리 상태에서 다른 메모리 상태로 임의로 변동할 것입니다.열 변동으로부터 보호되지 않은 경우 내부 메모리 상태는 확산 동역학을 보여 상태를 저하시킵니다.[22]따라서 자유 에너지 장벽은 비트 작동의 낮은 비트 오류 확률을 보장할 수 있을 만큼 충분히 높아야 합니다.[39]따라서 모든 메모리 장치에서 의도적으로 비트 값을 변경하려면 필요한 비트 오류 확률에 따라 에너지 요구량의 하한이 항상 존재합니다.[39][40]

멤리스티브 체계의 일반적인 개념에서 정의 방정식은 다음과 같습니다.

여기서 u(t)는 입력 신호이고, y(t)는 출력 신호입니다.벡터 x는 장치의 다양한 내부 메모리 상태를 설명하는 n개의 상태 변수 세트를 나타냅니다.ẋ는 시간에 따른 상태 벡터 x의 시간 의존적 변화율입니다.

단순한 곡선 맞춤을 넘어서서 저항성 랜덤 액세스 메모리 장치와 같은 비휘발성 메모리 요소의 실제 물리적 모델링을 목표로 할 때는 앞서 언급한 물리적 상관 관계를 주시해야 합니다.제안된 모델과 그 결과 상태 방정식의 적합성을 확인하기 위해, 입력 신호 u(t)는 불가피한 열 변동의 존재를 고려한 확률적 항 ξ(t)와 중첩될 수 있습니다.일반적인 형태의 동적 상태 방정식은 최종적으로 다음과 같이 읽힙니다.

여기서 ξ(t)는 예를 들어 백색 가우스 전류 또는 전압 노이즈입니다.노이즈에 대한 시스템의 시간 의존적 반응에 대한 분석 또는 수치 분석에 기초하여 모델링 접근법의 물리적 유효성에 대한 결정이 내려질 수 있습니다. 예를 들어 시스템이 전원 오프 모드에서 메모리 상태를 유지할 수 있습니까?

이러한 분석은 Di Ventra와 Pershin에[22] 의해 진짜 전류 제어 멤리스터에 대해 수행되었습니다.제안된 동적 상태 방정식은 그러한 멤리스터가 피할 수 없는 열 변동에 대처할 수 있도록 하는 물리적 메커니즘을 제공하지 않기 때문에 전류 제어 멤리스터는 전류 노이즈의 영향 하에서 시간 경과에 따라 상태가 불규칙하게 변경됩니다.[22][41]따라서 디 벤트라와 퍼신은[22] 저항(기억) 상태가 전류 또는 전압 이력에만 의존하는 멤리스터는 피할 수 없는 존슨-나이퀴스트 잡음으로부터 그들의 기억 상태를 보호할 수 없을 것이며, 소위 "스토캐스틱 파국"이라고 불리는 정보 손실로 영구적으로 고통 받을 것이라고 결론지었습니다.따라서 전류 제어 멤리스터는 물리적 현실에서 고체 소자로 존재할 수 없습니다.

위에서 언급된 열역학적 원리는 더 나아가, 2-단자 비-휘발성 메모리 디바이스들(예컨대, "저항-스위칭" 메모리 디바이스들(ReRAM))의 동작이 멤리스터 개념과 연관될 수 없음을 암시하며, 즉, 그러한 디바이스들은 그들의 전류 또는 전압 이력을 그 자체로 기억할 수 없습니다.별개의 내부 메모리 또는 저항 상태 간의 전이는 확률적인 특성을 갖습니다.상태 {i}에서 상태 {j}로의 전환 확률은 두 상태 사이의 자유 에너지 장벽의 높이에 따라 달라집니다.따라서 전이 확률은 메모리 장치를 적절하게 구동함으로써 영향을 받을 수 있습니다. 즉, 외부에서 인가된 바이어스를 통해 전이 {i} → {j}에 대한 자유 에너지 장벽을 "lowering"함으로써 영향을 받을 수 있습니다.

"저항 스위칭" 이벤트는 외부 바이어스를 특정 임계값 이상의 값으로 설정하면 간단히 실행할 수 있습니다.이것은 사소한 경우입니다. 즉, 전이 {i} → {j}에 대한 자유 에너지 장벽이 0으로 감소합니다.임계값 미만의 바이어스를 적용하는 경우 장치가 시간 경과에 따라 전환될 가능성은 여전히 유한하지만(무작위 열 변동에 의해 트리거됨), 확률적 프로세스를 다루므로 전환 이벤트가 발생할 시기를 예측하는 것은 불가능합니다.이것이 관찰된 모든 저항 스위칭(ReRAM) 프로세스의 확률적 특성에 대한 기본 이유입니다.자유 에너지 장벽이 충분히 높지 않다면, 메모리 장치는 아무것도 할 필요 없이 심지어 바꿀 수 있습니다.

2단자 비휘발성 메모리 장치가 별개의 저항 상태 {j}인 것으로 확인되면 현재 상태와 앞서 설명한 전압 이력 사이에 물리적 일대일 관계가 없습니다.따라서 멤리스터/멤리스티브 시스템을 위해 제안된 수학적 프레임워크 내에서 개별 비휘발성 메모리 장치의 스위칭 동작을 설명할 수 없습니다.

추가적인 열역학적 호기심은 멤리스터/멤리스티브 장치가 저항기처럼 에너지적으로 작용해야 한다는 정의에서 생겨납니다.그러한 장치로 들어오는 순간적인 전력은 주변으로 줄 열로 완전히 소멸되므로 한 저항 상태 x에서i 다른 저항 상태 x로j 가져온 후 시스템에 여분의 에너지가 남아 있지 않습니다.따라서, 상태 xi, U(V, T, xi)에서 멤리스터 소자의 내부 에너지는 상태 xj, U(V, T, x)와j 동일할 것입니다. 비록 이러한 상이한 상태들이 다양한 소자의 저항들을 발생시킬 것이고, 그 자체는 소자의 재료의 물리적인 변화에 의해 야기될 것입니다.

다른 연구자들은 선형 이온 드리프트 가정에 기초한 멤리스터 모델이 설정 시간(고-저저항 스위칭)과 리셋 시간(저-고저항 스위칭) 사이의 비대칭성을 설명하지 않으며 실험 데이터와 일치하는 이온 이동도 값을 제공하지 않는다고 지적했습니다.이러한 단점을 보완하기 위해 비선형 이온 드리프트 모델이 제안되었습니다.[42]

ReRAM 연구자들의 2014년 기사는 Strukov(HP)의 초기/기본 멤리스터 모델링 방정식이 실제 장치 물리학을 잘 반영하지 못하는 반면, Pickett(피켓)의 모델이나 Menzel(멘젤은 해당 기사의 공동 저자)의 ECM 모델과 같은 후속 (물리학 기반) 모델은 적절한 예측 가능성을 가지고 있다고 결론 내렸습니다.계산적으로 금지되어 있습니다.2014년 현재에도 이러한 문제를 해결하는 모델을 찾고 있습니다. 기사는 Chang과 Yakoppic의 모델을 잠재적으로 좋은 타협점으로 파악하고 있습니다.[43]

연구 기관 Gartner의 전기 공학 분석가 Martin Reynolds는 HP가 자신의 기기를 멤리스터라고 부르는 것은 엉성하지만 비평가들은 멤리스터가 아니라고 현학적으로 말하고 있다고 지적했습니다.[44]

실험시험

Chua는 장치가 적절하게 멤리스터로 분류될 수 있는지를 판단하기 위한 실험 테스트를 제안했습니다.[2]

- 전압-전류 평면에서 리사쥬 곡선은 초기 조건에 관계없이 양극성 주기 전압 또는 전류에 의해 구동될 때 핀치 히스테리시스 루프입니다.

- 강제 신호의 주파수가 증가함에 따라 핀치된 히스테리시스 루프의 각 로브의 면적이 축소됩니다.

- 주파수가 무한대로 갈수록 히스테리시스 루프는 원점을 통해 직선으로 퇴화되며, 원점의 기울기는 강제 신호의 진폭과 모양에 따라 달라집니다.

Chua에[45][46] 따르면 ReRAM을 포함한 모든 저항성 스위칭 메모리, MRAM 및 상변화 메모리는 이러한 기준을 충족하며 멤리스터입니다.그러나 초기 조건의 범위 또는 주파수의 범위에 걸친 리사쥬 곡선에 대한 데이터의 부족은 이 주장에 대한 평가를 복잡하게 합니다.

실험적 증거에 따르면 레독스 기반 저항 메모리(ReRAM)는 Chua의 멤리스터 모델과 반대되는 나노 배터리 효과를 포함합니다.이는 정확한 ReRAM 모델링이 가능하도록 멤리스터 이론을 확장하거나 수정해야 함을 나타냅니다.[25]

이론.

2008년, HP Labs의 연구원들은 이산화티타늄 박막을 기반으로 한 멤리스턴스 함수 모델을 소개했습니다.[17]R ≪ R의 경우 멤리스턴스 함수는 다음과 같이 결정되었습니다.

여기서, R은OFF 고저항 상태를 나타내고ON, R은 저저항 상태를 나타내고, μ는v 박막 내 도펀트의 이동도를 나타내고, D는 막 두께를 나타냄.HP Labs 그룹은 비선형 이온 드리프트 및 경계 효과로 인한 실험 측정과 멤리스터 모델 간의 차이를 보완하기 위해 "창 기능"이 필요하다고 언급했습니다.

스위치로 작동

일부 멤리스터의 경우 인가된 전류 또는 전압이 저항에 상당한 변화를 일으킵니다.이러한 장치는 원하는 저항 변화를 달성하기 위해 소비되어야 하는 시간과 에너지를 조사함으로써 스위치로 특징지을 수 있습니다.이것은 인가된 전압이 일정하게 유지된다고 가정합니다.단일 스위칭 이벤트 동안 에너지 소산을 해결하면 멤리스터가 시간 T에서 T로 R에서 전환하려면 전하가 δQ = Q-Q만큼 변화해야 함을 알 수 있습니다.

V = I(q)M(q)을 대입한 다음 ∫dq/V = ∆Q/V를 상수 V로 대입하면 최종 식을 생성합니다.이러한 전력 특성은 축전기 기반의 금속 산화물 반도체 트랜지스터와 근본적으로 다릅니다.트랜지스터와 달리 멤리스터의 최종 상태는 바이어스 전압에 의존하지 않습니다.

Williams가 설명한 멤리스터의 유형은 전체 저항 범위를 전환한 후 이상적인 것을 멈추고, 히스테리시스를 생성하여 "하드 스위칭 레짐"이라고도 합니다.[17]다른 종류의 스위치는 순환 M(q)을 가지므로 일정한 바이어스 하에서 각 꺼짐 이벤트 뒤에 꺼짐 이벤트가 이어집니다.이러한 장치는 모든 조건에서 멤리스터 역할을 하지만 실용성은 떨어집니다.

멤리스티브 시스템

n차 멤리스티브 시스템의 더 일반적인 개념에서 정의 방정식은

여기서 u(t)는 입력 신호, y(t)는 출력 신호, 벡터 x는 장치를 설명하는 n개의 상태 변수 집합을 나타내고 g와 f는 연속 함수입니다.전류 제어 멤리스티브 시스템의 경우 신호 u(t)는 전류 신호 i(t)를 나타내고 신호 y(t)는 전압 신호 v(t)를 나타냅니다.전압 제어 멤리스티브 시스템의 경우 신호 u(t)는 전압 신호 v(t)를 나타내고 신호 y(t)는 전류 신호 i(t)를 나타냅니다.

순수 멤리스터는 이러한 방정식의 특별한 경우로, 즉 x가 전하에만 의존할 때(x = q), 전하가 시간 도함수 dq/dt = i(t)를 통해 전류와 관련되어 있기 때문입니다.따라서 순수 멤리스터의 경우 f(즉, 상태 변화율)는 전류 i(t)와 같거나 비례해야 합니다.

핀치 히스테리시스

멤리스터와 멤리스티브 시스템의 결과적인 특성 중 하나는 핀치 히스테리시스 효과의 존재입니다.[47]전류 제어 멤리스티브 시스템의 경우 입력 u(t)는 전류 i(t), 출력 y(t)는 전압 v(t), 곡선의 기울기는 전기 저항을 나타냅니다.핀치된 히스테리시스 곡선의 기울기 변화는 ReRAM과 다른 형태의 2단자 저항 메모리의 중심이 되는 현상인 서로 다른 저항 상태 간의 전환을 보여줍니다.멤리스티브 이론은 높은 주파수에서 핀치 히스테리시스 효과가 퇴화되어 선형 저항을 나타내는 직선이 발생할 것으로 예측합니다.일부 비교차 고정 히스테리시스 곡선(타입-II로 표시)은 멤리스터로 설명할 수 없음이 입증되었습니다.[48]

회로 상호작용의 멤리스티브 네트워크 및 수학적 모델

멤리스티브 네트워크의 개념은 Leon Chua에 의해 1965년 논문 "멤리스티브 디바이스 및 시스템"에서 처음 소개되었습니다.Chua는 인간 뇌의 행동을 시뮬레이션 할 수 있는 인공 신경망을 구축하기 위한 수단으로 멤리스티브 장치의 사용을 제안했습니다.사실 회로의 멤리스티브 소자는 키르히호프의 법칙으로 인해 복잡한 상호작용을 합니다.멤리스티브 네트워크는 멤리스티브 디바이스를 기반으로 하는 인공 신경망의 한 종류로서, 멤리스티브의 특성을 나타내는 전자 부품입니다.멤리스티브 네트워크에서 멤리스티브 장치는 인간 뇌의 뉴런과 시냅스의 행동을 시뮬레이션하는 데 사용됩니다.네트워크는 가중치 세트를 통해 다른 계층에 연결되는 멤리스티브 디바이스의 계층으로 구성됩니다.이러한 가중치는 교육 과정 중에 조정되므로 네트워크가 새로운 입력 데이터를 학습하고 적응할 수 있습니다.멤리스티브 네트워크의 한 가지 장점은 비교적 간단하고 저렴한 하드웨어를 사용하여 구현할 수 있기 때문에 저비용 인공지능 시스템을 개발하는 데 매력적인 옵션이 됩니다.그들은 또한 더 적은 전력을 사용하여 정보를 저장하고 처리할 수 있기 때문에 기존의 인공 신경망보다 더 에너지 효율적일 수 있는 가능성이 있습니다.그러나 멤리스티브 네트워크 분야는 아직 개발 초기 단계로, 이들의 역량과 한계를 충분히 이해하기 위해서는 더 많은 연구가 필요합니다.전압 발생기가 직렬로 있는 멤리스티브 장치만 있는 가장 간단한 모델의 경우, 각 장치에 대한 네트워크 내부 메모리의 진화를 설명하는 정확하고 닫힌 형태의 방정식(Caravelli-Traversa-Di Ventra equation, CTD)[49]이 있습니다.Williams-Strukov 모델 = R -+ x )=에 의해 주어진 두 저항 값 사이의 스위치의 단순 멤리스터 모델의 경우(현실적이지는 않음) / dt / - / -인}에는 다음과 같은 형태를 갖는 비선형 결합 미분 방정식 세트가 있습니다

여기서 는 대각선에 원소 가 있는 대각선 행렬이며, χ 는 멤리스터 물리 매개 변수를 기반으로 합니다.벡터 → 는 멤리스터에 대한 전압 발생기의 벡터입니다.회로 토폴로지는 그래프의 주기 행렬로 정의된 프로젝터 운영자 ω ω = ω }=\에서만 입력됩니다이 방정식은 키르히호프의 법칙으로 인한 상호작용에 대한 간결한 수학적 설명을 제공합니다.흥미롭게도, 이 방정식은 랴푸노프 함수의 존재와 고전적인 터널링 현상과 같은 홉필드 네트워크와 공통적으로 많은 특성을 공유합니다.[50]멤리스티브 네트워크의 맥락에서, CTD 방정식은 상이한 동작 조건에서 멤리스티브 디바이스의 동작을 예측하거나 특정 애플리케이션에 대한 멤리스티브 회로를 설계 및 최적화하는 데 사용될 수 있습니다.

확장형 시스템

일부 연구자들은 ReRAM의 동작을 설명하는 데 HP의 멤리스터 모델의 과학적 정당성에 대한 문제를 제기하고 인식된 결함을 해결하기 위해 확장된 멤리스티브 모델을 제안했습니다.[36][37][25]

일 예는[51] 입력 신호 u(t)의 고차 미분을 직렬 확장으로서 통합하는 동적 시스템을 포함함으로써 멤리스티브 시스템 프레임워크를 확장하려고 시도합니다.

여기서 m은 양의 정수, u(t)는 입력 신호, y(t)는 출력 신호, 벡터 x는 장치를 설명하는 n개의 상태 변수의 집합을 나타내고 함수 g와 f는 연속 함수입니다.이 방정식은 멤리스티브 시스템과 동일한 영 교차 히스테리시스 곡선을 생성하지만 멤리스티브 시스템이 예측한 것과는 다른 주파수 응답을 생성합니다.

다른 예는 예측된 제로 크로싱 핀치 히스테리시스 효과를 위반하는 관찰된 나노 배터리 효과를 설명하기 위해 오프셋 값 a a를 포함하는 것을 제안합니다.[25]

구현

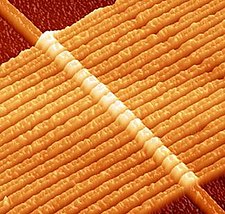

이산화티타늄 멤리스터

실험용 고체 상태 버전이 R에 의해 보고되었을 때 멤리스터에 대한 관심이 되살아났습니다. 2007년 휴렛 패커드의 스탠리 윌리엄스.[52][53][54]이 기사는 고체 소자가 나노 스케일의 박막의 거동을 바탕으로 멤리스터의 특성을 가질 수 있음을 처음으로 보여준 것입니다.이 장치는 이론적 멤리스터가 제안한 대로 자속을 사용하지도 않고 축전기처럼 전하를 저장하지도 않으며 대신 전류의 이력에 따라 저항을 달성합니다.

비록 그들의 TiO2 멤리스터에 대한 HP의 초기 보고서에는 인용되지 않았지만, 이산화티타늄의 저항 스위칭 특성은 1960년대에 처음 기술되었습니다.[55]

HP 장치는 두 개의 5nm 두께의 전극, 하나는 티타늄, 다른 하나는 백금 사이의 얇은 (50nm) 이산화티타늄 막으로 구성되어 있습니다.처음에는 이산화티타늄 막에 두 개의 층이 있는데, 그 중 하나는 산소 원자가 약간 고갈되어 있습니다.산소 빈자리는 전하 운반체 역할을 하는데, 이는 고갈된 층이 고갈되지 않은 층보다 저항이 훨씬 낮다는 것을 의미합니다.전기장이 인가되면 산소공극이 드리프트(고속 이온 전도체 참조)되어 고저항 층과 저저항 층의 경계가 변경됩니다.따라서 필름 전체의 저항은 특정 방향으로 얼마나 많은 전하를 통과시켰는지에 따라 달라지는데, 이는 전류의 방향을 변경함으로써 가역적입니다.[17]HP 소자는 나노 스케일에서 빠른 이온 전도를 보여주기 때문에 나노 이온 소자로 여겨집니다.[56]

멤브레인 저항은 도핑된 층과 고갈된 층이 모두 저항에 기여하는 경우에만 표시됩니다.충분한 전하가 멤리스터를 통과하여 이온이 더 이상 이동할 수 없게 되면 장치는 히스테리시스에 들어갑니다.q= ∫Idt의 적분을 중단하고 오히려 q를 상한으로 유지하고 M을 고정하여 전류가 반전될 때까지 일정한 저항으로 작용합니다.

박막 산화물의 메모리 응용은 한동안 활발한 연구의 영역이었습니다.IBM은 2000년에 Williams가 설명한 것과 유사한 구조에 대한 기사를 발표했습니다.[57]삼성은 Williams가 설명한 것과 유사한 산화물-공백 기반 스위치에 대한 미국 특허를 보유하고 있습니다.[58]

2010년 4월, HP 연구소는 1ns(~1GHz) 스위칭 시간과 3nm x 3nm 크기로 작동하는 실용적인 멤리스터를 보유하고 있다고 발표했습니다.[59] 이는 이 기술의 미래에 좋은 징조입니다.[60]이러한 밀도에서는 현재 25nm 이하의 플래시 메모리 기술에 쉽게 맞설 수 있습니다.

이산화규소 멤리스터

60년대부터 이산화규소로 실현된 나노크기의 박막에 멤리스턴스가 등록된 것으로 보입니다.[61]

그러나 실리콘의 히스테리틱 전도율은 2009년에만 멤리스티브 효과와 관련이 있는 반면 토니 케니언과 그의 그룹은 실리콘 산화물 박막의 저항성 스위칭이 고도의 비양론적 아산화물 상에서 실리콘 나노 포함으로 인한 것임을 분명히 보여주었습니다.[63]

고분자 멤리스터

2004년, Krieger와 Spitzer는 작동하는 비휘발성 메모리 셀을 만드는 데 필요한 스위칭 특성과 유지력을 향상시킨 고분자 및 무기 유전체 유사 물질의 동적 도핑을 설명했습니다.[64]전극과 활성 박막 사이에 수동층을 사용하여 전극에서 이온을 추출하는 기능을 향상시켰습니다.이 패시브 층으로 패스트 이온 도체를 사용할 수 있어 이온 추출 분야를 크게 줄일 수 있습니다.

2008년 7월, Erokhin과 Fontana는 최근에 발표된 이산화티타늄 멤리스터 이전에 고분자 멤리스터를 개발했다고 주장했습니다.[65]

2010년에, Alibart, Gamrat, Vuillaume [66]등은 멤리스터로서[67] 동작하고 생물학적 스파이킹 시냅스의 주요 거동을 나타내는 새로운 하이브리드 유기/나노입자 장치(NOMFET : Nanoparticle Organic Memory Field Effect Transistor)를 소개했습니다.시냅스 트랜지스터(synapstor)라고도 불리는 이 장치는 신경에서 영감을 받은 회로(파블로비아 학습을 보여주는 연상 메모리)를 보여주기 위해 사용되었습니다.[68]

2012년 크루피, 프라단, 토저는 유기 이온 기반 멤리스터를 사용하여 신경 시냅스 메모리 회로를 만드는 개념 설계 증명을 설명했습니다.[69]시냅스 회로는 학습에 대한 장기적인 잠재력과 비활동 기반 망각을 입증했습니다.회로의 격자를 사용하여 빛의 패턴이 저장되었고 나중에 회상되었습니다.이것은 가장자리와 움직이는 선과 같은 시각 신호를 처리하는 시공간 필터 역할을 하는 일차 시각 피질의 V1 뉴런의 행동을 모방합니다.

2012년, Erokhin과 공동 저자들은 고분자 멤리스터를 기반으로 학습하고 적응하는 능력을 갖춘 확률적 3차원 행렬을 증명했습니다.[70]

레이어드 멤리스터

2014년, Bessonov et al.[71] 은 플라스틱 호일 상의 은 전극 사이에 끼인 MoOx/MoS2 헤테로 구조를 포함하는 유연한 멤리스티브 디바이스를 보고했습니다.제조 방법은 전적으로 2차원 층상 전이금속 디칼코게나이드(TMDs)를 이용한 프린팅 및 용액-가공 기술에 기반을 두고 있습니다.멤리스터는 기계적으로 유연하고 광학적으로 투명하며 저렴한 가격으로 생산됩니다.스위치의 멤리스티브 거동은 두드러진 멤 정전용량 효과를 동반하는 것으로 확인되었습니다.높은 스위칭 성능, 입증된 시냅스 가소성 및 기계적 변형에 대한 지속 가능성은 새로운 컴퓨팅 기술에서 생물학적 신경 시스템의 매력적인 특성을 모방할 것을 약속합니다.

아톰리스터

원자리스터는 원자적으로 얇은 나노 물질 또는 원자 시트에서 멤리스티브 거동을 나타내는 전기 소자로 정의됩니다.2018년, 텍사스 대학교 Akinwande 그룹의 Ge and Wu et al. 은 수직 금속- insulator-금속(MIM) 소자 구조를 기반으로 하는 단층 TMD (MX, M = Mo, W; 및 X = S, Se) 원자 시트에서 보편적 멤리스티브 효과를 최초로 보고했습니다.그 작업은 나중에 약 0.33 nm의 가장 얇은 메모리 재료인 단층 육각 질화붕소로 확장되었습니다.[73]이러한 원자 리스터는 형성이 필요 없는 스위칭과 단극성 및 양극성 작동을 모두 제공합니다.스위칭 거동은 다양한 도전 전극(금, 은 및 그래핀)을 갖는 단결정 및 다결정 필름에서 발견됩니다.원자적으로 얇은 TMD 시트는 CVD/MOCVD를 통해 준비되므로 저비용으로 제조할 수 있습니다.이후 낮은 "on" 저항과 큰 on/off ratio의 장점을 살려 MoS2 또는 h-BN atomristor 기반의 고성능 제로 파워 RF 스위치를 증명하여 5G, 6G 및 THz 통신 및 연결 시스템을 위한 멤리스터의 새로운 적용을 나타냅니다.[74][75]2020년, 전도성 가상점 메커니즘에 대한 원자론적 이해는 자연 나노기술의 논문에서 설명되었습니다.[76]

강유전체 멤리스터

강유전체 멤리스터는[77] 두 개의 금속 전극 사이에 끼인 얇은 강유전체 장벽을 기반으로 합니다.접합부에 양 또는 음의 전압을 인가하여 강유전체 물질의 편광을 전환하면 R ≫ R(Tunnel Electro-Resistance라고 하는 효과)이라는 두 가지 크기의 저항 변화가 발생할 수 있습니다.일반적으로 편광은 갑자기 전환되지 않습니다.반전은 극과 극이 반대인 강유전체 영역의 핵생성과 성장을 통해 점진적으로 발생합니다.이 과정에서 저항은 R 또는ON R이OFF 아니라 그 사이에 있습니다.전압이 순환되면 강유전체 도메인 구성이 진화하여 저항값을 미세하게 조정할 수 있습니다.강유전성 멤리스터의 주요 장점은 강유전성 도메인 역학을 조정할 수 있어 멤리스터 응답을 조작할 수 있는 방법을 제공하고, 저항 변화가 순수 전자 현상에 기인하여 재료 구조에 대한 깊은 변화가 수반되지 않기 때문에 장치 신뢰성에 도움이 된다는 것입니다.

탄소나노튜브 멤리스터

2013년 Ageev, Blinov 등은 [78]CNT의 다발을 스캔 터널링 현미경으로 연구하는 수직 정렬 탄소나노튜브를 기반으로 구조 내 멤리스터 효과를 관찰했다고 보고했습니다.

이후 나노튜브가 불균일한 탄성변형률 δL0을 가질 때 CNT 멤리스티브 스위칭이 관찰됨을 알 수 있었습니다.변형된 сNT의 멤리스티브 스위칭 메커니즘은 외부 전기장 E(x,t)의 영향 하에 나노튜브에서 불균일한 탄성 변형률과 압전장 Edef의 형성 및 후속 재배분에 기초함을 보여주었습니다.

생체분자막

생체 재료는 인공 시냅스에 사용하기 위해 평가되었으며 뉴로모픽 시스템에 적용 가능성을 보여주었습니다.[80]특히, 콜라겐 ‐ 기반의 바이오엠리스터를 인공 시냅스 소자로 이용할 수 있는 가능성이 검토된 바,반면에, 리그닌에 기초한 시냅스 소자는 전압의[82] 부호에 따라 연속적인 전압 스위프로 전류의 상승 또는 하강을 나타냈고, 또한 천연 실크 피브로인은 멤리스티브 특성을 나타냈고,[83] 생체분자에 기초한 스핀 멤리스티브 시스템 또한 연구되고 있습니다.[84]

2012년, Sandro Carara와 공동 저자들은 매우 민감한 바이오 센서를 실현하기 위한 목적으로 최초의 생체 분자 멤리스터를 제안했습니다.[85]그 후, 몇몇 멤리스티브 센서들이 증명되었습니다.[86]

스핀 멤리스티브 시스템

스핀트로닉 멤리스터

디스크 드라이브 제조업체인 Seagate Technology의 연구원인 Chen과 Wang은 자기 멤리스터의 세 가지 예를 설명했습니다.[87]한 소자 저항은 소자의 한 구간에서 전자의 스핀이 다른 구간의 스핀과 다른 방향을 가리키면서 두 구간 사이의 경계인 "영역 벽"을 생성할 때 발생합니다.전자 장치에 유입되는 전자는 일정한 스핀을 가지며, 이는 장치의 자화 상태를 바꿉니다.자화를 변경하면 도메인 벽이 이동하고 저항이 변경됩니다.이 작업의 중요성은 IEEE Spectrum의 인터뷰로 이어졌습니다.[88]자기터널접합에서 스핀전류에 의한 도메인 벽운동에 기초한 스핀트로닉 멤리스터의 첫 번째 실험적 증명은 2011년에 제시되었습니다.[89]

자기터널접합에서의 멤저항

자기 터널 접합은 외재적(redox 반응, 전하 포획/탈래핑 및 장벽 내에서의 전자 이동)과 내재적(spin-transfer torque) 모두의 잠재적으로 상호보완적인 메커니즘을 통해 멤리스터로 작동하도록 제안되었습니다.

외인성 메커니즘

1999년과 2003년 사이에 수행된 연구에 기초하여, Bowen 등은 2006년에 쌍안정 스핀 의존 상태[90](저항 스위칭)를 부여받은 자기 터널 접합(MTJ)에 대한 실험을 발표했습니다.MTJ는 반금속 산화물 LSMO와 강자성 금속 CoCr 전극을 분리하는 SrTiO3(STO) 터널 장벽으로 구성됩니다.전극 자화의 평행 또는 반평행 정렬을 특징으로 하는 MTJ의 통상적인 두 디바이스 저항 상태는 전기장을 적용하여 변경됩니다.CoCr에서 LSMO 전극으로 전기장을 인가하면 터널 자기저항(TMR) 비율이 양입니다.전기장의 방향이 반대일 때, TMR은 음이 됩니다.두 경우 모두 30% 정도의 큰 폭의 TMR이 발견됩니다.반금속 LSMO 전극에서 완전한 스핀 분극 전류가 흐르기 때문에 줄리에르 모델 내에서 이러한 부호 변화는 STO/CoCr 인터페이스의 유효 스핀 분극의 부호 변화를 시사합니다.이 다중 상태 효과의 기원은 관찰된 Cr의 장벽 내 이동과 그것의 산화 상태에 있습니다.TMR의 부호 변화는 상태의 STO/CoCr 인터페이스 밀도에 대한 수정과 CrOx 산화환원 반응에 의해 유도된 STO/CoCr 인터페이스의 터널링 풍경에 대한 변경에서 비롯될 수 있습니다.

MgO 기반 MTJ 내 MgO 기반 멤리스티브 스위칭에 대한 보고서는 2008년과[91] 2009년부터 등장했습니다.[92]관찰된 멤리스티브 효과를 설명하기 위해 절연 MgO 층 내의 산소공극의 드리프트(drift)가 제안되었지만, 또 다른 설명은 산소공극의[93] 국부적인 상태와[94] 스핀트로닉스에 미치는 영향에 대한 전하 트래핑/디트래핑([92]charge trapping/detrapping)일 수 있습니다.이는 강유전성[95] 또는 다중강성과 같은 고유한 특성을 가진 복합 산화물을 배치하는 장치의 멤리스티브 작동에서 산소 빈자리가 어떤 역할을 하는지를 이해하는 것의 중요성을 강조합니다.[96]

고유기전

MTJ의 자화 상태는 스핀 전달 토크에 의해 제어될 수 있으며, 따라서 이러한 고유한 물리적 메커니즘을 통해 멤리스티브 동작을 나타낼 수 있습니다.이 스핀 토크는 전류가 접점을 통해 흐르는 것에 의해 유도되며, MRAM을 달성하는 효율적인 수단으로 이어집니다.그러나 전류가 접점을 통과하는 시간의 길이에 따라 필요한 전류의 양이 결정됩니다. 즉, 전하가 핵심 변수입니다.[97]

고유(스핀-전달 토크) 및 외부(저항 스위칭) 메커니즘의 조합은 자연스럽게 상태 벡터 x = (x,x)에 의해 설명되는 2차 멤리스티브 시스템으로 이어지는데, 여기서 x는 전극의 자기 상태를 설명하고 x는 MgO 장벽의 저항 상태를 나타냅니다.이 경우 x의1 변화는 전류 제어(스핀 토크는 높은 전류 밀도에 기인함)되는 반면 x의2 변화는 전압 제어(산소 공실의 드리프트는 높은 전기장에 기인함)됩니다.멤리스티브 자기 터널 접합에서 두 효과의 존재는 나노스코픽 시냅스-신경계 시스템의 아이디어로 이어졌습니다.[98]

스핀 멤리스티브 시스템

Pershin과 Di Ventra는 멤리스티브 행동에 대한 근본적으로 다른 메커니즘을 제안했습니다.[99][100]저자들은 특정 유형의 반도체 스핀트로닉 구조가 Chua와 Kang에 의해 정의된 광범위한 종류의 멤리스티브 시스템에 속한다는 것을 보여줍니다.[2]이러한 구조에서 멤리스티브 거동의 메커니즘은 전적으로 나노 구조에서 이온 수송보다 더 편리한 제어를 가능하게 하는 전자 스핀 자유도에 기반을 두고 있습니다.외부 제어 파라미터(전압 등)가 변경되면 히스테리시스를 일으키는 확산 및 이완 과정 때문에 전자 스핀 분극의 조정이 지연됩니다.이 결과는 반도체/강자석 인터페이스에서의 스핀 추출 연구에서 예상되었지만 [101]멤리스티브 거동 측면에서는 설명되지 않았습니다.짧은 시간 척도에서 이들 구조는 거의 이상적인 멤리스터로 동작합니다.[1]이 결과는 반도체 스핀트로닉스의 적용 가능 범위를 넓히고 향후 실용적인 적용 분야에서 한 단계 발전하게 됩니다.

자기지향 채널 멤리스터

2017년 크리스 캠벨은 SDC([102]Self-Directed Channel) 멤리스터를 공식적으로 선보였습니다.SDC 장치는 전 세계 연구원, 학생 및 전자 제품 애호가들이 상업적으로 이용할 수 있는 최초의 멤리스티브 장치입니다.[103]SDC 장치는 제작 즉시 작동합니다.GeSe23 활성층에서 Ge-Ge 호모폴라 결합이 발견되고 스위칭이 발생합니다.상부 텅스텐 전극 바로 아래에 있는 GeSe23/Ag/GeSe로23 구성된 세 개의 층은 증착 동안 함께 섞이고 은-소스 층을 공동으로 형성합니다.SnSe 계층은 은 소스 계층이 활성 계층과 직접적으로 접촉하지 않도록 이 두 계층 사이에 있습니다.은이 고온에서 활성층으로 이동하지 않고 활성층이 약 350 °C(662 °F)의 높은 유리 전이 온도를 유지하므로 장치의 가공 및 작동 온도는 각각 250 °C(482 °F)와 최소 150 °C(302 °F)에서 상당히 높습니다.이러한 가공 및 작동 온도는 대부분의 이온 전도성 칼코게나이드 장치 유형(예를 들어, 광도핑 또는 열적 어닐링이 필요한 S 기반 안경(GeS)을 포함)보다 높습니다.이러한 요인을 통해 SDC 장치는 150°C(302°F)에서 장기간 연속 작동하는 등 광범위한 온도에서 작동할 수 있습니다.

잠재적인 응용프로그램

멤리스터는 아직 상업적인 응용을 얻기에는 부족한 숫자로 만들어졌으므로 실험실의 호기심으로 남아 있습니다.이러한 대량 가용성 부족에도 불구하고 Allied Market Research에 따르면 멤리스터 시장은 2015년 320만 달러 규모였으며 2022년에는 79.0만 달러 규모가 될 것이라고 합니다.[104]

멤리스터의 잠재적인 응용은 초전도 양자 컴퓨터를 위한 아날로그 메모리에 있습니다.[12]

멤리스터는 잠재적으로 비휘발성 솔리드 스테이트 메모리로 변형될 수 있으며, 이는 DRAM과 액세스 시간이 비슷한 하드 드라이브보다 데이터 밀도를 높여 두 구성 요소를 모두 대체할 수 있습니다.[31]HP는 평방 센티미터에 100기가비트가 들어갈 수 있는 크로스바 래치 메모리를 시제품으로 제작하고 [105]확장 가능한 3D 설계(최대 1000층 또는 cm당3 1페타비트로 구성)를 제안했습니다.[106]2008년 5월, HP는 자사의 장치가 현재 DRAM 속도의 약 10분의 1에 달한다고 보고했습니다.[107]저장된 값이 영향을 받지 않도록 교류 전류로 장치의 저항을 읽습니다.[108]2012년 5월에는 액세스 시간이 90나노초로 향상되었으며, 이는 동시대 플래시 메모리보다 거의 100배 빠른 속도입니다.동시에 에너지 소비량은 플래시 메모리에서 소비되는 에너지의 1%에 불과했습니다.[109]

멤리스터는 프로그래밍 가능한[110] 논리 신호 처리,[111] 초해상도 이미징[112] 물리적 신경망,[113] 제어 시스템,[114] 재구성 가능 컴퓨팅,[115] 메모리 내 컴퓨팅,[116] 뇌-컴퓨터 인터페이스[117] 및 RFID에 응용됩니다.[118]멤리스티브 장치는 CMOS 기반 논리 계산을[119] 대체할 수 있는 상태 저장 논리 암시를 위해 잠재적으로 사용됩니다. 이 방향으로 여러 초기 작업이 보고되었습니다.[120][121]

2009년에는 LC 네트워크와 멤리스터로 구성된 간단한 전자회로를[122] 사용하여 단세포 생물의 적응 행동에 대한 실험을 모델링했습니다.[123]일련의 주기적인 펄스에 따라 회로는 세포질 내 채널의 점도가 주기적인 환경에 반응하는 슬라임 주형 Physarum polycephalum의 거동과 유사한 다음 펄스를 학습하고 예측하는 것으로 나타났습니다.[123]그러한 회로들의 응용들은 예를 들어, 패턴 인식을 포함할 수 있습니다.DARPA SyNAPSE 프로젝트는 HP Labs에 자금을 지원하고 보스턴 대학교 뉴로모픽 랩과 협력하여 멤리스티브 시스템을 기반으로 할 수 있는 뉴로모픽 아키텍처를 개발해 왔습니다.2010년, Versace와 Chandler는 MoNETA(Modular Neural Exploring Traveling Agent) 모델을 설명했습니다.[124]MoNETA는 멤리스티브 하드웨어를 사용하여 가상 및 로봇 에이전트에 전력을 공급하기 위해 전뇌 회로를 구현한 최초의 대규모 신경망 모델입니다.[125]Merrikh-Bayat와 Shouraki는 아날로그 소프트 컴퓨팅 시스템의 구축에서 멤리스터 크로스바 구조의 적용을 증명했습니다.[126]2011년, 그들은 멤리스터 크로스바가 퍼지 논리와 어떻게 결합되어 퍼지 입출력 단자를 갖는 아날로그 멤리스티브 신경-퍼지 컴퓨팅 시스템을 만들 수 있는지[127] 보여주었습니다.학습은 Hebbian 학습 규칙에서 영감을 받은 퍼지 관계의 생성을 기반으로 합니다.

2013년에 Leon Chua는 멤리스터가 포괄하는 광범위한 복잡한 현상과 응용 프로그램을 설명하고 어떻게 그것들이 비휘발성 아날로그 메모리로 사용되고 고전적인 습관화 및 학습 현상을 모방할 수 있는지를 설명하는 튜토리얼을 발표했습니다.[128]

파생 장치

멤리스터 및 멤트랜지스터

멤리스터와 멤트랜지스터는 멤리스터 기능을 포함하는 트랜지스터 기반 소자입니다.

멤캐패시터 및 멤인덕터

2009년, 디 벤트라(Di Ventra), 퍼신(Pershin), 추아(Chua)는 멤리스티브 시스템의 개념을 멤캐패시터(memcapacitor)와 메민터(meminductor) 형태의 정전용량 및 유도소자(inductive element)로 확장하였으며[129], 이들의 특성은 시스템의 상태와 이력에 따라 달라지며, 2013년 디 벤트라(Di Ventra)와 퍼신(Pershin)에 의해 더욱 확장되었습니다.[22]

멤프랙턴스 및 멤프랙터, 2차 및 3차 멤리스터, 멤캐패시터 및 멤프랙터

2014년 9월, 모하메드-살라 압델루아합(Mohammed-Salah Abdelouahab), 르네 로지(Rene Lozi), 레온 추아(Leon Chua)는 분수 도함수를 이용한 1차, 2차, 3차, n차 멤리스티브 요소의 일반 이론을 발표하였다.[130]

역사

전구물질

험프리 데이비 경은 멤리스터 효과로 설명될 수 있는 최초의 실험을 1808년 전에 수행했다고 합니다.[20][131]그러나 구성된 관련된 성질의 최초의 장치는 1960년에 버나드 위드로우가 ADALIN이라고 불리는 초기 인공 신경망의 회로 소자를 설명하기 위해 만든 용어인 멤리스터(즉, 메모리 저항기)였습니다. 몇 년 후, 1968년에,Argall은 후에 Hewlett Packard의 연구자들에 의해 멤리스터의 증거라고 주장된 TiO의2 저항 전환 효과를 보여주는 기사를 출판했습니다.[55][citation needed]

이론서술

Leon Chua는 1971년에 그의 새로운 2단자 회로 소자를 가정했습니다.제4의 기본 회로 소자로서 전하와 플럭스 링키지의 관계를 가지는 것을 특징으로 합니다.[1]5년 후 그와 그의 제자 강성모는 전류 대 전압 거동을 특징짓는 리사쥬 곡선의 영 교차 특성을 포함한 멤리스터와 멤리스티브 시스템 이론을 일반화했습니다.[2]

21세기

2008년 5월 1일, Strukov, Snider, Stewart, 그리고 Williams는 Nature지에 나노스케일 시스템에서 발견되는 2단자 저항 전환 행동과 멤리스터 사이의 연관성을 확인하는 기사를 실었습니다.[17]

2009년 1월 23일, 디 벤트라, 퍼신, 추아는 멤리스티브 시스템의 개념을 시스템의 상태와 역사에 따라 특성이 달라지는 축전기와 유도기로 확장했습니다.[129]

2014년 7월, MeMOSAT/LabOSAT 그룹[132](아르헨티나 국립대학교(Universidad Nacional de General San Martín), INTI, CNEA, CONICET 연구원들로 구성됨)은 기억 장치를 지구 저궤도에 올려놓았습니다.[133]그 이후로, 7개의 다른[134] 장치를 가진 미션들이 Satellogic의 Nu-Sat 위성을 타고 낮은 궤도에서 실험을 수행하고 있습니다.[135][136][clarification needed]

2015년 7월 7일, Knowm Inc.는 SDC(Self Directed Channel) 멤버리스터를 상업적으로 발표했습니다.[137]이 장치들은 여전히 적은 숫자로 사용할 수 있습니다.

2018년 7월 13일 멤리스터 평가 페이로드를 비행하기 위해 멤리스터 위성이 발사되었습니다.[138]

2021년, MIT의 제니퍼 루프(Jennifer Rupp)와 마틴 바잔트(Martin Bazant)는 뉴로모픽 컴퓨팅의 리튬 산화물 기반 멤리스터를 포함하여 배터리 전극에서 사용할 수 없는 리튬의 응용 분야를 조사하기 위한 "Lithionics" 연구 프로그램을 시작했습니다.[139][140]

참고 항목

참고문헌

- ^ a b c d e Chua, L. (1971). "Memristor-The missing circuit element". IEEE Transactions on Circuit Theory. 18 (5): 507–519. CiteSeerX 10.1.1.189.3614. doi:10.1109/TCT.1971.1083337.

- ^ a b c d e Chua, L. O.; Kang, S. M. (1976-01-01), "Memristive devices and systems", Proceedings of the IEEE, 64 (2): 209–223, doi:10.1109/PROC.1976.10092, S2CID 6008332

- ^ a b c d Pershin, Y. V.; Di Ventra, M. (2019). "A simple test for ideal memristors". Journal of Physics D: Applied Physics. 52 (1): 01LT01. arXiv:1806.07360. Bibcode:2019JPhD...52aLT01P. doi:10.1088/1361-6463/aae680. S2CID 53506924.

- ^ a b Kim, J.; Pershin, Y. V.; Yin, M.; Datta, T.; Di Ventra, M. (2019). "An experimental proof that resistance-switching memories are not memristors". Advanced Electronic Materials. arXiv:1909.07238. doi:10.1002/aelm.202000010. S2CID 202577242.

- ^ Knoepfel, H. (1970), Pulsed high magnetic fields, New York: North-Holland, p. 37, Eq. (2.80)

- ^ a b Muthuswamy, Bharathwaj; Banerjee, Santo (2019). Introduction to Nonlinear Circuits and Networks. Springer International. ISBN 978-3-319-67325-7.

- ^ Paul L. Penfield Jr. (1974). "1. Frequency-Power Formulas for Josephson Junctions". V. Microwave and Millimeter Wave Techniques (PDF) (Report). pp. 31–32. QPR No. 113.

- ^ Langenberg, D. N. (1974), "Physical Interpretation of the term and implications for detectors" (PDF), Revue de Physique Appliquée, 9: 35–40, doi:10.1051/rphysap:019740090103500

- ^ Pedersen, N.F.; et al. (1972), "Magnetic field dependence and Q of the Josephson plasma resonance" (PDF), Physical Review B, 11 (6): 4151–4159, Bibcode:1972PhRvB...6.4151P, doi:10.1103/PhysRevB.6.4151

- ^ Pedersen, N. F.; Finnegan, T. F.; Langenberg, D. N. (1974). "Evidence for the Existence of the Josephson Quasiparticle-Pair Interference Current". Low Temperature Physics-LT 13. Boston, MA: Springer US. pp. 268–271. doi:10.1007/978-1-4684-2688-5_52. ISBN 978-1-4684-2690-8.

- ^ Thompson, E.D. (1973), "Power flow for Josephson Elements", IEEE Trans. Electron Devices, 20 (8): 680–683, Bibcode:1973ITED...20..680T, doi:10.1109/T-ED.1973.17728

- ^ a b Peotta, A.; Di Ventra, M. (2014), "Superconducting Memristors", Physical Review Applied, 2 (3): 034011-1–034011-10, arXiv:1311.2975, Bibcode:2014PhRvP...2c4011P, doi:10.1103/PhysRevApplied.2.034011, S2CID 119020953

- ^ Muthuswamy, B.; Jevtic, J.; Iu, H. H. C.; Subramaniam, C. K.; Ganesan, K.; Sankaranarayanan, V.; Sethupathi, K.; Kim, H.; Shah, M. Pd.; Chua, L. O. (2014). "Memristor modelling". 2014 IEEE International Symposium on Circuits and Systems (ISCAS). pp. 490–493. doi:10.1109/ISCAS.2014.6865179. ISBN 978-1-4799-3432-4. S2CID 13061426.

- ^ a b Sah, M.; et al. (2015), "A Generic Model of Memristors with Parasitic Components", IEEE TCAS I: Regular Papers, 62 (3): 891–898

- ^ Chua, L. O.; Tseng, C. (1974), "A memristive circuit model for p-n junction diodes", International Journal of Circuit Theory and Applications, 2 (4): 367–389, doi:10.1002/cta.4490020406

- ^ a b c d Chua, Leon (2011-01-28). "Resistance switching memories are memristors". Applied Physics A. 102 (4): 765–783. Bibcode:2011ApPhA.102..765C. doi:10.1007/s00339-011-6264-9.

- ^ a b c d e f g Strukov, Dmitri B.; Snider, Gregory S.; Stewart, Duncan R.; Williams, R. Stanley (2008). "The missing memristor found" (PDF). Nature. 453 (7191): 80–83. Bibcode:2008Natur.453...80S. doi:10.1038/nature06932. PMID 18451858. S2CID 4367148.

- ^ Memristor FAQ, Hewlett-Packard, retrieved 2010-09-03

- ^ Williams, R. S. (2008). "How We Found The Missing Memristor" (PDF). IEEE Spectrum. 45 (12): 28–35. doi:10.1109/MSPEC.2008.4687366. S2CID 27319894.

- ^ a b Clarke, P. (2012-05-23), "Memristor is 200 years old, say academics", EE Times, retrieved 2012-05-25

- ^ a b c d Meuffels, P.; Soni, R. (2012). "Fundamental Issues and Problems in the Realization of Memristors". arXiv:1207.7319 [cond-mat.mes-hall].

- ^ a b c d e f g Di Ventra, M.; Pershin, Y. V. (2013), "On the physical properties of memristive, memcapacitive and meminductive systems", Nanotechnology, 24 (25): 255201, arXiv:1302.7063, Bibcode:2013Nanot..24y5201D, CiteSeerX 10.1.1.745.8657, doi:10.1088/0957-4484/24/25/255201, PMID 23708238, S2CID 14892809

- ^ Sundqvist, Kyle M.; Ferry, David K.; Kish, Laszlo B. (2017-11-21). "Memristor Equations: Incomplete Physics and Undefined Passivity/Activity". Fluctuation and Noise Letters. 16 (4): 1771001–519. arXiv:1703.09064. Bibcode:2017FNL....1671001S. doi:10.1142/S0219477517710018. S2CID 1408810.

- ^ Abraham, Isaac (2018-07-20). "The case for rejecting the memristor as a fundamental circuit element". Scientific Reports. 8 (1): 10972. Bibcode:2018NatSR...810972A. doi:10.1038/s41598-018-29394-7. PMC 6054652. PMID 30030498.

- ^ a b c d e Valov, I.; et al. (2013), "Nanobatteries in redox-based resistive switches require extension of memristor theory", Nature Communications, 4 (4): 1771, arXiv:1303.2589, Bibcode:2013NatCo...4.1771V, doi:10.1038/ncomms2784, PMC 3644102, PMID 23612312

- ^ Marks, P. (2008-04-30), "Engineers find 'missing link' of electronics", New Scientist, retrieved 2008-04-30

- ^ Zidan, Mohammed A.; Strachan, John Paul; Lu, Wei D. (2018-01-08). "The future of electronics based on memristive systems". Nature Electronics. 1 (1): 22–29. doi:10.1038/s41928-017-0006-8. S2CID 187510377.

- ^ HP 100TB Memristor drives by 2018 – if you're lucky, admits tech titan, 2013-11-01

- ^ Artificial synapses could lead to advanced computer memory and machines that mimic biological brains, HRL Laboratories, 2012-03-23, retrieved 2012-03-30

- ^ Bush, S. (2008-05-02), "HP nano device implements memristor", Electronics Weekly

- ^ a b Kanellos, M. (2008-04-30), "HP makes memory from a once theoretical circuit", CNET News, retrieved 2008-04-30

- ^ Mellor, C. (2011-10-10), "HP and Hynix to produce the memristor goods by 2013", The Register, retrieved 2012-03-07

- ^ Courtland, R. (2011-04-01). "Memristors...Made of Blood?". IEEE Spectrum. Retrieved 2012-03-07.

- ^ Johnsen, G. K. (2011-03-24). "Memristive model of electro-osmosis in skin". Physical Review E. 83 (3): 031916. Bibcode:2011PhRvE..83c1916J. doi:10.1103/PhysRevE.83.031916. PMID 21517534. S2CID 46437206.

- ^ McAlpine, K. (2011-03-02), "Sweat ducts make skin a memristor", New Scientist, 209 (2802): 16, Bibcode:2011NewSc.209...16M, doi:10.1016/S0262-4079(11)60481-8, retrieved 2012-03-07

- ^ a b Clarke, P. (2012-01-16), "Memristor brouhaha bubbles under", EETimes, retrieved 2012-03-02

- ^ a b Marks, P. (2012-02-23), "Online spat over who joins memristor club", New Scientist, retrieved 2012-03-19

- ^ Meuffels, P.; Schroeder, H. (2011), "Comment on "Exponential ionic drift: fast switching and low volatility of thin-film memristors" by D. B. Strukov and R. S. Williams in Appl. Phys. A (2009) 94: 515–519", Applied Physics A, 105 (1): 65–67, Bibcode:2011ApPhA.105...65M, doi:10.1007/s00339-011-6578-7, S2CID 95168959

- ^ a b Kish, Laszlo B.; Granqvist, Claes G.; Khatri, Sunil P.; Wen, He (2014). "Demons: Maxwell's demon, Szilard's engine and Landauer's erasure–dissipation". International Journal of Modern Physics: Conference Series. 33: 1460364. arXiv:1412.2166. Bibcode:2014IJMPS..3360364K. doi:10.1142/s2010194514603640. S2CID 44851287.

- ^ Kish, L. B.; Khatri, S. P.; Granqvist, C. G.; Smulko, J. M. (2015). "Critical remarks on Landauer's principle of erasure-dissipation: Including notes on Maxwell demons and Szilard engines". 2015 International Conference on Noise and Fluctuations (ICNF). pp. 1–4. doi:10.1109/ICNF.2015.7288632. ISBN 978-1-4673-8335-6.

- ^ Slipko, V. A.; Pershin, Y. V.; Di Ventra, M. (2013), "Changing the state of a memristive system with white noise", Physical Review E, 87 (1): 042103, arXiv:1209.4103, Bibcode:2013PhRvE..87a2103L, doi:10.1103/PhysRevE.87.012103, PMID 23410279, S2CID 2237458

- ^ Hashem, N.; Das, S. (2012), "Switching-time analysis of binary-oxide memristors via a non-linear model" (PDF), Applied Physics Letters, 100 (26): 262106, Bibcode:2012ApPhL.100z2106H, doi:10.1063/1.4726421, retrieved 2012-08-09

- ^ Linn, E.; Siemon, A.; Waser, R.; Menzel, S. (2014-03-23). "Applicability of Well-Established Memristive Models for Simulations of Resistive Switching Devices". IEEE Transactions on Circuits and Systems I: Regular Papers. 61 (8): 2402–2410. arXiv:1403.5801. Bibcode:2014arXiv1403.5801L. doi:10.1109/TCSI.2014.2332261. S2CID 18673562.

- ^ Garling, C. (2012-07-25), "Wonks question HP's claim to computer-memory missing link", Wired.com, retrieved 2012-09-23

- ^ Chua, L. (2012-06-13), Memristors: Past, Present and future (PDF), archived from the original (PDF) on 2014-03-08, retrieved 2013-01-12

- ^ Adhikari, S. P.; Sah, M. P.; Hyongsuk, K.; Chua, L. O. (2013), "Three Fingerprints of Memristor", IEEE Transactions on Circuits and Systems I, 60 (11): 3008–3021, doi:10.1109/TCSI.2013.2256171, S2CID 12665998

- ^ Pershin, Y. V.; Di Ventra, M. (2011), "Memory effects in complex materials and nanoscale systems", Advances in Physics, 60 (2): 145–227, arXiv:1011.3053, Bibcode:2011AdPhy..60..145P, doi:10.1080/00018732.2010.544961, S2CID 119098973

- ^ Biolek, D.; Biolek, Z.; Biolkova, V. (2011), "Pinched hysteresis loops of ideal memristors, memcapacitors and meminductors must be 'self-crossing'", Electronics Letters, 47 (25): 1385–1387, Bibcode:2011ElL....47.1385B, doi:10.1049/el.2011.2913

- ^ Caravelli; et al. (2017). "The complex dynamics of memristive circuits: analytical results and universal slow relaxation". Physical Review E. 95 (2): 022140. arXiv:1608.08651. Bibcode:2017PhRvE..95b2140C. doi:10.1103/PhysRevE.95.022140. PMID 28297937. S2CID 6758362.

- ^ Caravelli; et al. (2021). "Global minimization via classical tunnelling assisted by collective force field formation". Science Advances. 7 (52): 022140. arXiv:1608.08651. Bibcode:2021SciA....7.1542C. doi:10.1126/sciadv.abh1542. PMID 28297937. S2CID 231847346.

- ^ Mouttet, B. (2012). "Memresistors and non-memristive zero-crossing hysteresis curves". arXiv:1201.2626 [cond-mat.mes-hall].

- ^ Fildes, J. (2007-11-13), Getting More from Moore's Law, BBC News, retrieved 2008-04-30

- ^ Taylor, A. G. (2007), "Nanotechnology in the Northwest" (PDF), Bulletin for Electrical and Electronic Engineers of Oregon, 51 (1): 1

- ^ Stanley Williams, HP Labs, archived from the original on 2011-07-19, retrieved 2011-03-20

- ^ a b Argall, F. (1968), "Switching Phenomena in Titanium Oxide Thin Films", Solid-State Electronics, 11 (5): 535–541, Bibcode:1968SSEle..11..535A, doi:10.1016/0038-1101(68)90092-0

- ^ Terabe, K.; Hasegawa, T.; Liang, C.; Aono, M. (2007), "Control of local ion transport to create unique functional nanodevices based on ionic conductors", Science and Technology of Advanced Materials, 8 (6): 536–542, Bibcode:2007STAdM...8..536T, doi:10.1016/j.stam.2007.08.002

- ^ Beck, A.; et al. (2000), "Reproducible switching effect in thin oxide films for memory applications", Applied Physics Letters, 77 (1): 139, Bibcode:2000ApPhL..77..139B, doi:10.1063/1.126902

- ^ 스테파노비치, 겐리크; 조, 충래; 유인경; 이, 은홍; 조, 성일; 문, 창욱(2006) "2 이상의 산화물층을 갖는 전극 구조체 및 이를 갖는 비휘발성 메모리 소자" 미국 특허 7,417,271

- ^ Finding the Missing Memristor - R. Stanley Williams

- ^ Markoff, J. (2010-04-07), "H.P. Sees a Revolution in Memory Chip", New York Times

- ^ Kavehei, O.; Iqbal, A.; Kim, Y.S.; Eshraghian, K.; Al-Sarawi, S. F.; Abbott, D. (2010). "The fourth element: characteristics, modelling and electromagnetic theory of the memristor". Proceedings of the Royal Society A: Mathematical, Physical and Engineering Sciences. 466 (2120): 2175–2202. arXiv:1002.3210. Bibcode:2010RSPSA.466.2175K. doi:10.1098/rspa.2009.0553. S2CID 7625839.

- ^ Ben-Jamaa, M. H.; Carrara, S.; Georgiou, J.; Archontas, N.; De Micheli, G. (2009), "Fabrication of memristors with poly-crystalline silicon nanowires", Proceedings of 9th IEEE Conference on Nanotechnology, 1 (1): 152–154

- ^ Mehonic, A.; Cueff, S.; Wojdak, M. , …; Kenyon, A. J. (2012). "Resistive switching in silicon suboxide films" (PDF). Journal of Applied Physics. 111 (7): 074507–074507–9. Bibcode:2012JAP...111g4507M. doi:10.1063/1.3701581.

{{cite journal}}: CS1 유지 : 여러 이름 : 저자 목록 (링크) - ^ Krieger, J. H.; Spitzer, S. M. (2004), "Non-traditional, Non-volatile Memory Based on Switching and Retention Phenomena in Polymeric Thin Films", Proceedings of the 2004 Non-Volatile Memory Technology Symposium, IEEE, p. 121, doi:10.1109/NVMT.2004.1380823, ISBN 978-0-7803-8726-3, S2CID 7189710

- ^ Erokhin, V.; Fontana, M. P. (2008). "Electrochemically controlled polymeric device: A memristor (and more) found two years ago". arXiv:0807.0333 [cond-mat.soft].

- ^ An; Alibart, F.; Pleutin, S.; Guerin, D.; Novembre, C.; Lenfant, S.; Lmimouni, K.; Gamrat, C.; Vuillaume, D. (2010). "An Organic Nanoparticle Transistor Behaving as a Biological Spiking Synapse". Advanced Functional Materials. 20 (2): 330–337. arXiv:0907.2540. doi:10.1002/adfm.200901335. S2CID 16335153.

- ^ Alibart, F.; Pleutin, S.; Bichler, O.; Gamrat, C.; Serrano-Gotarredona, T.; Linares-Barranco, B.; Vuillaume, D. (2012). "A Memristive Nanoparticle/Organic Hybrid Synapstor for Neuroinspired Computing". Advanced Functional Materials. 22 (3): 609–616. arXiv:1112.3138. doi:10.1002/adfm.201101935. hdl:10261/83537. S2CID 18687826.

- ^ Pavlov's; Transistors, Organic; Bichler, O.; Zhao, W.; Alibart, F.; Pleutin, S.; Lenfant, S.; Vuillaume, D.; Gamrat, C. (2013). "Pavlov's Dog Associative Learning Demonstrated on Synaptic-Like Organic Transistors". Neural Computation. 25 (2): 549–566. arXiv:1302.3261. Bibcode:2013arXiv1302.3261B. doi:10.1162/NECO_a_00377. PMID 22970878. S2CID 16972302.

- ^ Crupi, M.; Pradhan, L.; Tozer, S. (2012), "Modelling Neural Plasticity with Memristors" (PDF), IEEE Canadian Review, 68: 10–14

- ^ Erokhin, V.; Berzina, T.; Gorshkov, K.; Camorani, P.; Pucci, A.; Ricci, L.; Ruggeri, G.; Signala, R.; Schüz, A. (2012). "Stochastic hybrid 3D matrix: learning and adaptation of electrical properties". Journal of Materials Chemistry. 22 (43): 22881. doi:10.1039/C2JM35064E.

- ^ Bessonov, A. A.; et al. (2014), "Layered memristive and memcapacitive switches for printable electronics", Nature Materials, 14 (2): 199–204, Bibcode:2015NatMa..14..199B, doi:10.1038/nmat4135, PMID 25384168

- ^ Ge, Ruijing; Wu, Xiaohan; Kim, Myungsoo; Shi, Jianping; Sonde, Sushant; Tao, Li; Zhang, Yanfeng; Lee, Jack C.; Akinwande, Deji (2017-12-19). "Atomristor: Nonvolatile Resistance Switching in Atomic Sheets of Transition Metal Dichalcogenides". Nano Letters. 18 (1): 434–441. Bibcode:2018NanoL..18..434G. doi:10.1021/acs.nanolett.7b04342. PMID 29236504.

- ^ Wu, Xiaohan; Ge, Ruijing; Chen, Po‐An; Chou, Harry; Zhang, Zhepeng; Zhang, Yanfeng; Banerjee, Sanjay; Chiang, Meng‐Hsueh; Lee, Jack C.; Akinwande, Deji (April 2019). "Thinnest Nonvolatile Memory Based on Monolayer h‐BN". Advanced Materials. 31 (15): 1806790. Bibcode:2019AdM....3106790W. doi:10.1002/adma.201806790. PMID 30773734. S2CID 73505661.

- ^ Kim, Myungsoo; Ge, Ruijing; Wu, Xiaohan; Lan, Xing; Tice, Jesse; Lee, Jack C.; Akinwande, Deji (2018). "Zero-static power radio-frequency switches based on MoS2 atomristors". Nature Communications. 9 (1): 2524. Bibcode:2018NatCo...9.2524K. doi:10.1038/s41467-018-04934-x. PMC 6023925. PMID 29955064.

- ^ "Towards zero-power 6G communication switches using atomic sheets". Nature Electronics. 5 (6): 331–332. June 2022. doi:10.1038/s41928-022-00767-1. S2CID 249221166.

- ^ Hus, Saban M.; Ge, Ruijing; Chen, Po-An; Liang, Liangbo; Donnelly, Gavin E.; Ko, Wonhee; Huang, Fumin; Chiang, Meng-Hsueh; Li, An-Ping; Akinwande, Deji (January 2021). "Observation of single-defect memristor in an MoS2 atomic sheet". Nature Nanotechnology. 16 (1): 58–62. Bibcode:2021NatNa..16...58H. doi:10.1038/s41565-020-00789-w. PMID 33169008. S2CID 226285710.

- ^ Chanthbouala, A.; et al. (2012), "A ferroelectric memristor", Nature Materials, 11 (10): 860–864, arXiv:1206.3397, Bibcode:2012NatMa..11..860C, doi:10.1038/nmat3415, PMID 22983431, S2CID 10372470

- ^ Ageev, O. A.; Blinov, Yu F.; Il’in, O. I.; Kolomiitsev, A. S.; Konoplev, B. G.; Rubashkina, M. V.; Smirnov, V. A.; Fedotov, A. A. (2013-12-11). "Memristor effect on bundles of vertically aligned carbon nanotubes tested by scanning tunnel microscopy". Technical Physics. 58 (12): 1831–1836. Bibcode:2013JTePh..58.1831A. doi:10.1134/S1063784213120025. S2CID 53003312.

- ^ Il'ina, Marina V.; Il'in, Oleg I.; Blinov, Yuriy F.; Smirnov, Vladimir A.; Kolomiytsev, Alexey S.; Fedotov, Alexander A.; Konoplev, Boris G.; Ageev, Oleg A. (October 2017). "Memristive switching mechanism of vertically aligned carbon nanotubes". Carbon. 123: 514–524. doi:10.1016/j.carbon.2017.07.090.

- ^ Park, Youngjun; Kim, Min-Kyu; Lee, Jang-Sik (2020-07-16). "Emerging memory devices for artificial synapses". Journal of Materials Chemistry C. 8 (27): 9163–9183. doi:10.1039/D0TC01500H. S2CID 219912115.

- ^ Raeis‐Hosseini, Niloufar; Park, Youngjun; Lee, Jang-Sik (2018). "Flexible Artificial Synaptic Devices Based on Collagen from Fish Protein with Spike-Timing-Dependent Plasticity". Advanced Functional Materials. 28 (31): 1800553. doi:10.1002/adfm.201800553. S2CID 104277945.

- ^ Park, Youngjun; Lee, Jang-Sik (2017-09-26). "Artificial Synapses with Short- and Long-Term Memory for Spiking Neural Networks Based on Renewable Materials". ACS Nano. 11 (9): 8962–8969. doi:10.1021/acsnano.7b03347. PMID 28837313.

- ^ Hota, Mrinal K.; Bera, Milan K.; Kundu, Banani; Kundu, Subhas C.; Maiti, Chinmay K. (2012). "A Natural Silk Fibroin Protein-Based Transparent Bio-Memristor". Advanced Functional Materials. 22 (21): 4493–4499. doi:10.1002/adfm.201200073. S2CID 137399893.

- ^ Cardona-Serra, Salvador; Rosaleny, Lorena E.; Giménez-Santamarina, Silvia; Martínez-Gil, Luis; Gaita-Ariño, Alejandro (2020-12-16). "Towards peptide-based tunable multistate memristive materials". Physical Chemistry Chemical Physics. 23 (3): 1802–1810. doi:10.1039/D0CP05236A. hdl:10550/79239. PMID 33434247. S2CID 231595640.

- ^ Milano, G.; Porro, S.; Valov, I.; Ricciardi, C. (2019). "Recent Developments and Perspectives for Memristive Devices Based on Metal Oxide Nanowires". Advanced Electronic Materials. 5 (9): 1800909. doi:10.1002/aelm.201800909. S2CID 139445142.

- ^ Carrara, S. (2021). "The Birth of a New Field: Memristive Sensors. A Review". IEEE Sensors Journal. 21 (11): 12370–12378. Bibcode:2021ISenJ..2112370C. doi:10.1109/JSEN.2020.3043305. S2CID 234542676.

- ^ Wang, X.; Chen, Y.; Xi, H.; Dimitrov, D. (2009), "Spintronic Memristor through Spin Torque Induced Magnetization Motion", IEEE Electron Device Letters, 30 (3): 294–297, Bibcode:2009IEDL...30..294W, doi:10.1109/LED.2008.2012270, S2CID 39590957

- ^ Savage, N. (2009-03-16). "Spintronic Memristor". IEEE Spectrum. Archived from the original on 2010-12-24. Retrieved 2011-03-20.

- ^ Chanthbouala, A.; Matsumoto, R.; Grollier, J.; Cros, V.; Anane, A.; Fert, A.; Khvalkovskiy, A. V.; Zvezdin, K. A.; Nishimura, K.; Nagamine, Y.; Maehara, H.; Tsunekawa, K.; Fukushima, A.; Yuasa, S. (2011-04-10). "Vertical-current-induced domain-wall motion in MgO-based magnetic tunnel junctions with low current densities". Nature Physics. 7 (8): 626–630. arXiv:1102.2106. Bibcode:2011NatPh...7..626C. doi:10.1038/nphys1968. S2CID 119221544.

- ^ Bowen, M.; Maurice, J.-L.; Barthe´le´my, A.; Prod’homme, P.; Jacquet, E.; Contour, J.-P.; Imhoff, D.; Colliex, C. (2006). "Bias-crafted magnetic tunnel junctions with bistable spin-dependent states". Applied Physics Letters. 89 (10): 103517. Bibcode:2006ApPhL..89j3517B. doi:10.1063/1.2345592.

- ^ Halley, D.; Majjad, H.; Bowen, M.; Najjari, N.; Henry, Y.; Ulhaq-Bouillet, C.; Weber, W.; Bertoni, G.; Verbeeck, J.; Van Tendeloo, G. (2008). "Electrical switching in Fe/Cr/MgO/Fe magnetic tunnel junctions". Applied Physics Letters. 92 (21): 212115. Bibcode:2008ApPhL..92u2115H. doi:10.1063/1.2938696.

- ^ a b Krzysteczko, P.; Günter, R.; Thomas, A. (2009), "Memristive switching of MgO based magnetic tunnel junctions", Applied Physics Letters, 95 (11): 112508, arXiv:0907.3684, Bibcode:2009ApPhL..95k2508K, CiteSeerX 10.1.1.313.2571, doi:10.1063/1.3224193, S2CID 15383692

- ^ Bertin, Eric; Halley, David; Henry, Yves; Najjari, Nabil; Majjad, Hicham; Bowen, Martin; DaCosta, Victor; Arabski, Jacek; Doudin, Bernard (2011), "Random barrier double-well model for resistive switching in tunnel barriers", Journal of Applied Physics, 109 (8): 013712–013712–5, Bibcode:2011JAP...109a3712D, doi:10.1063/1.3530610, retrieved 2014-12-15

- ^ Schleicher, F.; Halisdemir, U.; Lacour, D.; Gallart, M.; Boukari, S.; Schmerber, G.; Davesne, V.; Panissod, P.; Halley, D.; Majjad, H.; Henry, Y.; Leconte, B.; Boulard, A.; Spor, D.; Beyer, N.; Kieber, C.; Sternitzky, E.; Cregut, O.; Ziegler, M.; Montaigne, F.; Beaurepaire, E.; Gilliot, P.; Hehn, M.; Bowen, M. (2014-08-04), "Localized states in advanced dielectrics from the vantage of spin- and symmetry-polarized tunnelling across MgO", Nature Communications, 5: 4547, Bibcode:2014NatCo...5.4547S, doi:10.1038/ncomms5547, PMID 25088937

- ^ Garcia, V.; Bibes, M.; Bocher, L.; Valencia, S.; Kronast, F.; Crassous, A.; Moya, X.; Enouz-Vedrenne, S.; Gloter, A.; Imhoff, D.; Deranlot, C.; Mathur, N. D.; Fusil, S.; Bouzehouane, K.; Barthelemy, A. (2010-02-26), "Ferroelectric Control of Spin Polarization", Science, 327 (5969): 1106–1110, Bibcode:2010Sci...327.1106G, doi:10.1126/science.1184028, PMID 20075211, S2CID 206524358

- ^ Pantel, D.; Goetze, S.; Hesse, D.; Alexe, M. (2012-02-26), "Reversible electrical switching of spin polarization in multiferroic tunnel junctions", Nature Materials, 11 (4): 289–293, Bibcode:2012NatMa..11..289P, doi:10.1038/nmat3254, PMID 22367005

- ^ Huai, Y. (December 2008), "Spin-Transfer Torque MRAM (STT-MRAM): Challenges and Prospects" (PDF), AAPPS Bulletin, 18 (6): 33–40, archived from the original (PDF) on 2012-03-23

- ^ Krzysteczko, P.; Münchenberger, J.; Schäfers, M.; Reiss, G.; Thomas, A. (2012), "The Memristive Magnetic Tunnel Junction as a Nanoscopic Synapse-Neuron System", Advanced Materials, 24 (6): 762–766, Bibcode:2012APS..MAR.H5013T, doi:10.1002/adma.201103723, PMID 22223304, S2CID 205242867

- ^ "Massimiliano Di Ventra's Homepage". physics.ucsd.edu.

- ^ Pershin, Y. V.; Di Ventra, M. (2008), "Spin memristive systems: Spin memory effects in semiconductor spintronics", Physical Review B, 78 (11): 113309, arXiv:0806.2151, Bibcode:2008PhRvB..78k3309P, doi:10.1103/PhysRevB.78.113309, S2CID 10938532

- ^ Pershin, Y. V.; Di Ventra, M. (2008), "Current-voltage characteristics of semiconductor/ferromagnet junctions in the spin-blockade regime", Physical Review B, 77 (7): 073301, arXiv:0707.4475, Bibcode:2008PhRvB..77g3301P, doi:10.1103/PhysRevB.77.073301, S2CID 119604218

- ^ Campbell, K. (January 2017), "Self-directed channel memristor for high temperature operation", Microelectronics Journal, 59: 10–14, arXiv:1608.05357, doi:10.1016/j.mejo.2016.11.006, S2CID 27889124

- ^ Knowm Memristors, Knowm Inc

- ^ "Memristor Market Expected to Reach $79.0 Million by 2020, Globally - Allied Market Research". Archived from the original on 2017-02-26. Retrieved 2017-02-25.

- ^ Johnson, R. C. (2008-04-30), "'Missing link' memristor created", EE Times, retrieved 2008-04-30

- ^ "Finding the Missing Memristor - R. Stanley Williams", Youtube, 2010-01-22

- ^ Markoff, J. (2008-05-01), "H.P. Reports Big Advance in Memory Chip Design", New York Times, retrieved 2008-05-01

- ^ Gutmann, E. (2008-05-01), "Maintaining Moore's law with new memristor circuits", Ars Technica, retrieved 2008-05-01

- ^ Palmer, J. (2012-05-18), "Memristors in silicon promising for dense, fast memory", BBC News, retrieved 2012-05-18

- ^ Snider, Gregory Stuart (2004) "재구성 가능한 저항기 크로스바를 갖는 컴퓨팅을 위한 아키텍처 및 방법" 미국 특허 7,203,789

- ^ Moutet, Blaze Laurent (2006) "프로그래밍 가능한 크로스바 신호 프로세서" 미국 특허 7,302,513

- ^ Dong, Zhekang; Sing Lai, Chun; He, Yufei; Qi, Donglian; Duan, Shukai (2019-11-01). "Hybrid dual-complementary metal–oxide–semiconductor/memristor synapse-based neural network with its applications in image super-resolution". IET Circuits, Devices & Systems. 13 (8): 1241–1248. doi:10.1049/iet-cds.2018.5062.

- ^ Snider, Greg (2003) "분자-접합-나노와이어-크로스바 기반 신경망" 미국 특허 7,359,888

- ^ Moutet, Blaze Laurent (2007) "크로스바 제어 회로" 미국 특허 7,609,086

- ^ Pino, Robinson E. (2010) "재구성 가능한 전자 회로" 미국 특허 7,902,857

- ^ Ielmini, D; Wong, H.-S. P. (2018). "In-memory computing with resistive switching devices". Nature Electronics. 1 (6): 333–343. doi:10.1038/s41928-018-0092-2. hdl:11311/1056513. S2CID 57248729.

- ^ Moutet, Blaze Laurent (2009) "멤리스터 크로스바 신경 인터페이스" 미국 특허 7,902,867

- ^ 강희복(2009) "멤리스터 특성을 갖는 메모리 유닛을 갖는 RFID 장치" 미국 특허 8,113,437

- ^ Luo, Li; Dong, Zhekang; Duan, Shukai; Lai, Chun Sing (2020-04-20). "Memristor-based stateful logic gates for multi-functional logic circuit". IET Circuits, Devices & Systems. 14 (6): 811–818. doi:10.1049/iet-cds.2019.0422.

- ^ Lehtonen, E.; Poikonen, J.H.; Laiho, M. (2010). "Two memristors suffice to compute all Boolean functions". Electronics Letters. 46 (3): 230. Bibcode:2010ElL....46..230L. doi:10.1049/el.2010.3407.

- ^ Chattopadhyay, A.; Rakosi, Z. (2011). "Combinational logic synthesis for material implication". 2011 IEEE/IFIP 19th International Conference on VLSI and System-on-Chip. p. 200. doi:10.1109/VLSISoC.2011.6081665. ISBN 978-1-4577-0170-2. S2CID 32278896.

- ^ Pershin, Y. V.; La Fontaine, S.; Di Ventra, M. (2009), "Memristive model of amoeba learning", Physical Review E, 80 (2): 021926, arXiv:0810.4179, Bibcode:2009PhRvE..80b1926P, doi:10.1103/PhysRevE.80.021926, PMID 19792170, S2CID 9820970

- ^ a b Saigusa, T.; Tero, A.; Nakagaki, T.; Kuramoto, Y. (2008), "Amoebae Anticipate Periodic Events" (PDF), Physical Review Letters, 100 (1): 018101, Bibcode:2008PhRvL.100a8101S, doi:10.1103/PhysRevLett.100.018101, hdl:2115/33004, PMID 18232821, S2CID 14710241

- ^ Versace, M.; Chandler, B. (2010-11-23). "MoNETA: A Mind Made from Memristors". IEEE Spectrum.

Versace, M.; Chandler, B. (2010). "The brain of a new machine". IEEE Spectrum. 47 (12): 30–37. doi:10.1109/MSPEC.2010.5644776. S2CID 45300119. - ^ Snider, G.; et al. (2011), "From Synapses to Circuitry: Using Memristive Memory to Explore the Electronic Brain", IEEE Computer, 44 (2): 21–28, doi:10.1109/MC.2011.48, S2CID 16307308

- ^ Merrikh-Bayat, F.; Bagheri-Shouraki, S.; Rohani, A. (2011), "Memristor crossbar-based hardware implementation of IDS method", IEEE Transactions on Fuzzy Systems, 19 (6): 1083–1096, arXiv:1008.5133, doi:10.1109/TFUZZ.2011.2160024, S2CID 3163846

- ^ Merrikh-Bayat, F.; Bagheri-Shouraki, S. (2011). "Efficient neuro-fuzzy system and its Memristor Crossbar-based Hardware Implementation". arXiv:1103.1156 [cs.AI].

- ^ Chua, L. (2013). "Memristor, Hodgkin-Huxley, and Edge of Chaos". Nanotechnology. 24 (38): 383001. Bibcode:2013Nanot..24L3001C. doi:10.1088/0957-4484/24/38/383001. PMID 23999613. S2CID 34999101.

- ^ a b Di Ventra, M.; Pershin, Y. V.; Chua, L. (2009), "Circuit elements with memory: memristors, memcapacitors and meminductors", Proceedings of the IEEE, 97 (10): 1717–1724, arXiv:0901.3682, Bibcode:2009arXiv0901.3682D, doi:10.1109/JPROC.2009.2021077, S2CID 7136764

- ^ Abdelhouahad, M.-S.; Lozi, R.; Chua, L. (September 2014), "Memfractance: A Mathematical Paradigm for Circuit Elements with Memory" (PDF), International Journal of Bifurcation and Chaos, 24 (9): 1430023 (29 pages), Bibcode:2014IJBC...2430023A, doi:10.1142/S0218127414300237

- ^ Prodromakis, T.; Toumazou, C.; Chua, L. (June 2012), "Two centuries of memristors", Nature Materials, 11 (6): 478–481, Bibcode:2012NatMa..11..478P, doi:10.1038/nmat3338, PMID 22614504

- ^ Barella, M. (2016), "LabOSat: Low cost measurement platform designed for hazardous environments", 2016 Seventh Argentine Conference on Embedded Systems (CASE), pp. 1–6, doi:10.1109/SASE-CASE.2016.7968107, ISBN 978-987-46297-0-8, S2CID 10263318

- ^ "Probaron con éxito las memorias instaladas en el satélite argentino "Tita"". Telam. 2014-07-21.

- ^ Barella, M. (2019), "Studying ReRAM devices at Low Earth Orbits using the LabOSat platform", Radiation Physics and Chemistry, 154: 85–90, Bibcode:2019RaPC..154...85B, doi:10.1016/j.radphyschem.2018.07.005

- ^ "UNSAM - Universidad Nacional de San Martín". www.unsam.edu.ar.

- ^ "Qué hace LabOSat, el laboratorio electrónico dentro de los nanosatélites Fresco y Batata". Telam. 2016-06-22.

- ^ "Startup Beats HP, Hynix to Memristor Learning". EE Times. 2015-07-05.

- ^ "MemSat". Gunter Space Page. 2018-05-22.

- ^ "MIT and Ericsson Collaborates to Research New Generation of Energy-Efficient Computing Networks - News". eepower.com.

- ^ "MIT and Ericsson Set Goals for Zero-power Devices and a New Field—"Lithionics" - News". www.allaboutcircuits.com.

추가열람

- Chen, Dongmin; Chua, Leon O.; Hwang, Cheol Seong; Wang, Shih-Yuan; Waser, Rainer; Williams, R. Stanley; Yang, Jianhua, eds. (March 2011). "Special Issue: Memristive and Resistive Devices and Systems". Applied Physics A. 102 (4).

- Mazumder, P.; Kang, S. M.; Waser, R., eds. (June 2012). "Special Issue: MEMRISTORS: DEVICES, MODELS, AND APPLICATIONS". Proceedings of the IEEE. 100 (6): 1905–2092. doi:10.1109/JPROC.2012.2197452.

- Tetzlaff, Ronald, ed. (2013). Memristors and Memristive Systems. Springer Science & Business Media. doi:10.1007/978-1-4614-9068-5. ISBN 978-1-4614-9068-5.

- Adamatzky, Andrew; Chua, Leon, eds. (2013). Memristor Networks. Springer Science & Business Media. doi:10.1007/978-3-319-02630-5. ISBN 978-3-319-02630-5. S2CID 39739718.

- Atkin, Keith (May 2013). "An introduction to the memristor". Physics Education. 48 (3): 317–321. Bibcode:2013PhyEd..48..317A. doi:10.1088/0031-9120/48/3/317. S2CID 121268844.

- Gale, Ella (2014-10-01). "TiO2-based memristors and ReRAM: materials, mechanisms and models (a review)". Semiconductor Science and Technology. 29 (10): 104004. arXiv:1611.04456. Bibcode:2014SeScT..29j4004G. doi:10.1088/0268-1242/29/10/104004. S2CID 5686212.

- Traversa, Fabio Lorenzo; Di Ventra, Massimiliano (November 2015). "Universal Memcomputing Machines". IEEE Transactions on Neural Networks and Learning Systems. 26 (11): 2702–2715. arXiv:1405.0931. CiteSeerX 10.1.1.747.5690. doi:10.1109/TNNLS.2015.2391182. PMID 25667360. S2CID 1406042.

- Caravelli, Francesco; Carbajal, Juan Pablo (January 2019). "Memristors for the curious outsiders". Technologies. 6 (4): 118. arXiv:1812.03389. doi:10.3390/technologies6040118. S2CID 54464654.

- Maan, Akshay Kumar; Jayadevi, Deepthi Anirudhan; James, Alex Pappachen (August 2017). "A Survey of Memristive Threshold Logic Circuits". IEEE Transactions on Neural Networks and Learning Systems. 28 (8): 1734–1746. arXiv:1604.07121. doi:10.1109/TNNLS.2016.2547842. PMID 27164608. S2CID 1798273.

외부 링크

- YouTube에서 누락된 멤리스터 찾기

- 멤리스터 논문 대화형 데이터베이스(2013)

- Simonite, Tom (2015-04-21). "Machine Dreams". Technology Review. Retrieved 2017-12-05.

- "레옹 추아: 전구 대 구글 바둑기사" - (폴란드어로) 멤리스터 제작자 레옹 추아 인터뷰

- "레옹 추아: 전구 대 구글 바둑기사" - (영어로) 멤리스터 제작자 레옹 추아 인터뷰

방전관 양단의 전압이고,

방전관 양단의 전압이고,  방전관에 흐르는 전류이며,

방전관에 흐르는 전류이며,

![{\displaystyle {\begin{aligned}v&=R_{0}(T_{0})\exp \left[\beta \left({\frac {1}{T}}-{\frac {1}{T_{0}}}\right)\right]i\\&\equiv R(T)i\\{\frac {dT}{dt}}&={\frac {1}{C}}\left[-\delta \cdot (T-T_{0})+R(T)i^{2}\right]\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/82ed93071ea27056ff61354632e515cc4d64dde7)