JFET

JFET 게이트에 전압이 인가되면 P채널 JFET에서 소스에서 드레인까지의 전류가 제한됩니다. | |

| 유형 | 활동적인 |

|---|---|

| 핀 구성 | 드레인, 게이트, 소스 |

| 전자 기호 | |

| |

접합 게이트 전계효과 트랜지스터(JFET)는 가장 단순한 유형의 전계효과 트랜지스터 [1]중 하나입니다.JFET는 3단자 반도체 소자로 전자 제어 스위치 또는 저항으로 사용하거나 증폭기를 조립하는 데 사용할 수 있습니다.

바이폴라 접합 트랜지스터와 달리 JFET는 바이어스 전류를 필요로 하지 않는다는 점에서 배타적으로 전압 제어됩니다.전하가 소스와 드레인 단자 사이의 반도체 채널을 통해 흐릅니다.게이트 단자에 역바이어스 전압을 인가함으로써 채널을 끼우고 전류를 방해하거나 완전히 차단한다.JFET는 일반적으로 게이트와 소스 단자 사이에 전압이 0일 때 전도됩니다.게이트 단자와 소스 단자 사이에 적절한 극성의 전위차가 적용되면 JFET는 전류 흐름에 대해 저항성이 높아지며, 이는 소스와 드레인 단자 사이의 채널에서 흐르는 전류가 적다는 것을 의미합니다.

JFET는 다수의 전하 캐리어가 없는 고갈 영역의 원리에 의존하기 때문에 고갈 모드 디바이스라고 불리기도 합니다.전류가 흐를 수 있도록 하려면 고갈 영역을 닫아야 합니다.

JFET에는 n타입 또는 p타입 채널을 사용할 수 있습니다.n형에서는 게이트에 인가되는 전압이 소스에 대해 음의 경우 전류가 감소합니다(p형에서도 마찬가지로 게이트에 인가되는 전압이 소스에 대해 양의 경우).공통 소스 또는 공통 드레인 구성의 JFET는 입력[2] 임피던스가 크기 때문에(때로는 10옴10 정도) 게이트 입력으로 사용되는 회로에서 전류가 거의 유입되지 않습니다.

역사

1920년대와 1930년대에 Julius Lilienfeld에 의해 일련의 FET 유사 장치들이 특허를 받았습니다.그러나 재료 과학 및 제조 기술은 FET가 실제로 제조되기까지 수십 년의 발전이 필요합니다.

JFET는 1945년 [3]하인리히 웰커에 의해 처음 특허를 받았다.1940년대 동안, 연구원 존 바딘, 월터 하우저 브래튼, 그리고 윌리엄 쇼클리는 FET를 건설하려고 노력했지만, 그들의 반복적인 시도에서 실패했다.그들은 고장 원인을 진단하는 과정에서 포인트 접점 트랜지스터를 발견했다.1952년 쇼클리의 JFET에 대한 이론적인 치료에 이어 1953년 조지 C에 의해 실용적인 JFET가 만들어졌다. 데이지와 이안 M.[4] 로스입니다일본인 엔지니어 니시자와 준이치 씨와 Y 씨.와타나베는 1950년에 정적 유도 트랜지스터(SIT)라고 불리는 유사한 장치에 대한 특허를 출원했다.SIT는 채널이 [4]짧은 JFET의 한 종류입니다.

2008년 실리콘 카바이드(SiC) 와이드 밴드갭 디바이스의 상용 도입으로 JFET를 사용한 고속 고전압 스위칭이 기술적으로 실현 가능하게 되었습니다.SiC JFET는 제조의 초기 어려움(특히 불일치와 낮은 수율)으로 인해 처음에는 틈새 제품으로 남아 있었고 그에 따라 비용이 많이 들었습니다.2018년까지 이러한 제조 문제는 대부분 해결되었습니다.그때까지 SiC JEFET는 기존의 저전압 실리콘 MOSFET와 [5]함께 일반적으로 사용되었습니다.이 조합에서 SiC JFET + Si MOSFET 디바이스는 MOSFET의 [5]간단한 게이트 구동뿐만 아니라 광대역 갭 디바이스의 장점을 가지고 있습니다.

구조.

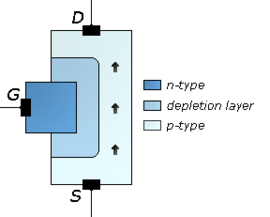

JFET는 반도체 재료의 긴 채널로, 양전하 캐리어 또는 구멍(p형)을 풍부하게 포함하거나 음전하 캐리어 또는 전자(n형)를 포함합니다.양 끝의 오믹 접점이 소스(S)와 드레인(D)을 형성합니다.채널의 한쪽 또는 양쪽에 pn접합을 형성하거나 채널과 반대되는 도핑이 있는 영역을 이용하여 둘러싸고 오믹 게이트 접점(G)을 이용하여 바이어스한다.

기능들

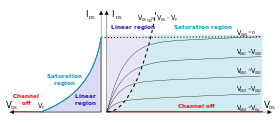

JFET 작동은 정원 호스와 비교할 수 있습니다.호스를 통과하는 물의 흐름은 단면을 줄이기 위해 압착하여 제어할 수 있으며, JFET를 통과하는 전하의 흐름은 전류 통로를 제한하여 제어합니다.전류는 또한 소스와 드레인 사이의 전계에 따라 달라집니다(호스 양쪽 끝의 압력 차이와 유사함).이 전류 의존성은 특정 인가 전압 위의 다이어그램에 표시된 특성에서는 지원되지 않습니다.이것은 포화 영역이며, JFET는 일반적으로 디바이스 전류가 드레인 소스 전압의 영향을 거의 받지 않는 정전류 영역에서 작동합니다.JFET는 이 정전류 특성을 접합 트랜지스터 및 열전자 튜브(밸브) 테트로이드 및 펜토드와 공유합니다.

도통채널의 협착은 전계효과를 이용하여 이루어진다.게이트와 소스 사이의 전압이 인가되어 게이트-소스 pn접합이 역바이어스 되고, 그 결과 이 접합부의 고갈층이 확대되어 도통채널을 잠식하여 그 단면적을 제한한다.이 고갈층은 이동통신사가 고갈되고 실질적인 목적을 [6]위해 전기적으로 비전도적이기 때문에 소위 말하는 것이다.

고갈층이 전도 채널의 폭에 걸치면 핀치오프가 달성되고 드레인에서 소스로의 전도가 정지됩니다.핀치오프(pinch-off)는 게이트-선원 접합부의 특정 역바이어스(VGS)에서 발생한다.핀치오프 전압(Vp)(임계값[7][8] 전압 또는 차단[9][10][11] 전압이라고도 함)은 같은 유형의 장치 간에도 상당히 다릅니다.예를 들어 Temic J202 디바이스의 V는GS(off) -0.8V에서 [12]-4V까지 다양합니다.일반적인 값은 -0.3V에서 -10V까지 다양합니다(혼합적으로 핀치오프 전압이라는 용어는 선형 영역과 포화 영역을 구분하는 V 값을DS 가리킬 때도 사용됩니다).[10][11]

n채널 장치를 끄려면 음의 게이트-소스 전압(VGS)이 필요합니다.반대로 p채널 디바이스를 끄려면 양의GS V가 필요합니다.

정상 작동 시 게이트에 의해 개발된 전계는 소스-드레인 전도를 어느 정도 차단한다.

일부 JFET 디바이스는 소스 및 드레인에 대해 대칭입니다.

도식 기호

JFET 게이트는 때때로 채널 중앙에 그려집니다(다음 예시와 같이 드레인 또는 소스 전극 대신).이 대칭은 "드레인"과 "소스"가 서로 호환된다는 것을 나타내므로, 이 기호는 실제로 상호 호환이 가능한 JFET에만 사용해야 합니다.

같은 패키지의 듀얼 매치 [13]컴포넌트와 같이 인클로저가 회로 기능에 중요한 경우, 기호는 원 안에 그려질 수 있습니다(이별 장치의 엔벨로프를 나타냄).

모든 경우 화살표 헤드는 채널과 게이트 사이에 형성된 P-N 접합의 극성을 나타냅니다.일반 다이오드와 마찬가지로 화살표는 P에서 N(전방 바이어스 시)을 가리킵니다.영어 니모닉은 N채널 디바이스의 화살표가 "지정"되는 것입니다.

다른 트랜지스터와의 비교

상온에서 JFET 게이트 전류(게이트-채널 접점의 역누전)는 MOSFET(게이트와 채널 사이에 절연 산화물이 있음)와 비슷하지만 바이폴라 접점 트랜지스터의 기본 전류보다 훨씬 작습니다.JFET는 MOSFET보다 게인(트랜스컨덕턴스)이 높을 뿐만 아니라 플리커 노이즈가 낮기 때문에 일부 저노이즈, 고입력 임피던스 op-amp에서 사용됩니다.또한 JFET는 정전하 [14]축적으로 인한 손상에 덜 취약합니다.

수학적 모형

선형 옴 영역

작은 전압DS V(즉, 선형, 오믹[15] 또는 삼극[7] 영역)로 인한 N-JFET의 전류는 채널을 전기 _[16]의 직사각형 막대로 처리하여 얻을 수 있습니다.

어디에

- ID = 방전 전류,

- b = 주어진 게이트 전압에 대한 채널 두께,

- W = 채널 폭,

- L = 채널 길이,

- q = 전자 전하 = 1.6×10−19 C,

- μ = 전자n 이동도,

- Nd = n-type 도핑(표준) 농도,

- VP = 핀치오프 전압.

그러면 선형 영역의 방전 전류를 다음과 같이 근사할 수 있습니다.

DSS의 에서 보면 { 드레인 전류는 다음과 같이 나타낼[citation needed] 수 있습니다.

정전류 영역

포화 또는 활성[17][7] 또는 핀치오프[18] 영역의 드레인 전류는 종종 게이트 바이어스의[16] 관점에서 다음과 같이 근사됩니다.

여기서DSS I는 0 게이트-소스 전압에서 포화 전류, 즉 임의의 (허용) 드레인-소스 전압에서 FET를 통해 소스로 흐를 수 있는 최대 전류입니다(예: 위의 I-V 특성 다이어그램 참조).

포화 영역에서 JFET 드레인 전류는 게이트-소스 전압의 영향을 가장 많이 받고 드레인-소스 전압의 영향을 거의 받지 않습니다.

채널 도핑이 균일하여 게이트 소스 전압의 절대값의 제곱근에 비례하여 고갈 영역 두께가 커지는 경우 채널 두께 b는 제로 바이어스 채널 두께 a로[citation needed] 다음과 같이 나타낼 수 있습니다.

어디에

- V는P 채널 두께가 0이 되는 게이트 소스 전압인 핀치오프 전압입니다.

- a는 제로 게이트 소스 전압에서의 채널 두께입니다.

트랜스컨덕턴스

접합부 FET의 트랜스컨덕턴스는 다음과 같습니다.

서 V P V_은 핀치오프 전압이고DSS I는 최대 드레인 전류입니다.은 g fs투과율 y 라고 불리기도 합니다

「 」를 참조해 주세요.

레퍼런스

- ^ Hall, John. "Discrete JFET" (PDF). linearsystems.com.

- ^ "Junction Field Effect Transistor". Electronics Tutorials. Archived from the original on 2022-01-31. Retrieved 2022-06-19.

- ^ Grundmann, Marius (2010). The Physics of Semiconductors. Springer-Verlag. ISBN 978-3-642-13884-3.

- ^ a b Junction 전계효과 소자, 전력조절용 반도체 소자, 1982.

- ^ a b 를 클릭합니다Flaherty, Nick (October 18, 2018), "Third generation SiC JFET adds 1200 V and 650 V options", EeNews Power Management.

- ^ JFET 의 구조와 동작에 대해서는, 예를 참조해 주세요.

- ^ a b c "Junction Field Effect Transistor (JFET)" (PDF). ETEE3212 Lecture Notes.

value of vGS ... for which the channel is completely depleted ... is called the threshold, or pinch-off, voltage and occurs at vGS = VGS(OFF). ... This linear region of operation is called ohmic (or sometimes triode) ... Beyond the knee of the ohmic region, the curves become essentially flat in the active (or saturation) region of operation.

- ^ Sedra, Adel S.; Smith, Kenneth C. "5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)" (PDF). Microelectronic Circuits.

At this value of vGS the channel is completely depleted ... For JFETs the threshold voltage is called the pinch-off voltage and is denoted VP.

- ^ Horowitz, Paul; Hill, Winfield (1989). The art of electronics (2nd ed.). Cambridge [England]: Cambridge University Press. p. 120. ISBN 0-521-37095-7. OCLC 19125711.

For JFETs the gate-source voltage at which drain current approaches zero is called the "gate-source cutoff voltage", VGS(OFF), or the "pinch-off voltage", VP ... For enhancement-mode MOSFETs the analogous quantity is the "threshold voltage"

- ^ a b Mehta, V. K.; Mehta, Rohit (2008). "19 Field Effect Transistors" (PDF). Principles of electronics (11th ed.). S. Chand. pp. 513–514. ISBN 978-8121924504. OCLC 741256429.

Pinch off Voltage (VP). It is the minimum drain–source voltage at which the drain current essentially becomes constant. ... Gate–source cut off voltage VGS (off). It is the gate–source voltage where the channel is completely cut off and the drain current becomes zero.

- ^ a b U. A. Bakshi; A. P. Godse (2008). Electronics Engineering. Technical Publications. p. 10. ISBN 978-81-8431-503-5.

Do not confuse cutoff with pinch off. The pinch-off voltage VP is the value of the VDS at which the drain current reaches a constant value for a given value of VGS. ... The cutoff voltage VGS(off) is the value of VGS at which the drain current is 0.

- ^ "J201 data sheet" (PDF). Retrieved 2021-01-22.

- ^ "A4.11 Envelope or Enclosure". ANSI Y32.2-1975 (PDF).

The envelope or enclosure symbol may be omitted from a symbol referencing this paragraph, where confusion would not result

- ^ Kopp, Emilie (2019-01-16). "What's the difference between a MOSFET and a JFET?". Power Electronic Tips. Archived from the original on 2021-05-17. Retrieved 2022-06-16.

- ^ "What is the Ohmic Region of a FET Transistor". www.learningaboutelectronics.com. Retrieved 2020-12-13.

ohmic region ... also called the linear region

- ^ a b Balbir Kumar and Shail B. Jain (2013). Electronic Devices and Circuits. PHI Learning Pvt. Ltd. pp. 342–345. ISBN 9788120348448.

- ^ "Junction Field Effect Transistor". Electronics Tutorials.

Saturation or Active Region

- ^ Scholberg, Kate (2017-03-23). "What is the meaning of "pinch-off region"?".

The "pinch-off region" (or "saturation region") refers to operation of a FET with more than a few volts.

- ^ Kirt Blattenberger RF Cafe. "JFETS: How They Work, How to Use Them, May 1969 Radio-Electronics". Retrieved 2021-01-04.

yfs – Small-signal, common-source, forward transadmittance (sometimes called gfs-transconductance)

외부 링크

Wikimedia Commons의 JFET 관련 미디어

Wikimedia Commons의 JFET 관련 미디어- 물리 111 연구소 - JFET 회로 I

- n채널 JFET의 대화형 설명