클리퍼 아키텍처

Clipper architecture클리퍼 아키텍처는 Fairchild Semiconductor가 설계한 32비트 RISC와 같은 명령어세트 아키텍처입니다Opus Systems는 개인용 메인프레임 제품군의 [1]일부로 Clipper 기반의 제품을 제공했지만, 이 아키텍처는 시장에서 큰 성공을 거두지 못했습니다.또한 Clipper 프로세서를 사용하여 주요 제품군을 만든 컴퓨터 제조업체는 Intergraph와 High Level Hardware뿐이었습니다.Clipper 아키텍처를 사용한 최초의 프로세서는 Fairchild에 의해 설계 및 판매되었지만, 이를 담당하는 사업부는 1987년에 Intergraph에 매각되었습니다. Intergraph는 자체 [2]시스템에서 사용하기 위해 Clipper 프로세서에 대한 작업을 계속했습니다.

Clipper 아키텍처는 이전의 CISC 아키텍처에 비해 단순화된 명령어세트를 사용했지만, 현재의 다른 RISC 프로세서보다 복잡한 명령어를 포함하고 있었습니다.이러한 명령어는 클리퍼 CPU 내의 이른바 매크로 인스트럭션 ROM에 실장되어 있습니다.이 스킴에 의해 Clipper는 다른 RISC CPU보다 코드 밀도가 다소 높아졌습니다.

버전

Fairchild가 생산한 최초의 Clipper 마이크로프로세서는 1986년에 출시된 C100이었습니다.1988년에는 인터그래프사의 C300이 더 빨라졌다.Clipper의 최종 모델은 1990년에 출시된 C400으로, 더 빠르고 더 많은 부동소수점 레지스터를 추가하도록 광범위하게 재설계되었다.C400 프로세서는 슈퍼스케어 명령 디스패치와 슈퍼파이프라인 처리라는2가지 주요 아키텍처 기술을 조합하여 새로운 수준의 퍼포먼스를 실현했습니다.

당시의 많은 프로세서가 슈퍼스칼라 명령 디스패치 또는 슈퍼파이프라인 처리를 사용했지만 Clipper C400은 이 둘을 [3]모두 사용한 최초의 프로세서였습니다.

Intergraph는 C5로 알려진 후속 Clipper 프로세서 설계에 대한 작업을 시작했지만, 이는 완료되거나 출시되지 않았습니다.그럼에도 불구하고, 일부 고급 프로세서 설계 기술은 C5용으로 고안되었고 Intergraph는 이러한 기술에 대한 특허를 부여받았다.이들 특허는 Clipper 특허와 함께 Intergraph가 인텔 및 기타 [4]기업을 상대로 특허 침해 소송의 기초가 되어 왔습니다.

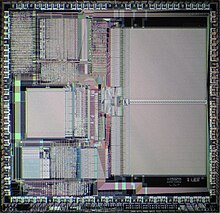

다른 많은 마이크로프로세서와는 달리 클리퍼 프로세서는 사실 여러 개의 칩셋이었다.C100 및 C300은 3개의 칩으로 구성되어 있습니다.하나는 정수 유닛과 부동소수점 유닛을 모두 갖춘 중앙처리 유닛, 2개의 캐시 및 메모리 관리 유닛(CAMMU)입니다.하나는 데이터 및 명령용입니다.CAMMU에는 캐시, 변환 룩사이드버퍼 및 메모리 보호 및 가상 메모리 지원이 포함되어 있습니다.C400은 정수 CPU, FPU, MMU 및 캐시 유닛의 4가지 기본 유닛으로 구성됩니다.초기 버전에서는 CPU와 FPU에 각각 1개의 칩을 사용하고 MMU와 캐시 유닛에 개별 요소를 사용했지만 이후 버전에서는 MMU와 캐시 유닛이 하나의 CAMMU 칩으로 결합되었습니다.

레지스터 및 명령 세트

Clipper에는 16개의 정수 레지스터(스택 포인터로서 R15가 사용), 16개의 부동소수점 레지스터(초기 구현에서는 8개로 제한됨), 프로그램 카운터(PC), ALU 및 FPU 상태 플래그와 트랩을 포함하는 PSW(프로세서 상태 워드), 외부 인터럽트 활성화, 사용자/슈퍼바이저 모드를 포함하는 시스템 상태 워드(SSW)가 있습니다.주소 변환 제어 비트

사용자 모드와 슈퍼바이저 모드에는 별도의 정수 레지스터 뱅크가 있습니다.인터럽트 처리에는 스택상의 PC, PSW 및 SSW의 저장, PSW의 클리어 및 메모리트랩 벡터로부터의 PC 및 SSW의 로드가 포함됩니다.

Clipper는 로드/스토어 아키텍처로, 산술 연산은 레지스터 또는 즉시 피연산자만 지정할 수 있습니다.기본 명령 "parcel"은 16비트였습니다. opcode 8비트, source register 4비트, destination register 4비트입니다.immediate-operand 형식을 사용하면 다음 명령 구획에서 16비트(부호 확장) 또는 32비트 즉시 피연산자를 지정할 수 있습니다.프로세서는 즉시 피연산자를 포함하여 한결같이 리틀 엔디안이었습니다.

4비트 부호 없는 피연산자를 가진 특별한 "빠른" 인코딩은 (등록에 빠르게 이동)이 아닌 더하기, 빼기, 로드(등록에 빠르게 이동)용으로 제공되었습니다.

로드/스토어 및 브랜치 명령의 어드레싱 모드는 다음과 같습니다.모든 배치가 확장되었습니다.

- (Rn), d12(Rn), d32(Rn): 0, 12 또는 32비트 변위에 상대 등록

- d16(PC), d32(PC): PC 상대

- d16, d32: 절대

- [Rx](Rn), [Rx](PC): 레지스터 또는 PC 상대 인덱스.인덱스 레지스터의 크기가 조정되지 않았습니다.

통상적인 논리 연산과 산술 연산에 가세해, 프로세서는 다음을 서포트하고 있습니다.

- 32×32→32비트 곱셈, 나누기 및 나머지(서명 및 부호 없음)

- 64비트 시프트 및 회전, 짝수/홀수 레지스터 쌍으로 동작

- 32×32→64비트 확장 멀티플

- 정수 레지스터 푸시/팝(감소 전 스토어, 증가 후 로드)

- 서브루틴 콜(PC 푸시, 오퍼랜드의 주소를 PC로 이동)

- 서브루틴에서 반환(스택에서 팝 PC)

- ATOMIC 메모리 로드 및 설정 msbit

- 슈퍼바이저 트랩

보다 복잡한 매크로 명령이 허용됨:

- 다중 정수 레지스터 Rn–R14 푸시/팝

- 복수의 부동소수점 레지스터 Dn~D7 푸시/팝

- 푸시/팝 사용자가 R0~R15를 등록합니다.

- 인터럽트에서 복귀(팝 SSW, PSW 및 PC)

- 문자열 초기화(R1부터 시작하는 R2의 R0 복사본을 메모리에 저장)

- 문자 이동 및 비교(길이: R0, 소스: R1, 대상: R2)

대부분의 명령에서는 임의의 스택포인터 레지스터를 지정할 수 있었지만, 사용자 레지스터의 저장/복원을 제외하고, 복수의 레지스터 조작에서는 R15 만을 사용할 수 있었습니다.

Intergraph의 클리퍼 시스템

Intergraph는 서버와 워크스테이션을 포함한 여러 세대의 Clipper 시스템을 판매했습니다.이러한 시스템에는 InterAct, InterServe 및 InterPro 제품군이 포함되었으며 주로 CAD 시장을 대상으로 했습니다.

Fairchild는 UNIX System V의 버전인 CLIX 운영 체제를 Clipper와 함께 사용하도록 홍보했습니다.Intergraph는 Clipper 기반 시스템에 CLIX를 채택하여 개발을 계속하였습니다.이것이 이 시스템에서 사용할 수 있는 유일한 운영 체제였습니다.Intergraph는 Clipper 시스템용 Microsoft Windows NT 버전을 사용하여 공개적으로 시연했지만 이 작업은 [5]출시 전에 취소되었습니다.Intergraph는 Clipper 라인을 중단하기로 결정하고 대신 Windows NT를 탑재한 x86 시스템을 판매하기 시작했습니다.

레퍼런스

- ^ "Opus Systems Unveils Series 300 Unix Workstations". Computerworld. 4 March 1987. p. 41. Retrieved 23 June 2022.

- ^ Weisberg, David (2008). "The Engineering Design Revolution: The People, Companies and Computer Systems That Changed Forever the Practice of Engineering" (PDF). Chapter 14. Archived (PDF) from the original on 4 March 2016. Retrieved 26 June 2016.

- ^ CPU 컬렉션"Intergraph Clipper C4."

- ^ Flynn, Laurie (31 March 2004). "Intergraph And Intel Settle Chip Dispute". The New York Times. Archived from the original on 19 June 2015. Retrieved 26 June 2016.

- ^ Simpson, Nik (January 15, 2000). "Re: Intergraph Interact 340". Newsgroup: comp.sys.intergraph. Usenet: Sg0g4.34$Ek.5695@newsin1.ispchannel.com.

- Fairchild Semiconductor Corporation (1987). CLIPPER 32-Bit microprocessor: User's Manual. Prentice-Hall. ISBN 0-13-138058-3.

- Walter Hollingsworth; Howard Sachs; Alan Jay Smith (1989). "The CLIPPER Processor: Instruction Set Architecture and Implementation". Communications of the ACM. 32 (2): 200–219. doi:10.1145/63342.63346. S2CID 13239029.

- Walter Hollingsworth; Howard Sachs; Alan Jay Smith (February 11, 1987). The Fairchild CLIPPER: Instruction Set Architecture and Processor Implementation (PDF) (Technical report). UCB/CSD. 87/329. Retrieved 2011-03-22.

- James Cho; Alan Jay Smith; Howard Sachs (April 1986). The Memory Architecture and the Cache and Memory Management Unit for the Fairchild CLIPPER Processor (PDF) (Technical report). UCB/CSD. 86/289. Retrieved 2011-03-22.

- Howard Sachs; Harlan McGhan; Lee Hanson; Nathan Brookwood (1991). "Design and Implementation Trade-offs in the Clipper C400 Architecture". IEEE Micro. 11 (3): 18–21, 74–80. doi:10.1109/40.87566. S2CID 8895269.

- 그래프 간 이력

- Clipper™ 32-Bit Microprocessor Module Instruction Set (PDF), Fairchild, October 1985, retrieved 2020-07-11

- Clipper™ 32-Bit Microprocessor: Introduction to the CLIPPER Architecture (PDF), Fairchild, May 1986, retrieved 2020-07-11

- Clipper™ C100 32-Bit Compute Engine Data Sheet (PDF), Intergraph, December 1987, retrieved 2020-07-11