DEC 알파

DEC Alpha 디지털에서 사용되는 "Alpha Generation" 로고 | |

| 디자이너 | 디지털 이그니션 코퍼레이션 |

|---|---|

| 비트 | 64비트 |

| 소개했다 | 전( |

| 설계. | RISC |

| 유형 | 등록-등록 |

| 부호화 | 고정된. |

| 엔디안니스 | Bi |

| 내선번호 | 바이트/워드 확장(BWX), 제곱근 및 부동소수점 변환 확장(FIX), 카운트 확장(CIX), 모션 비디오 명령(MVI) |

| 열다. | 네, 그렇습니다[1]. |

| 레지스터 | |

| 범용 | 31 + 상시 제로 R31 |

| 부동 소수점 | 31+항상-0.0 F31 |

Alpha(원명 Alpha AXP)는 Digital Equipment Corporation(DEC)이 개발한 64비트 RISC(Reduced Instruction Set Computer) 명령 집합 아키텍처입니다.Alpha는 32비트 VAX 복합 명령어 세트 컴퓨터(CISC)를 대체하여 Unix 워크스테이션 및 유사한 시장에서 매우 경쟁력 있는 RISC 프로세서가 되도록 설계되었습니다.

Alpha는 DEC에 의해 개발 및 제조된 일련의 마이크로프로세서에 구현됩니다.이러한 마이크로프로세서는 다양한 DEC 워크스테이션과 서버에서 가장 두드러지게 사용되고 있으며, 최종적으로는 중간 규모에서 상위 규모 라인업의 거의 모든 기반이 되었습니다.PC 폼팩터 메인보드를 포함한 여러 서드파티 벤더도 Alpha 시스템을 생산했습니다.

Alpha를 지원하는 운영 체제에는 OpenVMS(이전 이름 OpenVMS AXP), Tru64 UNIX(이전 이름 DEC OSF/1 AXP 및 Digital UNIX), Windows NT([2]NT 4.0 이후 중단됨), Linux(Debian, SUSE,[3] Gentoo) 등이 있습니다.SD(최대 6.x), Bell Labs의 Plan 9 및 L4Ka:: 피스타치오 커널.Alpha 아키텍처의 초기 개발 중에 Ultrix에서 Alpha로 포트가 실행되었지만 제품으로 [4]출시되지는 않았습니다.

알파 아키텍처는 DEC의 대부분과 함께 [5]1998년에 Compaq에 매각되었습니다.이미 인텔의 x86 고객인 Compaq는 곧 출시될 Hewlett-Packard/Intel Itanium 아키텍처를 위해 Alpha를 단계적으로 폐지한다고 발표했으며 2001년에 [6]Alpha의 모든 지적 재산을 인텔에 매각하여 사실상 제품을 폐기했습니다.Hewlett-Packard는 2002년에 Compaq를 인수하여 2004년까지 기존 제품군을 계속 개발하고 2007년 [7]4월까지 주로 기존 고객층을 대상으로 Alpha 기반 시스템을 판매하였습니다.

역사

프리즘

Alpha는 Parallel Reduced Instruction Set Machine(PRISM)이라는 이름의 초기 RISC 프로젝트에서 등장했으며, 그 자체는 여러 초기 프로젝트의 산물입니다.PRISM은 Unix와 유사한 애플리케이션과 디지털의 기존 VAX/VMS 소프트웨어를 지원하는 유연한 설계를 의도했습니다.MICA라는 새로운 운영체제는 공통 커널 상에서 ULTRIX 인터페이스와 VAX/VMS 인터페이스를 모두 지원하므로 두 플랫폼의 소프트웨어를 PRISM [8]아키텍처로 쉽게 이식할 수 있습니다.

1985년에 시작된 PRISM 설계는 컴퓨터 시장의 변화에 따라 개발 과정에서 지속적으로 변경되어 도입이 지연되었습니다.1987년 여름이 되어서야 마이크로프로세서 형식의 초기 설계 중 64비트 설계로 결정되었습니다.1987년 10월, Sun Microsystems는 새로운 SPARC 프로세서를 사용한 최초의 워크스테이션인 Sun-4를 발표했습니다.Sun-4는 Motorola 68020을 사용하는 최신 Sun-3 디자인 및 DEC의 유닉스 제품보다 약 3~4배 빠르게 작동합니다.PRISM은 다시 32비트 부품으로 재편성되어 UNIX 시장을 직접 겨냥하고 있습니다.이로 인해 설계가 [9]더욱 지연되었습니다.

Palo Alto 사무실의 한 팀은 PRISC의 납기가 계속 늦어지는 것을 보고 다른 RISC 프로세서를 사용하여 자체 워크스테이션을 설계하기로 결정했습니다.실사 후, MIPS R2000을 선택하고,[10] 90일 이내에 Ultrix를 실행하는 워크스테이션을 구축했습니다.이것은 1988년 7월 경영자 회의에서 정점에 도달한 회사 내부의 신랄한 논쟁을 촉발시켰다.PRISM은 R2000보다 빠른 것처럼 보였지만 R2000 머신은 PRISM보다 1년 빠른 1989년 1월에 출시될 수 있습니다.이 제안이 받아들여졌을 때, PRISM의 원래 역할 2개 중 하나는 사라졌습니다.VMS PRISM을 만들기로 한 결정은 이 시점에서 이미 끝났기 때문에 남은 역할은 없었습니다.프리즘은 미팅에서 [11]취소되었습니다.

RISCy VAX

회의가 결렬되자 Ken Olsen이 Bob Supnik에게 연락을 취했는데, Ken Olsen은 RISC 칩이 VAX 라인에 미래에 위협이 될 것으로 보인다고 말했습니다.그는 Supnik에게 미래의 RISC [9]시스템과의 경쟁력을 유지하기 위해 VAX를 사용하여 무엇을 할 수 있는지 검토해 달라고 요청했습니다.

이것은 "RISCy VAX" 팀의 결성으로 이어졌다.그들은 처음에 세 가지 개념을 고려했다.하나는 VAX 명령 집합 아키텍처(ISA)의 축소 버전으로, RISC와 같은 시스템에서 실행되며 보다 복잡한 VAX 명령은 시스템 서브루틴에 남겨집니다.또 다른 개념은 기존 VAX 코드를 자체 ISA로 즉시 변환하여 CPU 캐시에 저장하는 순수 RISC 시스템입니다.마지막으로 VAX ISA 전체를 실행하는 CISC 프로세서가 훨씬 더 빨라질 가능성도 있었습니다.유감스럽게도 이러한 접근 방식 모두 오버헤드를 초래하여 네이티브 RISC [12]코드를 실행하는 순수 RISC 머신과는 경쟁할 수 없습니다.

그 후 기존 VAX 원칩 솔루션 중 하나와 RISC 칩을 고성능 요구에 사용되는 코프로세서로 결합하는 하이브리드 시스템을 검토했습니다.이러한 연구들은 시스템이 저성능 부품에 의해 불가피하게 방해받고 설득력 있는 이점을 제공하지 못할 것이라는 것을 시사했다.바로 이 시점에서 Nancy Kronenberg는 사람들이 VAX가 아닌 VMS를 실행하고 있으며 VMS는 인터럽트 및 메모리 페이징 모델링에 기초한 하드웨어 의존성이 적다고 지적했습니다.이러한 모델의 작은 부분이 보존되어 있는 한, VMS를 RISC 칩에 이식할 수 없는 것은 납득할 만한 이유가 없는 것 같습니다.이 개념에 대한 추가 연구는 이것이 실행 가능한 [12]접근법이었음을 시사했다.

Supnik은 1989년 2월에 그 결과 보고서를 전략 태스크 포스에 제출했다.두 가지 질문이 제기되었습니다.그 결과 발생하는 RISC 설계가 Unix 시장의 퍼포먼스 리더가 될 수 있는가?또, 머신이 오픈 스탠다드가 될 필요가 있는가?그 결과, PRISM 아키텍처를 적절히 수정하여 채택하기로 결정했습니다.이는 CMOS CVAX의 성공적인 구현의 후속 조치인 "EVAX" 개념이 되었습니다.경영진이 조사 결과를 받아들였을 때, 그들은 프로젝트에 좀 더 중립적인 이름을 붙이기로 결정했고, "VAX"를 제거했고,[13] 결국 알파로 결정을 내렸습니다.곧이어 VMS 포트에서 새로운 [14]아키텍처에 대한 작업이 시작되었습니다.

알파

새로운 디자인은 대부분의 기본 PRISM 개념을 사용하지만 VMS와 VMS 프로그램을 변환 없이 합리적인 속도로 실행할 수 있도록 재조정되었습니다.Alpha 명령어 세트 설계자는 Richard L.사이트와 리처드 T.Witek.[15] PRISM의 Epicode는 Alpha의 PAL코드로 개발되어 플랫폼 및 프로세서 구현 고유의 기능에 대한 추상화된 인터페이스를 제공합니다.

Alpha가 마이크로프로세서 업계에 공헌한 주된 이유는 아키텍처가 아니라 [16]구현입니다.당시(현재와 같이) 마이크로칩 산업은 자동화된 설계 및 배치 도구가 주를 이뤘습니다.Digital의 칩 설계자들은 복잡한 VAX 아키텍처를 다루기 위해 정교한 수동 회로 설계를 계속 추구했습니다.Alpha 칩은 보다 단순하고 깨끗한 아키텍처에 적용된 수동 회로 설계가 보다 자동화된 설계 시스템에서 가능한 것보다 훨씬 더 높은 작동 주파수를 가능하게 한다는 것을 보여줍니다.이러한 칩은 마이크로프로세서 설계 커뮤니티 내에서 커스텀 회로 설계의 부흥을 가져왔다.

원래 알파 프로세서는 DEC칩 21x64 [17]시리즈로 명명되었으며 1990년대 중반에 "DEC칩"이 "알파"로 대체되었다.처음 두 자리 숫자 "21"은 21세기를 나타내고 마지막 두 자리 숫자 "64"[17]는 64비트를 나타냅니다.Alpha는 처음부터 64비트로 설계되었으며 32비트 버전은 없습니다.가운데 숫자는 Alpha 아키텍처의 생성에 해당합니다.내부적으로도 Alpha 프로세서는 EV 번호로 식별되었으며, EV는 공식적으로는 "Extended VAX"를 의미하지만 "Electric Vlasic"이라는 유머러스한 의미를 가지고 있어 Western Research [18]Lab의 Electric Pitchle 실험에 경의를 표합니다.

개량된 모델

알파 칩의 처음 몇 세대는 그 시대의 가장 혁신적인 것들이었다.

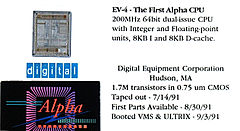

- 첫 번째 버전인 Alpha 21064 또는 EV4는 작동 주파수가 고출력 ECL 미니컴퓨터와 메인프레임에 필적하는 최초의 CMOS 마이크로프로세서입니다.

- 두 번째 모델인 21164 또는 EV5는 대용량 2차 캐시를 [19]온칩에 배치한 최초의 마이크로프로세서입니다.

- 세 번째 제품인 21264 또는 EV6는 높은 동작 주파수와 보다 복잡한 순서 외 실행 마이크로아키텍처를 조합한 최초의 마이크로프로세서입니다.

- 21364 또는 EV7은 온칩 메모리 컨트롤러를 [20]탑재한 최초의 고성능 프로세서입니다.

- 제작되지 않은 21464 또는 EV8은 동시 멀티스레딩을 최초로 포함시켰지만, 이 버전은 DEC를 Compaq에 매각한 후 취소되었습니다.EV9로 불렸을 것으로 보이는 타란툴라 연구 프로젝트는 벡터 프로세서 유닛을 [21]탑재한 최초의 알파 프로세서였을 것이다.

DEC 관계자의 계속적인 보고에 의하면, 프로세서의 AXP 태그의 선택은, VAX 상표의 [22]대실패에 시달리고 있던 DEC의 법무 부문에 의해서 행해진 것이라고 합니다.오랜 검색 끝에 "AXP"라는 태그는 전혀 문제가 없는 것으로 밝혀졌다.컴퓨터 업계에서는 AXP라는 약자가 "Almost eXactly PRISM"[citation needed]이라는 뜻이라는 우스갯소리가 돌기 시작했다.

설계 원리

Alpha 아키텍처는 고성능 설계를 의도했습니다.Digital은 25년 동안 1,000배의 성능 향상을 지원하는 아키텍처를 의도했습니다.이를 위해 여러 명령 문제, 클럭 속도 또는 멀티프로세싱을 지연시키는 아키텍처 기능이 모두 제거되었습니다.그 결과 알파에는 다음이 없습니다.

상태 코드

Alpha에는 상태 레지스터에서 잠재적인 병목 현상을 제거하기 위한 정수[25] 명령의 상태 코드가 없습니다.64비트에 맞지 않는 2개의 숫자를 추가하는 등 오버플로가 발생하는 명령에서는 32비트 또는 64비트의 최하위 비트를 수신처 레지스터에 씁니다.어느 피연산자와도 부호 없는 비교를 수행하여 결과가 어느 피연산자보다 작은지 확인합니다.테스트가 참일 경우 값 1은 수신처 레지스터의 최하위 비트에 쓰여져 상태를 나타냅니다.

레지스터

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

아키텍처는 프로그램 카운터, 2개의 잠금 레지스터 및 부동소수점 제어 레지스터(FPCR) 외에 32개의 정수 레지스터와 32개의 부동소수점 레지스터 세트를 정의합니다.또한 구현에 필요한 경우에만 구현된 선택 사항인 레지스터도 정의합니다.마지막으로 PAL code의 레지스터를 정의합니다.

정수 레지스터는 R0 ~ R31로 나타내며 부동소수점 레지스터는 F0 ~ F31로 나타냅니다.R31 및 F31 레지스터는 0에 유선 연결되며 이러한 레지스터에 대한 지침에 의한 쓰기는 무시됩니다.디지털은 복합 레지스터 파일을 사용하는 것을 고려했지만, 분할 레지스터 파일은 2칩 구현이 각 칩에 레지스터 파일을 배치하고 정수 전용 구현이 가능하여 부동소수점 레지스터 파일을 포함하는 부동소수점 레지스터 파일을 생략할 수 있기 때문에 더 나은 것으로 판단되었다.또한 읽기 및 쓰기 포트의 수가 감소했기 때문에 분할 레지스터 파일이 여러 명령 문제에 더 적합하다고 판단되었습니다.레지스터 파일당 레지스터 수도 고려되었으며 32개 및 64개가 경쟁업체로 지정되었습니다.디지털은 32개의 레지스터가 더 적합하다는 결론을 내렸습니다. 다이 공간이 적게 필요하기 때문에 클럭 주파수가 향상됩니다.32개의 레지스터가 최소 8방향 명령 문제를 지원할 수 있기 때문에 이 레지스터 수는 성능 및 미래 성장에 있어 큰 문제가 되지 않는 것으로 간주되었습니다.

프로그램 카운터는 64비트 레지스터로 롱워드 정렬 가상 바이트 주소를 포함합니다.즉, 프로그램카운터의 하위2비트는 항상 0입니다.명령이 디코딩되면 PC는 다음 명령의 주소로 4씩 증가합니다.멀티프로세서 지원을 위한 로드록 및 스토어 조건부 명령에 의해 잠금 플래그 및 잠금 물리 주소 레지스터가 사용됩니다.Floating Point Control Register(FPCR; 부동소수점 제어 레지스터)는 IEEE 754 준거 부동소수점 하드웨어와 함께 Alpha 구현에 사용되는 아키텍처에 의해 정의된 64비트 레지스터입니다.

데이터형

Alpha 아키텍처에서 바이트는 8비트 데이텀(옥텟), 워드는 16비트 데이텀, 롱워드 32비트 데이텀, 쿼드워드 64비트 데이텀, 옥타워드는 128비트 데이텀으로 정의됩니다.

Alpha 아키텍처는 원래 다음과 같은 6가지 데이터 유형을 정의했습니다.

- 쿼드워드(64비트) 정수

- 롱워드(32비트) 정수

- IEEE T-Floating Point(이중 정밀도, 64비트)

- IEEE S 플로팅 포인트(단정도, 32비트)

Alpha 이전의 32비트 아키텍처인 VAX와의 호환성 수준을 유지하기 위해 다음 두 가지 부동소수점 데이터 유형이 포함되어 있습니다.

- VAX G 플로팅 포인트 (이중 정밀도, 64비트)

- VAX F-플로팅 포인트 (단정도, 32비트)

- VAX H 부동소수점([26]정밀도 4분의 1, 128비트)은 지원되지 않지만, 또 다른 128비트 부동소수점 옵션인 X 부동소수점 옵션은 Alpha에서 사용할 수 있지만 [27]VAX에서는 사용할 수 없습니다.

H와 X는 비슷하지만 동일하지는 않다고 기술되어 있습니다.H 플로팅용 소프트웨어 에뮬레이션은 DEC migrate라는 이름의 소스 코드레벨 컨버터와 마찬가지로 DEC부터 사용할 수 있습니다.

기억

Alpha에는 메모리 분할이 없는 64비트 선형 가상 주소 공간이 있습니다.구현에서는 최소 43비트의 작은 가상 주소 공간을 구현할 수 있습니다.사용되지 않는 비트는 TLB 등의 하드웨어에서는 구현되지 않았지만 아키텍처에서는 가상 주소 공간이 더 크거나 완전한 구현과의 소프트웨어 호환성을 확보하기 위해 구현이 필요합니다.

명령 형식

Alpha ISA에는 32비트의 고정 명령 길이가 있습니다.6가지 명령 형식이 있습니다.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 유형 |

| 오퍼코드 | 라 | Rb | 미사용 | 0 | 기능. | Rc | 정수 연산 | |||||||||||||||||||||||||

| 오퍼코드 | 라 | 리터럴 | 1 | 기능. | Rc | 정수 연산, 리터럴 | ||||||||||||||||||||||||||

| 오퍼코드 | 라 | Rb | 기능. | Rc | 부동소수점 연산 | |||||||||||||||||||||||||||

| 오퍼코드 | 라 | Rb | 변위 | 메모리 포맷 | ||||||||||||||||||||||||||||

| 오퍼코드 | 라 | 변위 | 분기 형식 | |||||||||||||||||||||||||||||

| 오퍼코드 | 기능. | CALL_PAL 형식 | ||||||||||||||||||||||||||||||

정수 연산 형식은 정수 명령에서 사용됩니다.여기에는 6비트 opcode 필드가 포함되어 그 뒤에 Ra 필드가 표시됩니다.Ra 필드는 첫 번째 오퍼랜드를 포함하는 레지스터를 지정하고 Rb 필드는 두 번째 오퍼랜드를 포함하는 레지스터를 지정합니다.다음으로 사용되지 않고 예약된 3비트 필드입니다.1비트 필드에는 이 형식을 정수 리터럴 형식과 구별하는 "0"이 포함됩니다.이어서 7비트 함수필드를 opcode와 조합하여 조작을 지정합니다.마지막 필드는 Rc 필드입니다.이 필드는 계산 결과를 쓸 레지스터를 지정합니다.레지스터 필드는 모두 5비트 길이로 32개의 고유 위치, 즉 32개의 정수 레지스터를 처리하는 데 필요합니다.

정수 리터럴 형식은 리터럴을 오퍼랜드 중 하나로 사용하는 정수 명령에서 사용됩니다.형식은 5비트 Rb 필드 및 사용되지 않는 공간의 3비트를 64비트 오퍼랜드로 제로 확장되는8비트 리터럴필드로 대체하는 것을 제외하고 정수 연산 형식과 동일합니다.

부동소수점 연산 형식은 부동소수점 명령에서 사용됩니다.이는 정수 연산 형식과 비슷하지만 정수 연산 형식으로 예약된 리터럴 및 사용되지 않는 비트를 사용하여 11비트 함수 필드를 사용할 수 있습니다.

메모리 형식은 주로 로드 및 저장 명령에 의해 사용됩니다.6비트 opcode 필드, 5비트 Ra 필드, 5비트 Rb 필드 및 16비트 치환 필드가 있습니다.

분기 명령에는 6비트 opcode 필드, 5비트 Ra 필드 및 21비트 치환 필드가 있습니다.Ra 필드는 조건부 분기 명령으로 테스트할 레지스터를 지정하고, 조건이 충족되면 프로그램 카운터에 변위 필드의 내용을 추가하여 프로그램 카운터를 업데이트합니다.변위 필드에는 부호 있는 정수가 포함되어 있으며, 정수 값이 양수인 경우 분기가 취해진 경우 프로그램 카운터가 증가합니다.정수 값이 음수인 경우 분기가 취득되면 프로그램카운터가 감소합니다.따라서 분기의 범위는 ±1 Mi 명령 또는 ±4 MiB입니다.Alpha Architecture는 아키텍처의 미래 지향적인 목표의 일부로서 광범위한 범위로 설계되었습니다.

CALL_PAL 포맷은 Call_PAL에서 사용됩니다.CALL_PAL명령: PAL code 서브루틴 호출에 사용됩니다.형식은 opcode 필드를 유지하지만 다른 필드는 PAL 서브루틴을 지정하는 정수를 포함하는 26비트 함수 필드로 대체됩니다.

명령 집합

제어 절차

제어 지침은 조건부 및 무조건적 분기와 점프로 구성됩니다.조건부 및 무조건 브랜치명령어는 분기명령어 형식을 사용하고 점프명령어는 메모리명령어 형식을 사용합니다.

조건부 브랜치는 레지스터의 최하위 비트가 설정되어 있는지 클리어되어 있는지 테스트하거나 부호 있는 쿼드워드로 레지스터를 0으로 비교하고 지정된 조건이 참일 경우 분기합니다.레지스터를 0과 비교할 때 사용할 수 있는 조건은 평등, 불평등, 작음, 작음 또는 같음, 크거나 같음, 크다입니다.새 주소는 21비트 변위를 확장한 롱워드 정렬 및 부호로 계산되며 조건부 분기 뒤에 오는 명령 주소에 추가됩니다.

무조건 브랜치는 조건부 브랜치와 동일한 방법으로 계산된 새 주소로 프로그램 카운터를 업데이트합니다.또, 무조건 브랜치 후의 명령의 주소도 레지스터에 저장합니다.이러한 지침은 두 가지가 있으며 분기 예측 하드웨어에 제공되는 힌트만 다릅니다.

점프 지침은 4가지가 있다.이들 모두 동일한 동작을 수행하여 점프 후 명령의 주소를 저장하고 프로그램 카운터에 레지스터에서 새 주소를 제공합니다.분기 예측 하드웨어에 제공되는 힌트가 다릅니다.사용되지 않은 변위 필드가 이 용도로 사용됩니다.

정수 산술

정수 산술 명령에서는 롱워드 및 쿼드워드에 대한 덧셈, 곱셈 및 뺄셈과 쿼드워드에 대한 비교를 수행합니다.설계자는 하드웨어에서의 분할 구현이 단순성에 반한다고 생각했기 때문에 분할에 대한 지침은 없습니다.표준 더하기 및 빼기 명령 외에도 확장 버전이 있습니다.이러한 버전은 두 번째 피연산자를 더하기 또는 빼기 전에 두 번째 피연산자를 왼쪽으로 두세 비트 이동합니다.Multiply Longword 명령과 Multiply Quadword 명령은 각각 64비트 또는 128비트 결과의 최하위 32비트 또는 64비트를 수신처 레지스터에 씁니다.가장 중요한 반을 얻는 것이 유용하므로 UMULH(Unsigned Multiply Quadword High) 명령이 제공됩니다.UMULH는 다정밀 산술 및 나눗셈 알고리즘을 구현하기 위해 사용됩니다.결과의 가장 중요한 절반을 반환하는 곱셈 명령의 개념은 PRISM에서 따왔다.

긴 워드로 동작하는 명령어는 레지스터의 가장 중요한 절반을 무시하고 32비트 결과는 대상 레지스터에 쓰기 전에 부호 확장됩니다.기본적으로는 덧셈, 곱셈 및 뺄셈 명령은 UMULH 및 축소판 덧셈 및 뺄셈을 제외하고 오버플로에 트랩되지 않습니다.이러한 기능이 필요한 경우 오버플로우 검출 및 오버플로우 시 트랩을 실행하는 이러한 명령 버전이 제공됩니다.

비교 지침은 두 레지스터 또는 레지스터와 리터럴을 비교하고 지정된 조건이 참이면 대상 레지스터에 '1'을, 그렇지 않으면 '0'을 씁니다.그 조건들은 평등, 불평등, 같거나 같거나 작거나 그 이하이다.앞의 두 조건을 지정하는 지침을 제외하고 서명된 버전과 서명되지 않은 버전을 비교하는 방법이 있습니다.

정수 연산 명령어는 정수 연산 명령 형식을 사용합니다.

논리 및 시프트

논리 명령은 정수 레지스터에서 비트 논리 연산 및 조건부 이동을 수행하기 위한 명령으로 구성됩니다.비트 논리 명령은 두 개의 레지스터 또는 레지스터와 리터럴 사이에서 AND, NAND, NOR, OR, XNOR 및 XOR을 수행합니다.조건부 이동 명령은 레지스터를 부호 있는 4단어로 테스트하여 0으로 설정하고 지정된 조건이 참일 경우 이동합니다.지정된 조건은 평등, 불평등, 이하, 이하, 이하, 초과 및 초과입니다.시프트 명령은 산술적 우측 시프트와 논리적인 좌측 및 우측 시프트를 수행합니다.이동량은 레지스터 또는 리터럴로 지정됩니다.논리 및 시프트 명령은 정수 연산 명령 형식을 사용합니다.

내선번호

바이트 워드 확장자(BWX)

이후 알파벳에는 8비트 및 16비트 데이터 유형을 조작하는 명령어 세트인 바이트 워드 확장자가 포함됩니다.이러한 순서는, 21164A(EV56) 마이크로프로세서에 최초로 도입되어 이후의 모든 실장에 기재되어 있습니다.이러한 명령어는 이전에는 여러 명령을 구현해야 했던 작업을 수행하므로 코드 밀도와 특정 애플리케이션의 성능이 향상됩니다.또한 BWX는 x86 머신 코드의 에뮬레이션과 디바이스 드라이버의 기입을 [28]용이하게 합니다.

| 니모닉 | 설명 |

|---|---|

LDBU | 메모리에서 레지스터로의 제로 확장 바이트 로드 |

LDWU | 메모리에서 레지스터로 제로 확장 워드 로드 |

SEXTB | 서명 확장 바이트 |

SEXTW | 단어 확장 서명 |

STB | 레지스터에서 메모리로 바이트 저장 |

STW | 레지스터에서 메모리로 단어 저장 |

모션 비디오 명령(MVI)

모션 비디오 명령(MVI)은 단일 명령, 다중 데이터(SIMD)[29] 작업에 대한 명령을 추가한 Alpha ISA의 명령 세트 확장입니다.MVI를 시간순으로 실장하는 알파 실장은 Alpha 21164PC(PCA56 및 PCA57), Alpha 21264(EV6) 및 Alpha 21364(EV7)입니다.MIPS의 MDMX나 SPARC의 Visual Instruction Set과 같이 같은 기간의 다른 대부분의 SIMD 명령 집합과 달리, 그러나 PA-RISC의 Multimedia Acceleration eXtensions(MAX-1, MAX-2)와 같이, MVI는 정수에 저장된 몇 가지 명령으로 구성된 단순한 명령 집합이었다.

MVI의 심플한 이유는 두 가지입니다.우선, Digital은 Alpha 21164가 이미 소프트웨어를 통해 DVD 디코딩을 실행할 수 있기 때문에 하드웨어 프로비저닝을 필요로 하지 않지만 MPEG-2 인코딩에서는 비효율적이라고 판단했습니다.두 번째 이유는 구현의 빠른 사이클 타임을 유지하기 위한 요건입니다.많은 명령어를 추가하면 명령어 디코드 로직이 복잡해지고 확대되어 구현의 클럭 주파수가 감소합니다.

MVI는 13개의 명령으로 구성됩니다.

| 니모닉 | 설명 |

|---|---|

MAXSB8 | 벡터 부호 바이트 최대값 |

MAXSW4 | 벡터 부호 단어 최대값 |

MAXUB8 | 벡터 부호 없는 바이트 최대값 |

MAXUW4 | 벡터 부호 없는 단어 최대값 |

MINSB8 | 벡터 부호 바이트 최소값 |

MINSW4 | 벡터 부호 단어 최소값 |

MINUB8 | 벡터 부호 없는 최소 바이트 |

MINUW4 | 벡터 부호 없는 단어 최소값 |

PERR | 픽셀 오류 |

PKLB | 긴 단어를 바이트로 팩 |

PKWB | 단어를 바이트로 팩하다 |

UNPKBL | 긴 단어로 바이트 언팩 |

UNPKBW | 바이트를 단어로 언팩 |

부동 소수점 확장(FIX)

부동소수점 확장(FIX)은 Alpha 아키텍처의 확장입니다.부동소수점 제곱근 및 정수 레지스터와 부동소수점 레지스터 간의 데이터 전송에 대한 9가지 명령이 소개되어 있습니다.Alpha 21264(EV6)는 이러한 명령을 구현하는 최초의 마이크로프로세서입니다.

| 니모닉 | 설명 |

|---|---|

FTOIS | 부동 소수점에서 정수 레지스터로 이동, S_floating |

FTOIT | 부동소수점에서 정수 레지스터로 이동, T_floating |

ITOFF | 부동소수점 레지스터로 정수 이동, F_floating |

ITOFS | 부동소수점 레지스터로 정수 이동, S_floating |

ITOFT | 부동소수점 레지스터로 정수 이동, T_floating |

SQRTF | 제곱근 F_floating |

SQRTG | 제곱근 G_floating |

SQRTS | 제곱근 S_floating |

SQRTT | 제곱근 T_floating |

확장 수(CIX)

Count Extensions(CIX; 카운트 확장)는 비트를 카운트하기 위한 3가지 명령을 도입하는 아키텍처의 확장입니다.이러한 명령은 정수 산술 명령으로 분류됩니다.그것들은 Alpha 21264A(EV67)에 최초로 실장되었습니다.

| 니모닉 | 설명 |

|---|---|

CTLZ | 선두 0의 카운트 |

CTPOP | 인구수 |

CTTZ | 후행 제로 수 |

실장

발표 당시 알파는 향후 25년 동안 건축물로 알려졌습니다.하지만 알파는 꽤 긴 삶을 살았다.첫 번째 버전인 Alpha 21064(EV4라는 명칭)는 1992년 11월에 최대 192MHz로 실행되었으며, 몇 달 후 다이(EV4S, 0.75µm에서 0.675µm로 축소)가 200MHz로 실행되었습니다.64비트 프로세서는 다른 RISC 설계와 마찬가지로 슈퍼파이프라인과 슈퍼스칼라 설계였지만 그럼에도 불구하고 이들 모두를 능가했고 DEC는 세계에서 가장 빠른 프로세서라고 선전했습니다.거대한 중앙집중식 클럭 회로와 같은 허드슨 설계팀의 특징인 회로 설계에 세심한 주의를 기울였기 때문에 마이크로 아키텍처는 다른 RISC 칩과 상당히 비슷했지만 CPU를 더 빠른 속도로 실행할 수 있었습니다.이에 비해 가격이 저렴한 인텔 Pentium은 이듬해 봄 출시 당시 66MHz로 동작했다.

Alpha 21164 또는 EV5는 1995년에 최대 333MHz의 프로세서 주파수로 출시되었습니다.1996년 7월에는 500MHz로, 1998년 3월에는 666MHz로 속도가 향상되었습니다.또한 1998년에는 Alpha 21264(EV6)가 450MHz로 출시되어 최종적으로 (2001년에는 21264C/EV68CB로) 1.25GHz에 도달했습니다.2003년에 Alpha 21364 또는 EV7 Marvel이 출시되었으며, 기본적으로 1.6GB/s[a] 프로세서 간 통신 링크를 4개 갖춘 EV68 코어로, 1GHz 또는 1.15GHz의 멀티프로세서 시스템 성능을 향상시켰습니다.

1996년 알파칩 생산은 삼성전자에 허가됐다.Compaq가 Digital을 사들인 후, 대부분의 Alpha 제품은 Samsung과 Compaq가 출자한 민간 회사인 API NetWorks, Inc.(구 Alpha Processor Inc.)와 함께 배치되었습니다.2001년 10월, Microway는 API NetWorks의 Alpha 베이스 제품 라인의 독점 판매 및 서비스 프로바이더가 되었습니다.

2001년 6월 25일 Compaq는 Alpha가 인텔의 Itanium을 위해 2004년까지 단계적으로 폐지되고 계획되었던 EV8 칩을 취소하고 Alpha의 모든 지적 재산을 [6]인텔에 매각할 것이라고 발표했습니다.Hewlett-Packard는 2002년에 Compaq와 합병했다.HP는 Alpha 시리즈의 개발이 EV7z라는 이름의 1.3GHz EV7의 출시를 포함하여 몇 년 더 계속될 것이라고 발표했다.이것은 Alpha의 마지막 반복이며, 0.13µm EV79도 취소된다.

Alpha는 또한 Compaq의 기업 연구팀과 Western Research Laboratory and Systems Research Center의 논스톱 하드웨어 개발 그룹이 개발한 연구 프로토타입인 Piranha에도 구현됩니다.Piranha는 트랜잭션 처리 워크로드를 위한 멀티코어 설계로, 8개의 단순 코어를 포함합니다.2000년 [30]6월에 개최된 제27회 국제 컴퓨터 아키텍처 심포지엄에서 설명되었습니다.

모델 이력

| 모델 | ISA | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| EV4 | 21064 | 1992 | 100–200 | 0.75 | 1.68 | 234 | 290 | 30 | 3.3 | 8 | 8 | – | 128 KB ~ 16 MB | ||

| EV4S | 21064 | 1993 | 100–200 | 0.675 | 1.68 | 186 | 290 | 27 | 3.3 | 8 | 8 | – | 128 KB ~ 16 MB | ||

| EV45 | 21064A | 1994 | 200–300 | 0.5 | 2.85 | 164 | 33 | 3.3 | 16 | 16 | – | 256 KB ~16 MB | |||

| LCA4 | 21066 | 1993 | 100–166 | 0.675 | 1.75 | 209 | 21 | 3.3 | 8 | 8 | – | ||||

| LCA4 | 21068 | 1994 | 66 | 0.675 | 1.75 | 209 | 9 | 3.3 | 8 | 8 | – | ||||

| LCA45 | 21066A | 1994 | 100–266 | 0.5 | 1.8 | 161 | 23 | 3.3 | 8 | 8 | – | ||||

| LCA45 | 21068A | 1994 | 100 | 0.5 | 1.8 | 161 | 3.3 | 8 | 8 | – | |||||

| EV5 | 21164 | 1995 | 266–500 | 0.5 | 9.3 | 299 | 296 | 56 | 3.3/2.5 | 8 | 8 | 96 KB | 최대 64 MB | R | |

| EV56 | 21164A | 1996 | 366~666[1] | 0.35 | 9.66[1] | 209 | 31 ~ 55[1] | 3.3/2.5[1] | 8 | 8 | 96 KB | 최대 64 MB | R,B | ||

| PCA56 | 21164PC | 1997 | 400–533 | 0.35 | 3.5 | 141 | 264 | 26–35 | 3.3/2.5 | 8 | 16 | – | 512 KB ~4 MB | R,B,M | |

| PCA57 | 21164PC | 600–666 | 0.28 | 5.7 | 101 | 283 | 18–23 | 2.5/2.0 | 16 | 32개[1] | – | 512 KB ~4 MB | R,B,M | ||

| EV6 | 21264 | 1998 | 450–600 | 0.35 | 15.2 | 314 | 389 | 73 | 2.0 | 64 | 64 | – | 2 ~ 8 MB | R,B,M,F | |

| EV67 | 21264A | 1999 | 600–750 | 0.25 | 15.2 | 210 | 389 | 2.0 | 64 | 64 | – | 2 ~ 8 MB | R,B,M,F,C | ||

| EV68AL | 21264B | 2001 | 800–833 | 0.18 | 15.2 | 125 | 1.7 | 64 | 64 | – | 2 ~ 8 MB | R,B,M,F,C,T | |||

| EV68CB | 21264C | 2001 | 1000–1250 | 0.18 | 15.2 | 125 | 65–75 | 1.65 | 64 | 64 | – | 2 ~ 8 MB | R,B,M,F,C,T | ||

| EV68CX | 21264D | 1.65 | 64 | 64 | – | 2 ~ 8 MB | R,B,M,F,C,T | ||||||||

| EV7 | 21364 | 2003 | 1000–1150 | 0.18 | 130 | 397 | 125 | 1.5 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| EV7z | 21364 | 2004 | 1300 | 0.18 | 130 | 397 | 125 | 1.5 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| 취소된 | |||||||||||||||

| EV78/EV79 | 21364A | 2004년 예정 | 1700 | 0.13 | 152 | 300 | 120 | 1.2 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| EV8 | 21464 | 2003년 예정 | 1200–2000 | 0.125 | 250 | 420 | 1800 | ?? | 1.2 | 64 | 64 | 3 MB | – | R,B,M,F,C,T | |

| 모델 | ISA | ||||||||||||||

- ISA 확장 기능

- R – 무한대 및 음의 [31]무한대로 반올림하기 위한 하드웨어 지원.

- B – BWX (바이트/워드 확장자)메모리 및 I/O로부터의8비트 및 16비트 조작을 가능하게 하는 명령 추가

- M – MVI, "멀티미디어" 명령

- F – FIX, 정수와 부동소수점 레지스터 간 및 제곱근에 대한 데이터 이동 지침

- C – CIX, 비트 카운트 및 검색 절차

- T – 첫 번째 잠금 획득 시 성능 향상을 위한 수정 의도를 가진 프리페치 지원

성능

Alpha 기반 시스템의 성능을 비교하기 위해 SPEC(Standard Performance Evaluation Corporation)의 퍼포먼스 번호(SPECint95, SPECfp95)를 아래에 나타냅니다.SPEC 결과는 CPU뿐만 아니라 전체 컴퓨터 시스템(CPU, 버스, 메모리, 컴파일러 옵티마이저)의 측정된 성능을 보고한다고 주장합니다.또한 벤치마크와 규모가 1992년에서 1995년으로 변경되었음을 유의하십시오.다만, 이 수치는, 현재의 HP(64 비트)나 인텔 베이스의 제품(32 비트)에 비해, Alpha 아키텍처(64 비트)의 퍼포먼스의 대략적인 인상을 주고 있습니다.아마도 가장 분명한 경향은 인텔이 정수 퍼포먼스에서는 항상 Alpha에 상당히 근접할 수 있지만 부동소수점 퍼포먼스에서는 상당한 차이가 있었다는 것입니다.한편 HP(PA-RISC)도 상당히 Alpha에 가깝지만 이들 CPU는 상당히 낮은 클럭레이트(MHz)로 동작하고 있습니다.이 표에는 소비전력과 CPU 가격이라는 두 가지 중요한 값이 없습니다.

|

|

알파 기반 시스템

1세대 DEC Alpha 기반 시스템은 DEC 3000 AXP 시리즈워크스테이션과 로우엔드 서버, DEC 4000 AXP 시리즈 미드레인지 서버 및 DEC 7000 AXP 및 10000 시리즈 하이엔드 서버로 구성됩니다.DEC 3000 AXP 시스템은 이전 MIPS 기반 DEC 스테이션 모델과 동일한 TURBOChannel 버스를 사용하는 반면 4000은 Futurebus+를 기반으로 하고 7000/10000은 대응하는 VAX 모델과 아키텍처를 공유합니다.

또, DEC는, 확장 산업 표준 아키텍처(EISA) 버스, DECpc AXP 150(코드명 Jensen, DEC 2000 AXP)를 탑재한 PC(PC) 구성 Alpha 워크스테이션을 생산했습니다.이것은 Windows NT를 지원하는 최초의 Alpha 시스템입니다.DEC는 이후 21164 프로세서를 탑재한 Celebis XL 및 디지털 퍼스널 워크스테이션 PC 제품군의 Alpha 버전을 생산했습니다.

디지털은 또한 임베디드 및 산업용 VMEbus를 기반으로 한 싱글 보드 컴퓨터를 생산했습니다.제1세대에는 21068 기반의 AXPvme 64 및 AXPvme 64LC 및 21066 기반의 AXPvme 160이 포함됩니다.이것들은 1994년 3월 1일에 도입되었습니다.AXPMe 100, AXPMe 166, AXPMe 230 등의 최신 모델은 21066A 프로세서를 기반으로 하며 Alpha VME 4/224 및 Alpha VME 4/288은 21064A 프로세서를 기반으로 합니다.마지막 모델인 Alpha VME 5/352 및 Alpha VME 5/480은 21164 프로세서를 기반으로 합니다.

21066 칩은 DEC Multia VX40/41/42 콤팩트 워크스테이션 및 Tadpole Technology의 알파북1 노트북에 사용됩니다.

1994년 DEC는 새로운 범위의 AlphaStation 및 AlphaServer 시스템을 출시했습니다.이들은 21064 또는 21164 프로세서를 사용하며 PCI 버스, VGA 호환 프레임 버퍼 및 PS/2 스타일의 키보드와 마우스를 도입했습니다.AlphaServer 8000 시리즈는 DEC 7000/10000 AXP를 대체하며 XMI 및 FutureBus+ 버스도 사용합니다.

AlphaStation XP1000은 21264 프로세서를 탑재한 최초의 워크스테이션입니다.21264 기반의 최신 Alpha Server/Station 모델은 DS(부문별 서버), ES(엔터프라이즈 서버), GS(글로벌 서버) 패밀리로 분류됩니다.

최종 21364 칩은 AlphaServer ES47, ES80 및 GS1280 모델과 AlphaStation ES47에 사용됩니다.

OEM 메인보드는 [32]DEC가 제조한 것으로는 21066 및 21068 기반의 AXPci 33 "NoName", 21164 기반의 AlphaPC 164 및 AlphaPC 164LX, 21164 PC 기반의 AlphaPC 164LX, 164 PC 기반의 AlphaPC 164LX 등입니다.Samsung이나 API와 같은 서드파티에서도 API UP1000이나 UP2000과 같은 OEM 메인보드를 생산했습니다.

플랫폼용 하드웨어 및 소프트웨어 개발에 서드파티를 지원하기 위해 DEC는 Alpha 21064A 및 21164 마이크로프로세서용 EB64+ 및 EB164 등의 평가판을 각각 제작했습니다.

21164 및 21264 프로세서는 NetApp에서 다양한 네트워크 연결 스토리지 시스템에서 사용되었으며, 21064 및 21164 프로세서는 Cray에서 T3D 및 T3E 대규모 병렬 슈퍼컴퓨터에서 사용되었습니다.

슈퍼컴퓨터

Alpha 프로세서를 기반으로 한 가장 빠른 슈퍼컴퓨터는 Los Alamos National Laboratory의 ASCI Q였습니다.이 머신은 HP AlphaServer SC45/GS 클러스터로 구축되었습니다.4096 Alpha (21264 EV-68, 1.25 GHz) CPU를 탑재하여 7max.727 TFLOPS의 [33]R에 도달했습니다.몇몇 과학자들에 따르면 Sunway TaihuLight를 지원하는 Sunway 아키텍처는 Alpha [34]아키텍처의 라이센스 후예입니다.Alpha 슈퍼컴퓨터로 간주될 경우, TaihuLight는 40,960개의 코어에 대해 93페타플롭스의 LINPACK 등급을 가진 역사상 가장 강력한 Alpha 시스템이 될 것입니다.

메모들

레퍼런스

- ^ a b c d e f Paul V. Bolotoff (21 April 2007). "Alpha: The History in Facts and Comments". Archived from the original on 3 December 2013. Retrieved Nov 22, 2008.

- ^ Aaron Sakovich (2001). "Windows 2000?". The AlphaNT Source. Archived from the original on 2008-07-08. Retrieved 2007-01-01.

- ^ "SUSE Linux 7.0 Alpha Edition". SUSE. 2000. Archived from the original on 2014-01-08. Retrieved 2014-01-08.

- ^ George A. Darcy III; Ronald F. Brender; Stephen J. Morris; Michael V. Iles (1992). "Using Simulation to Develop and Port Software" (PDF). Digital Technical Journal. 4 (4): 181–192.

- ^ "Ghost of DEC Alpha is why Windows is rubbish at file compression". TheRegister.co.uk. November 2, 2016. Archived from the original on September 20, 2018. Retrieved September 20, 2018.

- ^ a b Popovich, Ken (2001-06-28). "Alpha proved costly for Compaq". www.zdnet.com. ZDNet. Archived from the original on 2016-03-03. Retrieved 2016-03-02.

- ^ "Transforming your AlphaServer environment". HP. Archived from the original on 2007-02-08. Retrieved 2007-01-11.

- ^ Catherine Richardson; Terry Morris; Rockie Morgan; Reid Brown; Donna Meikle (March 1987). "MICA Software Business Plan" (PDF). bitsavers.org. Archived (PDF) from the original on 2021-01-07. Retrieved 2021-01-04.

- ^ a b Supnik, Bob (24 February 2008). "MicroPrism". The Computer History Simulation Project. Archived from the original on 3 April 2021. Retrieved 26 April 2021.

- ^ Bolotoff, Paul V (2007-04-22). "Alpha: The History in Facts and Comments". Archived from the original on 2019-09-29. Retrieved 2019-09-09.

- ^ Mark Smotherman. "Sketch of DEC PRISM". Archived from the original on 2020-04-04. Retrieved 2018-09-20.

PRISM (Parallel Reduced Instruction Set Machine) ... first draft of PRISM architecture in August 1985; DEC cancels the project in 1988 in favor of a MIPS-based ...

- ^ a b Comerford, Richard (July 1992). "How DEC developed Alpha". IEEE Spectrum. 29 (7): 28. doi:10.1109/6.144508. Archived from the original on 2018-06-20. Retrieved 2021-10-23.

- ^ Supnik, Bob (1992). "Foreword". Digital Technical Journal. 4 (4). Archived from the original on 2021-05-03. Retrieved 2021-05-03.

- ^ "Managing Technological Leaps: A study of DEC's Alpha Design Team" (PDF). April 1993. Archived (PDF) from the original on 2021-02-07. Retrieved 2021-04-26.

- ^ Richard L. Sites; Richard T. Witek (2014-05-16). Alpha AXP Architecture Reference Manual - 2nd Edition. ISBN 978-1-4831-8403-6. Archived from the original on 2018-09-20. Retrieved 2018-09-20.

- ^ Warner, W. (December 22, 2004). "Great moments in microprocessor history". IBM. Archived from the original on January 19, 2018. Retrieved January 18, 2018.

- ^ a b "cpu-collection.de - DEC Alpha AXP". Archived from the original on 2018-09-20. Retrieved 2018-09-20.

The first processors of the Alpha family were designated the DECchip 21064 series (the "21" signifying 21st century)

- ^ Bill Hamburgen; Jeff Mogul; Brian Reid; Alan Eustace; Richard Swan; Mary Jo Doherty; Joel Bartlett (1989). "WRL Technical Note TN-13: Characterization of Organic Illumination Systems" (PDF). Digital Equipment Corporation. Retrieved 2007-10-04.

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ John H. Edmondson; Paul I. Rubinfeld; Peter J. Bannon; Bradley J. Benschneider; Debra Bernstein; Ruben W. Castelino; Elizabeth M. Cooper; Daniel E. Dever; Dale R. Donchin; Timothy C. Fischer; Anil K. Jain; Shekhar Mehta; Jeanne E. Meyer; Ronald P. Preston; Vidya Rajagopalan; Chandrasekhara Somanathan; Scott A. Taylor; Gilbert M. Wolrich (1995). "Internal Organization of the Alpha 21164, a 300-MHz 64-bit Quad-issue CMOS RISC Microprocessor". Digital Technical Journal. 7 (1): 119–135. CiteSeerX 10.1.1.38.9551.

large, on-chip, second-level, write-back cache

- ^ Reviews, C.T.I (2016). Structured Computer Organization. ISBN 978-1478426738.

21364 ... first high performance processor to have an onchip memory controller.

- ^ Roger Espasa; Federico Ardanaz; Julio Gago; Roger Gramunt; Isaac Hernandez; Toni Juan; Joel Emer; Stephen Felix; Geoff Lowney; Matthew Mattina; Andre Seznec (2002). "Tarantula: A Vector Extension to the Alpha Architecture". In Danielle C. Martin (ed.). Proceedings: 29th Annual International Symposium on Computer Architecture (ISCA '02). 29th Annual International Symposium on Computer Architecture (ISCA '02). Joe Daigle/Studio Productions. Los Alamitos, Calif: IEEE Computer Society. pp. 281–292. doi:10.1109/ISCA.2002.1003586. ISBN 0-7695-1605-X. Archived from the original on 2007-10-04. Retrieved 2007-10-04.

- ^ "The VAX Vacuum".

... legally, if DEC had used VAX in the U.S. before that ..... "reasonable person" has no difficulty distinguishing between the two uses

- ^ "The Alpha AXP, part 8: Memory access, storing bytes and words and unaligned data". August 16, 2017. Retrieved July 18, 2022.

Dealing with unaligned memory on the Alpha AXP is very annoying

- ^ "Alpha 21264 Microprocessor Data Sheet" (PDF). Archived (PDF) from the original on 2017-08-30. Retrieved 2018-09-20.

The instructions that comprise the BWX extension are ...

- ^ "MIPS Instructions".

DEC Alpha ... , no integer condition code.

[영구 데드링크] - ^ "Alpha Bits - Migrating To The Future". DEC Professional. August 1992. p. 62.

H floating datatypes are unavailable on Alpha

- ^ "Migrating an Application from OpenVMS VAX to OpenVMS Alpha".

- ^ Gronowski, P. E.; Bowhill, W. J.; Donchin, D. R.; Blake-Campos, R. P.; Carlson, D. A.; Equi, E. R.; Loughlin, B. J.; Mehta, S.; Mueller, R. O.; Olesin, A.; Noorlag, D. J. W.; Preston, R. P. (1996). "A 433-MHz 64-b quad-issue RISC microprocessor". IEEE Journal of Solid-State Circuits. 31 (11): 1687–1696. Bibcode:1996IJSSC..31.1687G. doi:10.1109/JSSC.1996.542313. S2CID 39280205.

- ^ 린리 구엔납(1996년 11월 18일)."디지털, MIPS 멀티미디어 확장 추가"마이크로프로세서 리포트

- ^ Luiz André Barroso; Kourosh Gharachorloo; Robert McNamara; Andreas Nowatzyk; Shaz Qadeer; Barton Sano; Scott Smith; Robert Stets; Ben Verghese (2000). Piranha: A Scalable Architecture Based on Single-Chip Multiprocessing. 27th Annual International Symposium on Computer Architecture. doi:10.1145/339647.339696.

- ^ David Mosberger. "Overview of Alpha Family". Archived from the original on January 20, 2009. Retrieved Dec 9, 2009.

- ^ 라인하르트 크라우즈."DEC 알파 보드 푸시 출시"일렉트로닉 뉴스 1994년 4월 4일

- ^ Los Alamos National Laboratories (2002). "The ASCI Q System: 30 TeraOPS Capability at Los Alamos National Laboratory" (PDF). Archived from the original (PDF) on 2011-01-12. Retrieved 2010-06-06.

- ^ Gustafson, John (2020). "Are China's largest supercomputers using Sunway CPUs actually based on reverse-engineered American DEC Alpha CPUs from the 1990s?". Archived from the original on 2022-03-12. Retrieved 2022-03-14.

외부 링크

- 알파 아키텍처 핸드북 버전 4

- 알파 아키텍처 핸드북 버전 3

- 디지털 테크니컬 저널, 제4권, 제4호, 1992년호 Alpha AXP의 아키텍처와 시스템 이 호에는 Alpha의 아키텍트로부터의 몇 가지 기사가 포함되어 있습니다.

- 아카이브 기술 문서 라이브러리 이 링크에는 Alpha 마이크로프로세서, 칩셋 및 OEM 메인보드용 하드웨어 레퍼런스 매뉴얼과 데이터시트가 포함되어 있습니다.Alpha Architecture Handbook 및 다양한 프로그래밍 매뉴얼이 포함되어 있습니다.

- Dan Dobberpuhl과의 대화 (2003년 10월 1일)

- 컴퓨터 아키텍처에 관한 브루스 허튼 박사의 강의 노트