트라이악

TRIAC 프린트 회로 기판에 장착되는 작은 플라스틱 케이스의 TRIAC 장치 | |

| 유형 | 수동적인 |

|---|---|

| 핀 구성 | 터미널 1, 게이트 및 터미널 2 |

| 전자 기호 | |

| |

TRIAC(교류용 3극, 양방향 3극 사이리스터 또는 양방향 3극 사이리스터[1])는 트리거 시 어느 방향으로 전류를 전달하는 3단자 전자 부품입니다.TRIAC라는 용어는 일반화된 상표입니다.

TRIAC는 사이리스터의 서브셋(작은 전압과 전류가 훨씬 큰 전압과 전류를 제어할 수 있다는 점에서 릴레이와 유사)으로 실리콘 제어 정류기(SCR)와 관련되어 있습니다.TRIAC는 양방향으로 전류가 흐를 수 있다는 점에서 SCR과 다릅니다.단, SCR은 단방향으로만 전류를 통전할 수 있습니다.대부분의 TRIAC는 게이트에 양의 전압 또는 음의 전압을 인가함으로써 트리거할 수 있습니다(SCR에는 양의 전압이 필요합니다).일단 트리거되면 게이트 전류가 중단되더라도 주 전류가 유지 전류라고 하는 특정 레벨 아래로 떨어질 때까지 SCR 및 TRIAC는 계속 전도합니다.

게이트 끄기 사이리스터(GTO)는 TRIAC와 유사하지만 게이트 신호가 중지되면 꺼짐으로써 더 많은 제어 기능을 제공합니다.

TRIAC의 쌍방향성은 교류(AC)에 편리한 스위치입니다.또한 주회로에서 AC의 제어된 위상각에 트리거를 적용함으로써 부하에 흐르는 평균전류를 제어할 수 있다(위상제어).일반적으로 범용 모터의 속도 제어, 램프 조광, 전기 히터 제어에 사용됩니다.TRIAC는 바이폴라 디바이스입니다.

작동

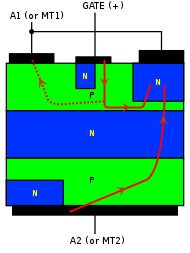

TRIAC의 구조를 이해하려면 4개의 사분원 각각에서의 트리거링을 검토합니다.4개의 사분면은 그림 1에 나타나 있으며, MT1에 관한 게이트 및 MT2 전압에 따라 달라집니다. Main Terminal 1(MT1) 및 Main Terminal(MT2)은 각각 [2]Anode 1(A1) 및 Anode 2(A2)라고도 합니다.

상대 감도는 특정 트라이악의 물리적 구조에 따라 다르지만 원칙적으로 사분면이 가장 민감하고(필요한 게이트 전류 최소), 사분면이 가장 민감하지 않다(필요한 게이트 전류 최대)[clarification needed Why is Q-IV the least sensitive? See discussion]

사분원 1, 2에서는 MT2가 양이고 전류는 MT2에서 P, N, P 및 N층을 통해 MT1로 흐른다.MT2에 접속되어 있는N 영역은, 큰폭으로 관여하고 있지 않습니다.사분원 3과 4에서는 MT2가 음이 되며 전류는 MT1에서 MT2로 흐르며 P, N, P 및 N 층을 통해서도 흐른다.MT2에 연결된N 영역은 활성화 되어 있지만 MT1에 연결된N 영역은 벌크 전류 플로우가 아닌 초기 트리거링에만 관여합니다.

대부분의 애플리케이션에서 게이트 전류는 MT2에서 발생하므로 사분원 1과 3이 유일한 작동 모드(MT1에 대한 게이트 및 MT2 양 또는 음)입니다.IC 또는 디지털 드라이브 회로에서 단극성 트리거를 사용하는 다른 애플리케이션은 MT1이 일반적으로 양의 전압(예: +5V)에 연결되고 게이트가 0V(접지)로 풀다운되는 경우보다 사분원 2 및 3에서 작동합니다.

쿼드런트 1

Quadrant 1 연산은 게이트와 MT2가 MT1에 Figure 1대해 양수일 때 발생합니다.

이 메커니즘은 그림 3에 나와 있습니다.게이트 전류는 등가 NPN 트랜지스터 스위치를 켜서 등가 PNP 트랜지스터의 베이스에서 전류를 끌어와 켜줍니다.게이트 전류(점선)의 일부는 p-실리콘을 가로지르는 오믹 경로를 통해 손실되어 NPN 트랜지스터 베이스를 통과하지 않고 MT1로 직접 흐른다.이 경우 p-silicon에 구멍을 주입하면 MT1 아래에 적층된n, p 및 n층이 NPN 트랜지스터처럼 동작하며, NPN 트랜지스터는 베이스에 전류가 존재하기 때문에 점등합니다.이에 따라 MT2 위의 p, n 및 p 레이어가 PNP 트랜지스터처럼 동작합니다.이거는 n타입 베이스가 이미터(MT2)에 대해 전방 바이어스가 되기 때문에 켜집니다.따라서 트리거 방식은 SCR과 동일합니다.그림 4에 등가회로를 나타냅니다.

단, SCR과는 구조가 다릅니다.특히 TRIAC는 항상 게이트에서 p-실리콘을 통해 MT1로 직접 흐르는 소량의 전류를 등가 NPN 트랜지스터의 베이스와 이미터 사이의 p-n 접점을 통과하지 않고 가지고 있습니다.이 전류는 빨간색 점선으로 그림 3에 나타나 있으며, TRIAC가 동등한 정격의 [3]SCR보다 더 많은 게이트 전류를 필요로 하는 이유입니다.

일반적으로 이 사분면은 네 가지 중 가장 민감합니다.이는 메인 디바이스 트랜지스터 [4]중 하나의 베이스에 게이트 전류가 직접 주입되는 유일한 사분면이기 때문입니다.

쿼드런트 2

Quadrant 2 연산은 MT1에 대해 게이트가 Figure 1음수이고 MT2가 양수일 때 발생합니다.

그림 5는 트리거링 프로세스를 나타내고 있습니다.장치의 켜짐은 3배이며 MT1에서 게이트 아래의 p-n 접점을 통해 게이트로 전류가 흐르면 시작됩니다.그러면 게이트가 음극인 NPN 트랜지스터와 PNP 트랜지스터로 구성된 구조가 켜집니다(그림에서 이 구조의 켜짐은 "1"로 표시됩니다).게이트 전류가 증가함에 따라 게이트 아래 p-silicon 좌측 전위가 MT1을 향해 상승합니다.이는 게이트와 MT2의 전위차가 낮아지는 경향이 있기 때문입니다.이것에 의해 p-silicon의 좌측과 우측 사이에 전류가 확립되어 NPN tra가 켜집니다.MT1 단자 아래의 nsistor와 그 결과 MT2와 상부 p-silicon 우측 사이의 pnp 트랜지스터도 마찬가지입니다.따라서 최종적으로 전류의 대부분을 가로지르는 구조는 사분면 I 연산과 동일합니다(그림 [3]5의 "3")

쿼드런트 3

Quadrant 3 연산은 게이트와 MT2가 MT1에 Figure 1대해 음수일 때 발생합니다.

전체 프로세스는 그림 6에 개략적으로 설명되어 있습니다.이 과정도 다른 단계로 진행됩니다.제1상에서는, MT1 단자와 게이트의 pn접점이 전방 바이어스가 된다(스텝 1).전방 바이어싱은 접합부에 합류하는 두 층의 소수 캐리어 주입을 의미하므로 게이트 아래의 p층에 전자가 주입된다.이들 전자 중 일부는 재결합하지 않고 기초가 되는 n개 영역으로 빠져나간다(2단계).이는 다시 n 영역의 전위를 낮추어 스위치를 켜는 pnp 트랜지스터의 베이스 역할을 합니다(기본 전위를 직접 낮추지 않고 트랜지스터를 켜는 것을 원격 게이트 컨트롤이라고 합니다).하부 p층은 이 PNP 트랜지스터의 컬렉터로서 동작하며 전압이 높아집니다.이 p층은 MT2 단자 바로 위에 있는 마지막 3개의 레이어로 이루어진 NPN 트랜지스터의 베이스로서도 기능합니다.이것이 활성화 됩니다.따라서 그림 6에서 "3"으로 표시된 빨간색 화살표는 [3]전류의 최종 전도 경로를 나타냅니다.

쿼드런트 4

Quadrant 4 연산은 게이트가 양이고 MT2가 음일 때 MT1에 대해 발생합니다.

이 쿼드런트에서 트리거하는 것은 쿼드런트 III에서 트리거하는 것과 같습니다.이 프로세스는 원격 게이트 컨트롤을 사용하며 그림 7에 나와 있습니다.게이트 하단의 p층에서 MT1 하단의 n층으로 전류가 흐르므로 자유전자 형태의 소수담체가 p영역에 주입되고 일부는 기초 n-p접합부에 의해 수집되어 재결합하지 않고 인접한 n영역에 통과한다.사분면 III의 트리거링의 경우와 마찬가지로 n층의 전위를 낮추고 n층과 그 옆에 있는 2개의 p층으로 이루어진 PNP 트랜지스터를 켭니다.하부 p층은 이 PNP 트랜지스터의 컬렉터로서 동작하며 전압이 높아집니다.이 p층은 MT2 단자 바로 위에 있는 마지막 3개의 레이어로 이루어진 NPN 트랜지스터의 베이스로서도 기능합니다.이것이 활성화 됩니다.따라서 그림 6에서 "3"으로 표시된 빨간색 화살표는 [3]전류의 최종 전도 경로를 나타냅니다.

일반적으로 이 사분면은 [2]4개 중 가장 덜 민감합니다.또한 TRIAC(로직레벨 및 스너블리스 타입)의 일부 모델은 이 쿼드런트에서 트리거할 수 없으며 나머지 3개 모델에서만 트리거할 수 있습니다.

문제들

회선내에서 TRIAC 를 사용하는 경우는, 몇개의 제한이 있습니다.이 섹션에서는 몇 가지 내용을 요약합니다.

게이트 임계값 전류, 래치 전류 및 유지 전류

TRIAC는 게이트로 들어오거나 게이트에서 나가는 전류가 작동 사분면에서 관련 접점을 작동하기에 충분할 때 도통을 시작합니다.이를 수행할 수 있는 최소 전류를 게이트 임계값 전류라고 하며 일반적으로 I로 나타냅니다GT.일반적인 TRIAC에서 게이트 임계값 전류는 일반적으로 몇 밀리암페어이지만 다음 사항도 고려해야 합니다.

- 온도에GT 따라 달라집니다.온도가 높을수록 막힌 접합부의 역류도 높아집니다.이는 게이트 영역에 더 많은 빈 캐리어가 존재함을 의미하며, 이는 필요한 게이트 전류를 낮춥니다.

- 다른GT 사분면은 다른 트리거 방식을 의미하기 때문에 나는 운영 사분면에 의존합니다(여기를 참조).일반적으로 첫 번째 사분면은 가장 민감합니다(즉, 가장 낮은 전류를 필요로 합니다). 반면 네 번째 사분면은 가장 민감하지 않습니다.

- 오프 상태에서 전원을 켤 때는 2개의 메인 단자 MT1과 MT2의 전압에 의존합니다GT.MT1과 MT2 사이의 전압이 높을수록 차단된 접합부에 더 많은 역류 전류가 발생하므로 장치를 트리거하는 데 필요한 게이트 전류가 줄어듭니다(고온 작동과 유사).데이터시트에서는GT 일반적으로 MT1과 MT2 사이의 특정 전압에 대해 I가 주어집니다.

게이트 전류가 중단되면 두 메인 단자 사이의 전류가 래치 전류라고 하는 전류보다 클 경우 장치는 계속 전도합니다.래치 전류는 게이트 전류가 없을 때 장치 내부 구조를 래치 상태로 유지하는 최소 전류입니다.이 파라미터의 값은 다음에 따라 달라집니다.

- 게이트 전류 펄스(수직, 모양 및 폭)

- 온도

- 동작 사분면

특히 게이트 전류의 펄스 폭이 충분히 큰 경우(일반적으로 수십 마이크로초), TRIAC는 게이트 신호가 중단되고 래치 전류가 유지 전류라고 불리는 최소 레벨에 도달했을 때 트리거 처리를 완료했습니다.유지 전류는 장치가 내부 구조의 모든 부분에서 통전된 후에도 장치를 계속 켜두는 두 개의 주요 단자 사이에 흐르는 최소 요구 전류입니다.

데이터 시트에서 래치 전류는 I, 유지L 전류는 I로 표시됩니다H.보통 몇 밀리암페어 정도 됩니다.

정적 dv/dt

MT2와 MT1 사이의 d v t \ \ \ t }는 TRIAC가 꺼졌을 때 켜질 수 있습니다.임계 정적 dv/dt의 일반적인 값은 마이크로초당 볼트 수입니다.

켜짐은 게이트 단자와 MT2 단자의 기생 용량성 커플링으로 인해 발생하며, MT2에서 큰 전압 변화 속도에 따라 게이트로 전류가 흐릅니다.이 제한에 대처하기 위한1가지 방법은 적절한 RC 또는 RCL 스너버 네트워크를 설계하는 것입니다.대부분의 경우 이는 MT1을 향한 게이트의 임피던스를 낮추기에 충분합니다.이 두 단자 사이에 저항 또는 소형 캐패시터(또는 둘 다 병렬)를 배치하면 과도 중에 생성된 용량 전류가 활성화되지 않고 디바이스에서 흐릅니다.제조원이 제공하는 어플리케이션 노트를 주의 깊게 읽고 올바른 네트워크를 설계하기 위해 특정 디바이스 모델을 테스트하는 것이 좋습니다.게이트와 MT1 사이의 캐패시터 및 저항의 일반적인 값은 최대 100nF 및 10Ω ~[5] 1kΩ입니다.감응 [6]게이트로 시판되는 저전력 타입을 제외한 일반 TRIAC에는 스플리어스 dv/dt 트리거로부터 보호하기 위해 이미 이러한 저항이 내장되어 있습니다.멀티미터로 TRIAC를 테스트할 때 게이트의 예상 다이오드 유형 동작을 마스킹합니다.

데이터 시트에서 정적 dv/dt는 일반적으로 ( v ) t ) { v} {\ t})로표시되며, 전술한 바와 같이 큰 전압의 인가 후에도 TRIAC가 꺼지는 경향과 관련이 있다.문.

긴급 di/dt

디바이스의 전원이 들어가 있을 때 MT1과 MT2 사이의 전류 상승률이 높으면 펄스 지속시간이 매우 짧더라도 TRIAC가 손상되거나 파괴될 수 있습니다.그 이유는 변환 중에 소비전력이 디바이스 전체에 균일하게 분산되지 않기 때문입니다.전원을 켜면 도전이 끝나기 전에 전류가 흐르기 시작하여 접점 전체에 퍼집니다.일반적으로 디바이스는 몇 나노초 또는 마이크로초 후에 외부 회로에 의해 인가되는 전류를 통전하기 시작하지만, 전체 접점의 스위치를 켜는 데 시간이 오래 걸리기 때문에 전류가 너무 빨리 상승하면 로컬 핫스팟이 발생하여 TRIAC에 영구적인 손상을 줄 수 있습니다.

데이터 시트에서 이 파라미터는 보통 d d t{ { {} {\ {d} t로 나타나며 일반적으로 [2]마이크로초당 수십암페어입니다.

dv/dt와 di/dt의 정류

정류 dv/dt 정격은 TRIAC가 전도 중이고 인덕터와 같은 부분 무효 부하로 끄려고 할 때 적용됩니다.전류와 전압이 위상을 벗어났기 때문에 전류가 유지 값 아래로 감소하면 TRIAC가 끄려고 하지만 전류와 전압 사이의 위상 전환으로 인해 두 주 단자 간에 갑작스러운 전압 단계가 발생하여 장치가 다시 켜집니다.

데이터 시트에서 이 파라미터는 보통 ( d c \ t로 나타나며 일반적으로 마이크로초당 최대 몇 볼트입니다.

dv/dt의 정류량이 정적 dv/dt보다 적은 이유는 디바이스가 꺼지기 직전에 이전 전도의 결과로서 내부 레이어에 아직 약간의 과잉 소량의 전하가 존재하기 때문입니다.TRIAC가 꺼지기 시작하면 이러한 전하가 게이트 및 MT1 근처 영역의 내부 전위를 변화시키므로 dv/dt로 인한 정전용량 전류가 장치를 다시 켜기 쉬워집니다.

온상태에서 오프상태로 변환하는 동안 또 하나의 중요한 요인은 MT1에서 MT2로의 전류 di/dt입니다.이것은 표준 다이오드의 회복과 비슷합니다.di/dt가 높을수록 역전류가 커집니다.TRIAC에는 기생 저항이 존재하기 때문에 내부 p-n 접합부의 높은 역전류가 게이트 영역과 MT1 영역 사이의 전압 강하를 유발하여 TRIAC가 켜진 상태를 유지할 수 있습니다.

데이터시트에서 정류 di/dt는 보통 ( i d t ) {\ t로나타나며, 일반적으로 마이크로초당 암페어 수입니다.

TRIAC를 사용하여 유도 부하와 같이 전류와 전압 사이의 위상 편이를 통해 부하를 구동하는 경우 정류 dv/dt는 매우 중요합니다.인덕터를 끄려고 합니다.전류가 0이 되면 게이트가 공급되지 않으면 TRIAC가 꺼지려고 하지만 앞에서 설명한 위상 이동으로 인해 인덕터의 전압이 상승합니다.정류 dv/dt 정격을 초과하면 디바이스의 전원이 꺼지지 않습니다.

스너버 회로

무효(유도 또는 용량성) 부하를 제어하는 데 사용할 경우 주 회로에서 AC의 각 반주기 끝에 TRIAC가 올바르게 꺼지도록 주의해야 합니다.TRIAC는 MT1과 MT2 사이의 빠른 전압 변화(dv/dt)에 민감할 수 있으므로, 무효 부하에 의해 전류와 전압 사이의 위상 전환으로 인해 사이리스터가 잘못 [3]켜질 수 있는 전압 스텝이 발생할 수 있습니다.전기모터는 일반적으로 유도부하이며 오프라인 전원장치(대부분의 TV 및 컴퓨터에 사용됨)는 정전용량입니다.

MT1과 MT2 사이에 스너버 회로(일반적으로 저항/캐패시터 또는 저항/캐패시터/인덕터 유형)를 사용하면 원치 않는 켜짐을 방지할 수 있습니다. 스너버 회로도 주전원의 전압 스파이크로 인해 발생하는 조기 트리거링을 방지하기 위해 사용됩니다.

켜짐은 높은 dv/dt(즉, 급격한 전압 변화)의 결과로 게이트로 유입되는 내부 용량성 전류에 의해 발생하므로 게이트 저항 또는 캐패시터(또는 병렬로 모두)를 게이트와 MT1 사이에 연결하여 MT1에 대한 저임피던스 경로를 제공하고 나아가 잘못된 트리거링을 방지할 수 있습니다.그러나 이로 인해 필요한 트리거 전류가 증가하거나 캐패시터 충전으로 인한 지연 시간이 증가합니다.한편 게이트와 MT1 사이의 저항은 디바이스에서 누출 전류를 끌어내는 데 도움이 되며, 이로 인해 최대 허용 dv/dt가 낮은 고온에서 TRIAC의 성능이 향상됩니다.일반적으로 1kΩ 미만의 저항과 100nF의 캐패시터 값이 이 목적에 적합합니다. 단, 미세 조정은 특정 디바이스 [5]모델에서 수행해야 합니다.

고출력 부하 및 요구가 높은 부하에서는 1개의 TRIAC 대신 2개의 SCR을 역병렬로 사용할 수 있습니다.각 SCR에는 반주기 전체에 역극성 전압이 인가되기 때문에 부하 특성에 관계없이 SCR의 끄기가 보증됩니다.단, 게이트가 분리되어 있기 때문에 SCR의 적절한 트리거링은 TRIAC의 트리거링보다 복잡합니다.

또한 TRIAC는 현재 위상 시프트로 인해 트리거 시 주 회로 전류가 유지 전류보다 낮은 경우 무효 부하에서 안정적으로 켜지지 못할 수 있습니다.이 문제를 해결하려면 DC 또는 펄스 트레인을 사용하여 TRIAC가 켜질 때까지 반복적으로 트리거할 수 있습니다.

어플

저전력 TRIAC는 조광기, 선풍기 및 기타 전기 모터의 속도 제어 및 많은 가정용 소형 및 주요 기기의 최신 컴퓨터 제어 회로와 같은 많은 응용 분야에 사용됩니다.

마이크로컨트롤러에 의해 주전압 TRIAC가 트리거되는 경우, 광이성자를 사용하여 게이트 전류를 제어할 수 있습니다.또는 안전이 보장되고 컨트롤러의 전기적 분리가 필요하지 않은 경우 마이크로 컨트롤러의 파워 레일 중 하나를 주전원 공급 장치 중 하나에 연결할 수 있습니다.이러한 상황에서는 중성 단자를 트라이악의 A1과 함께 마이크로컨트롤러 전원의 양극 레일에 연결하고, A2를 통전 장치에 연결하는 것이 일반적입니다.TRIAC의 게이트는 광 절연 트랜지스터를 통해 연결할 수 있으며, 때로는 저항을 마이크로 컨트롤러에 연결하여 전압을 마이크로 컨트롤러의 논리 0으로 낮추면 TRIAC의 게이트를 트리거하기에 충분한 전류를 끌어낼 수 있습니다.이것에 의해, TRIAC는 사분원 II 와 III 로 트리거 되어, 통상, TRIAC 가 둔감한 [7]사분원 IV 를 회피할 수 있습니다.

데이터 예시

| 변수명 | 파라미터 | 표준값 | 구성 단위 |

|---|---|---|---|

| 게이트 임계값 전압 | 0.7-1.5 | V | |

| 게이트 임계값 전류 | 5–50 | 엄마. | |

| 반복 피크 오프 상태 순방향 전압 | 600–800 | V | |

| 반복 피크 오프 상태 반전 전압 | 600–800 | V | |

| RMS 온스테이트 전류 | 4–40 | A | |

| 온스테이트 전류, 비반복 피크 | 100–270 | A | |

| ON 상태 순방향 전압 | 1.5 | V |

고정류(2사분원 및 3사분원) TRIAC

3 사분원 TRIAC는 사분원1 ~ 3에서만 동작하며 사분원4에서는 트리거할 수 없습니다.이러한 장치는 정류 개선을 위해 특별히 제작되었으며 종종 스너버 회로를 사용하지 않고도 반응 부하를 제어할 수 있습니다.

이러한 유형의 최초의 TRIAC는 Thomson Semiconductors(현 ST Microelectronics)에 의해 "Alternistor"라는 이름으로 판매되었습니다.이후 버전은 "Snubberless" 및 "ACS"라는 상표로 판매됩니다(AC 스위치에는 게이트 버퍼도 포함되어 있기 때문에 쿼드런트I 의 조작은 한층 더 금지됩니다).Littelfuse는 또한 "Alternistor"라는 이름을 사용합니다.Philips Semiconductors(현 NXP Semiconductors)는 Hi-Com(하이컴퓨테이션)이라는 상표를 만들었습니다.

대부분의 경우 이러한 TRIAC는 로직레벨 컴포넌트에 의해 직접 구동되는 보다 작은 게이트 전류로 동작할 수 있습니다.

「 」를 참조해 주세요.

- DIAC(교류용 다이오드)

- 쿼드랙

- 실리콘 제어 정류기(SCR)

- 트라이오데

레퍼런스

- ^ Bhimsen (2020-10-06). "Thyristor or Silicon Controlled Rectifier (SCR)". electronics fun. Retrieved 2021-10-31.

- ^ a b c "사이리스터 이론 및 설계 고려 사항", ON Semiconductor, [1]에서 구할 수 있습니다.

- ^ a b c d e M.D. Singh, K.B. Khanchandani, Power Electronics, 제2판, 타타 맥그로힐, 뉴델리, 2007, 148-152쪽

- ^ "TRIAC – Operation, symbol, circuits & applications". Electrical Classroom.

{{cite web}}: CS1 maint :url-status (링크) - ^ a b 애플리케이션 노트 AN-3008, 사이리스터 전원 제어 및 과도 억제를 위한 RC 스너버 네트워크, Fairchild Semiconductor, http://www.fairchildsemi.com/an/AN/AN-3008.pdf, 1-5페이지에서 구할 수 있습니다.

- ^ "2N6071A/B Series Sensitive Gate Triacs" (PDF). Semiconductor Components Industries, LLC. Retrieved June 28, 2012.

- ^ 트라이악과 마이크로컨트롤러 - 간단한 연결

- ^ "Philips Semiconductors Product specification Triacs BT138 series" (PDF). 090119 nxp.com

- ^ "STMicroelectronics T3035H, T3050H Snubberless high temperature 30 A Triacs" (PDF). st.com 100922

추가 정보

- 사이리스터의 이론과 설계 고려사항; 반도체, 240페이지; 2006; HBD855/D. (PDF 무료 다운로드)

외부 링크

Wikimedia Commons의 트라이악 관련 미디어

Wikimedia Commons의 트라이악 관련 미디어

나타나며 일반적으로

나타나며 일반적으로