IA-64

IA-64| 디자이너 | HP 및 인텔 |

|---|---|

| 비트 | 64비트 |

| 소개했다 | 2001 |

| 설계. | 서사시 |

| 유형 | [Register] : [Register |

| 부호화 | 고정된. |

| 분기 | 상황 레지스터 |

| 엔디안니스 | 선택 가능 |

| 레지스터 | |

| 범용 | 128(64비트+1 트랩비트, 32는 스태틱, 96은 레지스터 창 사용), 64개의 1비트 술어 레지스터 |

| 부동 소수점 | 128 |

IA-64 (인텔 Itanium 아키텍처)는 64비트 인텔 마이크로프로세서 Itanium 패밀리의 명령 세트 아키텍처(ISA)입니다.기본적인 ISA 사양은 Hewlett-Packard(HP)에서 시작되었으며, 이후 인텔이 HP와 협력하여 구현되었습니다.최초의 Itanium 프로세서(코드네임 Merced)는 2001년에 출시되었습니다.

Itanium 아키텍처는 컴파일러가 병렬로 실행할 명령을 결정하는 명시적 명령 수준 병렬화에 기반합니다.이는 실행 시 명령 의존성을 관리하기 위해 프로세서에 의존하는 슈퍼스케일러 아키텍처와 대조됩니다.Tukwila를 포함한 모든 Itanium 모델에서 코어는 클럭 사이클당 최대 6개의 명령을 실행합니다.

2008년 Itanium은 x86-64, Power ISA 및 SPARC에 이어 [1]4번째로 많은 엔터프라이즈 클래스 시스템용 마이크로프로세서 아키텍처였습니다.

역사

개발: 1989~2000년

1989년에 HP는 RISC(Reduced Instruction Set Computing) 아키텍처가 사이클당 1개의 명령으로 처리 제한에 가까워지고 있는 것을 우려하기 시작했습니다.인텔과 HP의 연구자는, 장래의 설계를 위해서 컴퓨터 아키텍쳐의 옵션을 조사하고 있었습니다.또,[3] 1980년대 초에 예일 대학의 연구에서 나온 VLIW([2]Very long instruction word)라고 불리는 새로운 개념에 대해서도 조사하기 시작했습니다.

VLIW는 컴퓨터 아키텍처의 개념(RISC나 CISC 등)으로, 1개의 명령어에는 1개의 매우 긴 명령어로 부호화된 복수의 명령어가 포함되어 있어 각 클럭 사이클에서 프로세서가 복수의 명령을 실행하는 것을 용이하게 합니다.일반적인 VLIW의 실장은 컴파일 시에 동시에 실행할 수 있는 명령과 이러한 명령의 적절한 실행 스케줄을 결정하고 브랜치 조작의 방향을 예측하는 데 도움이 되는 고도의 컴파일러에 크게 의존하고 있습니다.이 접근방식의 가치는 보다 적은 클럭 사이클로 보다 유용한 작업을 수행하고 프로세서 명령 스케줄링과 분기 예측 하드웨어 요건을 단순화하는 것입니다.그 대신 프로세서의 복잡성, 비용 및 에너지 소비가 증가합니다.

생산.

이 기간 동안 HP는 자체와 같은 개별 엔터프라이즈 시스템 회사가 자체 마이크로프로세서를 개발하는 것은 더 이상 비용 효율이 높지 않다고 생각하기 시작했습니다.인텔은 x86 ISA를 넘어 하이엔드 엔터프라이즈 서버 및 하이 퍼포먼스 컴퓨팅(HPC) 요건에 대응하기 위한 아키텍처 옵션도 연구해 왔습니다.

인텔과 HP는 1994년에 파트너십을 맺고 다양한 VLIW 설계 컨셉을 사용하여 IA-64 ISA를 개발했습니다.이 컨셉은 인텔이 명시적으로 병렬 명령 컴퓨팅(EPIC)이라고 명명했습니다.인텔의 목표는 HP가 초기 VLIW 작업에서 개발한 전문 지식을 활용하여 모든 OEM(Original Equipment Manu)에 판매할 수 있는 상기 하이엔드 시스템을 대상으로 한 볼륨 제품 라인을 개발하는 것이었습니다.또, HP는 인텔의 볼륨 매뉴를 사용한 시판 프로세서를 구입할 수 있기를 희망하고 있었습니다.PA-RISC 프로세서보다 뛰어난 팩터링과 최신 프로세스 테크놀로지.

인텔은 설계 및 상용화 프로세스를 주도하고 HP는 ISA 정의, Merced/Itanium 마이크로아키텍처 및 Itanium 2에 공헌하고 있습니다.최초의 Itanium 패밀리 제품인 Merced의 당초 [2]목표는 1998년입니다.

마케팅.

인텔의 제품 마케팅 및 업계 참여 노력은 상당하여 당시 RISC 프로세서를 탑재한 OEM을 포함한 대부분의 엔터프라이즈 서버 OEM 업체에서 설계상의 성공을 거두었습니다.업계 분석가들은 IA-64가 서버, 워크스테이션 및 하이엔드 데스크톱에서 우위를 점할 것이며, 최종적으로는 모든 범용 애플리케이션에서 [4][5]RISC 아키텍처와 CISC 아키텍처를 모두 대체할 것이라고 예측했습니다.Compaq와 Silicon Graphics는 각각 IA-64로의 [6]이행을 위해 Alpha와 MIPS 아키텍처의 추가 개발을 포기하기로 결정했습니다.

1997년에 IA-64 아키텍처와 컴파일러는 당초 생각했던 것보다 훨씬 구현이 어려웠고 Itanium의 제공은 [7]슬럼프에 빠지기 시작했다.Itanium은 최초의 EPIC 프로세서였기 때문에 개발 작업은 팀이 익숙한 것보다 더 많은 예상치 못한 문제에 직면했습니다.또한 EPIC의 개념은 이전에 구현되지 않은 컴파일러 기능에 의존하기 때문에 더 많은 연구가 [8]필요했습니다.

Linux, HP-UX, FreeBSD, Solaris,[9][10][11] Tru64 UNIX,[6] Montrey/64 등의 Microsoft Windows, Unix[12] 및 Unix와 유사한 시스템을 포함한 여러 그룹이 아키텍처용 운영 체제를 개발했습니다(마지막 3개는 시장에 출시되기 전에 취소되었습니다).1999년 인텔은 오픈소스 산업 컨소시엄을 주도하여 Linux를 IA-64에 포팅하는 데 앞장섰습니다.이 컨소시엄에는 인텔이 주도하고 Caldera Systems, CERN, Cygnus Solutions, Hewlett-Packard, IBM, Red Hat, Sgi, Sgi가 포함되어 있습니다.그 결과 IA-64 Linux가 예정보다 빨리 제공되어 새로운 Itanium 프로세서에서 실행되는 최초의 OS가 되었습니다.

인텔은 1999년 [13]10월 4일 프로세서의 정식 명칭인 Itanium을 발표했습니다.몇 시간 안에, 아이타닉이라는 이름은 1912년 [14]첫 항해에서 침몰한 "침몰할 수 없는" 원양 정기선인 타이타닉이라는 이름에 대한 말장난으로 유즈넷 뉴스그룹에서 만들어졌다.

Itanium (Merced) : 2001

아이테니엄 프로세서 | |

| 일반 정보 | |

|---|---|

| 개시. | 2001년 6월 |

| 단종 | 2002년 6월 |

| 공통 제조원 |

|

| 성능 | |

| 최대 CPU 클럭 속도 | 733MHz~800MHz |

| FSB 속도 | 266 MT/s |

| 캐시 | |

| L2 캐시 | 96 KB |

| L3 캐시 | 2 MB 또는 4 MB |

| 아키텍처 및 분류 | |

| 명령 집합 | 아이테니엄 |

| 물리 사양 | |

| 코어 |

|

| 소켓 | |

| 제품, 모델, 변종 | |

| 코어명 |

|

2001년 6월에 Itanium이 출시될 때까지 그 성능은 경쟁 RISC [15]및 CISC 프로세서에 비해 우수하지 않았습니다.

인텔은 소프트웨어의 부족이 장래에 중대한 문제가 될 가능성이 있다는 것을 인식하고, 독립계 소프트웨어 벤더(ISV)가 개발을 촉진하기 위해서, 이러한 초기 시스템 수천 대를 입수할 수 있도록 했습니다.HP와 인텔은 1년 후 차세대 Itanium 2 프로세서를 출시했습니다.

아이테니엄 2: 2002-2010

아이테니엄 2 프로세서 | |

| 일반 정보 | |

|---|---|

| 개시. | 2002 |

| 단종 | 현재의. |

| 설계자 | 인텔(R) |

| 공통 제조원 |

|

| 성능 | |

| 최대 CPU 클럭 속도 | 733MHz~2.66GHz |

| 캐시 | |

| L2 캐시 | 256 KB (Itanium 2) 256 KB (D) + 1 MB (I) 또는 512 KB (I) (Itanium 2 9x00 시리즈) |

| L3 캐시 | 1.5 ~ 32 MB |

| 아키텍처 및 분류 | |

| 명령 집합 | 아이테니엄 |

| 물리 사양 | |

| 코어 |

|

| 소켓 |

|

| 제품, 모델, 변종 | |

| 코어명 |

|

Itanium 2 프로세서는 2002년에 출시되었습니다.메모리 서브시스템의 비효율성에 기인한 오리지널 Itanium 프로세서의 퍼포먼스 문제를 대부분 해소했습니다.

2003년 AMD는 자체 64비트 아키텍처(x86-64)를 구현한 Opteron을 출시했습니다.Opteron은 x86에서 쉽게 업그레이드할 수 있었기 때문에 엔터프라이즈 서버 공간에서 빠르게 받아들여졌습니다.인텔은 2004년에 [6]Xeon 마이크로프로세서에 x86-64(Em64t)를 실장했습니다.

2005년 11월 주요 Itanium 서버 제조업체는 인텔 및 다수의 소프트웨어 벤더와 협력하여 Itanium Solutions Alliance를 결성하여 아키텍처를 촉진하고 소프트웨어 [16]포팅을 가속화합니다.

2006년에 인텔은 퍼포먼스를 약 2배로 향상시켜 소비전력을 [17]약 20% 삭감한 듀얼 코어 프로세서인 Montecito(Itanium 2 9000 시리즈)를 출시했습니다.

Itanium 9300 (Tukwila) : 2010

Itanium 9300 시리즈 프로세서(코드명 Tukwila)는 2010년 2월 8일 출시되었으며 성능과 메모리 [18]용량이 향상되었습니다.투킬라는 원래 2007년에 출시될 [19]예정이었다.

디바이스는 65 nm 프로세스를 사용하며, 2 ~4개의 코어, 최대 24 MB의 온다이 캐시, 하이퍼스레딩 테크놀로지 및 내장 메모리 컨트롤러를 포함합니다.Double-Device Data Correction(DDC; 이중 디바이스 데이터 수정)을 구현하여 메모리 오류를 해결합니다.또한 Tukwila는 인텔 QuickPath Interconnect(QPI)를 구현하여 Itanium 버스 기반 아키텍처를 대체합니다.프로세서 간 최대 대역폭은 96GB/s, 메모리 최대 대역폭은 34GB/s입니다.QuickPath를 사용하면 프로세서는 메모리 컨트롤러를 내장하고 QPI 인터페이스를 사용하여 다른 프로세서 및 I/O허브에 직접 접속하여 메모리에 직접 접속할 수 있습니다.QuickPath는 Nehalem 마이크로아키텍처를 사용하는 인텔 프로세서에서도 사용되고 있기 때문에 Tukwila와 Nehalem은 같은 칩셋을 [20]사용할 수 있습니다.Tukwila에는 4개의 메모리 컨트롤러가 내장되어 있습니다.각 컨트롤러는 Nehalem 기반의 Xeon 프로세서 코드명 Beckton과 [22]마찬가지로 별도의 메모리 [21]컨트롤러를 통해 여러 개의 DDR3 DIMM을 지원합니다.

아이테니엄 9500 (Poulson) : 2012

이 섹션은 업데이트해야 합니다.하여 이 할 수 있도록 . (2017년 4월) |

Itanium 9500 시리즈 프로세서(코드명 Poulson)는 Tukwila의 후속 프로세서로서 8개의 코어를 갖추고 있으며, 12개의 광범위한 문제 아키텍처, 멀티스레딩 기능 확장 기능 및 특히 [20][23][24]가상화에서 병렬 처리를 활용하기 위한 새로운 지침을 제공합니다.Poulson L3 캐시 크기는 32MB입니다. L2 캐시 크기는 [25]코어당 6MB, 512IKB, 256DKB입니다.다이 크기는 544mm²로 이전 Tukwila(698.75mm²)[26][27]보다 작습니다.

ISSCC 2011에서 인텔은 "A 32nm 31억 트랜지스터 12-Wide-Issue Itanium Processor for Mission Critical Servers"[25][28]라는 논문을 발표했습니다.인텔이 ISSCC에서 Itanium 마이크로프로세서에 대한 자세한 내용을 공개한 이력을 볼 때 이 문서는 Poulson을 언급하고 있을 가능성이 높습니다.분석가 David Kanter는 Poulson이 최대 2개의 스레드를 사용하는 고급 형태의 멀티 스레드를 갖춘 새로운 마이크로 아키텍처를 사용하여 싱글 스레드 워크로드와 멀티 스레드 [29]워크로드의 성능을 향상시킬 것으로 예측하고 있습니다.하치입스 [30][31]컨퍼런스에서 새로운 정보가 발표됐어요새로운 정보에 의해 멀티스레딩, 복원력 향상(Instruction Replay RAS) 및 몇 가지 새로운 명령(스레드 우선 순위, 정수 명령, 캐시 프리페치, 데이터 액세스 힌트)이 향상되었습니다.

아이테니엄 9700 (Kittson) : 2017

Kittson은 9500 Poulson과 동일하지만 조금 [32]더 높은 기록을 가지고 있다.

종료일 : 2021

2019년 1월, 인텔은 Kittson이 2020년 1월, 2021년 [32][33]7월로 단종한다고 발표했습니다.

계획된 후계자는 없습니다.

아키텍처

인텔은 Itanium 명령어[34] 세트를 폭넓게 문서화하고 있으며 테크니컬 프레스에서는 [4][7]개요를 제공하고 있습니다.그 건축물은 그 역사 동안 여러 번 이름이 바뀌었다.HP는 원래 그것을 PA-WideWord라고 불렀다.인텔은 인텔 Itanium 아키텍처를 채택하기 전에 IA-64, 그 후 Itanium 프로세서 아키텍처(IPA)[35]라고 불렀습니다만, 아직도 IA-64라고 불리고 있습니다.

64비트 레지스터가 풍부한 명시적 병렬 아키텍처입니다.기본 데이터 워드는 64비트이며 바이트 주소 지정이 가능합니다.논리 주소 공간은 2바이트입니다64.이 아키텍처는 예측, 추측 및 분기 예측을 구현합니다.파라미터 전달에는 가변 크기 레지스터 윈도우 설정을 사용합니다.루프의 병렬 실행을 가능하게 하기 위해서도 같은 메커니즘이 사용됩니다.추측, 예측, 예측 및 이름 변경은 컴파일러가 제어합니다. 각 명령어에는 이를 위한 추가 비트가 포함됩니다.이 접근방식은 아키텍처의 구별되는 특징입니다.

아키텍처는 다수의 [36][37][38]레지스터를 구현합니다.

- 추측 실행에 사용되는 128개의 일반 정수 레지스터(64비트 + 1개의 트랩 비트("NaT")).이 중 32개는 정적이고 나머지 96개는 가변 크기의 레지스터 창을 사용하여 적층되거나 파이프라인 루프용으로 회전합니다.

gr0항상 0이 됩니다. - 128 부동소수점 레지스터부동소수점 레지스터의 길이는 중간 결과의 정밀도를 유지하기 위해 82비트입니다.정수 레지스터와 같은 전용 "NaT" 트랩 비트 대신 부동 소수점 레지스터에는 NaN과 유사하지만 구별되는 "NaTVal"("Not a Thing Value")라는 트랩 값이 있습니다.또한 32개의 정적 레지스터와 96개의 창 또는 회전 레지스터가 있습니다.

fr0항상 +0.0을 읽습니다.fr1는 항상 +1.0 입니다. - 64개의 1비트 술어 레지스터또한 32개의 정적 레지스터와 96개의 창 또는 회전 레지스터가 있습니다.

pr0항상 1(true)이 됩니다. - 8개의 지점 레지스터, 간접 점프 주소.

br0를 사용하여 함수를 호출할 때 반환 주소로 설정됩니다.br.call. - 128개의 특수 목적(또는 "어플리케이션") 레지스터.일반 어플리케이션이 아닌 커널에 주로 관심이 있습니다.예를 들어, 1개의 레지스터가

bsp는 두 번째 스택을 가리킵니다.이 스택에서는 레지스터 창이 닫힐 때 하드웨어가 자동으로 레지스터를 흘립니다.

각 128비트 명령어는 번들로 불리며 각각 41비트 명령을 유지하는 3개의 슬롯과 각 슬롯에 어떤 유형의 명령이 있는지 나타내는 5비트 템플릿을 포함합니다.이러한 유형은 M 유닛(메모리 명령), I 유닛(정수 ALU, 비 ALU 정수 또는 롱 즉시 확장 명령), F 유닛(부동소수점 명령) 또는 B 유닛(브랜치 또는 롱 브랜치 확장 명령)입니다.또한 템플릿은 중지 전후의 데이터 간에 데이터 종속성이 존재함을 나타내는 중지 부호화도 수행합니다.한 쌍의 스톱 사이에 있는 모든 명령은 번들에 관계없이 명령 그룹을 구성하며 많은 유형의 데이터 의존성이 없어야 합니다.이러한 지식으로 프로세서는 복잡한 데이터 분석을 수행할 필요 없이 명령을 병렬로 실행할 수 있습니다.이러한 정보는 명령이 이미 실행되었을 때 분석이 완료되었기 때문입니다.작성되었습니다.

각 슬롯에서는, 몇개의 명령어를 제외한 모든 명령어가, 술어 레지스터를 지정해, 그 값(참 또는 거짓)에 의해서 명령이 실행되는지 아닌지가 결정됩니다.항상 실행해야 하는 사전 지정된 명령은 다음과 같습니다.pr0그것은 항상 사실로 읽힌다.

IA-64 어셈블리 언어와 명령어 형식은 인간이 아닌 컴파일러에 의해 작성되도록 의도적으로 설계되었다.명령어는 3개의 명령어가 허용된 템플릿과 일치하도록 3개의 명령어로 묶어야 합니다.명령어는 특정 유형의 데이터 종속성 간에 중지 명령을 발행해야 하며, 또한 허용된 템플릿에 따라 제한된 장소에서만 중지 명령을 사용할 수 있습니다.

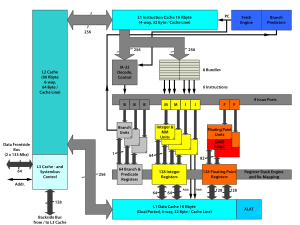

명령 실행

가져오기 메커니즘은 L1 캐시에서 파이프라인으로 클럭당 최대 2개의 번들을 읽을 수 있습니다.컴파일러가 이를 최대한 활용할 수 있는 경우 프로세서는 클럭 사이클당 6개의 명령을 실행할 수 있습니다.프로세서에는 30개의 기능 실행 유닛이 11개의 그룹으로 구성되어 있습니다.각 유닛은 명령 집합의 특정 서브셋을 실행할 수 있으며, 실행이 데이터 대기를 정지하지 않는 한 각 유닛은 사이클당 1개의 명령 속도로 실행된다.그룹 내의 모든 유닛이 명령 집합의 동일한 서브셋을 실행하는 것은 아니지만 공통 명령어는 여러 유닛에서 실행할 수 있습니다.

실행 유닛 그룹에는 다음이 포함됩니다.

- 범용 ALU×6, 정수 유닛×2, 교대 유닛×1

- 4개의 데이터 캐시 유닛

- 6개의 멀티미디어 유닛, 2개의 병렬 시프트 유닛, 1개의 병렬 멀티플, 1개의 인구 수

- 2개의 82비트 부동소수점 곱셈 누적 유닛, 2개의 SIMD 부동소수점 곱셈 누적 유닛([39]각각2개의 32비트 연산)

- 3개의 브런치 유닛

컴파일러는 명령어를 동시에 실행할 수 있는6개의 세트로 그룹화하는 것이 이상적입니다.부동소수점 유닛은 곱셈-누적 연산을 구현하기 때문에 어플리케이션에 곱셈과 덧셈이 필요한 경우 단일 부동소수점 명령으로 두 가지 명령의 작업을 수행할 수 있습니다.이것은 과학적 처리에서 매우 일반적입니다.이 경우 프로세서는 사이클당 4개의 FLOP를 실행할 수 있습니다.예를 들어 800MHz Itanium의 이론정격은 3.2GFLOPS였고 가장 빠른 Itanium 2의 1.67GHz는 6.67GFLOPS였습니다.

실제로 사용 가능한 번들템플릿의 데이터 의존성이나 제한 등의 이유로 모든 슬롯이 유용한 명령으로 채워지는 것은 아니기 때문에 프로세서가 충분히 활용되지 않는 경우가 많습니다.기존의 RISC 프로세서의 명령당 32비트에 비해 코드 밀도가 가장 높은 코드에는 명령당 42.6비트가 필요합니다.슬롯의 낭비에 의한 no-ops는 코드의 밀도를 더욱 낮춥니다.추측 부하에 대한 추가 명령과 브랜치 및 캐시에 대한 힌트는 최신 컴파일러를 사용하더라도 최적으로 생성하기 어렵습니다.

메모리 아키텍처

2002년부터 2006년까지 Itanium 2 프로세서는 공통 캐시 계층을 공유했습니다.16KB의 레벨 1 명령 캐시와 16KB의 레벨 1 데이터 캐시를 보유하고 있었습니다.L2 캐시는 (명령어와 데이터 모두) 통합되었으며 크기는 256KB입니다.레벨 3 캐시도 통합되었으며 크기가 1.5MB에서 24MB까지 다양했습니다.256KB L2 캐시에는 메인 산술 논리 유닛(ALU)을 방해하지 않고 세마포 연산을 처리하기에 충분한 논리가 포함되어 있습니다.

메인 메모리는 버스를 통해 오프칩 칩셋에 액세스합니다.Itanium 2 버스는 처음에는 McKinley 버스라고 불렸지만, 현재는 보통 Itanium 버스라고 불리고 있습니다.새로운 프로세서가 출시됨에 따라 버스 속도는 꾸준히 향상되었습니다.버스는 클럭 사이클당 2×128비트를 전송하므로 200MHz McKinley 버스는 6.4GB/s, 533MHz Montecito 버스는 17.056GB/s를 전송합니다[40].

아키텍처 변경

2006년 이전에 출시된 Itanium 프로세서는 IA-32 아키텍처를 하드웨어로 지원하여 레거시 서버 애플리케이션을 지원했지만 IA-32 코드의 성능은 네이티브 코드보다 훨씬 나빴으며 동시대의 x86 프로세서의 성능보다 나빴습니다.2005년에 인텔은 IA-32 이그제큐션 레이어(IA-32 EL)를 개발했습니다.이는 보다 뛰어난 성능을 제공하는 소프트웨어 에뮬레이터입니다.따라서 Montecito에서는 IA-32 코드에 대한 하드웨어 지원이 폐지되었습니다.

2006년, Montecito의 릴리스에 의해, 인텔은 다음과 [41]같은 기본적인 프로세서·아키텍쳐(architecture)를 다수 강화했습니다.

- 하드웨어 멀티스레딩:각 프로세서 코어는 2개의 실행 스레드의 컨텍스트를 유지합니다.메모리 액세스 중에 한쪽 스레드가 정지하면 다른 쪽 스레드가 실행될 수 있습니다.인텔은 이를 일부 x86 및 x86-64 마이크로프로세서에 통합된 하이퍼스레딩 테크놀로지와의 구별을 위해 "커서스 멀티스레딩"이라고 부릅니다.

- 가상화를 위한 하드웨어 지원:인텔은 핵심 가상화 기능에 하드웨어 지원을 제공하는 인텔 버추얼라이제이션 테크놀로지(인텔 VT-i)를 추가했습니다.가상화를 통해 소프트웨어 "하이퍼바이저"는 프로세서 상에서 여러 운영 체제 인스턴스를 동시에 실행할 수 있습니다.

- 캐시 확장 기능:Montecito는 스플릿 L2 캐시를 추가했습니다.이 캐시에는 지시용 전용 1MB L2 캐시가 포함되어 있습니다.원래 256KB L2 캐시가 전용 데이터 캐시로 변환되었습니다.또한 Montecito는 최대 12MB의 온다이 L3 캐시를 포함했습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ Morgan, Timothy (2008-05-27). "The Server Biz Enjoys the X64 Upgrade Cycle in Q1". IT Jungle. Archived from the original on 2016-03-03. Retrieved 2008-10-29.

- ^ a b "Inventing Itanium: How HP Labs Helped Create the Next-Generation Chip Architecture". HP Labs. June 2001. Archived from the original on 2012-03-04. Retrieved 2007-03-23.

- ^ Fisher, Joseph A. (1983). "Very Long Instruction Word architectures and the ELI-512". Proceedings of the 10th annual international symposium on Computer architecture. International Symposium on Computer Architecture. New York, NY, USA: Association for Computing Machinery (ACM). pp. 140–150. doi:10.1145/800046.801649. ISBN 0-89791-101-6.

- ^ a b De Gelas, Johan (2005-11-09). "Itanium–Is there light at the end of the tunnel?". AnandTech. Archived from the original on 2012-05-03. Retrieved 2007-03-23.

- ^ Takahashi, Dean (2009-05-08). "Exit interview: Retiring Intel chairman Craig Barrett on the industry's unfinished business". VentureBeat. Archived from the original on 2018-04-21. Retrieved 2009-05-17.

- ^ a b c "Itanium: A cautionary tale". Tech News on ZDNet. 2005-12-07. Archived from the original on 2008-02-09. Retrieved 2007-11-01.

- ^ a b Shankland, Stephen (1999-07-08). "Intel's Merced chip may slip further". CNET News. Archived from the original on 2012-10-24. Retrieved 2008-10-16.

- ^ "Microprocessors - VLIW, The Past" (PDF). NY University. 2002-04-18. Archived (PDF) from the original on 2018-06-27. Retrieved 2018-06-26.

- ^ Vijayan, Jaikumar (1999-07-16). "ComputerWorld: Solaris for IA-64 coming this fall". Linuxtoday. Archived from the original on 2009-02-13. Retrieved 2008-10-16.

- ^ Wolfe, Alexander (1999-09-02). "Core-logic efforts under way for Merced". EE Times. Archived from the original on 2016-03-06. Retrieved February 27, 2016.

- ^ "Sun Introduces Solaris Developer Kit for Intel to Speed Development of Applications On Solaris; Award-winning Sun Tools Help ISVs Easily Develop for Solaris on Intel Today". Business Wire. 1998-03-10. Archived from the original on 2004-09-20. Retrieved 2008-10-16.

- ^ "Next-generation chip passes key milestone". CNET News.com. 1999-09-17. Archived from the original on 2011-08-09. Retrieved 2007-11-01.

- ^ Kanellos, Michael (1999-10-04). "Intel names Merced chip Itanium". CNET News.com. Archived from the original on 2015-12-30. Retrieved 2007-04-30.

- ^ Finstad, Kraig (1999-10-04). "Re:Itanium". USENET group comp.sys.mac.advocacy. Retrieved 2013-12-19.

- ^ Linley Gwennap (2001-06-04). "Itanium era dawns". EE Times. Archived from the original on 2019-12-17. Retrieved 2020-01-19.

- ^ "Itanium Solutions Alliance". ISA web site. Archived from the original on 2008-09-08. Retrieved 2007-05-16.

- ^ Niccolai, James (2008-05-20). "'Tukwila' Itanium servers due early next year, Intel says". ComputerWorld. Archived from the original on 2009-02-08. Retrieved 2008-10-16.

- ^ Burt, Jeffrey (2010-02-08). "New Intel Itanium Offers Greater Performance, Memory Capacity". eWeek.

- ^ Merritt, Rick (2005-03-02). "Intel preps HyperTransport competitor for Xeon, Itanium CPUs". EE Times. Archived from the original on 2018-11-30. Retrieved 2018-11-30.

- ^ a b Tan, Aaron (2007-06-15). "Intel updates Itanium line with 'Kittson'". ZDNet. Archived from the original on 2020-08-27. Retrieved 2021-02-22.

- ^ Stokes, Jon (2009-02-05). "Intel delays quad Itanium to boost platform memory capacity". Ars Technica. Archived from the original on 2012-01-22. Retrieved 2009-02-05.

- ^ Ng, Jansen (10 February 2009). "Intel Aims for Efficiency With New Server Roadmap". DailyTech. Archived from the original on 2009-02-13. Retrieved 2009-02-10.

- ^ "Poulson: The Future of Itanium Servers". realworldtech.com. 2011-05-18. Archived from the original on 2011-06-10. Retrieved 2011-05-24.

- ^ "Intel Discloses Architecture Features of Next Itanium Processor at Hot Chips 2011" (PDF) (Press release). 2011-08-19. Archived from the original (PDF) on 2012-03-24. Retrieved 2011-08-19.

- ^ a b Riedlinger, Reid J.; Bhatia, Rohit; Biro, Larry; Bowhill, Bill; Fetzer, Eric; Gronowski, Paul; Grutkowski, Tom (2011-02-24). "A 32nm 3.1 billion transistor 12-wide-issue Itanium® processor for mission-critical servers". 2011 IEEE International Solid-State Circuits Conference. pp. 84–86. doi:10.1109/ISSCC.2011.5746230. ISBN 978-1-61284-303-2. S2CID 20112763.

- ^ Merritt, Rick (2010-11-23). "Researchers carve CPU into plastic foil". EE Times. Archived from the original on 2013-05-20. Retrieved 2020-01-19.

- ^ O'Brien, Terrence (2011-08-22). "Intel talks up next-gen Itanium: 32nm, 8-core Poulson". Engadget. Archived from the original on 2018-04-21. Retrieved 2020-01-19.

- ^ "ISSCC 2011" (PDF). Archived from the original (PDF) on 2012-03-02. Retrieved 2011-11-20.

- ^ Kanter, David (2010-11-17). "Preparing for Tukwila: The Next Generation of Intel's Itanium Processor Family". Real World Tech. Archived from the original on 2010-11-23. Retrieved 2010-11-17.

- ^ "Itanium Poulson Update - Greater Parallelism, New Instruction Replay & More: Catch the details from Hotchips!". 2011-08-19. Archived from the original on 2012-02-11. Retrieved 2012-01-23.

- ^ "Intel Itanium Hotchips 2011 Overview". 2011-08-18. Archived from the original on 2012-02-14. Retrieved 2012-01-23.

- ^ a b Anton Shilov (January 31, 2019). "Intel to Discontinue Itanium 9700 'Kittson' Processor, the Last of the Itaniums". AnandTech. Archived from the original on April 16, 2019. Retrieved April 16, 2019.

- ^ "Product Change Notification" (PDF). January 30, 2019. Archived (PDF) from the original on February 1, 2019. Retrieved May 9, 2019.

- ^ "Intel Itanium Architecture Software Developer's Manual". Archived from the original on 2019-04-08. Retrieved 2019-04-08.

- ^ "HPWorks Newsletter". September 2001. Archived from the original on 2008-11-20. Retrieved 2008-01-24.

- ^ Chen, Raymond (2015-07-27). "The Itanium processor, part 1: Warming up". Archived from the original on 2018-11-01. Retrieved 2018-10-31.

- ^ Chen, Raymond (2015-07-28). "The Itanium processor, part 2: Instruction encoding, templates, and stops". Archived from the original on 2018-11-01. Retrieved 2018-10-31.

- ^ Chen, Raymond (2015-07-29). "The Itanium processor, part 3: The Windows calling convention, how parameters are passed". Archived from the original on 2018-11-01. Retrieved 2018-10-31.

- ^ 샤랑파니, 하스, 아로라, 켄(2000)."Itanium 프로세서 마이크로아키텍처"IEEE Micro. 페이지 38-39.

- ^ Cataldo, Anthony (2001-08-30). "Intel outfits Itanium processor for faster runs". EE Times. Archived from the original on 2020-08-01. Retrieved 2020-01-19.

- ^ "Intel product announcement". Intel web site. Archived from the original on November 7, 2007. Retrieved 2007-05-16.

외부 링크

- 인텔 아이테니엄 홈페이지

- Hewlett Packard Enterprise Integrity Servers 홈페이지

- 인텔(R) Itanium

- 일부 Itanium 2 마이크로아키텍처 정보는 Wayback Machine (아카이브 2007-02-23)에서 문서화되어 있습니다.

- IA-64 튜토리얼(코드 예 포함)

- HP의 Itanium 문서