멀티플렉서

Multiplexer전자공학에서 멀티플렉서(또는 멀티플렉서라고도 함)는 여러 아날로그 또는 디지털 입력 신호 중에서 선택하고 선택한 입력을 단일 출력 [1]라인으로 전달하는 장치입니다.선택 작업은 선택 라인으로 알려진 별도의 디지털 입력 세트에 의해 수행됩니다. 2개 의 멀티플렉서에는의 선택 라인이 ,[2] 이 라인은 출력으로 전송할 입력 라인을 선택하는 데 사용됩니다.

멀티플렉서는 입력신호당 하나의 디바이스를 갖는 대신 예를 들어 하나의 아날로그-디지털 변환기 또는 하나의 통신전송매체 등 여러 입력신호가 하나의 디바이스 또는 자원을 공유하는 것을 가능하게 한다.멀티플렉서를 사용하여 여러 변수의 부울 함수를 구현할 수도 있습니다.

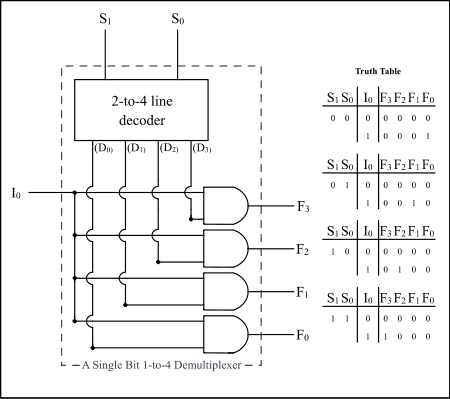

반대로 디멀티플렉서(또는 디멀티플렉서)는 단일 입력을 받아 단일 입력에 접속된 호환 가능한 멀티플렉스 출력 신호와 공유 선택 회선을 선택하는 장치이다.멀티플렉서는, 수신측에서 [1]상보적인 디멀티플렉서와 함께 사용되는 경우가 많습니다.

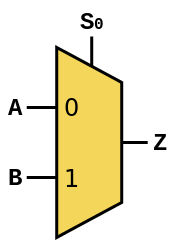

전자 멀티플렉서는 멀티입력 싱글출력 스위치로, 디멀티플렉서는 싱글입력 멀티출력 스위치로 [3]간주할 수 있습니다.멀티플렉서의 도식 기호는 입력 핀이 들어 있는 긴 평행 측과 출력 [4]핀이 들어 있는 짧은 평행 측을 가진 이등변 사다리꼴입니다.오른쪽의 도식은 왼쪽에 2-to-1 멀티플렉서, 오른쪽에 동등한 스위치를 나타냅니다. sel 와이어는 입력을 출력에 연결합니다.

적용들

멀티플렉서는 메모리 칩이든 하드웨어 주변기기든 특정 소스에서 데이터를 선택하는 컴퓨터 시스템의 일부입니다.컴퓨터는 멀티플렉서를 사용하여 데이터 및 주소 버스를 제어하고 프로세서가 여러 데이터 소스에서 데이터를 선택할 수 있도록 합니다.

디지털 통신에서 멀티플렉서는 멀티플렉서의 단일 출력을 디멀티플렉서의 단일 입력(시분할 다중화)에 연결하여 단일 채널을 통해 여러 연결을 허용합니다.오른쪽 이미지는 이 장점을 보여줍니다.이 경우 데이터 소스별로 별도의 채널을 구현하기 위한 비용은 다중화/복제 기능을 제공하기 위한 비용과 불편함보다 높아집니다.

데이터 링크의 수신측에서는, 통상, 1개의 데이터 스트림을 원래의 스트림으로 되돌리기 위해서 보완적인 디멀티플렉서가 필요합니다.경우에 따라서는 원단 시스템은 단순한 디멀티플렉서보다 더 큰 기능을 가지고 있을 수 있습니다.또, 디멀티플렉싱은 기술적으로 아직 발생하고 있습니다만, 결코 개별적으로 실장되지 않는 경우가 있습니다.예를 들어 멀티플렉서가 다수의 IP 네트워크 사용자에게 서비스를 제공하고 나서 라우터에 직접 공급되는 경우입니다.라우터는 링크 전체의 내용을 즉시 라우팅 프로세서로 읽어들이고 메모리 내의 디멀티플렉싱을 IP 섹션으로 직접 변환합니다.

많은 경우 멀티플렉서와 디멀티플렉서는 단일 기기에 결합되어 있으며, 이를 단순히 멀티플렉서라고 합니다.대부분의 통신 시스템이 양방향으로 전송되기 때문에 두 회로 소자는 모두 전송 링크의 양 끝에 필요합니다.

아날로그 회로 설계에서 멀티플렉서는 여러 입력에서 선택한 하나의 신호를 단일 출력에 연결하는 특수한 유형의 아날로그 스위치입니다.

디지털 멀티플렉서

디지털 회로 설계에서 셀렉터 와이어는 디지털 가치가 있습니다.2-to-1 멀티플렉서의 경우 로직 값 0은 I 을 출력에 하고 로직 값 1은 1})을 출력에 합니다.대형 멀티플렉서에서는 셀렉터 핀의 수는 2 ( ) { \ \ _ 2} ) \ \ } 입니다.서n { \ n}은 입력 수입니다.

예를 들어, 9~16개의 입력에는 4개의 셀렉터 핀이, 17~32개의 입력에는 5개의 셀렉터 핀이 필요합니다.이러한 선택기 핀에 표시되는 이진 값에 따라 선택한 입력 핀이 결정됩니다.

2-to-1 멀티플렉서에는 부울 방정식이 있습니다.서 A A와B(\ B는 2개의 입력, 은 셀렉터 입력,(\ Z는 출력입니다.

이것은 진실 표로 표현될 수 있다:

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

또는 간단한 표기법:

| 0 | A |

| 1 | B |

다음 표는 S {\}=일 때 Z { Z이지만 0 Z = B(\ }=1。이 2-to-1 및 2-displaystyle Gate를 직접 실현하려면 , 2개의 게이트가 필요합니다.이것이 수학적으로 정확하지만, 직접적인 물리적 구현은 [5]억제하기 위해 추가 관문이 필요한 경주 조건에 노출되기 쉽다.

대형 멀티플렉서도 일반적이며 위에서 설명한 바와 같이 n개의\ 입력에 2( n )、 \ \ _ ( ) \ \ }셀렉터 핀이 필요합니다.그 외의 일반적인 사이즈는, 4 대 1, 8 대 1, 및 16 대 1 입니다.디지털 로직은 바이너리 값을 사용하기 때문에 2의 거듭제곱(4, 8, 16)을 사용하여 주어진 수의 셀렉터 입력에 대한 입력 수를 최대한 제어합니다.

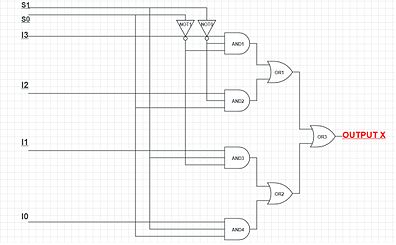

4-to-1 멀티플렉서의 부울 방정식은 다음과 같습니다.

다음의 4-to-1 멀티플렉서는 3스테이트 버퍼와 AND 게이트로 구성됩니다(AND 게이트가 디코더로 동작합니다).

의 첨자는 해당 입력이 통과하는 바이너리 제어 입력의 10진수 값을 나타냅니다.

멀티플렉서 체인

대형 멀티플렉서는 소형 멀티플렉서를 체인으로 연결하여 구성할 수 있습니다.예를 들어 8대1 멀티플렉서는 2개의 4-to-1 멀티플렉서와 1개의 2-to-1 멀티플렉서로 만들 수 있습니다.4 대 1 멀티플렉서 출력 2개가 2 대 1로 공급되며, 4 대 1의 셀렉터 핀이 병렬로 배치되어 총 셀렉터 입력 수가 3으로 8 대 1에 해당합니다.

멀티플렉싱을 제공하는 IC 목록

다음 표의 7400 시리즈 부품 번호의 경우 "x"가 로직 패밀리입니다.

| IC 번호 | 기능. | 출력 상태 |

|---|---|---|

| 74배속 | 쿼드 2:1 멀티플렉스 | 출력은 지정된 입력과 동일합니다. |

| 74배속 | 쿼드 2:1 멀티플렉스 | 출력이 반전 입력입니다. |

| 74배속 | 듀얼 4:1 멀티플렉스 | 출력은 입력과 동일합니다. |

| 74 x 352 | 듀얼 4:1 멀티플렉스 | 출력이 반전 입력입니다. |

| 74x151A | 8:1 mux. | 두 출력 모두 사용 가능(즉, 보완 출력) |

| 74배속 | 8:1 mux. | 출력이 반전 입력입니다. |

| 74 x 150 | 16:1 mux. | 출력이 반전 입력입니다. |

디지털 디멀티플렉서

디멀티플렉서는 1개의 데이터 입력과 다수의 선택 입력을 받아 여러 개의 출력을 가집니다.선택 입력 값에 따라 데이터 입력을 출력 중 하나로 전달합니다.디멀티플렉서는 디멀티플렉서의 입력이 항상 참이면 디멀티플렉서가 바이너리 디코더로 동작하기 때문에 범용 로직을 설계하는 데 편리할 수 있습니다.즉, 올바른 출력 세트를 논리적으로 OR하여 선택 비트의 기능을 구성할 수 있습니다.

X가 입력이고 S가 셀렉터이고 A와 B가 출력인 경우:

디멀티플렉싱을 제공하는 IC 목록

다음 표의 7400 시리즈 부품 번호의 경우 "x"가 로직 패밀리입니다.

| IC 번호(7400) | IC 번호(4000) | 기능. | 출력 상태 |

|---|---|---|---|

| 74배속 | 듀얼 1:4 DEMUX | 출력이 반전 입력입니다. | |

| 74배속 | 듀얼 1:4 DEMUX | 출력은 오픈 컬렉터입니다. | |

| 74배속 | 1:8 demux. | 출력이 반전 입력입니다. | |

| 74 x 238 | 1:8 demux. | ||

| 74배속 | 1:16 demux. | 출력이 반전 입력입니다. | |

| 74 x 159 | CD4514/15 | 1:16 demux. | 출력은 오픈 컬렉터이며 입력과 동일합니다. |

PLD로서의 멀티플렉서

멀티플렉서는 부울 함수를 구현하기 위해 프로그래밍 가능한 로직 디바이스로도 사용할 수 있습니다.n개의 변수와 1개의 결과의 부울 함수는 n개의 셀렉터 입력을 가진 멀티플렉서로 구현할 수 있습니다.변수는 선택기 입력에 연결되며, 선택기 입력의 가능한 각 조합에 대한 함수 결과 0 또는 1은 해당 데이터 입력에 연결됩니다.변수 중 하나(예를 들어 D)를 반전하여 사용할 수 있는 경우 n-1 선택기 입력을 가진 멀티플렉서로도 충분합니다. 데이터 입력은 선택기 [6]입력의 각 조합에 대해 원하는 출력에 따라 0, 1, D 또는 ~D에 연결됩니다.

「 」를 참조해 주세요.

- Digital Subscriber Line Access Multiplexer(DSLAM)

- 역다중기

- 멀티플렉싱

- priority 인코더

- 규칙 184는 각 셀이 인접한 두 셀의 값을 다중화하는 셀 오토마톤이다.

- 통계 멀티플렉서

레퍼런스

- ^ a b Dean, Tamara (2010). Network+ Guide to Networks. Delmar. pp. 82–85. ISBN 978-1423902454.

- ^ Debashis, De (2010). Basic Electronics. Dorling Kindersley. p. 557. ISBN 9788131710685.

- ^ Lipták, Béla (2002). Instrument engineers' handbook: Process software and digital networks. CRC Press. p. 343. ISBN 9781439863442.

- ^ Harris, David (2007). Digital Design and Computer Architecture. Penrose. p. 79. ISBN 9780080547060.

- ^ Crowe, John; Hayes-Gill, Barrie (1998). "The multiplexer hazard". Introduction to Digital Electronics. Elsevier. pp. 111–3. ISBN 9780080534992.

- ^ Lancaster, Donald E. (1974). The TTL Cookbook. H.W. Sams. pp. 140–3. ISBN 9780672210358.

추가 정보

- Mano, M. Morris; Kime, Charles R. (2008). Logic and Computer Design Fundamentals (4th ed.). Prentice Hall. ISBN 978-0-13-198926-9.

외부 링크

Wiktionary의 멀티플렉서 사전 정의

Wiktionary의 멀티플렉서 사전 정의

출력에

출력에

2개의 입력,

2개의 입력,  셀렉터 입력,

셀렉터 입력, 출력입니다.

출력입니다.

때 Z

때 Z

첨자는 해당 입력이 통과하는 바이너리 제어 입력의 10진수 값을 나타냅니다.

첨자는 해당 입력이 통과하는 바이너리 제어 입력의 10진수 값을 나타냅니다.