파이프라인 스톨

Pipeline stall파이프라인 컴퓨터 프로세서의 설계에서 파이프라인 스톨은 [1]위험을 해결하기 위한 명령 실행의 지연이다.

세부 사항

표준 5단계 파이프라인에서 제어부는 복호화 단계에서 현재 실행 중인 명령이 기입되는 레지스터에서 복호화 명령을 읽을지 여부를 판정한다.이 상태가 지속될 경우 컨트롤 유닛은 명령을 한 클럭 사이클씩 정지시킵니다.또한 가져오기 단계의 명령이 프로그램의 [2]다음 명령에 의해 덮어쓰기되는 것을 방지하기 위해 해당 단계의 명령이 중지됩니다.

프로그램 카운터(PC) 레지스터를 사용하여 파이프라인에서 Import되는 현재 명령을 결정하는 Von Neumann 아키텍처에서 복호화 단계의 명령이 정지되었을 때 새로운 명령이 Import되는 것을 방지하기 위해 PC 레지스터의 값 및 Fetch 단계의 명령이 변경되는 것을 방지하기 위해 유지된다.. 경합을 일으키는 명령이 실행 [3]단계를 통과할 때까지 값이 유지됩니다.이러한 현상을 유체 파이프에 있는 기포와 비유하여 종종 기포라고 합니다.

일부 아키텍처에서는 파이프라인의 실행 단계가 항상 모든 사이클에서 작업을 수행해야 합니다.이 때, 실행 스테이지에 NOP(「조작 없음」) 명령을 공급해, 버블을 지나 플래시 할 때까지 버블을 실행한다.

예

타임라인

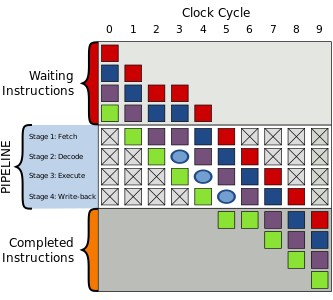

다음은 4단계 파이프라인을 통해 동일한 4개 명령을 2회 실행한 것입니다. 그러나 어떤 이유로든 사이클 #2에서 보라색 명령을 가져오는 것이 지연되면 버블이 생성되어 그 이후에 모든 명령이 지연됩니다.

|  |

| 통상적인 실행 | 버블에 의한 실행 |

기존 RISC 파이프라인

아래 예제는 5단계(IF = 명령 가져오기, ID = 명령 디코드, EX = 실행, MEM = 메모리 액세스, WB = 레지스터 라이트백)로 구성된 기존 RISC 파이프라인에 버블을 삽입하는 방법을 보여 줍니다.이 예에서는 첫 번째 명령의 MEM 단계(4단계) 후에 사용할 수 있는 데이터가 두 번째 명령의 EX 단계(3단계)에 의해 입력되어야 한다.버블이 없으면 EX 스테이지(3단계)는 이전 EX 스테이지의 출력에만 액세스할 수 있습니다.따라서 버블을 추가하면 데이터를 시간 역방향으로 전파할 필요 없이 시간 의존성이 해결됩니다(이는 불가능합니다.

| 과거로 되돌아가다 | 버블을 사용하여 문제 해결 |

|  |

「 」를 참조해 주세요.

레퍼런스

- ^ Patterson, David A.; Hennessy, John L., Computer Organization and Design (4 ed.), Morgan Kaufmann, p. 338

- ^ Patterson, David A; Hennessy, John L (2014), Computer organization and design: the hardware/software interface (5th ed.), p. 318, OCLC 1130276006, retrieved 2020-05-25

- ^ Patterson, David A.; Hennessy, John L., Computer Organization and Design (4 ed.), Morgan Kaufmann, p. 373