기존 RISC 파이프라인

Classic RISC pipeline컴퓨터 하드웨어의 역사에서 일부 초기 축소 명령 집합 컴퓨터 중앙 처리 장치(RISC CPU)는 현재 고전적인 RISC 파이프라인이라고 불리는 매우 유사한 아키텍처 솔루션을 사용했습니다.그 CPU는 MIPS, SPARC, Motorola 88000, 그리고 나중에는 교육용으로 개발된 개념의 CPU DLX입니다.

이러한 표준 스칼라 RISC 설계는 각각 사이클당 1개의 명령을 가져오고 실행하려고 합니다.각 설계의 주요 공통 개념은 5단계 실행 명령 파이프라인입니다.작동 중 각 파이프라인 단계는 한 번에 하나의 명령으로 작동합니다.이러한 각 단계는 상태를 유지하기 위한 플립 플랍 세트와 플립 플랍의 출력에 대해 작동하는 조합 로직으로 구성됩니다.

클래식한 5단계 RISC 파이프라인

명령 가져오기

이 명령어는 메모리에 상주하며 읽기까지 1주기가 소요됩니다.이 메모리는 전용 SRAM 또는 명령 캐시일 수 있습니다."지연"이라는 용어는 컴퓨터 공학에서 자주 사용되며, 작업이 시작된 후 완료될 때까지의 시간을 의미합니다.따라서 명령 페치는 1클럭 사이클의 지연을 가집니다(단일 사이클의 SRAM을 사용하는 경우 또는 명령이 캐시에 있는 경우).따라서 명령 가져오기 단계에서는 명령 메모리에서 32비트 명령을 가져옵니다.

프로그램 카운터(PC)는 명령 메모리에 표시되는 주소를 유지하는 레지스터입니다.사이클의 개시시에, 주소는 명령 메모리에 제시된다.그 후 사이클 중에 명령 메모리에서 명령이 읽히고 동시에 다음 PC를 결정하기 위한 계산이 수행됩니다.다음 PC의 계산은 PC를 4씩 늘려 다음 PC로 할지 분기/점프 계산 결과를 다음 PC로 할지 선택합니다.기존의 RISC 에서는, 모든 순서의 길이가 같은 것에 주의해 주세요(이것은 RISC 와 CISC 를 구별하는1가지입니다).원래의 RISC 설계에서는 명령의 사이즈는 4바이트이므로 명령 주소에 항상 4를 추가합니다.단, 분기, 점프 또는 예외의 경우 PC + 4를 사용하지 마십시오(아래 지연된 분기 참조).(현대의 일부 기계에서는 다음 명령 주소를 추측하기 위해 보다 복잡한 알고리즘(분기 예측 및 분기 대상 예측)을 사용합니다.)

명령 디코드

최초의 RISC 머신과 이전의 CISC 머신을 구별하는 또 다른 점은 RISC에 마이크로코드가 [2]없다는 것입니다.CISC 마이크로코드 명령의 경우 명령 캐시에서 일단 가져오면 명령 비트는 파이프라인 아래로 시프트되며, 여기서 각 파이프라인 스테이지의 단순한 조합 로직은 명령 비트로부터 직접 데이터 패스에 대한 제어 신호를 생성한다.이러한 CISC 설계에서는 전통적으로 디코딩 단계라고 불리는 단계에서는 디코딩이 거의 이루어지지 않습니다.이러한 디코딩 부족의 결과로 명령이 수행하는 작업을 지정하기 위해 더 많은 명령 비트를 사용해야 합니다.그러면 레지스터 인덱스 등의 비트가 줄어듭니다.

모든 MIPS, SPARC 및 DLX 명령에는 최대 2개의 레지스터 입력이 있습니다.디코드 스테이지에서는 명령 내에서 이들 2개의 레지스터의 인덱스를 식별하고 인덱스를 주소로서 레지스터 메모리에 제시한다.따라서 이름이 지정된 2개의 레지스터가 레지스터 파일에서 읽힙니다.MIPS 설계에서는 레지스터 파일에는 32개의 엔트리가 있습니다.

레지스터 파일을 읽는 것과 동시에, 이 스테이지의 명령 발행 로직은 파이프라인이 이 스테이지의 명령을 실행할 준비가 되어 있는지 여부를 판단한다.그렇지 않으면 문제 로직으로 인해 명령 가져오기 단계와 디코드 단계가 모두 중지됩니다.정지 사이클에서는 입력 플립 플랍이 새로운 비트를 수신하지 않기 때문에 그 사이클 동안 새로운 계산이 이루어지지 않습니다.

복호화된 명령이 분기 또는 점프일 경우 레지스터 파일 읽기와 병행하여 분기 또는 점프의 목표 주소를 계산한다.분기 조건은 다음 사이클(레지스터 파일 읽기 후)로 계산되며, 분기가 실행되거나 명령이 점프인 경우 계산한 증분 PC가 아닌 첫 번째 단계의 PC에 분기 타깃이 할당됩니다.일부 아키텍처는 명령 스루풋이 약간 감소하는 대신 실행 단계에서 산술 논리 유닛(ALU)을 사용했습니다.

디코드 스테이지에는 꽤 많은 하드웨어가 있었습니다.MIPS는 2개의 레지스터가 같으면 분기할 가능성이 있습니다.따라서 32비트 폭의 AND 트리가 레지스터 파일을 읽은 후에 연속적으로 실행되므로 이 스테이지에서 매우 긴 크리티컬 패스가 생성됩니다(즉, 1초당 사이클의 감소).또한 브랜치 타깃 계산에는 일반적으로 16비트의 추가와 14비트의 인크리더가 필요합니다.디코드 단계에서 브랜치를 해결함으로써 단일 사이클 브랜치가 패널티를 잘못 예측할 수 있었습니다.브랜치가 자주 사용되기 때문에(따라서 예측이 빗나갔기 때문에) 이 패널티를 낮게 유지하는 것이 매우 중요했습니다.

실행

실행 단계는 실제 계산이 발생하는 단계입니다.일반적으로 이 단계는 ALU와 비트 시프터로 구성됩니다.또한 다중 사이클 승수 및 분할기를 포함할 수 있습니다.

ALU는 부울 연산(및 nand, nor, noor, xor, xnor)을 수행하고 정수 더하기 및 빼기를 수행합니다.결과 외에 ALU는 일반적으로 결과가 0인지, 오버플로가 발생했는지 등의 상태 비트를 제공합니다.

비트 시프터는 변속과 회전을 담당합니다.

이러한 심플한 RISC 머신의 순서는, 동작의 타입에 따라, 다음의 3개의 지연 클래스로 나눌 수 있습니다.

- Register-Register 조작(단일 사이클 지연):더하기, 빼기, 비교 및 논리적 연산.실행 단계 동안, 두 개의 인수는 단순한 ALU에 공급되어 실행 단계가 끝날 때까지 결과를 생성했습니다.

- 메모리 레퍼런스(2 사이클 지연).모든 로드는 메모리에서 로드됩니다.실행 단계에서 ALU는 2개의 인수(레지스터와 상수 오프셋)를 추가하여 사이클 종료까지 가상 주소를 생성했습니다.

- 멀티 사이클 명령(다사이클 지연).정수 곱셈 및 나눗셈 및 모든 부동 소수점 연산.실행 단계 동안, 이러한 작업에 대한 피연산자는 멀티 사이클 곱셈/분할 장치에 공급되었습니다.나머지 파이프라인은 멀티플라이드/나눗셈 장치가 작동하는 동안 실행을 계속할 수 있었습니다.라이트백 단계와 로직을 복잡하게 만드는 것을 피하기 위해 멀티사이클 명령은 결과를 별도의 레지스터 세트에 기록했습니다.

메모리 액세스

데이터 메모리에 액세스 할 필요가 있는 경우는, 이 단계에서 실시합니다.

이 단계에서 단일 사이클 지연 명령은 결과를 다음 단계로 전송하기만 하면 됩니다.이 전송을 통해 1사이클 명령과 2사이클 명령 모두 항상 파이프라인의 같은 스테이지에 결과를 쓸 수 있으므로 레지스터 파일에 대한 쓰기 포트를 하나만 사용할 수 있으며 항상 사용할 수 있습니다.

많은 데이터 캐시 조직 중 가장 단순한 직접 매핑 및 가상 태그가 부착된 데이터 캐싱에는 2개의 SRAM이 사용됩니다. 하나는 데이터를 저장하고 다른 하나는 태그를 저장합니다.

라이트백

이 단계에서는 단일 사이클 명령과 2사이클 명령이 모두 결과를 레지스터 파일에 씁니다.2개의 다른 스테이지가 동시에 레지스터 파일에 액세스 하고 있는 것에 주의해 주세요.디코드 스테이지가 2개의 소스 레지스터를 읽고 있는 것과 동시에, 라이트백스테이지가 이전의 명령의 행선지 레지스터를 쓰고 있습니다.실제 실리콘에서는 이 문제가 발생할 수 있습니다(위험에 대한 자세한 내용은 아래 참조).이는 디코딩으로 읽히는 소스 레지스터 중 하나가 라이트백으로 쓰는 수신처 레지스터와 같을 수 있기 때문입니다.이 경우 레지스터 파일 내의 동일한 메모리셀이 동시에 읽혀지고 쓰이게 됩니다.실리콘에서는 메모리 셀의 많은 구현이 동시에 읽고 쓸 때 올바르게 작동하지 않습니다.

위험 요소

헤네시와 패터슨은 파이프라인에서 명령을 내리면 오답이 나오는 상황을 위해 위험이라는 용어를 만들었다.

구조적 위험

구조적 위험은 두 명령이 동시에 동일한 자원을 사용하려고 할 때 발생합니다.기존의 RISC 파이프라인은 하드웨어를 복제함으로써 이러한 위험을 회피했습니다.특히 브랜치 명령에서는 ALU를 사용하여 브랜치의 타깃주소를 계산할 수 있습니다.ALU가 디코드 단계에서 그 목적을 위해 사용되었을 경우, ALU 명령 뒤에 브랜치가 이어지면 두 명령이 동시에 ALU를 사용하려고 하는 것을 볼 수 있습니다.특수한 분기 타깃 가산기를 디코딩 단계로 설계하면 이 경합을 쉽게 해결할 수 있습니다.

데이터 위험

데이터가 레지스터 파일에서 사용 가능해지기 전에 무작정 예약된 명령이 데이터를 사용하려고 할 때 데이터 위험이 발생합니다.

기존의 RISC 파이프라인에서는 데이터 위험은 다음 두 가지 방법 중 하나로 회피됩니다.

솔루션 A.바이패스

바이패스는 오퍼랜드 포워딩이라고도 합니다.

CPU가 다음 코드를 실행하고 있다고 가정합니다.

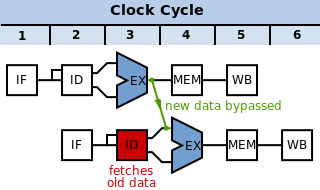

후보선수 r3,r4 -> r10 ; r3 - r4를 r10에 씁니다. 그리고. r10,r3 -> r11 ; r10 및 r3을 r11에 씁니다. 명령 가져오기 및 디코딩 단계는 첫 번째 명령 후 한 사이클 후에 두 번째 명령을 전송합니다.다음 그림과 같이 파이프라인을 따라 흐릅니다.

단순한 파이프라인에서 위험 고려 없이 데이터 위험은 다음과 같이 진행된다.

사이클 3에서는SUB명령어는 새로운 값을 계산합니다.r10같은 사이클에서AND동작은 디코딩되고 값은r10레지스터 파일에서 가져옵니다.하지만, 그SUB지시는 아직 그 결과를 쓰지 않았다r10이 문제는 보통 사이클 5(녹색 상자)에서 발생합니다.따라서 레지스터 파일에서 읽어 ALU로 전달된 값(의 Execute 단계에서)AND조작, 빨간색 상자)가 올바르지 않습니다.

대신, 우리는 다음에 의해 계산된 데이터를 전달해야 합니다.SUB실행 단계(즉, 다이어그램의 빨간색 원으로)로 돌아갑니다.AND정상적으로 라이트백되기 전에 동작합니다.이 문제의 해결책은 바이패스 멀티플렉서 쌍입니다.이러한 멀티플렉서는 디코드 스테이지의 끝에 위치하며, 플랩된 출력은 ALU에 대한 입력입니다. 각 멀티플렉서는 다음 중 하나를 선택합니다.

- 레지스터 파일 읽기 포트(즉, Naigive 파이프라인과 같은 디코드 단계의 출력): 빨간색 화살표

- ALU의 현재 레지스터 파이프라인(1단계에 따라 우회): 파란색 화살표

- 액세스 스테이지의 현재 레지스터 파이프라인(로드된 값 또는 전송된 ALU 결과 중 하나이며, 이는 두 단계의 바이패스를 제공합니다): 보라색 화살표.이를 위해서는 데이터가 1사이클씩 시간적으로 역방향으로 전달되어야 합니다.이 경우 버블을 삽입하여 버블을 정지시켜야 합니다.

AND데이터가 준비될 때까지 작업을 수행합니다.

디코드 스테이지 로직은 파이프라인의 실행 스테이지 및 액세스 스테이지의 명령에 의해 쓰여진 레지스터와 디코드 스테이지의 명령에 의해 읽혀진 레지스터를 비교하여 멀티플렉서가 최신 데이터를 선택하도록 한다.이러한 바이패스 멀티플렉서를 사용하면 ALU, 멀티플렉서 및 플립플롭의 지연만으로 파이프라인이 간단한 명령을 실행할 수 있습니다.멀티플렉서가 없으면 레지스터 파일을 쓴 후 읽는 지연 시간이 이러한 명령의 지연 시간에 포함되어야 합니다.

데이터는 시간 내에만 전달할 수 있습니다.데이터가 아직 처리되지 않은 경우 이전 단계로 우회할 수 없습니다.위의 경우, 데이터는 전송 됩니다(데이터 전송 시간:ANDALU에 등록할 준비가 되어 있습니다.SUB이미 계산되어 있습니다).

솔루션 B.파이프라인 인터록

다만, 다음의 순서를 고려해 주세요.

LD 표류하다 -> r10 그리고. r10,r3 -> r11 주소에서 읽은 데이터adr의 메모리 액세스 단계가 끝날 때까지 데이터 캐시에 존재하지 않습니다.LD설명.이때쯤이면AND명령어는 이미 ALU를 통과하고 있습니다.이 문제를 해결하려면 메모리의 데이터를 ALU 입력으로 제시간에 되돌려야 합니다.이건 불가능해.해결방법은 이 문제를 지연시키는 것입니다.AND한 사이클에 의한 지시.데이터 위험은 디코드 단계에서 감지되고, 가져오기 및 디코드 단계는 정지됩니다. 즉, 입력 플랩이 방지되므로 사이클 동안 동일한 상태를 유지합니다.다운스트림의 실행, 액세스 및 라이트백스테이지에서는 사이에 삽입된 추가 NOP(No-Operation Instruction)가 표시됩니다.LD그리고.AND지침들.

이 NOP는 파이프라인에 떠 있는 것처럼 파이프라인에 떠있기 때문에 파이프라인 버블이라고 불리며 자원을 점유하고 있지만 유용한 결과를 얻을 수 없습니다.데이터 위험을 감지하고 위험이 해소될 때까지 파이프라인을 정지시키는 하드웨어를 파이프라인 인터락이라고 합니다.

| 과거로 되돌아가다 | 버블을 사용하여 문제 해결 |

|  |

단, 데이터 전송에는 파이프라인 인터락을 사용할 필요가 없습니다.의 첫 번째 예SUB이어서AND그리고 두 번째 예시는LD이어서AND첫 번째 스테이지가 라이트백이 실현될 때까지3 사이클을 정지함으로써 해결할 수 있습니다.또한 레지스터 파일 내의 데이터가 올바르고 이로 인해 올바른 레지스터 값이 에 의해 취득됩니다.AND의 디코딩 단계이로 인해 프로세서는 아무것도 처리하지 않기 때문에 퍼포먼스에 큰 영향을 미치지만, 대기하는 전송 로직이 적어지기 때문에 클럭 속도가 향상될 수 있습니다.

이 데이터 위험은 컴파일러에 의해 프로그램의 머신 코드가 작성되면 매우 쉽게 검출될 수 있습니다.스탠포드 MIPS 머신은 이 경우 처음 2개의 파이프라인 스테이지를 검출하고 정지시키는 회로가 아니라 컴파일러에 의존하여 NOP 명령을 추가합니다.따라서 MIPS: Interlocked Pipeline Stage가 없는 마이크로프로세서라는 이름이 붙었습니다.컴파일러에 의해 추가된 NOP 명령어는 명령 캐시 적중률이 줄어들 정도로 프로그램 바이너리를 확장한 것으로 나타났습니다.스톨 하드웨어는 비싸긴 하지만 명령 캐시 적중률을 개선하기 위해 이후 설계에 다시 적용되었으며, 이 시점에서는 약어가 더 이상 의미가 없습니다.

위험 관리

제어 위험은 조건부 및 무조건적 분기에 의해 발생합니다.기존의 RISC 파이프라인은 디코드 단계에서 브랜치를 해결합니다.즉, 브랜치 분해능의 반복은 2 사이클 길이입니다.다음 3가지 의미가 있습니다.

- 분기 해상도의 반복은 명령 캐시 읽기, 레지스터 파일 읽기, 분기 조건 계산(MIPS CPU에서의 32비트 비교가 필요), 다음 명령 주소 멀티플렉서 등 많은 회로를 거칩니다.

- 분기 타깃과 점프 타깃은 레지스터 판독과 병행하여 계산되므로 일반적으로 RISC ISA에는 레지스터+오프셋주소로 분기하는 명령어가 없습니다.등록으로 건너뛰기가 지원됩니다.

- 취득한 브랜치에서는, 브랜치 직후의 명령은 항상 명령 캐시로부터 취득됩니다.이 명령을 무시하면 취해진 브랜치 IPC 패널티마다 1 사이클이 존재하며, 이는 충분히 큰 것입니다.

브랜치 퍼포먼스 문제를 해결하려면 다음 4가지 방법이 있습니다.

- 가져가지 않음 예측: 항상 명령 캐시에서 브랜치 뒤에 명령을 가져오지만 브랜치를 가져가지 않은 경우에만 명령을 실행합니다.분기를 취득하지 않으면 파이프라인이 가득 찬 상태로 유지됩니다.브런치를 취득하면, 명령이 플래시 되어(NOP인 것처럼 마크 되어), 1 사이클의 명령 종료 기회가 없어집니다.

- 예상되는 지점:항상 명령 캐시에서 분기 뒤에 명령을 가져오지만 분기를 가져온 경우에만 명령을 실행하십시오.컴파일러는 항상 이러한 브랜치의 브랜치 지연 슬롯을 채울 수 있습니다.브런치에는 이전 브랜치보다 적은 IPC 패널티가 할당됩니다.

- Branch Delay Slot : 항상 명령 캐시에서 브랜치 뒤에 명령을 가져와 브랜치를 취득한 경우에도 항상 실행합니다.브런치 지연 슬롯은 취득한 브랜치(약 60%) 또는 취득하지 않은 브랜치(약 40%)의 일부에 대해 IPC 패널티를 부과하는 대신 컴파일러가 브런치 지연 슬롯을 스케줄 할 수 없었던 브랜치에 대해 IPC 패널티를 부과합니다.SPARC, MIPS 및 MC88K 설계자는 ISA에 분기 지연 슬롯을 설계했습니다.

- 분기 예측:각 명령을 가져오는 것과 동시에 명령이 분기인지 점프인지 추측하고, 그렇다면 대상을 추측합니다.분기 또는 점프 후 사이클에서 추측된 타겟에서 명령을 가져옵니다.추측이 틀리면 잘못 가져온 대상을 플러시합니다.

지연된 분기는 첫째, 그 의미가 복잡하기 때문에 논란이 많았다.지연 브랜치는 다음 명령 후에 새 위치로 점프하는 것을 지정합니다.이 다음 명령어는 분기 후 명령 캐시에 의해 불가피하게 로드되는 명령입니다.

지연된 브랜치는 ISA 설계에서 단기적으로는 좋지 않은 선택이라는 비판을[by whom?] 받아 왔습니다.

- 컴파일러는 일반적으로 브랜치 뒤에 논리적으로 독립된 명령(브런치 뒤의 명령어를 지연 슬롯이라고 부릅니다)을 찾는 데 어려움을 겪기 때문에 NOP를 지연 슬롯에 삽입해야 합니다.

- Superscalar 프로세서는 사이클당 여러 명령을 가져오며 분기 예측의 형식을 가져야 하므로 분기가 지연되는 이점을 얻을 수 없습니다.알파 ISA는 슈퍼스칼라 프로세서를 위한 것이었기 때문에 지연된 브랜치를 생략했습니다.

- 브런치 지연의 가장 큰 단점은 브런치 지연으로 인한 제어 복잡성입니다.지연 슬롯 명령에 예외가 있는 경우 프로세서를 다음 명령이 아닌 브랜치로 재시작해야 합니다.예외에는 기본적으로 예외 주소와 재시작 주소라는2개의 주소가 있습니다.이 두 주소를 올바르게 생성하고 구별하는 것이 이후의 설계에서는 버그의 원인이 되었습니다.

예외

32비트 RISC가 2개의 큰 숫자를 추가하는 ADD 명령을 처리하여 결과가 32비트에 맞지 않는다고 가정합니다.

대부분의 아키텍처에서 제공하는 가장 간단한 솔루션은 래핑 산술입니다.가능한 최대 부호화 값보다 큰 숫자는 일치할 때까지 최상위 비트가 잘립니다.일반적인 정수 체계에서는 3000000000+3000000000=6000000000입니다.부호 없는 32비트랩 산술에서는 3000000000+3000000000=1705032704(60000000 mod 2^32)입니다.이것은 그다지 유용해 보이지 않을 수 있습니다.래핑 산술의 가장 큰 장점은 모든 연산의 결과가 잘 정의된다는 것입니다.

그러나 프로그래머는 특히 큰 정수(예: 리스프 또는 스킴)를 지원하는 언어로 프로그래밍하는 경우 래핑 산수를 원하지 않을 수 있습니다.일부 아키텍처(예: MIPS)는 결과를 포장하지 않고 오버플로우 시 특수 위치로 분기하는 특수 추가 작업을 정의합니다.문제의 수정은 대상 장소의 소프트웨어에서 담당합니다.이 특별한 가지를 예외라고 합니다.예외는 대상 주소가 명령 자체에 의해 지정되지 않고 명령 결과에 따라 분기 결정이 결정된다는 점에서 일반 분기와는 다릅니다.

기존의 RISC 머신 중 하나에서 가장 일반적인 소프트웨어 표시 예외는 TLB 미스입니다.

예외는 분기 및 점프와는 다릅니다. 다른 제어 흐름 변경은 디코딩 단계에서 해결되기 때문입니다.예외는 라이트백 단계에서 해결됩니다.예외가 검출되면 다음 명령(파이프라인의 이전 단계)은 무효로 표시되며 파이프 끝으로 흐르면 결과가 파기됩니다.프로그램 카운터는 특수 예외 핸들러의 주소로 설정되며 특수 레지스터는 예외 위치와 원인을 사용하여 기록됩니다.

소프트웨어에서 문제를 쉽게 해결하고 프로그램을 재시작하기 위해 CPU는 정확한 예외를 두어야 합니다.정확한 예외는 예외 명령까지의 모든 명령이 실행되었으며 예외 명령 및 그 이후의 모든 명령이 실행되지 않았음을 의미한다.

정확한 예외를 적용하기 위해 CPU는 소프트웨어 표시 상태에 대한 변경을 프로그램 순서로 커밋해야 합니다.이 순서대로 커밋은 기존의 RISC 파이프라인에서 매우 자연스럽게 이루어집니다.대부분의 명령어는 쓰기백 단계에서 결과를 레지스터 파일에 쓰기 때문에 이러한 쓰기는 자동으로 프로그램 순서로 수행됩니다.단, 스토어 명령어는 액세스 단계에서 그 결과를 스토어 데이터 큐에 씁니다.스토어 명령에서 예외가 발생하면 Store Data Queue 엔트리가 비활성화되어 나중에 캐시 데이터 SRAM에 기록되지 않습니다.

캐시 미스 처리

데이터 캐시 또는 명령 캐시에 필수 데이터 또는 명령이 포함되지 않는 경우가 있습니다.이 경우 CPU는 캐시가 필요한 데이터로 가득 찰 때까지 작업을 일시 중단한 후 실행을 재개해야 합니다.캐시를 필요한 데이터로 채우는 문제(및 제거된 캐시 라인이 메모리에 다시 기록될 수 있음)는 파이프라인 조직에 고유하지 않으며, 여기서는 설명하지 않습니다.

일시정지/재개 문제에 대처하기 위해서는 두 가지 전략이 있습니다.첫 번째는 글로벌 정지 신호입니다.이 신호가 활성화되면 일반적으로 각 스테이지 시작 시 클럭을 플립 플랍으로 게이트함으로써 명령이 파이프라인 아래로 이동하는 것을 방지합니다.이 전략의 단점은 플립 플랍 수가 많기 때문에 글로벌스톨 신호가 전파되는 데 오랜 시간이 걸린다는 것입니다.기계는 일반적으로 정지가 필요한 조건을 식별하는 사이클과 같은 사이클로 정지해야 하므로 정지 신호는 속도 제한 임계 경로가 됩니다.

일시정지/재개를 처리하는 또 다른 전략은 예외 로직을 재사용하는 것입니다.기계는 문제의 지시에 대해 예외를 두며 이후의 모든 명령은 무효화됩니다.캐시에 필요한 데이터가 가득 차면 캐시 누락의 원인이 된 명령이 다시 시작됩니다.데이터 캐시 누락 처리를 신속하게 하기 위해 명령을 재시작하여 데이터 캐시가 채워진 후 액세스 사이클이 1사이클 발생하도록 할 수 있습니다.

「 」를 참조해 주세요.

레퍼런스

- Hennessy, John L.; Patterson, David A. (2011). Computer Architecture, A Quantitative Approach (5th ed.). Morgan Kaufmann. ISBN 978-0123838728.

- ^ Patterson, David (12 May 1981). "RISC I: A Reduced Instruction Set VLSI Computer". Isca '81. pp. 443–457.

- ^ Patterson, David (12 May 1981). "RISC I: A Reduced Instruction Set VLSI Computer". Isca '81. pp. 443–457.