어드레스 디코더

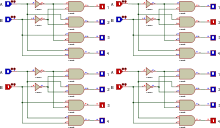

Address decoder디지털 전자제품에서 어드레스 디코더란 어드레스 비트에 대해 2개 이상의 입력과 디바이스 선택 [1]신호에 대해 1개 이상의 출력을 갖는 바이너리 디코더입니다.특정 디바이스의 주소가 주소 입력에 표시되었을 경우, 디코더는 그 디바이스의 선택 출력을 아사트 합니다.전용의 단일 출력 주소 디코더를 주소 버스상의 각 디바이스에 짜넣을 수도 있고, 1개의 주소 디코더가 [2]복수의 디바이스에 서비스를 제공할 수도 있다.

n개의 주소 입력 비트를 가진 단일 주소 디코더는 최대n 2개의 디바이스를 지원할 수 있습니다.7400 시리즈 집적회선의 여러 멤버를 주소 디코더로 사용할 수 있습니다.예를 들어, 주소 디코더로서 사용되는 경우, 74154는[3] 4개의 주소 입력과 16개의 디바이스 셀렉터4 출력을 제공한다.주소 디코더는 "디멀티플렉서" 또는 "디멀티플렉서"로 알려진 바이너리 디코더 회로(74154는 일반적으로 "4-16 디멀티플렉서"라고 함)의 특정 용도이며, 주소 디코딩 외에도 많은 용도가 있습니다.

주소 디코더는 버스를 사용하는 시스템의 기본 구성 요소입니다.모든 집적회로 패밀리와 프로세스 및 모든 표준 FPGA 및 ASIC 라이브러리에 표시됩니다.그것들은 디지털 논리 설계 [1]입문 교과서에서 논의된다.

주소 디코더는 메모리의 스토리지 셀을 선택합니다.

주소 디코더는 랜덤 주소 지정 가능한 메모리 디바이스에서 메모리 셀을 선택하기 위해 사용되는 마이크로 일렉트로닉스에서 일반적으로 사용되는 컴포넌트입니다.

이러한 메모리 셀은 고정된 수의 메모리 요소 또는 비트로 구성됩니다.주소 디코더는 주소 버스에 접속되어 거기서 작성된 주소를 읽습니다.특별한 스위칭 로직을 사용하여 이 주소를 사용하여 액세스해야 할 메모리 셀을 계산합니다.그런 다음 특별한 제어선을 통해 셀을 선택하여 셀을 선택합니다.이 행은 선택 행이라고도 합니다.Dynamic Memory(DRAM; 다이내믹 메모리)에서는 메모리 매트릭스 상에 행 및 열 선택 라인이 있으며, 이들은 칩에 내장된 어드레스 디코더에 의해 제어된다.

디코더 유형에 따라 메모리 셀 선택에 사용되는 로직을 특정 상황에서 프로그래밍할 수 있습니다.

주소 디코더는 적절한 메모리 모듈을 선택합니다.

주소 디코더는 프로세서 시스템의 주소 버스에 의해 특정 주소가 제공되는 경우 여러 메모리 모듈 또는 메모리 칩 중 적절한 것을 선택하기 위해서도 사용된다.

이를 위해 메모리 모듈 또는 메모리칩에는 선택 입력이 있으며, 일반적으로 칩 선택 핀(CS) 또는 칩 활성화 핀(CE)이라고 불립니다.이러한 입력에는 종종 음의 로직 함수(CS 또는 CE)가 있습니다. 즉, 인접한 로직 0(전압 레벨 낮음)이 있는 H가 선택됩니다.

주소 디코더는 다른 조합 로직을 사용하여 메모리 모듈 또는 칩을 프로세서의 주소 공간에 배치합니다.메모리 모듈은 주소 공간보다 용량이 작은 경우가 많습니다.대부분의 경우 구조가 완전히 동일하더라도 여러 모듈을 사용할 수 있습니다.주소의 범위가 다른 것을 확인할 필요가 있습니다.

레퍼런스

- ^ a b Paul Horowitz and Winfield Hill (1989). The Art of Electronics (2nd ed.). Cambridge University Press. p. 685,766. ISBN 978-0-521-37095-0.

- ^ S. J. Cahill (1993). Digital and microprocessor engineering (2nd ed.). Ellis Horwood. pp. 489–494. ISBN 978-0-13-213398-2.

- ^ 74HCT154 데이터 시트