멀티코어 프로세서

Multi-core processor멀티코어 프로세서는 프로그램 [1]명령을 읽고 실행하는 코어라고 불리는 두 개 이상의 개별 처리 장치가 있는 단일 집적회로상의 컴퓨터 프로세서입니다.명령어는 일반적인 CPU 명령어(데이터 추가, 이동, 브랜치 등)이지만 단일 프로세서가 동시에 개별 코어로 명령을 실행할 수 있기 때문에 멀티스레딩 또는 기타 병렬 컴퓨팅 [2]기술을 지원하는 프로그램의 전체적인 속도가 향상됩니다.제조업체는 일반적으로 코어를 단일 집적회로 다이(칩 멀티프로세서 또는 CMP) 또는 단일 칩 패키지의 여러 다이에 통합합니다.현재 거의 모든 개인용 컴퓨터에 사용되는 마이크로프로세서는 멀티코어입니다.

멀티코어 프로세서는 단일 물리 패키지로 멀티프로세싱을 구현한다.설계자는 멀티코어 디바이스의 코어를 단단하거나 느슨하게 결합할 수 있습니다.예를 들어 코어는 캐시를 공유하거나 공유하지 않을 수 있으며 메시지 전달 또는 공유 메모리 코어 간 통신 방식을 구현할 수 있습니다.코어 상호 접속에 사용되는 일반적인 네트워크 토폴로지에는 버스, 링, 2차원 메쉬 및 크로스바가 있습니다.동종의 멀티 코어 시스템에는 동일한 코어만 포함되어 있습니다.이종의 멀티 코어 시스템에는 동일하지 않은 코어(크기 등)가 있습니다.같은 명령 세트를 공유하는 이종 코어가 거의 없는 반면 AMD 액셀러레이티드 프로세싱 유닛은 같은 명령 세트를 공유하지 않는 코어가 있습니다).싱글 프로세서 시스템과 마찬가지로 멀티 코어 시스템의 코어는 VLIW, 슈퍼스칼라, 벡터 또는 멀티스레딩 등의 아키텍처를 구현할 수 있습니다.

멀티코어 프로세서는 범용, 임베디드, 네트워크, 디지털 신호 처리(DSP), 그래픽스(GPU) 등 많은 애플리케이션 도메인에서 널리 사용되고 있습니다.코어 수는 최대 수십 개, 전문 칩 수가 10,000 [3]개 이상인 경우, 슈퍼컴퓨터(칩 클러스터 등)에서는 1,000만 개(호스트 [4]프로세서와 더불어 최대 2,000만 개의 처리 요소)를 초과할 수 있습니다.

멀티코어 프로세서의 사용으로 얻을 수 있는 퍼포먼스의 향상은, 사용하는 소프트웨어 알고리즘과 그 실장에 의해서 크게 좌우됩니다.특히 여러 코어에서 병렬로 동시에 실행할 수 있는 소프트웨어의 비율에 따라 이점이 제한됩니다.이 효과는 Amdahl의 법칙에 의해 설명됩니다.최선의 경우, 소위 말하는 병렬 문제는 코어 수에 가까운 속도 향상 계수를 실현하거나, 문제가 각 코어의 캐시 내에 들어갈 정도로 분할되어 훨씬 느린 메인 시스템 메모리를 사용하지 않도록 하는 경우 더 큰 속도를 실현할 수 있습니다.그러나 대부분의 애플리케이션은 프로그래머가 리팩터링에 [5]투자하지 않는 한 그다지 고속화되지 않습니다.

소프트웨어의 병렬화는 중요한 연구 주제입니다.멀티프로세서 애플리케이션의 통합에 의해, 네트워크 아키텍처 설계의 유연성이 향상됩니다.병렬 모델 내 적응성은 이러한 프로토콜을 [6]사용하는 시스템의 추가적인 기능입니다.

용어.

멀티코어 및 듀얼코어라는 용어는 일반적으로 일종의 중앙처리장치(CPU)를 가리킵니다만, 디지털 신호 프로세서(DSP)나 시스템 온 칩(SoC)에도 적용되는 경우가 있습니다.이 용어는 일반적으로 동일한 집적회로 다이에서 제조된 멀티코어 마이크로프로세서를 지칭할 때만 사용됩니다.같은 패키지 내의 개별 마이크로프로세서 다이는 일반적으로 멀티칩 모듈과 같은 다른 이름으로 불립니다.이 문서에서는 특별히 명기되어 있지 않는 한, 같은 집적회로상에서 제조된 CPU에 대해서, 「멀티 코어」와 「듀얼 코어」라고 하는 용어를 사용하고 있습니다.

멀티코어 시스템과 달리 멀티CPU라는 용어는 물리적으로 분리된 복수의 처리 유닛(대부분의 경우 서로간의 통신을 용이하게 하기 위한 특별한 회로를 포함한다)을 의미합니다.

many-core 및 massage-multi-core라는 용어는 특히 많은 수의 코어를 가진 멀티 코어 아키텍처를 나타낼 때 종종 사용됩니다(수천[7] [8]개).

시스템에 따라서는 단일 FPGA에 배치된 다수의 소프트 마이크로프로세서 코어를 사용합니다.각각의 「코어」는, 「반도체 지적 재산 코어」와 CPU [citation needed]코어라고 할 수 있습니다.

발전

제조 기술이 향상되어 개별 게이트의 크기가 줄어드는 반면, 반도체 기반 마이크로 일렉트로닉스의 물리적 한계는 주요 설계 문제가 되었습니다.이러한 물리적인 제한으로 인해 열방산 및 데이터 동기화 문제가 크게 발생할 수 있습니다.CPU의 퍼포먼스를 향상시키기 위해서, 그 외의 다양한 방법이 사용됩니다.슈퍼칼라 파이프라인과 같은 일부 ILP(명령 수준 병렬) 메서드는 많은 응용 프로그램에 적합하지만 예측하기 어려운 코드를 포함하는 다른 방법에는 비효율적입니다.많은 애플리케이션이 스레드 레벨 병렬 처리(TLP) 방식에 더 적합하며, 시스템의 전체 TLP를 증가시키기 위해 여러 개의 독립된 CPU가 일반적으로 사용됩니다.(제조 공정의 정교화에 의해) 사용 가능한 공간의 증가와 TLP의 증가로 인해 멀티 코어 CPU의 개발이 이루어졌습니다.

상업적 인센티브

멀티코어 아키텍처의 개발에는 몇 가지 비즈니스 동기가 있습니다.수십 년 동안 집적회로(IC)의 면적을 줄임으로써 CPU의 성능을 향상시킬 수 있었고, 이로 인해 IC의 장치당 비용이 절감되었습니다.또, 같은 회로 영역에 대해서, 보다 많은 트랜지스터를 설계에 사용할 수 있게 되어, 특히 복잡한 명령 세트 컴퓨팅(CISC) 아키텍처의 기능이 향상되었습니다.클럭 속도도 1980년대 수 메가헤르츠에서 2000년대 초 수 기가헤르츠로 20세기 후반 수십 년 동안 몇 배나 증가했다.

클럭 속도 향상 속도가 느려짐에 따라 전반적인 처리 성능을 개선하기 위해 멀티코어 프로세서 형태의 병렬 컴퓨팅 사용이 증가되었습니다.동일한 CPU 칩에 여러 개의 코어가 사용되었기 때문에 두 개 이상의 코어가 있는 CPU 칩의 판매가 향상될 수 있습니다.예를 들어 인텔은 클라우드 컴퓨팅에 관한 연구를 위해 48코어 프로세서를 개발했습니다.각 코어에는 x86 [9][10]아키텍처가 있습니다.

기술적 요인

컴퓨터 제조업체는 오랫동안 개별 CPU를 사용한 대칭형 멀티프로세서(SMP) 설계를 구현해 왔기 때문에 멀티코어 프로세서 아키텍처의 구현과 소프트웨어 지원에 관한 문제는 잘 알려져 있습니다.

기타:

- 아키텍처 변경 없이 검증된 프로세싱 코어 설계를 사용하면 설계 위험을 크게 줄일 수 있습니다.

- 범용 프로세서의 경우 멀티코어 프로세서의 동기의 대부분은 동작 주파수를 높임으로써 프로세서의 퍼포먼스가 크게 향상되지 않았기 때문입니다.이는 다음 3가지 주요 [11]요인에 의한 것입니다.

- 메모리의 벽. 프로세서와 메모리 속도의 격차 증가.이는 사실상 메모리의 지연을 마스킹하기 위해 캐시 크기를 더 크게 해야 합니다.이는 메모리 대역폭이 성능의 병목 현상이 아닌 범위 내에서만 도움이 됩니다.

- ILP 벽: 고성능 싱글 코어 프로세서를 계속 사용할 수 있는 충분한 병렬 처리를 단일 명령 스트림에서 찾는 것이 점점 더 어려워지고 있습니다.

- 전력 벽: 요인별 작동 빈도 증가에 따라 기하급수적으로 증가하는 전력(따라서 기하급수적으로 증가하는 열 발생)을 소비하는 추세입니다.같은 로직의 트레이스를 작게 하는 것으로, 프로세서를 「수축」하는 것으로, 이러한 증가를 경감할 수 있습니다.파워월에서는 메모리월 및 ILP월로 [citation needed]인해 퍼포먼스가 저하되고 있는 상황에서 제조, 시스템 설계 및 도입에 관한 문제가 발생하고 있습니다.

범용 프로세서의 정기적인 퍼포먼스 향상을 계속하기 위해 인텔이나 AMD 등의 제조업체는 멀티코어 설계를 채택하여 제조 비용을 절감하고 일부 애플리케이션이나 시스템의 퍼포먼스를 향상시키고 있습니다.멀티코어 아키텍처가 개발되고 있지만 대안도 개발되고 있습니다.기존 시장에서 특히 강력한 경쟁자는 칩에 주변기기의 추가 통합입니다.

이점

같은 다이에 복수의 CPU 코어가 근접하기 때문에 신호가 오프칩으로 전송될 때 가능한 것보다 훨씬 높은 클럭 속도로 캐시 일관성 회로를 작동할 수 있습니다.동일한 CPU를 단일 다이로 결합하면 캐시 스눕의 성능이 크게 향상됩니다(대안:버스 스누핑) 조작즉, 서로 다른 CPU 간의 신호가 더 짧은 거리를 이동하기 때문에 신호의 열화가 줄어듭니다.이러한 고품질 신호를 사용하면 개별 신호가 더 짧아질 수 있고 자주 반복할 필요가 없기 때문에 주어진 시간 내에 더 많은 데이터를 전송할 수 있습니다.

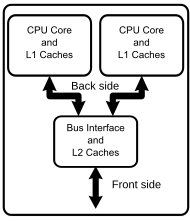

다이를 패키지에 물리적으로 장착할 수 있다고 가정하면 멀티코어 CPU 설계에서는 멀티칩 SMP 설계보다 인쇄회로기판(PCB) 공간이 훨씬 적게 필요합니다.또, 듀얼 코어 프로세서는, 2개의 싱글 코어 프로세서에 비해 소비 전력이 약간 낮습니다.이는 주로 칩 외부의 신호를 구동하는 데 필요한 전력이 감소하기 때문입니다.게다가 코어는, L2 캐시나 프론트 사이드 버스(FSB)에의 인터페이스등의 몇개의 회로를 공유합니다.사용 가능한 실리콘 다이 영역에 대한 경쟁 기술 측면에서 멀티 코어 설계는 입증된 CPU 코어 라이브러리 설계를 활용할 수 있으며 새로운 와이드 코어 설계를 고안하는 것보다 설계 오류 위험이 낮은 제품을 생산할 수 있습니다.또한 캐시를 추가하면 수익률이 감소합니다.

또, 멀티 코어 칩은, 저소비 전력으로 높은 퍼포먼스를 실현합니다.이는 배터리로 작동하는 모바일 기기에서 큰 요인이 될 수 있습니다.일반적으로 멀티코어 CPU의 각 코어는 에너지 효율이 높기 때문에 하나의 큰 모노리식 코어를 사용하는 것보다 칩의 효율이 높아집니다.이것에 의해, 적은 전력으로 높은 퍼포먼스를 실현할 수 있습니다.단, 병렬 [12]코드 작성에 따른 추가 오버헤드가 과제입니다.

단점들

멀티코어 프로세서가 제공하는 컴퓨팅 자원을 최대한 활용하려면 운영체제(OS) 지원과 기존 애플리케이션 소프트웨어를 모두 조정해야 합니다.또, 멀티 코어 프로세서의 애플리케이션 퍼포먼스 향상은, 애플리케이션내에서 복수의 스레드를 사용하는 것에 의해서 다릅니다.

멀티코어 칩을 통합하면 칩 생산 수율을 낮출 수 있습니다.또한 저밀도 싱글 코어 설계보다 열 관리가 더 어렵습니다.인텔은 1개의 다이에 2개의 듀얼 코어 다이를 통합 캐시에 조합하는 것으로, 이 최초의 문제에 부분적으로 대응하고 있습니다.따라서 1개의 다이에 4개의 코어를 제작하고 4개의 코어를 모두 쿼드 코어 CPU를 제작하는 것이 아니라, 2개의 동작하는 듀얼 코어 다이를 사용할 수 있습니다.아키텍처 관점에서 보면,궁극적으로 단일 CPU 설계는 멀티프로세싱 코어보다 실리콘 표면적을 더 잘 사용할 수 있기 때문에 이 아키텍처에 대한 개발 약속은 노후화의 위험을 수반할 수 있습니다.마지막으로 시스템 퍼포먼스에 제약이 되는 것은 물리 처리 능력뿐만이 아닙니다.2개의 프로세싱 코어가 동일한 시스템 버스와 메모리 대역폭을 공유하기 때문에 실제 성능의 이점이 제한됩니다.2009년 보고서에서 Jun Ni 박사는 단일 코어가 메모리 대역폭에 거의 제한적일 경우 듀얼 코어로 전환하면 30%에서 70%의 성능이 향상될 수 있음을 보여주었습니다.메모리 대역폭에 문제가 없다면 90%의 성능 향상을 기대할 수 있습니다.그러나 Amdahl의 법칙에 따르면 이 주장은 [13]의심스럽다고 합니다.2개의 CPU를 사용한 애플리케이션이 싱글코어 1개의 CPU로 고속으로 동작하는 것은 CPU간의 통신이 제한 요인이 되어 100% 이상 개선되는 것으로 간주될 수 있습니다.

하드웨어

트렌드

프로세서 개발의 경향은 이론적으로 수백 또는 수천 개의 코어를 가진 프로세서가 [14]가능해짐에 따라 코어 수가 계속 증가하고 있습니다.또한 멀티스레딩, 메모리 온 칩 및 특수 목적의 "이질적"(또는 비대칭) 코어와 혼합된 멀티코어 칩은 특히 멀티미디어, 인식 및 네트워킹 애플리케이션의 처리에서 성능과 효율성을 더욱 향상시킵니다.예를 들면 큰 거.LITTLE 코어에는 고성능 코어('빅'이라고 함)와 저전력 코어('LITTLE'이라고 함)가 포함됩니다.또한 고급 미세 또는 초미세 전력 관리 및 동적 전압 및 주파수 스케일링(노트북 컴퓨터 및 휴대용 미디어 플레이어 등)을 통해 와트당 성능을 중시하여 에너지 효율을 향상하는 경향도 있습니다.

처음부터 (단일 코어 설계에서 발전한 것이 아니라) 다수의 코어를 위해 설계된 칩을 종종 manycore 설계라고 부르며 질적 차이를 강조합니다.

아키텍처

멀티코어 아키텍처에서 코어의 구성과 균형은 매우 다양합니다.일부 아키텍처는 하나의 코어 설계를 일관되게 반복("동종")하는 반면, 다른 아키텍처는 각기 다른 "이질적" 역할에 최적화된 서로 다른 코어의 혼합을 사용합니다.

여러 코어를 구현하고 통합하는 방법은 개발자의 프로그래밍 기술과 앱 및 장치에 대한 소비자의 기대치에 [15]큰 영향을 미칩니다.옥타코어로 애드버타이즈되는 디바이스는 각각 고정 클럭 [16][17]속도를 가진2 세트의 쿼드코어가 아닌 True Octa-core 또는 이와 유사한 스타일로 애드버타이즈되는 경우 독립된 코어만 갖게 됩니다.

Rick Merritt, EE Times 2008의 "[18]CPU 설계자가 멀티코어의 미래에 대해 논의합니다" 기사에는 다음과 같은 코멘트가 포함되어 있습니다.

Chuck Moore [...]는 컴퓨터는 휴대폰과 같아야 한다고 제안했습니다.다양한 특수 코어를 사용하여 고급 애플리케이션 프로그래밍 인터페이스에 의해 스케줄된 모듈러 소프트웨어를 실행할 수 있습니다.

[...] 르네사스의 시니어 수석 엔지니어 하세가와 아츠시(Hasegushi Hasegawa 。그는 휴대폰이 많은 특수 코어를 함께 사용하는 것이 미래의 멀티 코어 디자인에 좋은 모델이라고 제안했다.

[...] 스타트업 Tilera의 설립자이자 CEO인 Anant Agarwal은 반대 의견을 내놓았다.그는 소프트웨어 모델을 단순하게 유지하려면 멀티코어 칩이 범용 코어의 동종 집합이어야 한다고 말했다.

소프트웨어 효과

오래된 버전의 안티바이러스 응용 프로그램은 스캔 프로세스를 위한 새 스레드를 만들 수 있으며, GUI 스레드는 사용자로부터의 명령을 기다립니다(스캔 취소 등).이러한 경우 멀티코어 아키텍처는 애플리케이션 자체에 거의 도움이 되지 않습니다.단일 스레드가 모든 부하를 주고 여러 코어에 걸쳐 균등하게 작업을 분산시킬 수 없기 때문입니다.진정한 멀티스레드 코드를 프로그래밍하려면 종종 스레드의 복잡한 조정이 필요하며 스레드 간에 공유되는 데이터에 대한 처리를 상호 연결하기 때문에 미묘하고 찾기 어려운 버그가 쉽게 발생할 수 있습니다('스레드 안전성' 참조).따라서 이러한 코드는 단일 스레드 코드보다 디버깅이 훨씬 어렵습니다.컴퓨터 하드웨어의 최대 사용에 대한 소비자 수준의 수요는 상대적으로 드물기 때문에 소비자 수준의 스레드 애플리케이션을 작성하려는 동기가 부족하다는 인식이 있습니다.또, 비디오 코덱에 사용되는 엔트로피 부호화 알고리즘의 복호화 등의 시리얼 태스크는, 생성되는 각 결과가 엔트로피 복호화 알고리즘의 다음 결과 작성에 도움이 되기 때문에, 병렬화가 불가능하다.

프로세서 클럭 속도의 대폭적인 증가로 인해 발생하는 심각한 열 및 전력 소비 문제에서 기인하는 멀티 코어 칩 설계에 대한 강조가 증가하고 있는 것을 고려하면, 이러한 새로운 칩을 이용하기 위해 소프트웨어를 멀티 스레드화할 수 있는 정도가 컴퓨터 성능의 가장 큰 제약이 될 수 있습니다.미래개발자가 여러 코어에 의해 제공되는 자원을 최대한 활용할 수 있는 소프트웨어를 설계할 수 없다면 궁극적으로는 퍼포먼스의 한계에 도달하게 됩니다.

통신 시장은 데이터 경로와 제어 플레인에 이러한 멀티 코어 프로세서가 매우 빠르게 채택되었기 때문에 병렬 데이터 경로 패킷 처리의 새로운 설계를 필요로 하는 최초의 시장 중 하나였습니다.이러한 MPU는, 독자적인 마이크로 코드나 피코 코드에 근거하고 있던 종래의 네트워크 프로세서를 대체하는 것입니다[19].

병렬 프로그래밍 기술은 여러 코어의 이점을 직접 얻을 수 있습니다.Cilk Plus, OpenMP, OpenHMPP, FastFlow, Skandium, MPI 및 Erlang 등의 기존 병렬 프로그래밍 모델을 멀티코어 플랫폼에서 사용할 수 있습니다.인텔은 TBB라고 불리는 C++ 병렬 처리를 위한 새로운 추상화를 도입했습니다.그 외 Codeplay Sieve System, Cray's Chapel, Sun's Portress, IBM의 X10 등의 연구 활동도 있습니다.

멀티코어 프로세싱은 현대의 컴퓨터 소프트웨어 개발 능력에도 영향을 미치고 있습니다.새로운 언어로 프로그래밍하는 개발자는 최신 언어가 멀티코어 기능을 지원하지 않는 것을 알 수 있습니다.이를 위해서는 수치 라이브러리를 사용하여 C나 Fortran과 같은 언어로 작성된 코드에 액세스해야 합니다.이 코드는 C#과 같은 새로운 언어보다 연산 속도가 빠릅니다.인텔의 MKL 및 AMD의 ACML은 이러한 네이티브 언어로 기술되어 멀티코어 프로세싱의 장점을 갖추고 있습니다.프로세서 간에 애플리케이션 워크로드의 균형을 맞추는 것은 특히 성능 특성이 다른 경우 문제가 될 수 있습니다.예를 들어, 조정 언어 및 프로그램 구성 요소(프로그래밍 라이브러리 또는 고차 함수)를 사용하는 등 문제를 다루는 다양한 개념 모델이 있습니다.각 블록은 프로세서 유형별로 다른 네이티브 구현을 가질 수 있습니다.사용자는 이러한 추상화를 사용하여 프로그래밍하기만 하면 인텔리전트 컴파일러는 컨텍스트에 [20]따라 최적의 구현을 선택할 수 있습니다.

동시성 관리는 병렬 애플리케이션 개발에서 중심적인 역할을 수행합니다.병렬 애플리케이션 설계의 기본 단계는 다음과 같습니다.

- 파티셔닝

- 설계의 분할 단계는 병렬 실행 기회를 노출하기 위한 것입니다.따라서, 문제의 세분화된 분해라고 불리는 것을 산출하기 위해 많은 작은 작업을 정의하는 데 초점을 맞추고 있다.

- 의사소통

- 파티션에 의해 생성된 태스크는 동시에 실행되도록 되어 있지만 일반적으로 독립적으로 실행할 수는 없습니다.한 작업에서 수행되는 계산에는 일반적으로 다른 작업과 관련된 데이터가 필요합니다.그런 다음 연산을 계속할 수 있도록 작업 간에 데이터를 전송해야 합니다.이 정보 흐름은 설계의 통신 단계에서 지정됩니다.

- 응집

- 제3단계에서는 추상적인 것에서 구체적인 것으로 발전한다.개발자는 병렬 컴퓨터의 일부 클래스에서 효율적으로 실행되는 알고리즘을 얻기 위해 분할 및 통신 단계에서 내린 결정을 다시 검토합니다.특히, 개발자들은 분할 단계에서 식별된 작업을 결합하거나 집적하는 것이 유용한지 검토하여 각각 더 큰 규모의 작업을 더 적은 수로 제공한다.또한 데이터와 계산을 복제할 가치가 있는지 여부도 결정합니다.

- 매핑

- 병렬 알고리즘 설계의 네 번째 및 마지막 단계에서 개발자는 각 태스크를 실행할 위치를 지정합니다.이 매핑 문제는 유니프로세서 또는 자동 태스크 예약을 제공하는 공유 메모리 컴퓨터에서는 발생하지 않습니다.

한편, 서버측에서는, 멀티 코어 프로세서가 이상적입니다.멀티 코어 프로세서는, 다수의 유저가 동시에 사이트에 접속해, 독립된 실행 스레드를 가질 수 있기 때문입니다.이것에 의해, throughput이 큰 Web 서버 및 애플리케이션서버가 가능하게 됩니다.

라이선스

벤더는, 「프로세서 마다」소프트웨어의 라이센스를 취득할 수 있습니다.이는 "프로세서"가 단일 코어로 구성되거나 코어의 조합으로 구성될 수 있기 때문에 모호함을 야기할 수 있습니다.

- 처음에 마이크로소프트는 일부 엔터프라이즈 소프트웨어에 대해 소켓 단위의 라이센스 시스템을 계속 사용했습니다.그러나 BizTalk Server 2013, SQL Server 2014 및 Windows Server 2016과 같은 일부 소프트웨어의 경우 Microsoft는 코어별 [21]라이센싱으로 전환했습니다.

- Oracle Corporation은 AMD X2 또는 Intel 듀얼 코어 CPU를 단일[citation needed] 프로세서로 간주하지만 다른 유형(특히 3개 이상의 [22]코어가 있는 프로세서)에는 다른 메트릭을 사용합니다.

임베디드 어플리케이션

임베디드 컴퓨팅은 "미드레인지" PC와는 다른 프로세서 테크놀로지 영역에서 작동합니다.멀티코어를 지향하는 동일한 기술 드라이브가 여기에 적용됩니다.실제로 태스크가 다른 프로세서 간에 쉽게 분할될 수 있다면 대부분의 경우 이 애플리케이션은 멀티코어 테크놀로지에 적합한 "자연스러운" 애플리케이션입니다.

또한 임베디드 소프트웨어는 일반적으로 특정 하드웨어 릴리스용으로 개발되기 때문에 소프트웨어의 이식성, 레거시 코드 또는 독립 개발자를 지원하는 문제는 PC 또는 엔터프라이즈 컴퓨팅에 비해 덜 중요합니다.그 결과, 개발자는 새로운 테크놀로지를 채용하기 쉬워지고, 그 결과 멀티 코어 프로세싱 아키텍처와 써플라이어의 종류가 다양해집니다.

네트워크 프로세서

2010년 현재[update] 멀티코어 네트워크 프로세서가 주류가 되어 있으며, Freescale Semiconductor, Cavium Networks, Wintegra, Broadcom 등의 기업은 모두 8개의 프로세서를 탑재한 제품을 제조하고 있습니다.시스템 개발자에게는 Symmetric Multiprocessing(SMP; 대칭형 멀티프로세서) 운영체제 고유의 퍼포먼스 제한에도 불구하고 이들 디바이스의 모든 코어를 활용하여 시스템레벨에서 최대의 네트워크 퍼포먼스를 실현하는 방법이 중요한 과제입니다.6WIND 등의 기업은 네트워크 데이터 플레인이 네트워크 [23]디바이스의 운영체제 이외의 고속 경로 환경에서 실행되도록 설계된 휴대용 패킷 처리 소프트웨어를 제공합니다.

디지털 신호 처리

디지털 신호 처리에서 같은 트렌드는 적용된다.텍사스 인스트루먼트는three-core TMS320C6488과 4TMS320C5441, Freescale은 4MSC8144과six-core MSC8156(이고 둘 다 그들이eight-core 후계자들 중에 일하고 있다고 말했습니다) 가지고 있다.두개의 항목천 Processors, 40세에서 80일반 목적 ALUs 칩, 모든 C에 죽다에 대한 단일 명령 다중 데이터 엔진과 Picochip 300프로세서 등을 통신 애플리케이션에 초점을 맞춘 대로 프로그램 가능과 Storm-1 가족들을 포함합니다.

이종 시스템

이종 컴퓨팅에, 시스템 처리기 또는 선심의 멀티 코어 솔루션은 공통적이게 되어집니다 하나 이상,:자일링스 Zynq UltraScale+ MPSoC quad-core ARMCortex-A53고 게다가 듀얼 코어 ARMCortex-R5다를 사용한다.OpenAMP 같은 소프트웨어 솔루션inter-processor 통신을 돕는 데 사용되고 있다.

모바일 장치는 ARM 큰 사용할 수 있다.LITTLE 건축물이다.

하드웨어 예시

이 기사는 과도한,이거나 관련 무차별적인 예 포함할 수 있다.부디 덜 적절한 예들을 제거하는 설명적인 텍스트를 더해 기사가 개선된다.추가 제안을 위한 더 좋은 기사 쓰는 것에 참조하라 위키 피디아의 가이드입니다.(7월 2016년) |

상업의

- Adapteva 에피 포니(Epiphany)를 4096에 on-chip할 수 있는 many-core 프로세서 아키텍처, 가난뱅이에 불과하긴 했지만16-core 버전 상업적으로 생산되 왔습니다.

- Aeroflex Gaisler LEON3, 멀티 코어 스팍는 고장 허용형 버전에 존재한다.

- Ageia PhysX, 멀티 코어 물리학 처리 단위이다.

- Ambric Am2045,336-core Massively 병렬 프로세서 배열(MPPA).

- AMD

- A 시리즈, 듀얼, 트리플 및 쿼드 코어의 가속 프로세서 유닛(APU)

- Athlon 64 FX 및 Athlon 64 X2 싱글 코어 및 듀얼 코어 데스크톱 프로세서.

- Athlon II, 듀얼 코어, 트리플 코어 및 쿼드 코어 데스크톱 프로세서.

- FX 시리즈, 쿼드 코어, 6 코어 및 8 코어 데스크톱 프로세서.

- Opteron, 싱글, 듀얼, 쿼드, 6 코어, 8 코어, 12 코어 및 16 코어 서버/워크스테이션 프로세서.

- 페넘, 듀얼, 트리플, 쿼드코어 프로세서

- Phenom II, 듀얼, 트리플, 쿼드 및 6코어 데스크톱 프로세서

- 셈프론, 주로 단선 또는 2선인, dual-, quad-core 엔트리 레벨 프로세서입니다.[24]

- 튜리온, 주로 단선 또는 2선인, 게다가 듀얼 코어 노트북 프로세서입니다.

- Ryzen,dual-, quad-, 6-, 8-, 12,16,24, 32-,64-core 데스크 톱, 모바일, 및 플랫폼에 프로세서가 넘었다.

- Epyc, quad-, 8-, 12,16,24, 32-,64-core 서버와 내장 프로세서입니다.

- 라데온과 FireStream multi-core GPU/GPGPU(핵심당 10코어, 165-issue 넓은 슈퍼 스칼라 스트림 프로세서).

- 아날로그 디바이스 블랙핀 BF561, 대칭적인 듀얼 코어 프로세서.

- ARM11 MPCore과 ARMCortex-A9 MPCore 프로세서 cores, 고성능 embedded과 오락 애플리케이션을 위한 ARMMPCore은 완전한synthesizable 멀티 코어 컨테이너입니다.

- ASOCS ModemX 128코어에, 무선 응용 프로그램이다.

- 아줄 시스템

- 베가 1,24-core 프로세서, 2005년 개봉된다.

- 베가 248-core 프로세서, 2006년에 발표된 한.

- 베가 3,54-core 프로세서, 2008년에 개봉된다.

- 브로드 컴 SiByte SB1250, SB1255, SB1455, BCM 2836 quad-core ARMSoC(는 라즈베리 파이 2를 위해 설계된).

- Cadence 설계 시스템 Tensilica Xtensa LX6, Espressif 시스템스의 ESP32에 게다가 듀얼 코어 구성에 이용할 수 있다.

- ClearSpeed

- CSX700, 192-core 프로세서, 2008년(32/64-bit 부동 소수 점;정수 ALU)에 발표했다.

- Cradle Technologies CT3400 및 CT3600, 둘 다 멀티코어 DSP.

- 32코어 MIPS MPU인 Cavium Networks Octeon.

- 100코어 DSP/GPP 프로세서인 Logix hx3100 프로세서

- 프리스케일 반도체 큐어IQ 시리즈 프로세서, 최대 8코어, Power ISA MPU.

- Hewlett-Packard PA-8800 및 PA-8900, 듀얼코어 PA-RISC 프로세서

- IBM

- POWER4는 2001년에 출시된 듀얼코어 PowerPC 프로세서입니다.

- POWER5는 듀얼코어 PowerPC 프로세서이며 2004년에 출시되었습니다.

- POWER6는 2007년에 출시된 듀얼코어 PowerPC 프로세서입니다.

- POWER7은 4, 6, 8코어의 PowerPC 프로세서이며 2010년에 출시되었습니다.

- 12코어 PowerPC 프로세서 POWER8은 2013년에 출시되었습니다.

- POWER9은 12코어 또는 24코어의 PowerPC 프로세서이며 2017년에 출시되었습니다.

- Power10은 15코어 또는 30코어의 PowerPC 프로세서이며 2021년에 출시되었습니다.

- Apple Power Mac G5에서 사용되는 듀얼 코어 PowerPC 프로세서인 PowerPC 970MP.

- 제논, 트리플 코어, SMT 지원, 전원Microsoft Xbox 360 게임 콘솔에 사용되는 PC 마이크로프로세서.

- z10은 쿼드코어 z/아키텍처 프로세서이며 2008년에 출시되었습니다.

- z196은 쿼드코어 z/아키텍처 프로세서이며 2010년에 출시되었습니다.

- zEC12는 2012년에 출시된 6코어 z/Architecture 프로세서입니다.

- z13은 8코어 z/Architecture 프로세서로서 2015년에 출시되었습니다.

- z14는 10코어 z/Architecture 프로세서로서 2017년에 출시되었습니다.

- z15는 12코어 z/Architecture 프로세서로서 2019년에 출시되었습니다.

- 8코어 z/아키텍처 프로세서인 Telum은 2021년에 출시되었습니다.

- 인피니온

- 인텔(R)

- 넷북, 넷톱, 임베디드 애플리케이션, 모바일 인터넷 디바이스(MID)[25]용 ATOM, 싱글, 듀얼 코어, 쿼드 코어, 8 코어, 12 코어, 16 코어 프로세서.

- ATOM SoC(칩 기반 시스템), 싱글 코어, 듀얼 코어 및 쿼드 코어 프로세서(스마트폰 및 [26]태블릿용).

- Celeron은 예산/[27][28]엔트리 레벨 시장용 최초의 듀얼 코어(나중에 쿼드 코어) 프로세서입니다.

- 듀얼 코어 [29]프로세서인 Core Duo.

- 듀얼 코어 [30]프로세서인 Core 2 Duo.

- Core 2 Quad, 2개의 듀얼 코어 다이(멀티 칩 [31]모듈 패키지)

- Core i3, Core i5, Core i7 및 Core i9은 듀얼, 쿼드, 6 코어, 8 코어, 10 코어, 12 코어, 14 코어, 16 코어, 및 18 코어 프로세서의 패밀리이며, Core 2 Duo 및 Core [32]2 Quad의 후계 프로세서입니다.

- Itanium, 싱글, 듀얼코어, 쿼드코어 및 8코어 프로세서.[33]

- 엔트리 레벨 시장에 [34]최적인 Pentium, 싱글, 듀얼 코어, 쿼드 코어 프로세서.

- Teraflops Research Chip(Polaris)은 3.16GHz, 80코어 프로세서 프로토타입으로,[35] 2011년까지 출시될 것이라고 당초 밝혔다.

- Xeon 듀얼, 쿼드, 6 코어, 8 코어, 10 코어, 12 코어, 14 코어, 15 코어, 16 코어, 18 코어, 20 코어, 22 코어, 24 코어, 26 코어, 28 코어,[36][37][38][39][40][41] 32 코어, 48 코어 및 56 코어 프로세서.

- Xeon Phi 57 코어, 60 코어, 61 코어, 64 코어, 68 코어 및 72 코어 프로세서.[42][43]

- 인텔라시스

- 칼레이

- MPPA-256, 256 코어 프로세서, 2012년 출시 (256 사용 가능한 VLIW 코어, Network-on-Chip(NoC; 네트워크 온 칩), 32/64 비트 IEEE 754 준거 FPU)

- NetLogic 마이크로시스템즈

- XLP, 32코어 쿼드 스레드 MIPS64 프로세서.

- XLR, 8코어 쿼드 스레드 MIPS64 프로세서.

- XLS, 8코어 쿼드 스레드 MIPS64 프로세서.

- 엔비디아

- 8코어 마이크로컨트롤러인 Parallax Proplemer P8X32.

- DSP 및 무선용 피코칩 PC200 시리즈 (디바이스당 200~300 코어)

- 복수의 HAL 시리즈가 긴밀하게 결합된 16~256 코어, L1 공유 메모리, 하드웨어 동기 프로세서.

- 파워를 탑재한 257코어 마이크로컨트롤러인 Relocore KC256PC 코어 및 256개의 8비트 "처리 요소"

- SiCortex "SiCortex 노드"는 단일 칩에 6개의 MIPS64 코어가 있습니다.

- SiFive

- U74에는 4개의 코어가 탑재되어 있습니다.

- Sony/IBM/Toshiba's Cell 프로세서, 1개의 범용 프로세서를 탑재한9 코어 프로세서Sony PlayStation 3에서 사용되는 벡터 연산에 최적화된 PC 코어 및 8개의 특수 SPU(Synergistic Processing Unit)

- Sun Microsystems

- 선웨이

- Sunway SW26010은 Sunway TaihuLight에 사용되는 260코어 프로세서입니다.

- 텍사스 인스트루먼트

- 틸레라

- XMOS 소프트웨어 정의 실리콘 쿼드코어 XS1-G4.

공짜

학업의

- MIT, 16코어 RAW 프로세서

- 캘리포니아 대학교 데이비스, 단순 프로세서의 비동기 배열(AsAP)

- 워싱턴 대학교, Wavescalar 프로세서

- 텍사스 대학교 오스틴, TRIPs 프로세서

- Linköping University, 스웨덴, ePUMA 프로세서

- UC Davis, Kilocore, 32nm IBM 프로세스[45] 상의 1000코어 1.78GHz 프로세서

벤치마크

멀티코어 프로세서의 연구와 개발은 많은 옵션을 비교하며, 벤치마크는 그러한 평가에 도움이 되도록 개발됩니다.기존 벤치마크에는 이기종 [46]시스템용 SPLASH-2, PARSEC 및 COSMIC이 포함됩니다.

「 」를 참조해 주세요.

- CPU 실드

- 쿠다

- GPGPU

- 하이퍼스레딩

- 멀티코어

- 멀티코어 어소시에이션

- 멀티태스킹

- OpenCL(Open Computing Language)– 이종 혼재형 실행 프레임워크

- 병렬 랜덤 액세스 머신

- Partitioned Global Address Space(PGAS; 분할 글로벌주소 공간)

- 레이스 조건

- 실

메모들

- ^디지털 신호 프로세서(DSP)는 하이엔드 범용 프로세서보다 훨씬 오랫동안 멀티 코어 아키텍처를 사용해 왔습니다.DSP 고유의 구현의 일반적인 예로는 RISC CPU와 DSP MPU의 조합을 들 수 있습니다.이를 통해 사용자 인터페이스용 범용 프로세서와 실시간 데이터 처리용 DSP를 필요로 하는 제품을 설계할 수 있습니다.이러한 유형의 설계는 휴대전화에서 흔히 볼 수 있습니다.그 외의 애플리케이션에서는, 매우 많은 수의 프로세서를 탑재한 멀티 코어 DSP를 개발하고 있는 기업이 증가하고 있습니다.

- ^ 듀얼 CPU 멀티프로세서를 사용할 수 있는 운영체제시스템은 분할 멀티프로세서와 대칭 멀티프로세서(SMP)의 2종류입니다.파티션화된 아키텍처에서는 각 CPU는 물리 메모리의 개별 세그먼트로 기동해 독립적으로 동작합니다.SMP OS에서는 프로세서가 공유 공간에서 동작하며 OS 내에서 스레드를 독립적으로 실행합니다.

레퍼런스

- ^ Rouse, Margaret (March 27, 2007). "Definition: multi-core processor". TechTarget. Archived from the original on August 5, 2010. Retrieved March 6, 2013.

- ^ Schauer, Bryan. "Multicore Processors – A Necessity" (PDF). Archived from the original (PDF) on 2011-11-25.

- ^ a b Smith, Ryan. "NVIDIA Announces the GeForce RTX 30 Series: Ampere For Gaming, Starting With RTX 3080 & RTX 3090". www.anandtech.com. Retrieved 2020-09-15.

- ^ "Sunway TaihuLight - Sunway MPP, Sunway SW26010 260C 1.45GHz, Sunway TOP500". www.top500.org. Retrieved 2020-09-15.

- ^ Suleman, Aater (May 20, 2011). "What makes parallel programming hard?". FutureChips. Archived from the original on May 29, 2011. Retrieved March 6, 2013.

- ^ Duran, A (2011). "Ompss: a proposal for programming heterogeneous multi-core architectures". Parallel Processing Letters. 21 (2): 173–193. doi:10.1142/S0129626411000151.

- ^ Schor, David (November 2017). "The 2,048-core PEZY-SC2 sets a Green500 record". WikiChip.

- ^ Vajda, András (2011-06-10). Programming Many-Core Chips. Springer. p. 3. ISBN 978-1-4419-9739-5.

- ^ Shrout, Ryan (December 2, 2009). "Intel Shows 48-core x86 Processor as Single-chip Cloud Computer". Archived from the original on January 5, 2016. Retrieved May 17, 2015.

- ^ "Intel unveils 48-core cloud computing silicon chip". BBC. December 3, 2009. Archived from the original on December 6, 2012. Retrieved March 6, 2013.

- ^ 패터슨, 데이비드 A. "컴퓨터 아키텍처의 미래"버클리 EECS 연례 연구 심포지엄(Bears), UC 버클리 공대, 2006년.

- ^ Suleman, Aater (May 19, 2011). "Q & A: Do multicores save energy? Not really". Archived from the original on December 16, 2012. Retrieved March 6, 2013.

- ^ Ni, Jun. "Enabling Technology of Multi-core Computing for Medical Imaging" (PDF). Archived from the original (PDF) on 2010-07-05. Retrieved 17 February 2013.

- ^ Clark, Jack. "Intel: Why a 1,000-core chip is feasible". ZDNet. Archived from the original on 6 August 2015. Retrieved 6 August 2015.

- ^ Kudikala, Chakri (Aug 27, 2016). "These 5 Myths About the Octa-Core Phones Are Actually True". Giz Bot.

- ^ "MediaTeck Launches MT6592 True Octa-core Mobile Platform". MediaTek. Nov 20, 2013.

- ^ "What is an Octa-core processor". Samsung.

Galaxy smartphones run on either Octa-core (2.3GHz Quad + 1.6GHz Quad) or Quad-core (2.15GHz + 1.6GHz Dual) processors

- ^ Merritt, Rick (February 6, 2008). "CPU designers debate multi-core future". EE Times. Archived from the original on November 14, 2012. Retrieved March 6, 2013.

- ^ "Multicore Packet Processing Forum". Archived from the original on 2009-12-21.

- ^ John Darlinton; Moustafa Ghanem; Yike Guo; Hing Wing To (1996). "Guided Resource Organisation in Heterogeneous Parallel Computing". Journal of High Performance Computing. 4 (1): 13–23. CiteSeerX 10.1.1.37.4309.

- ^ Bright, Peter (4 December 2015). "Windows Server 2016 moving to per core, not per socket, licensing". Ars Technica. Condé Nast. Archived from the original on 4 December 2015. Retrieved 5 December 2015.

- ^ 비교:

- ^ "6WINDGATE Software: Network Optimization Software – SDN Software – Control Plane Software 6WIND".

- ^ "Sempron™ 3850 APU with Radeon™ R3 Series AMD". AMD. Archived from the original on 4 May 2019. Retrieved 5 May 2019.

- ^ "Intel® Atom™ Processor C Series Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ "Intel® Atom™ Processor Z Series Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ "Intel Preps Dual-Core Celeron Processors". 11 October 2007. Archived from the original on 4 November 2007. Retrieved 12 November 2007.

- ^ "Intel® Celeron® Processor J Series Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ "Products formerly Yonah". ark.intel.com. Retrieved 2019-05-04.

- ^ "Products formerly Conroe". ark.intel.com. Retrieved 2019-05-04.

- ^ "Products formerly Kentsfield". ark.intel.com. Retrieved 2019-05-04.

- ^ "Intel® Core™ X-series Processors Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ "Intel® Itanium® Processor Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ "Intel® Pentium® Processor D Series Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ Zazaian, Mike (September 26, 2006). "Intel: 80 Cores by 2011". Archived from the original on 2006-11-09. Retrieved 2006-09-28.

- ^ Kowaliski, Cyril (February 18, 2014). "Intel releases 15-core Xeon E7 v2 processor". Archived from the original on 2014-10-11.

- ^ "Intel Xeon Processor E7 v3 Family". Intel. Archived from the original on 2015-07-07.

- ^ "Intel Xeon Processor E7 v2 Family". Intel. Archived from the original on 2015-07-07.

- ^ "Intel Xeon Processor E3 v2 Family". Intel. Archived from the original on 2015-07-07.

- ^ "Intel shows off Xeon Platinum CPU with up to 56 cores and 112 threads". TechSpot. Retrieved 2019-05-04.

- ^ PDF, Download. "2nd Gen Intel® Xeon® Scalable Processors Brief". Intel. Retrieved 2019-05-04.

- ^ "Intel® Xeon Phi™ x100 Product Family Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ "Intel® Xeon Phi™ 72x5 Processor Family Product Specifications". ark.intel.com. Retrieved 2019-05-04.

- ^ Cole, Bernard (September 24, 2008). "40-core processor with Forth-based IDE tools unveiled".

- ^ Chacos, Brad (June 20, 2016). "Meet KiloCore, a 1,000-core processor so efficient it could run on a AA battery". PC World. Archived from the original on June 23, 2016.

- ^ "COSMIC Heterogeneous Multiprocessor Benchmark Suite". Archived from the original on 2015-07-03.

추가 정보

- Khondker S. Hasan, Nicolas G. Grounds, John K. Antonio (July 2011). Predicting CPU Availability of a Multi-core Processor Executing Concurrent Java Threads. 17th International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA-11). Las Vegas, Nevada, USA. pp. 551–557.

{{cite conference}}: CS1 maint: 작성자 파라미터 사용(링크) - Khondker S. Hasan, John Antonio, Sridhar Radhakrishnan (February 2014). A New Composite CPU/Memory Model for Predicting Efficiency of Multi-core Processing. The 20th IEEE International Conference on High Performance Computer Architecture (HPCA-14) workshop. Orlando, FL, USA. doi:10.13140/RG.2.1.3051.9207.

{{cite conference}}: CS1 maint: 작성자 파라미터 사용(링크)

외부 링크

- "프로세서 코어란?": Make Use Of

- "임베디드 멀티코어로의 이행"—임베디드 컴퓨팅 설계

- 멀티코어는 슈퍼컴퓨터에 나쁜 소식입니다.IEEE 스펙트럼

- 2010년 2월 19일에 발표된 Manycore 미래를 위한 솔루션 설계(슬라이드에 기재된 여러 개의 데드링크)