칩상의 네트워크

Network on a chip| 시리즈의 일부 | ||||

| 네트워크 과학 | ||||

|---|---|---|---|---|

| 네트워크 타입 | ||||

| 그래프 | ||||

| ||||

| 모델 | ||||

| ||||

| ||||

칩 또는 네트워크 온 칩(NoC / ɛ noʊ oː si/ / en - oh - SEE 또는 / nnk / 노크)[nb 1]은 집적회로상의 네트워크 기반 통신 서브시스템입니다.대부분은 칩상의 시스템(SoC) 내의 모듈 간입니다.IC 상의 모듈은 일반적으로 컴퓨터 시스템의 다양한 기능을 도식화한 반도체 IP 코어로 네트워크 과학이라는 의미에서 모듈화되도록 설계되어 있습니다.Network on Chip은 SoC 모듈 간의 라우터 기반 패킷스위칭 네트워크입니다

NoC 테크놀로지는 컴퓨터 네트워킹의 이론과 방법을 온칩 통신에 적용하여 기존의 버스 및 크로스바 통신 아키텍처에 비해 현저한 향상을 가져옵니다.Networks-on-chip은 많은 네트워크 토폴로지로 구성되어 있으며,[citation needed] 2018년 현재 많은 토폴로지가 아직 실험 단계에 있습니다.

NoC는 다른 통신 서브시스템 설계에 비해 시스템 온칩의 확장성과 복잡한 SoC의 전력 효율을 향상시킵니다.현대의 퍼스널컴퓨터에서 일반적으로 사용되는 NoC는 그래픽 처리 유닛(GPU)입니다.GPU는 컴퓨터 그래픽스, 비디오 게임 및 고속 인공지능에 일반적으로 사용됩니다.이러한 테크놀로지는 새로운 테크놀로지이며, 멀티코어 컴퓨터 아키텍처가 보편화됨에 따라 가까운 장래에 큰 성장이 전망되고 있습니다.

구조.

NoC는 클럭도메인 크로스라고 불리는 동기 및 비동기 클럭도메인에 걸치거나 잠기지 않은 비동기 로직을 사용할 수 있습니다.NoC는 글로벌하게 비동기 로컬로 동기화된 전자기기 아키텍처를 지원하므로 시스템 온 칩 상의 각 프로세서 코어 또는 기능 유닛에 독자적인 클럭 [1]도메인을 설정할 수 있습니다.

아키텍처

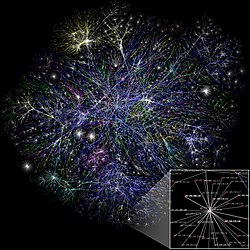

NoC 아키텍처는 일반적으로 스파스 Small-World Network(SWN; 소규모 세계 네트워크) 및 Scale-Free Network(SFN; 스케일프리 네트워크)를 모델화하여 상호접속 와이어 및 포인트 투 포인트 접속의 수, 길이, 면적 및 전력 소비를 제한합니다.

토폴로지

토폴로지는 NoC 설계의 첫 번째 기본적인 측면으로 네트워크 전체의 비용과 퍼포먼스에 큰 영향을 미칩니다.토폴로지에 따라 노드와 채널 간의 물리적 레이아웃과 연결이 결정됩니다.또한 메시지 트래버스홉과 각 홉의 채널 길이는 토폴로지에 따라 달라집니다.따라서 토폴로지는 지연과 소비전력에 큰 영향을 미칩니다.게다가 토폴로지에 의해서 노드간의 대체 패스의 수가 결정되기 때문에, 네트워크트래픽의 분산에 영향을 주고, 그 결과 달성된 네트워크 대역폭과 퍼포먼스에 영향을 줍니다.

혜택들

전통적으로 IC는 전용 포인트 투 포인트 연결로 설계되었으며, 각 신호 전용 와이어가 1개 있습니다.이것에 의해, 네트워크 토폴로지가 고밀화됩니다.특히 대형 설계에서는 물리적 설계 관점에서 몇 가지 제한이 있습니다.상호 연결 수에 2차 검정력이 필요합니다.와이어는 칩 면적의 대부분을 차지하고 있으며, 나노미터 CMOS 테크놀로지에서는 인터커넥트가 퍼포먼스와 동적 전력 소산을 모두 지배하고 있습니다.이는 칩을 통한 와이어에서의 신호 전파에 여러 클럭 사이클이 필요하기 때문입니다.이를 통해 회로에 더 많은 기생 캐패시턴스, 저항 및 인덕턴스가 축적됩니다.(포인트 투 포인트 접속의 배선 요건에 대해서는, 「임대」규칙을 참조해 주세요).

통신 서브시스템에서의 상호접속 희소성과 인접성은 기존의 버스 기반 및 크로스바 기반 시스템보다 몇 가지 개선점을 가져옵니다.

병렬화 및 확장성

네트워크 온 칩 링크의 와이어는 많은 신호에 의해 공유됩니다.NoC 내의 모든 데이터 링크는 다른 데이터 [why?]패킷 상에서 동시에 동작할 수 있기 때문에 높은 수준의 병렬화가 실현됩니다.따라서 통합 시스템의 복잡성이 계속 증가함에 따라 NoC는 이전 통신 아키텍처(예를 들어 전용 포인트 투 포인트 신호선, 공유 버스, 브리지가 있는 세그먼트버스)와 비교하여 성능(스루풋 등)과 확장성을 향상시킵니다.알고리즘은[which?] 대규모 병렬 처리를 제공하여 NoC의 가능성을 활용할 수 있도록 설계해야 합니다.

현재의 연구

일부 연구자들은[who?] NoC가 Quality of Service(QoS; 서비스 품질), 즉 스루풋, 엔드 투 엔드 지연,[2] 공정성 및 마감에 관한 [citation needed]다양한 요건을 충족해야 한다고 생각합니다.오디오 및 비디오 재생을 포함한 실시간 계산이 QoS를 지원하는 이유 중 하나입니다.그러나 VxWorks, RTLinux 또는 QNX와 같은 현재 시스템 구현에서는 특별한 [citation needed]하드웨어 없이도 밀리초 미만의 실시간 컴퓨팅을 실현할 수 있습니다.

이는 많은 실시간애플리케이션에서 기존 온칩인터커넥트인프라스트럭처의 서비스 품질은 충분하며 마이크로초의 정밀도를 실현하기 위해서는 전용 하드웨어 로직이 필요함을 나타낼 수 있습니다(사운드 또는 비디오 지터는 10분의 1밀리초의 레이텐시 보증이 필요합니다).NoC 레벨의 QoS(Quality of Service)를 실현하는 또 다른 동기는 퍼블릭 클라우드 컴퓨팅 인프라스트럭처에서 1개의 칩 멀티프로세서의 자원을 동시에 공유하는 여러 사용자를 지원하는 것입니다.이러한 경우 하드웨어 QoS 로직을 통해 서비스 공급자는 사용자가 받는 서비스 수준에 대해 계약상 보증을 할 수 있습니다.이 기능은 일부 기업 [citation needed]또는 정부 클라이언트에 의해 바람직하다고 간주될 수 있습니다.

물리 링크 레벨에서 네트워크 레벨에 이르기까지, 시스템 아키텍처와 애플리케이션 소프트웨어에 이르기까지, 모든 레벨에서 해결해야 할 많은 어려운 연구 문제가 남아 있습니다.2007년 [3]5월, 프린스턴 대학에서, 네트워크 온 칩에 관한 제1회 연구 심포지엄이 개최되었습니다.제2회 IEEE 네트워크 온 칩 국제 심포지엄은 2008년 4월에 뉴캐슬 대학에서 개최되었습니다.

칩상의 광네트워크(ONoC)[4][5]를 구성하는 집적형 광도파도와 소자에 대한 연구가 실시되고 있다.

NoC의 퍼포먼스를 향상시키는 가능한 방법은 칩(WiNoC)[6]이라는 이름의 무선통신채널을 사용하는 것입니다.

NoC의 부수적 이점

NoC에 의해 연결된 멀티코어 시스템에서는 일관성 메시지와 캐시 미스 요구가 스위치를 통과해야 합니다.따라서 스위치는 단순한 트래킹 및 포워딩 요소로 증강되어 향후 어떤 코어가 어떤 캐시 블록을 요구할지를 검출할 수 있습니다.그런 다음 포워딩 요소는 요청된 블록을 나중에 블록을 요구할 수 있는 모든 코어로 멀티캐스트합니다.이 메커니즘에 의해 캐시 미스환율이 [7]감소합니다.

벤치마크

NoC 개발 및 연구에는 다양한 제안과 옵션을 비교할 필요가 있다.이러한 평가에 도움이 되도록 NoC 트래픽패턴이 개발되고 있습니다.기존 NoC 벤치마크에는 NoCBench [8]및 MCSL NoC 트래픽패턴이 포함됩니다

상호접속처리장치

는 공동으로 통신과 동기화의 기본 요소의 집합을 통하고 현대적인 그는 선진 features[어떤?] 수 있도록 낮은 수준의 플랫폼 서비스를 제공한 system-on-chip 프로그래밍 모델의 주요 기능을 구현한 하드웨어와 소프트웨어 요소들을 가진 연계 처리 장치(IPU)[9]는 온칩의 통신망.terogeneous단일[definition needed] 다이로 응용 프로그램을 만듭니다.

「 」를 참조해 주세요.

메모들

레퍼런스

- ^ Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. p. 3. ISBN 9781466565272. OCLC 895661009.

- ^ "Balancing On-Chip Network Latency in Multi-Application Mapping for Chip-Multiprocessors". IPDPS. May 2014.

- ^ NoCS 2007 웹사이트

- ^ 온칩 네트워크 서지 목록

- ^ Inter-Chip/Intra-Chip 광네트워크 서지 목록 -

- ^ 슬리우사 V. I., 슬리우사 D.V. 나노안테나스 배열의 피라미드 설계.// VII 안테나 이론 및 기술에 관한 국제 회의(ICATT'11). - 우크라이나, 키이우. - 우크라이나 국립 기술 대학 " 키이우 폴리테크닉 연구소"- 2011년 9월 20일~23일 - 페이지 140~142 [1]

- ^ "NoC traffic". www.ece.ust.hk. Retrieved 2018-10-08.

- ^ 마르첼로 코폴라, 밀토스 DGramatikakis, Riccardo Locateli, Giuseppe Maruccia, Lorenzo Pieralisi, "비용 효율이 뛰어난 상호접속 처리 장치 설계: Spidergon STNoC", CRC Press, 2008, ISBN 978-1-4200-4471-3471-3

이고르 마르코프 ACM SIGDAe 뉴스레터의 Avinoam Kolodny's 칼럼에서 개작

원문은 http://www.sigda.org/newsletter/2006/060415.txt 에서 구할 수 있습니다.

추가 정보

- Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. ISBN 9781466565272. OCLC 895661009.

- Sheng Ma, Libo Huang, Mingche Lai, Wei Shi, Zhiying Wang (2014). Networks-on-Chip: From Implementations to Programming Paradigms (1st ed.). Amsterdam, NL: Morgan Kaufmann. ISBN 9780128011782. OCLC 894609116.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - Giorgios Dimitrakopoulos, Anastasios Psarras, Ioannis Seitanidis (2014-08-27). Microarchitecture of Network-on-Chip Routers: A Designer's Perspective (1st ed.). New York, NY. ISBN 9781461443018. OCLC 890132032.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - Natalie Enright Jerger, Tushar Krishna, Li-Shiuan Peh (2017-06-19). On-chip Networks (2nd ed.). San Rafael, California. ISBN 9781627059961. OCLC 991871622.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - Marzieh Lenjani, Mahmoud Reza Hashemi (2014). "Tree-based scheme for reducing shared cache miss rate leveraging regional, statistical and temporal similarities". IET Computers & Digital Techniques. 8: 30–48. doi:10.1049/iet-cdt.2011.0066.

{{cite journal}}: CS1 maint: 작성자 파라미터 사용(링크)

외부 링크

- NoC에서의 DATE 2006

- NoCS 2007 - 제1회 네트워크 온 칩에 관한 ACM/IEEE 국제 심포지엄

- NoCS 2008 - 제2회 IEEE 네트워크 온 칩 국제 심포지엄

- Jean-Jacques Lecler, Gilles Baillieu, Design Automation for Embedded Systems (Springer), "복잡한 SoC를 위한 애플리케이션 중심의 네트워크 온칩 아키텍처 탐색 및 개선", 2011년 6월, 제15호, 제2호, 페이지 133-158, doi:10.1007/106-17-17-590.http://www.arteris.com/hs-fs/hub/48858/file-14363521-pdf/docs/springer-appdrivennocarchitecture8.5x11.pdf