TO-5

TO-5

전자공학에서 TO-5는 트랜지스터와 일부 집적회로에 사용되는 표준화된 금속 반도체 패키지의 명칭이다.TO 요소는 "트랜지스터 개요"를 나타내며 JEDEC가 제작한 일련의 기술 도면을 가리킨다.[1]최초의 상용 실리콘 트랜지스터인 페어차일드 반도체의 2N696과 2N697은 TO-5 패키지로 나왔다.[2]null

시공 및 방향

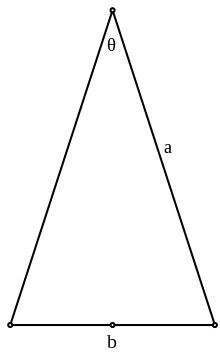

탭은 일반적으로 방출체인 핀 1에서 45°에 위치한다.일반적인 TO-5 패키지의 기본 직경은 8.9mm(0.35인치), 캡 직경은 8.1mm(0.32인치), 캡 높이는 6.3mm(0.25인치)이다.[1]핀은 개별 유리 금속 씰 또는 단일 수지 화분에 의해 포장에서 격리된다.때때로 하나의 핀이 금속 케이스에 직접 연결된다.null

변형

원래의 TO-5 패키지의 여러 변형 모델들은 캡 치수는 같지만 리드(와이어)의 수와 길이가 다르다.다소 부정확하게, TO-5와 TO-39는 흔히 제조자의 문헌에서 리드 수에 관계 없이 TO-5의 캡 치수를 가진 포장에 대한 동의어로 사용되며, 심지어 캡 높이와 리드 수에 관계 없이 TO-5의 직경을 가진 포장에 대해서도 사용된다.[3]TO-5와 비교하여 다른 변종(TO-33과 TO-42 제외)의 경우, 리드의 최소 길이는 38.1mm(1.50인치)에서 12.7mm(0.50인치)로 단축되었으며, 이는 스루홀 기술에 충분하고 비용 절감으로 이어지는 반면, 포인트 투 포인트 구축에는 더 긴 리드가 필요했다.리드 길이 25.4mm(1.00인치)와 19.05mm(0.750인치)는 상당히 일반적이지만 JEDEC에 의해 별도로 표준화되지는 않았다.리드가 2개에서 12개 사이인 변형 모델이 있다.리드는 직경 5.08mm(0.200인치)의 원형으로 배열된다(TO-96, TO-97, TO-100, TO-101 제외).1965년 듀얼 인라인 패키지가 도입되기 전 통합회로는 주로 리드 3개 이상의 TO-5 변종과 같은 메탈 캔 패키지로 포장됐다.[4]null

TO-39 / TO-9 / TO-16 / TO-42

TO-39, TO-9, TO-16 패키지는 3개의 리드를 가지며 위에서 언급한 단축 리드와 TO-5의 차이가 있다.[5]또한 TO-9과 TO-16 패키지에는 탭이 없다.[6]TO-42 패키지는 TO-5 패키지(긴 리드 포함)와 거의 동일하지만 베이스 하단에 4개의 스탠드오프가 있어 베이스가 회로기판 위 0.5mm 정도 위에 유지된다.[7]아마도 TO-16과 TO-42 지정은 실제로 사용되지 않았을 것이다.[8]null

TO-12 / TO-33

TO-12와 TO-33 패키지는 4개의 리드를 가지고 있다.[9]TO-33은 TO-5와 같이 38.1mm(1.50인치)의[10] 리드를 가지며, TO-12는 12.7mm(0.50인치)의 리드를 가진다.트랜지스터의 경우 일반적으로 네 번째 와이어는 무선 주파수 적용을 위한 전자기 차폐 수단으로 금속 케이스에 연결된다.null

TO-75

TO-75 패키지는 6개의 리드를 가지고 있다(대부분의 리드는 생략할 수 있다).[11]인접한 두 리드 사이의 최소 각도는 60°이다.null

TO-76 / TO-77

TO-76과 TO-77 패키지는 8개의 리드를 가지고 있다(그 중 최대 3개는 생략할 수 있다).[12]인접한 두 리드 사이의 최소 각도는 45°이다.TO-77 패키지는 TO-77 패키지의 하단이 회로 기판에 직접 장착될 수 있다는 점에서만 TO-76 패키지와 다르다. 반면 TO-76 패키지는 회로 기판과 패키지 사이의 거리가 최대 1.02mm(0.040인치)까지 필요하다.[13]null

TO-78 / TO-79 / TO-80 / TO-99

TO-78,[14] TO-79,[15] TO-80,[16] TO-99[17] 패키지에는 8개의 리드가 있다(이 중 최대 3개는 생략할 수 있다).인접한 두 리드 사이의 최소 각도는 45°이다.이 포장들은 뚜껑 높이에서 다른 변종들과 다르다.캡 높이는 6.3mm(0.25인치) 대신 TO-78/TO-99의 경우 4.45mm(0.175인치), TO-79의 경우 3.81mm(0.150인치), TO-80의 경우 2.41mm(0.095인치)에 불과하다.TO-78 패키지는 TO-78 패키지의 하단이 회로 기판에 직접 앉을 수 있다는 점에서만 TO-99 패키지와 다르다. 반면 TO-99 패키지는 회로 기판과 패키지 사이의 거리가 최대 1.02mm(0.040인치)까지 필요하다.null

TO-74

TO-74 패키지는 10개의 리드를 가지고 있다(대부분의 리드는 생략할 수 있다).[18]인접한 두 리드 사이의 최소 각도는 36°이다.null

TO-96 / TO-97 / TO-100

TO-96,[19] TO-97,[20] TO-100[21] 패키지에는 10개의 리드가 있다(대부분의 리드는 생략할 수 있다).인접한 두 리드 사이의 최소 각도는 36°이다.이러한 패키지의 경우 리드 원의 직경이 5.08mm(0.200인치)에서 5.84mm(0.230인치)로 증가한다.이것은 변하지 않는 지름의 캡에서 칩 면적을 약간 증가시킬 수 있다.TO-96은 표준 캡 높이가 6.3mm(0.25인치)인 반면, TO-100과 TO-97은 각각 4.45mm(0.175인치)와 3.81mm(0.150인치)의 캡 높이를 줄였다.null

TO-73

TO-73 패키지는 12개의 리드를 가지고 있다(대부분의 리드는 생략할 수 있다).[22]인접한 두 리드 사이의 최소 각도는 30°이다.null

TO-101

TO-101 패키지는 12개의 리드를 가지고 있다(대부분의 리드는 생략할 수 있다).[23]인접한 두 리드 사이의 최소 각도는 30°이다.이 패키지의 경우 리드 원의 직경은 5.08mm(0.200인치)에서 5.84mm(0.230인치)로 증가한다.이것은 변하지 않는 지름의 캡에서 칩 면적을 약간 증가시킬 수 있다.TO-101의 캡 높이는 4.45mm(0.175인치) (TO-78과 유사)이다.null

TO-205

TO-205는 이전의 패키지 정의를 지름 5.08mm(0.200인치)의 원형으로 배열된 리드로 대체하기 위한 것이다.[24][25]다른 개요는 현재 TO-205의 변형으로 정의된다. TO-5는 TO-205-AA로, TO-12는 TO-205-AB로, TO-33은 TO-205-AC로, TO-39는 TO-205-AD로 이름이 바뀐다.TO-205-AF에는 리드 3개와 캡 높이 4.32mm(0.170인치)의 새 패키지가 추가되었다.null

내셔널 스탠더드

| 표준조직 | 표준 | 에 대한 지정 | ||||

|---|---|---|---|---|---|---|

| TO-5 | TO-12 | TO-33 | TO-39 | TO-77 | ||

| 제덱 | JEP95[25] | TO-205-AA | TO-205-AB | TO-205-AC | TO-205-AD | — |

| IEC | IEC 60191[a][26] | C4/B4A | C4/B6C | C4/B6A | C4/B4C | C4/B7C |

| DIN | DIN 41873[27][26] | 5A3 | 5C4 | 5C3 | 5C8 | |

| EIAJ / JEITA | ED-7500A[a][28] | TC5/TB-5A | TC5/TB-14C | TC5/TB-14A | TC5/TB-5C | TC5/TB-15C |

| 영국 표준 | BS 3934[a][29][26] | SO-3/SB3-3A | SO-3/SB4-1B | SO-3/SB3-3B | SO-3/SB8-1B | |

| 고스탠다트 | GOST 18472—88[30] | — | KT-2-12[b] | — | KT-2-7[c] | — |

| 로즈스탠다트 | 고스트 R 57439[31] | |||||

| 콤비나트 미크로엘렉트로닉 에르푸르트 | TGL 11811[32] | — | — | — | B3/15-3a | — |

| TGL 26713/07[32] | — | — | — | F1BC3 | — | |

참조

- ^ a b "JEDEC TO-5 package specification" (PDF). JEDEC. Archived from the original (PDF) on June 18, 2017.

- ^ "Fairchild 2N697". Transistor Museum. Retrieved 2021-07-16.

- ^ "Metal Can Packages" (PDF). National Semiconductor / Texas Instruments. August 1999. pp. 7–14. Retrieved 2021-06-21.

- ^ "1965: Package is the first to accommodate system design considerations". Computer History Museum. Retrieved 2021-06-21.

- ^ "TO-39" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-9" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "...등록을 위한 최소한의 기준을 충족하지 못한다."

- ^ "...등록을 위한 최소한의 기준을 충족하지 못한다."

- ^ "TO-12" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-05. Retrieved 2021-06-21.

- ^ "TO-33" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-04. Retrieved 2021-06-21.

- ^ "TO-75" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-05. Retrieved 2021-06-21.

- ^ "TO-76" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-04. Retrieved 2021-06-21.

- ^ "TO-77" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-05. Retrieved 2021-06-21.

- ^ "TO-78" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-05. Retrieved 2021-06-21.

- ^ "TO-79" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-80" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-05. Retrieved 2021-06-21.

- ^ "TO-99" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-74" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-96" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-97" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-05. Retrieved 2021-06-21.

- ^ "TO-100" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-73" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "TO-101" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- ^ "Index by Device Type of Registered Transistor Outlines (TO)". JEDEC Publication No. 95 (PDF). JEDEC. October 2010. Retrieved 2021-07-13.

- ^ a b "Header Family 0.200 Pin Circle". JEDEC Publication No. 95 (PDF). JEDEC. November 1982. pp. 178–181. Retrieved 2021-07-13.

- ^ a b c "Semiconductors" (PDF). Pro Electron. 1978. pp. 215–219. Retrieved 2021-06-17.

- ^ "Semiconductor Databook" (PDF). Heilbronn: AEG-Telefunken. p. 15. Retrieved 2021-08-20.

- ^ "EIAJ ED-7500A Standards for the Dimensions of Semiconductor Devices" (PDF). JEITA. 1996. Retrieved 2021-06-14.

- ^ "Semiconductor and Photoelectric Devices" (PDF). Mullard. 1968. p. 457. Retrieved 2021-06-14.

- ^ "ГОСТ 18472—88 ПРИБОРЫ ПОЛУПРОВОДНИКОВЫЕ - Основные размеры" [GOST 18472—88 Semiconductor devices - basic dimensions] (PDF) (in Russian). Rosstandart. 1988. p. 37-38. Retrieved 2021-06-17.

- ^ "ПРИБОРЫ ПОЛУПРОВОДНИКОВЫЕ - Основные размеры" [Semiconductor devices - basic dimensions] (PDF) (in Russian). Rosstandart. 2017. p. 45. Retrieved 2021-06-17.

- ^ a b "TGL 26713/07: Gehäuse für Halbleiterbauelemente - Bauform F" (PDF) (in German). Leipzig: Verlag für Standardisierung. June 1988. Retrieved 2021-06-15.

외부 링크

- EESemi.com의 TO-5 패키지