전자 설계 자동화

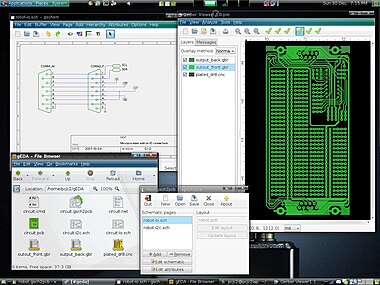

Electronic design automation전자설계자동화(EDA)는 전자컴퓨터지원설계(ECAD)[1]라고도 불리며 집적회로나 프린트회로기판과 같은 전자시스템을 설계하기 위한 소프트웨어 도구의 카테고리입니다.이 툴은 칩 설계자가 반도체 칩 전체를 설계 및 분석하는 데 사용하는 설계 흐름에서 함께 작동합니다.최신 반도체 칩은 수십억 개의 컴포넌트를 가질 수 있기 때문에 설계에 EDA 툴이 필수적입니다.특히 이 기사에서는 집적회로(IC)에 관한 EDA에 대해 설명합니다.

역사

초창기

EDA가 개발되기 전에는 집적회로를 손으로 설계하고 수동으로 배치했습니다.일부 고급 상점에서는 기하학 소프트웨어를 사용하여 단색 노출 이미지를 생성하는 Gerber 포토 플로터용 테이프를 생성했지만, 기계적으로 그려진 부품의 디지털 기록을 복사하기도 했습니다.이 프로세스는 기본적으로 그래픽스이며, 전자제품에서 그래픽스로의 번역을 수동으로 실시했습니다.이 시대의 가장 유명한 회사는 Calma로, GDSII 포맷은 현재도 사용되고 있습니다.1970년대 중반까지 개발자들은 제도뿐만 아니라 회로 설계도 자동화하기 시작했고 최초의 배치 및 라우팅 도구가 개발되었습니다. 이 일이 일어나면서 설계 자동화 회의의 진행은 대부분의 개발 사항을 카탈로그로 작성했습니다.

다음 시대는 1980년 Carver Mead와 Lynn Conway가 "VLSI 시스템 소개"를 발표한 후 시작되었습니다. 이 획기적인 텍스트는 실리콘으로 컴파일된 프로그래밍 언어를 사용한 칩 설계를 지지합니다.그 결과 논리 시뮬레이션을 사용하는 설계 검증 툴에 대한 접근성이 향상되어 설계 가능한 칩의 복잡성이 크게 증가했습니다.칩의 설계는 시공 전에 보다 철저하게 시뮬레이션할 수 있기 때문에 칩을 배치하기가 더 쉽고 올바르게 작동할 가능성이 더 높았습니다.언어와 도구가 진화했지만, 텍스트 프로그래밍 언어로 원하는 동작을 지정하고 도구가 세부적인 물리적 설계를 도출하도록 하는 이 일반적인 접근 방식은 오늘날에도 디지털 IC 설계의 기초가 됩니다.

최초의 EDA 도구는 학문적으로 제작되었습니다.가장 유명한 것 중 하나는 초기 VLSI 시스템을 설계하는 데 사용된 UNIX 유틸리티 세트인 "Berkeley VLSI Tools Tarball"이었다.회로 복잡성을 줄이는 에스프레소 휴리스틱 로직 미니마이저와 컴퓨터 지원 설계 플랫폼인 Magic이 여전히 널리 사용되고 있습니다.또 다른 중요한 발전은 MOSIS의 결성이었다.MOSIS는 실제 집적회로를 생산함으로써 학생용 칩 설계자를 양성하는 저렴한 방법을 개발한 대학과 제조사들로 구성된 컨소시엄이다.기본 개념은 신뢰성이 높고 저비용이며 상대적으로 기술이 낮은 IC 프로세스를 사용하여 웨이퍼당 다수의 프로젝트를 포장하고 각 프로젝트의 칩 복사본을 보존하는 것이었습니다.협력 제작자들은 가공된 웨이퍼를 기증하거나 원가에 판매했습니다. 이 프로그램은 장기적인 성장에 도움이 되었습니다.

상용 EDA의 탄생

1981년은 산업으로서의 EDA의 시작을 알렸다.수년간 Hewlett Packard, Tektronix 및 Intel과 같은 대형 전자 회사는 내부적으로 EDA를 추구해 왔으며, 매니저와 개발자들은 EDA에 집중하기 위해 EDA를 분사하기 시작했습니다.Daisy Systems, Mentor Graphics 및 Valid Logic Systems는 모두 이 시기에 설립되어 DMV라고 불리고 있습니다.미국 국방부는 1981년에 하드웨어 기술 언어로서 VHDL의 자금 지원을 추가로 시작했습니다.몇 년 사이에 EDA를 전문으로 하는 기업이 많이 생겨났는데, 각각의 기업이 약간씩 중점을 두고 있었습니다.

EDA의 첫 번째 무역 박람회는 1984년 Design Automation Conference에서 개최되었으며 1986년 Gateway Design Automation에 의해 하드웨어 기술 언어로 또 다른 인기 있는 고급 설계 언어인 Verilog가 처음 소개되었습니다.시뮬레이터는 칩 설계와 실행 가능한 사양을 직접 시뮬레이션할 수 있도록 이러한 도입에 신속하게 대응했습니다.몇 년 안에, 백엔드는 논리 합성을 수행하기 위해 개발되었습니다.

현황

현재의 디지털 플로우는 매우 모듈화되어 있어 프런트 엔드는 개별 테크놀로지에 관계없이 셀과 유사한 유닛의 호출로 컴파일되는 표준화된 설계 기술을 생성합니다.셀은 특정 집적회로 기술을 이용하여 논리 또는 기타 전자 기능을 구현합니다.제작자는 일반적으로 표준 시뮬레이션 도구에 맞는 시뮬레이션 모델을 사용하여 생산 공정을 위한 구성요소 라이브러리를 제공합니다.

대부분의 아날로그 회로는 여전히 수동 방식으로 설계되어 아날로그 설계에 고유한 전문 지식(예: 일치하는 개념)[2]이 필요합니다.따라서 아날로그 EDA 도구는 더 많은 기능이 필요하기 때문에 상호 작용이 더 강하고 일반적으로 구성요소가 덜 이상적입니다.

전자제품용 EDA는 반도체 [3]기술의 지속적인 확장으로 그 중요성이 급격히 증가했다.일부 사용자는 반도체 제조 시설("fabs")을 운영하는 주조 공장 운영자이며, EDA 소프트웨어를 사용하여 제조 준비 상태를 평가하는 기술 설계 서비스 회사를 활용할 책임이 있는 추가적인 개인도 있습니다.EDA 도구는 설계 기능을 FPGA로 프로그래밍하거나 필드 프로그래밍 가능한 게이트 어레이, 맞춤형 집적회로 설계에도 사용됩니다.

소프트웨어 초점

이 기사는 대부분의 독자들이 이해하기에는 너무 전문적일 수 있다.을 삭제하지 이해할 수 개선해주시기 . (2017년 2월) (이 삭제 방법 및 ) |

설계.

설계 흐름은 주로 다음과 같은 몇 가지 주요 구성 요소를 통해 특징지어집니다.

- 고레벨 합성(행동 합성 또는 알고리즘 합성) – 고레벨 설계 기술(C/C++ 등)은 레지스터 간의 상호작용을 통해 회로를 나타내는 RTL 또는 레지스터 전송 수준으로 변환됩니다.

- 로직 합성 – RTL 설계 설명(Verilog 또는 VHDL로 작성 등)을 개별 넷리스트 또는 로직 게이트 표현으로 변환합니다.

- 개략도 캡처 – 표준 셀 디지털, 아날로그 RF 유사 캡처 CIS by Cadence 및 IS in Proteus.[clarification needed]

- 레이아웃 – 일반적으로 Orcad의 레이아웃 by Cadence, Proteus의 ARES와 같은 개략도 중심의 레이아웃

시뮬레이션

- 트랜지스터 시뮬레이션 – 개략도/레이아웃 동작의 저레벨 트랜지스터 시뮬레이션으로 디바이스 레벨에서 정확합니다.

- 로직 시뮬레이션– RTL 또는 게이트 넷리스트의 디지털(부울 0/1) 동작을 디지털로 시뮬레이션하여 부울 레벨로 정확합니다.

- 동작 시뮬레이션 – 사이클 레벨 또는 인터페이스 레벨에서 정확한 설계 아키텍처 동작의 고급 시뮬레이션.

- 하드웨어 에뮬레이션– 제안된 설계의 로직을 에뮬레이트하기 위해 특수 목적 하드웨어를 사용합니다.아직 구축되지 않은 칩 대신 시스템에 연결할 수 있습니다. 이를 인서킷 에뮬레이션이라고 합니다.

- 기술 CAD는 기본 프로세스 기술을 시뮬레이션하고 분석합니다.디바이스의 전기적 특성은 디바이스 물리학에서 직접 도출됩니다.

- 전자기장 해결사 또는 그냥 전기장 해결사는 IC 및 PCB 설계에 관심이 있는 경우 맥스웰 방정식을 직접 해결합니다.위의 [where?]레이아웃 추출보다 속도는 느리지만 정확도가 높은 것으로 알려져 있습니다.

분석 및 검증

- 기능 검증

- 시계 도메인지만, 이 checks/tools과 데이터 손실, meta-stability 여러 시계 도메인의 디자인에 사용 때문에 같은 잠재적으로 문제 보고 탐지 전문 훈련을 받은 검증(CDC수표):linting과 비슷한.

- 형식 검증 및 모델 체크: 시스템에 원하는 속성이 있고, 특정 바람직하지 않은 효과(데드록 등)가 발생할 수 없음을 수학적인 방법으로 증명하려고 합니다.

- 동등성 검사: 칩의 RTL 설명과 합성 게이트 넷 리스트를 알고리즘적으로 비교하여 논리 레벨에서의 기능적 동등성을 보증합니다.

- 정적 타이밍 분석: 입력에 의존하지 않는 방식으로 회로의 타이밍을 분석하여 가능한 모든 입력에 대해 최악의 경우를 찾아냅니다.

- 물리적인 검증, PV: 설계가 물리적으로 제조 가능한지, 그 결과 발생하는 칩이 물리적인 결함을 방지하지 않고 원래의 사양을 충족하는지 확인합니다.

제조 준비

- 마스크 데이터 준비 또는 MDP - 칩을 물리적으로 제조하는 데 사용되는 실제 리소그래피 포토마스크 생성.

- 레이아웃의 제조성을 향상시키기 위한 커스텀 지정 및 구조를 포함한 칩 마감.후자의 예로는 씰링 및 필러 [4]구조가 있습니다.

- 테스트 패턴과 얼라인먼트 마크가 있는 레티클 레이아웃 생성.

- 해상도 향상 기법 또는 RET와 같은 그래픽 연산을 통해 레이아웃 데이터를 강화하는 레이아웃-투-마스크 준비 – 최종 포토마스크의 품질을 높이는 방법.여기에는 광학 근접 보정(OPC)도 포함됩니다. OPC는 나중에 이 마스크를 사용하여 칩을 제조할 때 발생하는 회절 및 간섭 효과에 대한 사전 보상입니다.

- 마스크 생성 – 계층 설계에서 플랫 마스크 이미지를 생성합니다.

- 자동 테스트 패턴 생성 또는 ATPG – 가능한 한 많은 논리 게이트 및 기타 컴포넌트를 실행하기 위해 패턴 데이터를 체계적으로 생성합니다.

- 빌트인 셀프 테스트(BIST)– 설계에 로직 또는 메모리 구조를 자동으로 테스트하는 자체 내장 테스트 컨트롤러 설치

기능 안전성

- 원하는 안전 무결성 수준에 대한 준수 요건을 충족하기 위한 기능적 안전성 분석, 시간 내 고장(FIT) 비율의 체계적 계산 및 설계에 대한 진단 적용 범위 메트릭.

- 기능적인 안전성 합성, 구조화 요소(모듈, RAM, ROM, 레지스터 파일, FIFO)에 신뢰성 향상 기능을 추가하여 장애 검출/내결함성을 향상시킵니다.여기에는 오류 검출 및/또는 수정 코드 추가(해밍), 장애 검출 및 내결함성을 위한 다중 로직(복제/복제), 프로토콜 체크(인터페이스 패리티, 주소 정렬, 비트 수) 등이 포함됩니다.

- 설계에 고장을 삽입하고 안전 메커니즘이 대상으로 간주되는 고장에 대해 적절한 방식으로 반응하는 것을 포함하여 고장 캠페인의 기능적 안전 검증, 실행.

회사들

구회사

2011년 [5]12월[update] 현재 시가총액 및 회사명:

- 57억7천만달러[6]– Synopsys

- 44억[7] 6천만 달러– Cadence

- 34억 1천만 달러– Altium

- 23억 3천만 달러– 멘토 그래픽스

- 5억 7백만 달러 – 마그마 설계 자동화; Synopsys는 2012년 2월에[8][9] 마그마를 인수했습니다.

- 64억4천만 대만달러– Spring Soft, Synopsys는 2012년 8월에 Spring Soft를 인수

- 주식회사 주켄 119억5000만엔

주의: EEsof는 [10]이 리스트에 포함되어 있을 가능성이 높지만, Keysight의 EDA 부문이기 때문에 시가총액은 없습니다.

취득

많은 EDA 기업들은 핵심 [11]사업에 적응할 수 있는 소프트웨어나 다른 기술을 가진 소규모 기업을 인수합니다.시장 리더의 대부분은 소규모 기업의 합병체이며, 이러한 경향은 소프트웨어 회사가 디지털 회로상의 대규모 벤더의 프로그램 스위트에 자연스럽게 맞는 액세서리로 툴을 설계하는 경향에 기인하고 있습니다.많은 새로운 툴은 아날로그 설계와 혼합 [12]시스템을 채택하고 있습니다.전자시스템 전체를 하나의 칩에 담는 추세 때문이다.

「 」를 참조해 주세요.

레퍼런스

- ^ "About the EDA Industry". Electronic Design Automation Consortium. Archived from the original on August 2, 2015. Retrieved July 29, 2015.

- ^ J. Lienig, J. Scheible (2020). "Chap. 6: Special Layout Techniques for Analog IC Design". Fundamentals of Layout Design for Electronic Circuits. Springer. p. 213-256. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ^ Lavagno, Martin, and Scheffer (2006). Electronic Design Automation For Integrated Circuits Handbook. Taylor and Francis. ISBN 0849330963.

{{cite book}}: CS1 maint: 여러 이름: 작성자 목록(링크) - ^ J. Lienig, J. Scheible (2020). "Chap. 3.3: Mask Data: Layout Post Processing". Fundamentals of Layout Design for Electronic Circuits. Springer. p. 102-110. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ^ 기업 비교 - 구글 파이낸스.Google.com 를 참조해 주세요.2013년 8월 10일 취득.

- ^ Synopsys, Inc.: 나스닥:SNPS 인용 및 뉴스 - 구글 파이낸스Google.com (2013-05-22)2013년 8월 10일 취득.

- ^ CDNS Key Statistics Cadence Design Systems, Inc. 재고 - Yahoo! 금융.자금.yahoo.com 를 참조해 주세요.2013년 8월 10일 취득.

- ^ Dylan McGrath (November 30, 2011). "Synopsys to buy Magma for $507 million". EETimes. Archived from the original on October 25, 2012. Retrieved July 17, 2012.

- ^ "Synopsys to Acquire Magma Design Automation".

- ^ "Agilent EEsof EDA – Part I".

- ^ Kirti Sikri Desai (2006). "EDA Innovation through Merger and Acquisitions". EDA Cafe. Retrieved March 23, 2010.

- ^ "Semi Wiki:EDA Mergers and Acquisitions Wiki". SemiWiki.com. January 16, 2011. Archived from the original on April 3, 2019. Retrieved April 3, 2019.

- 메모들

- http://www.staticfreesoft.com/documentsTextbook.html Steven M의 VLSI 설계에 관한 컴퓨터 지원.루빈

- Lienig, Scheible, Springer, doi: 10.1007/978-3-030-39284-0ISBN 978-39284-0, 2020

- VLSI 물리 설계: 그래프 분할에서 타이밍 클로즈까지 Kahng, Lienig, Markov 및 Hu에 의한 doi: 10.1007/978-90-481-6ISBN 978-90-481-9590-9, 2011

- 집적회로의 전자설계 자동화 핸드북, Lavagno, Martin, Scheffer, ISBN 0-8493-3096-3, 2006

- Kluwer Academic Publishers, Dirk Jansen 등의 전자 설계 자동화 핸드북, ISBN 1-4020-7502-2, 2003, 독일 ISBN 3-446-2288-4(2005)에서도 이용 가능

- Thomas Lengauer, ISBN 3-519-02110-2, Teubner Verlag, 1997년 집적회로 레이아웃을 위한 조합 알고리즘.