시스템 온 칩

System on a chip칩상의 시스템(SoC; /ˌsooʊsiː/es-oh-SEE 또는 /skk/sock[nb 1])은 시스템 온 칩 또는 시스템 온 칩이라고도 하며 컴퓨터 또는 기타 전자 시스템의 모든 컴포넌트 또는 대부분의 컴포넌트를 집적하는 집적회로입니다.이러한 컴포넌트에는 거의 항상 중앙처리장치(CPU), 메모리 인터페이스, 온칩 입출력 디바이스, 입출력 인터페이스, 세컨더리 스토리지 인터페이스가 포함되어 있으며, 무선 모뎀이나 그래픽스 처리장치(GPU) 등의 다른 컴포넌트와 함께 단일 기판 또는 [1]마이크로칩에 포함되어 있습니다.여기에는 디지털, 아날로그, 혼합 신호 및 무선 주파수 신호 처리 기능이 포함되어 있을 수 있습니다(그렇지 않으면 애플리케이션프로세서만으로 간주됩니다).

고성능 SoC는 많은 경우 물리적으로 분리된 전용 메모리 및 세컨더리 스토리지(각각 LPDDR, eUFS 또는 eMMC 등) 칩과 쌍을 이루며 패키지(PoP) 구성으로 SoC 위에 계층화되거나 SoC 근처에 배치할 수 있습니다.또한 SoC는 별도의 무선 [2]모뎀을 사용할 수 있습니다.

SoC는 기능에 따라 컴포넌트를 분리하여 중앙 인터페이스 회로 [nb 2]기판을 통해 접속하는 일반적인 메인보드 기반 PC 아키텍처와는 대조적입니다.메인보드는 탈부착 또는 교환 가능한 컴포넌트를 수용하여 접속하는 반면 SoC는 이들 컴포넌트를 모두 하나의 집적회로로 통합합니다.SoC는 일반적으로 CPU, 그래픽스 및 메모리 인터페이스,[nb 3] 세컨더리 스토리지와 USB 연결,[nb 4] 랜덤 액세스 및 읽기 전용 메모리, 세컨더리 스토리지 및/또는 컨트롤러를 하나의 회로 다이로 통합합니다.한편 메인보드는 이들 모듈을 개별 컴포넌트 또는 확장 카드로 연결합니다.

SoC는 마이크로컨트롤러, 마이크로프로세서 또는 여러 프로세서 코어를 GPU, Wi-Fi 및 셀룰러 네트워크 무선 모뎀 및/또는 하나 이상의 코프로세서와 같은 주변기기와 통합합니다.마이크로컨트롤러가 마이크로프로세서와 주변기기의 회로 및 메모리를 통합하는 것과 마찬가지로 SoC는 마이크로컨트롤러와 보다 고도의 주변기기를 통합하는 것으로 볼 수 있습니다.

보다 긴밀하게 통합된 컴퓨터 시스템 설계는 동등한 기능을 가진 멀티칩 설계보다 성능을 향상시키고 반도체 다이 면적뿐만 아니라 전력 소비도 줄입니다.이는 컴포넌트의 교환 가능성을 감소시키는 대가를 치르게 됩니다.정의상 SoC 설계는 서로 다른 컴포넌트 모듈 간에 완전히 또는 거의 완전히 통합됩니다.이러한 이유로 컴퓨터 하드웨어 업계에서는 SoC의 영향과 모바일 및 임베디드 컴퓨팅 시장에서 얻은 교훈에 따라 컴포넌트의 통합이 강화되는 경향이 일반적으로 나타나고 있습니다.SoC는 임베디드 컴퓨팅과 하드웨어 가속화를 향한 큰 흐름의 일부라고 볼 수 있습니다.

SoC는 모바일 컴퓨팅([3][4]스마트폰이나 태블릿 컴퓨터 등) 및 에지 컴퓨팅 시장에서 매우 일반적입니다.또한 WiFi 라우터나 사물 인터넷과 같은 임베디드 시스템에서도 일반적으로 사용됩니다.

종류들

일반적으로 다음 세 가지 유형의 SoC가 있습니다.

- 마이크로컨트롤러로 만들어진 SoC,

- 휴대 전화에서 자주 볼 수 있는 마이크로프로세서를 중심으로 구축된 SoC.

- 상기의 2개의 카테고리에 들어가지 않는 특정의 애플리케이션 전용의 전용의 집적 회로 SoC.

적용들

SoC는 모든 컴퓨팅 태스크에 적용할 수 있습니다.단, 일반적으로 태블릿, 스마트폰, 스마트워치, 넷북 등의 모바일 컴퓨팅과 임베디드 시스템 및 이전에 마이크로 컨트롤러가 사용되었던 애플리케이션에 사용됩니다.

임베디드 시스템

이전에는 마이크로 컨트롤러만 사용할 수 있었던 SoC는 임베디드 시스템 시장에서 두각을 나타내고 있습니다.시스템 통합이 긴밀해 신뢰성과 평균 장애 발생까지의 시간이 향상됩니다.SoC는 마이크로 [5]컨트롤러보다 고도의 기능과 컴퓨팅 능력을 제공합니다.애플리케이션에는 AI 가속, 임베디드 머신 비전,[6] 데이터 수집, 원격 측정, 벡터 처리 및 주변 인텔리전스가 포함됩니다.대부분의 임베디드 SoC는 사물 인터넷, 산업용 사물 인터넷 및 에지 컴퓨팅 시장을 타깃으로 합니다.

모바일 컴퓨팅

모바일 컴퓨팅 기반의 SoC는 프로세서, 메모리, 온칩 캐시, 무선 네트워크 기능 및 많은 경우 디지털 카메라 하드웨어와 펌웨어를 번들합니다.메모리 사이즈가 증가하면 하이엔드 SoC에는 메모리 및 플래시 스토리지가 없는 경우가 많아집니다.대신 메모리 및 플래시 메모리는 [7]SoC 바로 옆 또는 그 위에 배치됩니다(패키지 온 패키지).모바일 컴퓨팅 SoC의 예는 다음과 같습니다.

퍼스널 컴퓨터

1992년 Acon Computers는 ARM250 SoC를 탑재한 A3010, A3020 및 A4000 시리즈 퍼스널 컴퓨터를 생산했습니다.원래의 Acon ARM2 프로세서와 메모리 컨트롤러(MEMC), 비디오 컨트롤러(VIDC) 및 I/O 컨트롤러(IOC)를 조합했습니다.이전의 Acoron ARM 탑재 컴퓨터에서는, 이것들은 4개의 개별 칩이었습니다.ARM7500 칩은 ARM700, VIDC20 및 IOMD 컨트롤러를 기반으로 하는 2세대 SoC로 셋톱박스 등 임베디드 기기뿐만 아니라 이후 아콘 PC에도 널리 라이선스되었습니다.

SoC는 2018년 [8]현재 주류 PC에 적용되고 있다.특히 노트북과 태블릿 PC에 적용됩니다.태블릿 및 노트북 제조업체는 임베디드 시스템 및 스마트폰 시장에서 전력 소비 절감, 하드웨어 및 펌웨어 모듈의 긴밀한 통합, LTE 및 기타 칩 내장 무선 네트워크 통신(통합 네트워크 인터페이스 컨트롤러)[10]에 대한 교훈을 얻었습니다.

ARM 기반:

x86 기반:

구조.

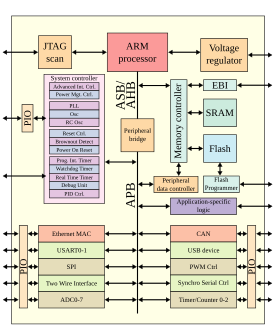

SoC는 소프트웨어 코드를 실행하는 마이크로프로세서를 포함한 하드웨어 기능 유닛과 이들 기능 모듈 간의 연결, 제어, 지시 및 인터페이스를 위한 통신 서브시스템으로 구성됩니다.

기능 컴포넌트

프로세서 코어

SoC에는 적어도1개의 프로세서코어가 필요하지만 일반적으로 SoC에는 여러 개의 코어가 있습니다.프로세서 코어는 마이크로컨트롤러, 마이크로프로세서(μP),[11] 디지털시그널프로세서(DSP) 또는 애플리케이션 고유의 명령 세트프로세서(ASIP) [12]코어입니다.ASIP에는 응용 프로그램도메인용으로 커스터마이즈된 명령어세트가 있으며 특정 유형의 워크로드에 대한 범용 명령어보다 효율적이 되도록 설계되어 있습니다.멀티프로세서 SoC에는 정의상 여러 프로세서코어가 있습니다

싱글코어, 멀티코어, 멀티코어 모두 SoC 프로세서 코어는 일반적으로 RISC 명령어 세트 아키텍처를 사용합니다.RISC 아키텍처는 SoC용 CISC 프로세서에 비해 유리합니다.이는 디지털 로직이 적게 필요하기 때문에 온보드 전력과 면적이 적기 때문입니다.임베디드 컴퓨팅 시장이나 모바일 컴퓨팅 시장에서는 영역과 전력이 크게 제약되기 때문입니다.특히 SoC 프로세서코어는 IP 코어로 지정된 소프트 프로세서로 [11]x86보다 전력 효율이 높기 때문에 ARM 아키텍처를 사용하는 경우가 많습니다.

기억

SoC는 마이크로컨트롤러 및 기타 임베디드 시스템과 마찬가지로 계산을 수행하려면 반도체 메모리 블록을 가지고 있어야 합니다.애플리케이션에 따라 SoC 메모리는 메모리 계층과 캐시 계층을 형성할 수 있습니다.이는 모바일 컴퓨팅 시장에서는 흔히 볼 수 있는 일이지만 많은 저전력 내장 마이크로 컨트롤러에서는 필수가 아닙니다.SoC의 메모리 테크놀로지에는 읽기 전용 메모리(ROM), 랜덤 액세스 메모리(RAM), EEPROM(Electrically Erasable Programmable ROM) 및 플래시 [11]메모리가 있습니다.다른 컴퓨터 시스템과 마찬가지로 RAM은 비교적 빠르지만 더 비싼 정적 RAM(SRAM)과 느리지만 저렴한 동적 RAM(DRAM)으로 세분화할 수 있습니다.SoC에 캐시 계층이 있는 경우 보통 SRAM은 프로세서 레지스터와 코어의 내장 캐시를 구현하기 위해 사용되는 반면 DRAM은 메인 메모리에 사용됩니다.SoC가 복수의 프로세서를 탑재하고 있는 경우, 「메인 메모리」는 1개의 프로세서(멀티 코어 가능)에만 한정되는 경우가 있습니다.이 경우, SoC는 분산형 메모리이며, 다른 [12]프로세서에서 액세스 하려면 § 모듈간 통신 온칩을 통해 전송되어야 합니다.멀티 프로세싱 메모리 문제에 대한 자세한 내용은 캐시 일관성 및 메모리 지연 시간을 참조하십시오.

인터페이스

SoC에는 일반적으로 통신 프로토콜을 위한 외부 인터페이스가 포함됩니다.USB, FireWire, Ethernet, USART, SPI, HDMI, I²C 등의 업계 표준을 기반으로 하는 경우가 많습니다.이러한 인터페이스는, 목적의 애플리케이션에 따라서 다릅니다.Wi-Fi, Bluetooth, 6LoWPAN, 근거리 통신 등의 무선 네트워크 프로토콜도 지원됩니다.

필요에 따라 SoC에는 아날로그-디지털 변환기 및 디지털-아날로그 변환기(종종 신호 처리용)를 포함한 아날로그 인터페이스가 포함됩니다.스마트 변환기를 비롯한 다양한 유형의 센서 또는 액추에이터와 상호 작용할 수 있습니다.애플리케이션 고유의 모듈 또는 [nb 5]실드와 인터페이스 할 수 있습니다.또는 아날로그 센서가 SoC에 내장되어 있고 수학 처리를 위해 판독값을 디지털 신호로 변환해야 하는 경우와 같이 SoC 내부에 있을 수 있습니다.

디지털 신호 프로세서

디지털 신호 프로세서(DSP) 코어는 대부분의 경우 SoC에 포함되어 있습니다.센서, 액추에이터, 데이터 수집, 데이터 분석 및 멀티미디어 처리를 위해 SoC에서 신호 처리 작업을 수행합니다.DSP 코어는 일반적으로 매우 긴 명령어(VLIW)와 단일 명령어, 다중 데이터(SIMD) 명령어 세트 아키텍처를 갖추고 있기 때문에 병렬 처리 및 슈퍼스칼라 [12]: 4 실행을 통한 명령어 수준의 병렬화를 매우 쉽게 이용할 수 있습니다.DSP 코어는 대부분의 경우 애플리케이션 고유의 명령어를 갖추고 있기 때문에 일반적으로 애플리케이션 고유의 명령어세트 프로세서(ASIP)가 사용됩니다.이러한 애플리케이션 고유의 명령은 이러한 명령을 계산하는 전용 하드웨어 기능 유닛에 해당합니다.

일반적인 DSP 명령에는 다중 누적, 고속 푸리에 변환, 퓨전 다중 가산 및 컨볼루션이 포함됩니다.

다른.

다른 컴퓨터 시스템과 마찬가지로 SoC는 클럭 신호를 생성하고, SoC 기능의 실행을 제어하며, 필요에 따라 SoC의 신호 처리 애플리케이션에 대한 시간 컨텍스트를 제공하기 위해 타이밍 소스를 필요로 합니다.일반적인 시간 소스는 크리스털 오실레이터와 위상 잠금 루프입니다.

카운터 타이머, 실시간 타이머, 전원 투입 리셋 제너레이터 등의 SoC 주변기기.SoC에는 전압 조절기와 전원 관리 회로도 포함되어 있습니다.

모듈간 통신

SoC는 많은 실행 단위로 구성됩니다.이러한 장치는 종종 데이터와 명령을 주고받아야 합니다.따라서 가장 사소한 SoC를 제외한 모든 SoC에는 통신 서브시스템이 필요합니다.원래는 다른 마이크로컴퓨터 기술과 마찬가지로 데이터 버스 아키텍처가 사용되었지만 최근에는 Networks-on-Chip(NoC; 네트워크 온 칩)으로 알려진 희박한 상호 통신 네트워크에 기반한 설계가 두드러지고 있으며 가까운 미래에 [13]SoC 설계에서 버스 아키텍처를 추월할 것으로 예상됩니다.

버스 기반 통신

지금까지 공유 글로벌 컴퓨터 버스는 일반적으로 SoC의 [13]다른 컴포넌트(블록이라고도 함)를 연결했습니다.SoC 통신에 매우 일반적인 버스는 ARM의 로열티 없는 Advanced Microcontroller Bus Architecture(AMBA) 규격입니다.

다이렉트 메모리액세스 컨트롤러는, 외부 인터페이스와 SoC 메모리간에 직접 데이터를 라우팅 해, CPU 또는 제어 유닛을 바이패스 해, SoC 의 데이터 스루풋을 향상시킵니다.이는 컴포넌트 기반의 멀티칩모듈 PC 아키텍처의 주변기기 드라이버와 비슷합니다.

컴퓨터 버스는 확장성이 제한되어 있어 단일 [13]: xiii 칩에서 최대 수십 개의 코어(멀티코어)만 지원합니다.와이어 지연은 소형화가 계속되기 때문에 측정할 수 없습니다.또한 연결된 코어의 수에 따라 시스템 퍼포먼스가 확장되지 않습니다.SoC의 동작 주파수는 전력을 유지하기 위해 추가 코어를 연결할 때마다 감소해야 합니다.또한 긴 와이어는 대량의 전력을 소비합니다.이러한 과제는, 다코어 시스템 온 [13]: xiii 칩을 서포트하는 데 있어서 매우 중요합니다.

칩상의 네트워크

2010년대 후반에는 SoC가 버스 기반 프로토콜 대신 네트워크와 유사한 토폴로지의 관점에서 통신 서브시스템을 구현하는 추세가 나타나고 있습니다.SoC의 프로세서 코어가 증가하는 경향에 따라 온칩 통신 효율이 시스템 전체의 퍼포먼스와 [13]: xiii 비용을 결정하는 중요한 요소 중 하나가 되었습니다.이것에 의해, 버스 [13]: xiii 베이스 네트워크의 보틀 넥을 극복하기 위해서, 「Networks on Chip」(NoC)이라고 불리는 라우터 베이스의 패킷 교환을 가지는 상호 접속 네트워크가 등장하고 있습니다.

네트워크 온 칩에는 수신처 및 애플리케이션 고유의 라우팅, 전력 효율 향상, 버스 경합 가능성 감소 등의 이점이 있습니다.네트워크 온칩 아키텍처는 일반적으로 네트워크 계층이 적지만 TCP 및 온칩 [13]통신을 위한 인터넷 프로토콜 스위트 같은 통신 프로토콜에서 영감을 얻습니다.최적의 Network-on-Chip 네트워크 아키텍처는 현재 많은 연구 관심 분야입니다.NoC 아키텍처는 Torus, 하이퍼큐브, 메시 및 트리 네트워크 등의 기존 분산 컴퓨팅 네트워크 토폴로지부터 유전 알고리즘 스케줄링, 분기 및 랜덤화 수명(TTL) 등의 랜덤화 알고리즘까지 다양합니다.

많은 SoC 연구자들은 SoC 아키텍처가 SoC 설계의 전력 및 throughput 요구를 효율적으로 충족시키는 것으로 나타났기 때문에 NoC 아키텍처가 SoC 설계의 미래라고 생각합니다.현재의 NoC 아키텍처는 2차원입니다.2D IC 설계는 SoC의 코어 수가 증가함에 따라 평면도 선택의 폭이 제한되므로 3차원 집적회로(3DIC)가 등장함에 따라 SoC 설계자는 3D NoC로 [13]알려진 3차원 온칩 네트워크 구축을 검토하고 있습니다.

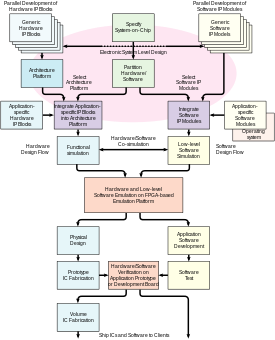

설계 흐름

칩상의 시스템은 § Structure에 기재된 하드웨어와 마이크로컨트롤러, 마이크로프로세서 또는 디지털 신호프로세서 코어, 주변기기 및 인터페이스를 제어하는 소프트웨어로 구성됩니다.SoC의 설계 흐름은 아키텍처 공동 설계라고도 하는 하드웨어와 소프트웨어를 동시에 개발하는 것을 목표로 합니다.설계 흐름은 최적화( optim 최적화 목표) 및 제약도 고려해야 합니다.

대부분의 SoC는 위에서 설명한 하드웨어 요소 및 실행 유닛의 사전 인정 하드웨어 컴포넌트 IP 코어 사양(블록)과 그 동작을 제어하는 소프트웨어 디바이스 드라이버에서 개발됩니다.특히 중요한 것은 USB와 같은 업계 표준 인터페이스를 구동하는 프로토콜 스택입니다.하드웨어 블록은 컴퓨터 지원 설계 도구, 특히 전자 설계 자동화 도구를 사용하여 조립됩니다. 소프트웨어 모듈은 소프트웨어 통합 개발 환경을 사용하여 통합됩니다.

SoCs 요소들 또한 종종 C++, MATLAB또는 SystemC 같은 높은 수준의 프로그래밍 언어에서 및 RTL설계에 C 같은 높은 수준의 합성(HLS)도구를 통해 HDL또는 HDL.[14]HLS제품이라고 불리는 흐름으로 개조하도록 설계된"알고리즘적인 합성"수 있는 디자이너들을 사용하여 C++에 모델과 새로 합성해 시스템, 회로, 소프트웨어 및 verificatio.n르벨은 일반적으로 HDL로 [15]지정되어 있는 시간 척도에 관계없이 컴퓨터 엔지니어에게 일반적으로 알려진 하나의 고급 언어로 제공됩니다.그 외의 컴포넌트는 소프트웨어인 채로 컴파일되어 IP 코어로 HDL의 모듈로서 SoC에 포함되어 있는 소프트 코어 프로세서에 짜넣을 수 있습니다.

SoC의 아키텍처가 정의되면 새로운 하드웨어 요소가 회로 동작을 정의하는 레지스터 전송 레벨(RTL)이라는 추상 하드웨어 기술 언어로 작성되거나 고급 언어에서 고급 합성을 통해 RTL로 합성됩니다.이들 요소는 하드웨어 기술 언어로 연결되어 완전한 SoC 설계를 작성합니다.이러한 컴포넌트를 접속하여 다른 벤더가 제공하는 다른 인터페이스 간에 변환하기 위해 지정된 논리를 글루 로직이라고 합니다.

설계 검증

칩은 반도체 주조 공장에 보내지기 전에 검증 정확성을 검증합니다.이 프로세스는 기능 검증이라고 불리며 칩 설계 라이프 사이클에서 소비되는 시간과 에너지의 상당 부분을 차지하며,[16][17] 70%에 이르는 경우가 많습니다.칩의 복잡성이 증가함에 따라 SystemVerilog, SystemC, e, OpenVera 등의 하드웨어 검증 언어가 사용되고 있습니다.검증 단계에서 발견된 버그는 설계자에게 보고됩니다.

기존에는 엔지니어들이 재프로그래밍 가능한 하드웨어에 시뮬레이션 가속, 에뮬레이션 또는 프로토타이핑을 사용하여 설계를 완성하기 전에 SoC 설계를 위한 하드웨어 및 소프트웨어를 검증하고 디버깅했습니다.FPGA 프로토타입은 재프로그래밍이 가능하고 디버깅이 가능하며 애플리케이션별 집적회로(ASIC)[18][19]보다 유연하기 때문에 필드프로그래머블 게이트 어레이(FPGA)는 SoC 프로토타이핑에 적합합니다.

시뮬레이션 가속 및 에뮬레이션은 대용량과 빠른 컴파일 시간으로 시스템에 대한 광범위한 가시성을 제공하는 강력한 기술입니다.그러나 두 테크놀로지 모두 SoC의 동작 주파수보다 훨씬 느릴 수 있으며, 최대 100배 느릴 수 있습니다.액셀러레이션 및 에뮬레이션 박스도 매우 크고 100만 [citation needed]달러가 넘는 고가입니다.

반대로 FPGA 프로토타입은 FPGA를 직접 사용하여 엔지니어가 실제 자극으로 시스템의 전체 작동 주파수 또는 그에 근접한 주파수를 검증하고 테스트할 수 있도록 한다.Certus와[20] 같은 도구는 신호를 관찰에 사용할 수 있도록 하는 프로브를 FPGA RTL에 삽입하는 데 사용됩니다.이것은 논리 분석기와 유사한 기능을 가진 여러 FPGA 간에 하드웨어, 펌웨어 및 소프트웨어 상호작용을 디버깅하기 위해 사용됩니다.

이와 병행하여 하드웨어 요소는 그룹화되어 논리합성의 프로세스를 통과하며, 이 과정에서 동작 주파수 및 예상 신호 지연 등의 성능 제약이 적용된다.이것에 의해, 설계를 물리 회선으로서 및 그 상호 접속으로서 기술하는 넷 리스트라고 불리는 출력이 생성됩니다.이들 넷리스트는 컴포넌트를 접속하는 글루 로직과 조합되어 칩에 인쇄할 수 있는 회로로서의 SoC의 개략적인 설명을 작성합니다.이 프로세스는 장소 및 경로라고 불리며 SoC가 Application-Specific Integrated Circuit(ASIC; 응용 프로그램 고유 집적회로)로 생성되는 경우 테이프 아웃보다 우선합니다.

최적화 목표

SoC는 전력 사용량, 다이 영역, 통신, 모듈러 유닛과 기타 요소 간의 인접성을 위해 위치 설정을 최적화해야 합니다.최적화는 반드시 SoC의 설계 목표입니다.최적화가 필요하지 않은 경우 엔지니어는 시스템의 영역 사용, 전력 소비 또는 성능을 동일한 정도로 고려하지 않고 멀티칩 모듈 아키텍처를 사용합니다.

다음으로 SoC 설계의 일반적인 최적화 타깃을 제시합니다.각각의 설명은 다음과 같습니다.일반적으로 이러한 양의 최적화는 어려운 조합 최적화 문제일 수 있으며, 실제로 NP-hard가 매우 쉽게 될 수 있습니다.따라서 종종 정교한 최적화 알고리즘이 필요하며 경우에 따라서는 근사 알고리즘이나 휴리스틱스를 사용하는 것이 실용적일 수 있습니다.또한 대부분의 SoC 설계에는 동시에 최적화할 수 있는 여러 변수가 포함되어 있기 때문에 SoC 설계에서는 Pareto의 효율적인 솔루션이 요구됩니다.대부분의 경우 이러한 수량을 최적화하는 목표는 직접적으로 상충되어 SoC의 설계 최적화를 더욱 복잡하게 만들고 시스템 설계에 트레이드오프를 도입합니다.

균형 및 요구사항 분석에 대한 광범위한 적용 범위는 요구사항 엔지니어링을 참조하십시오.

대상

소비전력

SoC는 SoC 기능을 수행하는 데 사용되는 전력을 최소화하도록 최적화되어 있습니다.대부분의 SoC는 저전력을 사용해야 합니다.SoC 시스템은 장시간 배터리 지속시간(스마트폰 등)을 필요로 하는 경우가 많아 자율기능을 유지해야 할 경우 전원 없이 수개월 또는 수년을 소비할 수 있습니다.또한 많은 수의 임베디드 SoC가 한 지역에서 네트워크에 연결되어 있기 때문에 전력 사용이 제한되는 경우가 많습니다.또, 에너지 코스트가 높을 가능성이 있어, 에너지 절약은 SoC의 총소유 코스트를 삭감합니다.마지막으로, 높은 에너지 소비로 인한 폐열은 너무 많은 열이 방산될 경우 다른 회로 구성 요소를 손상시킬 수 있으므로 에너지를 절약해야 하는 또 다른 실용적인 이유가 됩니다.회로에서 사용되는 에너지의 양은 시간에 대한 소비 전력의 적분이며, 평균 소비 전력 속도는 전류와 전압을 곱한 값입니다.마찬가지로 옴의 법칙에 따라 전력은 전류 제곱 저항 또는 전압 제곱을 저항으로 나눈 값입니다.

와트 성능

SoC는 와트당 퍼포먼스를 최대화할 수 있도록 최적화되어 있습니다.즉, 소비전력이 예산에 따라 SoC의 퍼포먼스를 최대화할 수 있습니다.엣지 컴퓨팅, 분산 처리, 환경 인텔리전스 등의 많은 애플리케이션은 일정 수준의 계산 퍼포먼스를 필요로 하지만 대부분의 SoC 환경에서는 전력이 제한됩니다.ARM 아키텍처는 임베디드 시스템의 x86보다 와트 성능이 우수하기 때문에 임베디드 프로세서를 필요로 하는 대부분의 SoC 애플리케이션에서는 x86보다 더 적합합니다.

폐열

SoC 설계는 칩의 폐열 출력을 최소화하도록 최적화되어 있습니다.다른 집적회로와 마찬가지로 높은 전력밀도로 인해 발생하는 열은 부품의 [21]: 1 소형화에 걸림돌이 됩니다.고속 집적회로, 특히 마이크로프로세서와 SoC를 포함한 전력 밀도는 매우 고르지 않게 되었습니다.폐열이 너무 많으면 회로가 손상되어 시간이 지남에 따라 회로의 신뢰성이 저하될 수 있습니다.고온 및 열응력은 신뢰성, 응력 이행, 평균 고장 간격 단축, 전자화, 와이어 본딩, 준안정성 및 [21]: 2–9 시간 경과에 따른 SoC의 성능 저하에 부정적인 영향을 미칩니다.

특히 대부분의 SoC는 물리적 영역 또는 부피가 작기 때문에 시스템 밖으로 확산될 여지가 거의 없기 때문에 폐열의 영향이 복합적입니다.현대 장치에서는 트랜지스터 수가 많기 때문에 충분한 throughput과 높은 트랜지스터 밀도의 레이아웃은 제작 공정에서 물리적으로 실현 가능하지만 회로 [21]: 1 부피에서 허용할 수 없을 정도로 많은 양의 열이 발생합니다.

이러한 열효과로 인해 SoC 및 기타 칩 설계자는 보수적인 설계 마진을 적용하게 되고, 치명적인 장애의 위험을 줄이기 위해 성능이 떨어지는 장치를 만들게 됩니다.길이 축척이 작아질수록 트랜지스터 밀도가 증가하기 때문에 각 공정에서 발생하는 열량이 지난번보다 많아집니다.이 문제를 더욱 복잡하게 만드는 것은 SoC 아키텍처가 일반적으로 이기종이기 때문에 공간적으로 불균일한 열 플럭스가 생성되기 때문에 균일한 수동 [21]: 1 냉각으로는 효과적으로 완화될 수 없다는 것입니다.

스루풋

SoC는 컴퓨팅 및 통신 스루풋을 최대화할 수 있도록 최적화되어 있습니다.

레이텐시

SoC는 일부 또는 모든 기능의 지연을 최소화하도록 최적화되어 있습니다.이는 상호접속 지연을 최소화하고 모듈, 기능 유닛 및 메모리 간에 데이터가 통신되는 속도를 최대화하기 위해 서로 적절한 근접성과 인접성을 가진 요소를 배치함으로써 달성할 수 있습니다.일반적으로 지연을 최소화하기 위해 최적화하는 것은 부울 만족도 문제와 동등한 NP-완전 문제입니다.

프로세서 코어로 실행되는 태스크의 경우 태스크 스케줄링을 통해 지연 및 throughput을 개선할 수 있습니다.그러나 일부 태스크는 응용 프로그램 고유의 하드웨어 유닛에서 실행되며 태스크 스케줄링으로도 타이밍 및 throughput 제약을 충족하기 위해 모든 소프트웨어 기반 태스크를 최적화하는 데 충분하지 않을 수 있습니다.

방법론

시스템 온 칩은 표준 하드웨어 검증 및 검증 기술을 사용하여 모델링되지만 SoC 설계 대안을 모델링 및 최적화하기 위해 추가 기술을 사용하여 상기 최적화 타깃에 대한 다중 기준 의사결정 분석과 관련하여 시스템을 최적화할 수 있습니다.

태스크 스케줄링

태스크 스케줄링은 하나의 프로세서 코어를 공유하는 여러 프로세스 또는 스레드를 가진 모든 컴퓨터 시스템에서 중요한 작업입니다.SoC의 ™ 프로세서 코어로 실행되는 임베디드 소프트웨어의 경우 ② 레이텐시를 줄이고 ③ 스루풋을 높이는 것이 중요합니다.SoC의 모든 중요한 컴퓨팅 액티비티가 온칩 프로세서에서 실행되는 소프트웨어에서 실행되는 것은 아니지만 스케줄링을 통해 소프트웨어 기반 태스크 및 공유 리소스를 포함하는 기타 태스크의 성능을 대폭 향상시킬 수 있습니다.

SoC는 종종 네트워크 스케줄링 및 랜덤 스케줄링 알고리즘에 따라 작업을 스케줄링합니다.

파이프라인

하드웨어 및 소프트웨어 태스크는 프로세서 설계에서 파이프라인으로 처리되는 경우가 많습니다.파이프라이닝은 컴퓨터 아키텍처의 속도 향상을 위한 중요한 원칙입니다.GPU(그래픽스 파이프라인) 및 RISC 프로세서(기존 RISC 파이프라인의 진화)에서 자주 사용되지만 SoC의 [12]맥락에서 디지털 신호 처리 및 멀티미디어 조작과 같은 애플리케이션 고유의 태스크에도 적용됩니다.

확률론적 모델링

SoC는 종종 확률론적 모델, 큐잉 이론, 큐잉 네트워크 및 마르코프 체인을 통해 분석됩니다.예를 들어 Little의 법칙을 통해 SoC 상태와 NoC 버퍼를 도착 프로세스로 모델링하고 포아송 랜덤 변수와 포아송 프로세스를 통해 분석할 수 있습니다.

마르코프 연쇄

SoC는 종종 마르코프 사슬, 이산 시간 및 연속 시간 변형을 사용하여 모델링됩니다.마르코프 연쇄 모델링은 전력, 열, 지연 및 기타 요인에 대한 SoC의 안정적인 상태 분포를 점근적으로 분석하여 일반적인 경우에 맞게 설계 결정을 최적화할 수 있도록 합니다.

제조

SoC 칩은 일반적으로 금속 산화물 반도체([22]MOS) 기술을 사용하여 제작됩니다.위에서 설명한 넷리스트는 설계자의 의도를 SoC 설계로 변환하기 위한 물리적 설계(장소 및 경로) 흐름의 기초로 사용됩니다.이 변환 프로세스 전체를 통해 정적 타이밍 모델링, 시뮬레이션 및 기타 도구를 사용하여 설계를 분석하여 주파수, 소비전력 및 소산, 기능 무결성(레지스터 전송 레벨 코드에 기재된 바와 같이) 및 전기적 무결성 등의 특정 동작 파라미터를 충족하는지 확인합니다.

알려진 모든 버그가 수정되고 이러한 버그가 다시 검증되고 모든 물리적 설계 점검이 완료되면 칩의 각 층을 설명하는 물리적 설계 파일이 주조 공장의 마스크 상점으로 전송되며, 여기에서 전체 유리 리소그래피 마스크 세트가 에칭됩니다.이것들은 포장 및 테스트 전에 SoC 주사위를 만들기 위해 웨이퍼 제조 공장으로 보내집니다.

SoC는 다음과 같은 몇 가지 테크놀로지로 제작할 수 있습니다.

ASIC는 FPGA보다 소비전력이 적고 속도가 빠르지만 재프로그래밍이 불가능하여 제조비용이 많이 듭니다.FPGA 설계는 저볼륨 설계에 더 적합하지만 충분한 생산 유닛을 갖춘 후 ASIC를 사용하면 [23]총소유비용을 절감할 수 있습니다.

SoC 설계는 교체되는 멀티칩 시스템에 비해 전력 소비량이 적고 비용 및 신뢰성이 높습니다.시스템의 패키지 수가 줄어들면 조립 비용도 절감됩니다.

그러나 대부분의 대규모 집적회로(VLSI) 설계와 마찬가지로 수율이 낮고[clarification needed] 반복되지 않는 엔지니어링 비용이 높기 때문에 하나의 대형 칩이 여러 개의 소형 칩에 분산된 동일한 기능보다 총 비용이 높습니다[clarification needed].

특정 애플리케이션에 대해 SoC를 구축할 수 없는 경우, 하나의 패키지에 다수의 칩을 포함하는 시스템 인 패키지(SiP)를 대신 사용할 수 있습니다.SoC는 대량 생산 시 패키징이 [24]간단해 SiP보다 비용 효율이 높다.SiP가 바람직한 또 다른 이유는 기능 구성요소가 서로 너무 가깝기 때문에 SoC에서 폐열이 너무 높을 수 있으며, SiP에서는 물리적으로 떨어져 있기 때문에 다른 기능 모듈에서 더 잘 방산될 수 있기 때문입니다.

벤치마크

SoC의 연구 및 개발은 많은 옵션을 비교합니다.COSMIC과 [25]같은 벤치마크는 이러한 평가에 도움이 되도록 개발되었습니다.

「 」를 참조해 주세요.

- 시스템 온 어 칩 공급업체 목록

- 실리콘 검증 후

- ARM 아키텍처

- 싱글보드 컴퓨터

- 패키지 내 시스템

- 칩상의 네트워크

- 프로그램 가능한 SoC

- 응용 프로그램 고유 명령 집합 프로세서(ASIP)

- 플랫폼 기반 설계

- 랩 온 칩

- 바이오메디컬 테크놀로지의 칩을 이용한 장기

- 멀티칩 모듈

메모들

- ^ 이 문서에서는 SoC가 /'so'si'/es-oh-SEE'로 발음되는 규칙을 사용합니다.따라서 SoC(SoC)에 대응하는 부정 기사에 대해 "an"이라는 규칙을 사용합니다.다른 소스에서는 /skk/sock으로 발음할 수 있으므로 "a SoC"를 사용합니다.

- ^ 이 중앙 보드는 "자녀" 구성 요소 카드를 호스팅하기 위한 "마더 보드"라고 불립니다.

- ^ 그래픽스 커넥션(PCI Express)과 RAM은 메인보드 기반 디스크리트 아키텍처의 노스브리지였습니다.

- ^ 하드 디스크와 USB의 접속은 지금까지 메인보드 기반의 개별 모듈러 아키텍처의 사우스브리지의 일부였습니다.

- ^ 임베디드 시스템에서 "쉴드"는 PC용 확장 카드와 유사합니다.Arduino와 같은 마이크로 컨트롤러나 Rasberry Pi와 같은 싱글 보드 컴퓨터에 적합하며 장치의 주변기기로 기능합니다.

레퍼런스

- ^ Shah, Agam (January 3, 2017). "7 dazzling smartphone improvements with Qualcomm's Snapdragon 835 chip". Network World.

- ^ "Qualcomm's Snapdragon X60 promises smaller 5G modems in 2021 – Ars Technica".

- ^ 피트 베넷, EE 타임즈입니다."저전력 SoC 설계의 이유, 장소 및 내용"2004년 12월 2일2015년 7월 28일 취득.

- ^ Nolan, Stephen M. "Power Management for Internet of Things (IoT) System on a Chip (SoC) Development". Design And Reuse. Retrieved September 25, 2018.

- ^ "Is a single-chip SOC processor right for your embedded project?". Embedded. Retrieved October 13, 2018.

- ^ "Qualcomm launches SoCs for embedded vision Imaging and Machine Vision Europe". www.imveurope.com. Retrieved October 13, 2018.

- ^ "Samsung Galaxy S10 and S10e Teardown". iFixit. March 6, 2019.

- ^ a b "ARM is going after Intel with new chip roadmap through 2020". Windows Central. Retrieved October 6, 2018.

- ^ a b "Always Connected PCs, Extended Battery Life 4G LTE Laptops Windows". www.microsoft.com. Retrieved October 6, 2018.

- ^ "Gigabit Class LTE, 4G LTE and 5G Cellular Modems Qualcomm". Qualcomm. Retrieved October 13, 2018.

- ^ a b c Furber, Stephen B. (2000). ARM system-on-chip architecture. Harlow, England: Addison-Wesley. ISBN 0201675196. OCLC 44267964.

- ^ a b c d e Haris Javaid, Sri Parameswaran (2014). Pipelined Multiprocessor System-on-Chip for Multimedia. Springer. ISBN 9783319011134. OCLC 869378184.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ a b c d e f g h Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. ISBN 9781466565272. OCLC 895661009.

- ^ "Best Practices for FPGA Prototyping of MATLAB and Simulink Algorithms". EEJournal. August 25, 2011. Retrieved October 8, 2018.

- ^ Bowyer, Bryan (February 5, 2005). "The 'why' and 'what' of algorithmic synthesis". EE Times. Retrieved October 8, 2018.

- ^ EE 타임즈"검증이 정말 70%입니까?2004년 6월 14일.2015년 7월 28일 취득.

- ^ "Difference between Verification and Validation". Software Testing Class. August 26, 2013. Retrieved April 30, 2018.

In interviews most of the interviewers are asking questions on “What is Difference between Verification and Validation?” Many people use verification and validation interchangeably but both have different meanings.

- ^ Rittman, Danny (January 5, 2006). "Nanometer prototyping" (PDF). Tayden Design. Retrieved October 7, 2018.

- ^ "FPGA Prototyping to Structured ASIC Production to Reduce Cost, Risk & TTM". Design And Reuse. Retrieved October 7, 2018.

- ^ EE 타임즈 브라이언 베일리입니다"Tektronix는 ASIC 프로토타이핑을 혁신하기를 희망합니다."2012년 10월 30일2015년 7월 28일 취득.

- ^ a b c d Ogrenci-Memik, Seda (2015). Heat Management in Integrated circuits: On-chip and system-level monitoring and cooling. London, United Kingdom: The Institution of Engineering and Technology. ISBN 9781849199353. OCLC 934678500.

- ^ Lin, Youn-Long Steve (2007). Essential Issues in SOC Design: Designing Complex Systems-on-Chip. Springer Science & Business Media. p. 176. ISBN 9781402053528.

- ^ "FPGA vs ASIC: Differences between them and which one to use? – Numato Lab Help Center". numato.com. Retrieved October 17, 2018.

- ^ EE 타임즈"대토론: SOC vs. SIP." 2005년 3월 21일.2015년 7월 28일 취득.

- ^ "COSMIC". www.ece.ust.hk. Retrieved October 8, 2018.

추가 정보

- Badawy, Wael; Jullien, Graham A., eds. (2003). System-on-Chip for Real-Time Applications. Kluwer international series in engineering and computer science, SECS 711. Boston: Kluwer Academic Publishers. ISBN 9781402072543. OCLC 50478525. 465페이지.

- Furber, Stephen B. (2000). ARM system-on-chip architecture. Boston: Addison-Wesley. ISBN 0-201-67519-6.

- Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. ISBN 9781466565272. OCLC 895661009.