시린스 비바도

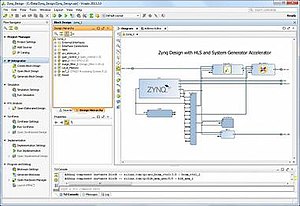

Xilinx Vivado Xilinx Vivado Design Suite 2014.2 블록 디자인 패널(가운데) 및 프로젝트 탐색 트리(왼쪽) | |

| 개발자 | 시린스 |

|---|---|

| 초기 릴리즈 | 2012년 4월, 전([1] |

| 안정된 릴리스 | |

| 기입처 | C++ |

| 운영 체제 | Microsoft Windows, Linux |

| 이용가능기간: | 영어 |

| 유형 | EDA |

| 면허증. | WebPACK Edition: 일부 (소형) 디바이스에는[4] 비용이 들지 않습니다. 기타 에디션: 상업용 |

| 웹 사이트 | https://www.xilinx.com/products/design-tools/vivado.html |

Vivado Design Suite는 하드웨어 기술 언어(HDL) 설계의 합성 및 분석을 위해 Xilinx에서 제작한 소프트웨어 제품군으로, Xilinx ISE를 칩 개발 및 고급 [1][5][6][7]합성 시스템에 대한 추가 기능으로 대체합니다.Vivado는 [8][9][10](ISE와 비교하여) 설계 흐름 전체를 처음부터 다시 쓰고 다시 생각하는 것을 의미합니다.

ISE의 최신 버전과 마찬가지로 Vivado는 로직 [11]시뮬레이터를 내장하고 있습니다.Vivado는 또한 C 코드를 프로그래밍 가능한 [6]로직으로 변환하는 툴 체인과 함께 높은 수준의 합성을 도입했습니다.

15년 된 ISE를 Vivado Design Suite로 교체하는 데 1000명이 걸렸고 2억 [12]달러의 비용이 들었습니다.

특징들

Vivado는 2012년 [1]4월에 소개되었으며, 확장 가능한 공유 데이터 모델과 공통 디버깅 환경을 기반으로 구축된 시스템-IC 레벨 툴을 갖춘 통합 설계 환경(IDE)입니다.Vivado에는 C 기반 알고리즘 IP의 합성 및 검증을 위한 ESL(전자 시스템 레벨), 재사용을 위한 알고리즘 및 RTL IP의 표준 기반 패키징, 표준 기반 IP 스티칭 및 모든 유형의 시스템 구성 블록의 시스템 통합, 블록 및 [13]시스템 검증이 포함됩니다.Vivado의 무료 버전 WebPACK Edition은 디자이너들에게 제한된 버전의 디자인 [14]환경을 제공합니다.

구성 요소들

Vivado High-Level Synthesis 컴파일러를 사용하면 C, C++ 및 SystemC 프로그램을 [15][16][17]Xilinx 디바이스로 직접 전송할 수 있습니다.Vivado HLS는 개발자 생산성을 높이기 위해 널리 검토되고 있으며 C++ 클래스, 템플릿, 함수 및 오퍼레이터 [18][16]오버로드를 지원하는 것으로 확인되었습니다.Vivado 2014.1은 Xilinx [19][16]디바이스용 OpenCL 커널을 IP로 자동 변환하는 지원을 도입했습니다.OpenCL 커널은 다양한 CPU,[16][19] GPU 및 FPGA 플랫폼에서 실행되는 프로그램입니다.

Vivado Simulator는 Vivado Design Suite의 구성요소입니다.이는 혼합 언어, TCL 스크립트, 암호화된 IP 및 향상된 검증을 지원하는 컴파일 언어 시뮬레이터입니다.

Vivado IP Integrator를 사용하면 엔지니어는 대규모 Xilinx IP 라이브러리에서 IP를 신속하게 통합하고 구성할 수 있습니다.Integrator는 또한 Xilinx의 System Generator와 Vivado High-Level [20]Synthesis로 구축된 MathWorks Simulink 설계에 맞게 조정되었습니다.

Vivado Tcl Store는 Vivado에 대한 추가 기능을 개발하기 위한 스크립트 시스템이며 Vivado의 기능을 [19]추가 및 수정하는 데 사용할 수 있습니다.TCL은 Vivado 자체의 [19]기반이 되는 스크립트 언어입니다.Vivado의 모든 기본 기능은 TCL [19]스크립트를 통해 호출 및 제어할 수 있습니다.

디바이스 지원

Vivado는 Xilinx의 7시리즈와 모든 새로운 디바이스(UltraScale 및 UltraScale+시리즈)[3]를 지원합니다.오래된 Xilinx의 디바이스와 CPLD를 대상으로 한 개발에는 이미 단종된 Xilinx ISE를 사용해야 합니다.

「 」를 참조해 주세요.

레퍼런스

- ^ a b c "Xilinx Inc, Form 8-K, Current Report, Filing Date Apr 25, 2012". secdatabase.com. Retrieved May 6, 2018.

- ^ Vivado 2022.1 릴리즈, Xilinx

- ^ a b Vivado Design Suite 사용자 가이드: 릴리즈 노트, 설치 및 라이선스 (UG973) (v2022.1), 2022년 4월 26일 Xilinx

- ^ "Vivado Design Suite Evaluation and WebPACK". Xilinx. n.d. Retrieved October 4, 2020.

- ^ Morris, Kevi (2014-11-18). "FPGAs Cool Off the Datacenter, Xilinx Heats Up the Race". Electronic Engineering Journal.

- ^ a b "Xilinx and its Ecosystem Demonstrate All Programmable and Smarter Vision Solutions at ISE 2015". SAN JOSE. 2015-02-04.

- ^ "Xilinx Vivado Design Suite Now Available in WebPACK Edition". SAN JOSE: Design & Reuse. 2012-12-19.

- ^ Morris, Kevin (2014-02-25). "Xilinx vs. Altera, Calling the Action in the Greatest Semiconductor Rivalry". Electronic Engineering Journal.

- ^ Vivado Design Suite, Xilinx 웹사이트

- ^ Vivado Design Suite, 2012년 첫 버전 출시, Xilinx 다운로드

- ^ Xilinx, Inc. (November 17, 2021). Vivado Design Suite User Guide: Design Flows Overview (PDF) (Technical report). p. 49. UG892.

The Vivado simulator, integrated into the Vivado IDE, allows you to simulate the design, add and view signals in the waveform viewer, and examine and debug the design as needed.

- ^ Joselyn, Louise (2013-12-10). "The road to success is long and hard for eda start ups". New Electronics.

- ^ EDN. "Vivado Design Suite는 프로그래밍 가능한 시스템 통합 및 구현을 최대 4배 고속화합니다." 2012년 6월 15일2013년 6월 25일 취득.

- ^ 클라이브 맥스필드, EE 타임즈입니다."Xilinx Vivado Design Suite의 WebPACK 에디션을 이용할 수 있게 되었습니다."2012년 12월 20일2013년 6월 25일 취득.

- ^ Xilinx는 Vivado Design Suite 2014.3, SDK 및 새로운 UltraFast Embedded Design Methodology Guide, SAN JOSE, 2014년 10월 8일 설계 및 재사용을 통해 Zynq-7000 All Programmable SoC의 생산성을 향상시킵니다.

- ^ a b c d "Vivado Design Suite 2014.1 Increases Productivity with Automation of UltraFast Design Methodology and OpenCL Hardware Acceleration". SAN JOSE: Market Watch. 2014-04-16.

- ^ Maxfield, Clive (2013-07-26). "Free High-Level Synthesis Guide for S/W Engineers". EE Times.

- ^ Wilson, Richard (2014-05-27). "How to make slow software run quicker". Electronics Weekly.

- ^ a b c d e Morris, Kevin (2014-05-06). "Viva Vivado!, Xilinx Tunes-Up Tools". Electronic Engineering Journal.

- ^ Wilson, Richard (2013-09-11). "Xilinx, MathWorks and National Instruments work on high-level FPGA design". Electronics Weekly.