사우스브리지(컴퓨팅)

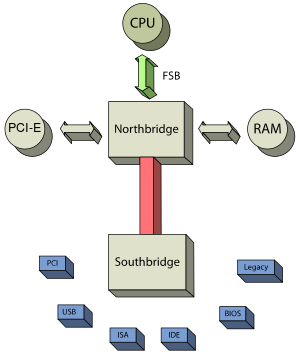

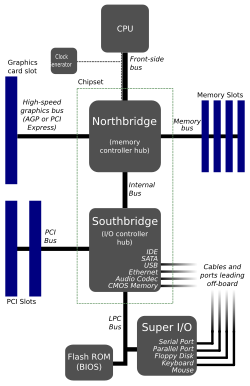

Southbridge (computing)사우스 브릿지는 PC 메인보드의 코어 로직 칩셋의 2개의 칩 중 하나이며, 다른 하나는 노스 브릿지입니다.사우스 브릿지는 일반적으로 노스 브릿지/사우스 브릿지 칩셋 컴퓨터 아키텍처에서 메인보드의 느린 기능을 구현합니다.인텔 칩셋을 탑재한 시스템에서는 사우스브릿지는 I/O Controller Hub(ICH; I/O컨트롤러 허브)로 명명됩니다.AMD는 Fusion AMD Accelerated Processing Unit(APU)를 도입한 이후 사우스브릿지의 기능을 CPU 다이허브에 탑재하고 있기 때문에 Northbridge의 기능도 같은 기능을 합니다.ler.

사우스 브릿지는 보통 CPU에 직접 접속되어 있지 않기 때문에 노스 브릿지와 노스 브릿지를 구별할 수 있습니다.대신 노스 브릿지는 사우스 브릿지를 CPU에 연결합니다.컨트롤러 내장 채널 회로를 사용하여 노스브릿지는 I/O 유닛에서 CPU로 직접 신호를 링크하여 데이터 제어 및 액세스를 할 수 있습니다.

현황

시스템온칩(SoC) 프로세서의 보급으로 최신 디바이스는 Northbridge를 CPU 다이 [further explanation needed]자체에 내장하고 있습니다.예를 들어 인텔의 Sandy[1] Bridge와 AMD의 Fusion [2]프로세서는 모두 2011년에 출시되었습니다.이 사우스 브릿지는 용장성이 되어 2008년에 인텔 5 시리즈 칩셋에 도입된 플랫폼 컨트롤러 허브(PCH) 아키텍처로 대체되었습니다.AMD는 2011년에 첫 APU를 출시하면서 PCH를 Fusion 컨트롤러 허브(FCH)라고 명명했습니다.이것은 2017년까지 AMD의 APU에서만 사용되었습니다.FCH 이름을 삭제하면서 Zen 아키텍처로 이동합니다.인텔 플랫폼에서는 모든 사우스브리지 기능과 나머지 I/O 기능은 PCH에 의해 관리되며 PCH는 Direct Media Interface(DMI;[3] 다이렉트 미디어 인터페이스)를 통해 CPU에 직접 연결됩니다.인텔의 저전력 프로세서(Haswell-U 이후)와 초저전력 프로세서(Haswell-Y 이후)도 온패키지 PCH를 통합했습니다.AMD Ryzen 프로세서는 칩렛 설계를 기반으로 USB 인터페이스와 SATA/NVMe 인터페이스 [4]등 사우스브리지 기능도 통합했습니다.

개요

사우스브리지 칩셋은 USB, 오디오, 시스템 BIOS, ISA 버스 또는 LPC 버스, 저속 PCI/PCIe 버스, IOAPIC 인터럽트 컨트롤러, SATA 스토리지,[5][6] 이력 PATA 스토리지 및 NVMe 스토리지와 같은 컴퓨터의 I/O 기능을 대부분 처리했습니다.Southbridge 칩과 Northbridge 칩의 다른 조합이 [7]가능하지만 이들 2종류의 칩은 함께 [8][9]동작하도록 설계되어야 합니다.다른 코어 로직 칩셋 설계 간의 상호 운용성에 관한 업계 전체의 표준은 없습니다.1990년대와 2000년대 초반에는 노스브리지와 사우스브리지 사이의 인터페이스가 PCI 버스였습니다.현재 사용되는 주요 브리징인터페이스는 DMI(Intel)와 UMI(AMD)입니다.

어원

이 이름은 맵의 방식으로 아키텍처를 나타내는 것에서 유래되었으며 1991년 PCI 로컬 버스 아키텍처가 소개되면서 처음 설명되었습니다.인텔에서는 PCI 사양의 저자가 PCI 로컬 버스를 PC 플랫폼 아키텍처(적도)의 가장 중심에 두고 있다고 생각했습니다.

노스브릿지는 CPU, 메모리/캐시 및 기타 퍼포먼스에 중요한 기능을 지원하기 위해 PCI 버스백본의 북쪽까지 확장됩니다.마찬가지로 사우스 브릿지는 PCI 버스 백본의 남쪽까지 확장되어 디스크 인터페이스, 오디오 등의 성능에 그다지 중요하지 않은 I/O 기능에 브리지합니다.

CPU는 지도 맨 위에 정북쪽에 있습니다.CPU는 그림과 같이 다른 시스템 디바이스의 북쪽에 있는 고속 브리지(노스 브리지)를 통해 칩셋에 접속되어 있습니다.노스 브릿지는 그림과 같이 다른 시스템 디바이스의 남쪽에 있는 저속 브리지(사우스 브릿지)를 통해 칩셋의 나머지 부분에 연결됩니다.

현재의 PC 플랫폼 아키텍처는 PCI 버스 백본을 고속 I/O 백본으로 대체했지만 브리지 명명 규칙은 그대로입니다.

기능

현대의 사우스브리지에는 다음과 같은 기능이 있습니다.[9][6]

- PCI 버스사우스 브릿지는 PCI-X 지원도 포함할 수 있습니다.

- 보통 이더넷 및 NVMe용 저속 PCI Express(PCIe) 인터페이스.

- ISA 버스 또는 LPC 브리지ISA 슬롯은 최신 메인보드에서 제공되지 않게 되었습니다.LPC 브릿지는 슈퍼 I/O(PS/2 키보드와 마우스, 패럴렐 포트, 시리얼 포트, IR 포트 및 플로피 컨트롤러의 일반 연결)로의 데이터 및 제어 경로를 제공합니다.

- SPI 버스SPI 버스는 주로 펌웨어(BIOS/UEFI 등) 플래시 스토리지 액세스에 사용되는 심플한 시리얼 버스입니다.

- SMBus 컨트롤러

- DMA 컨트롤러8237 DMA 컨트롤러를 사용하면 CPU의 도움 없이 ISA 또는 LPC 디바이스가 메인 메모리에 직접 액세스할 수 있습니다.

- PIC 및 I/O APIC

- SATA, M.2 및 이력 PATA 등의 대용량 스토리지 인터페이스.일반적으로 하드 드라이브 또는 SSD를 연결할 수 있습니다.

- 실시간 클럭

- 프로그램 가능한 인터벌타이머

- 고정밀 이벤트 타이머

- ACPI 컨트롤러 또는 APM 컨트롤러

- 비휘발성 BIOS 메모리시스템 CMOS(BIOS 구성 메모리)는 배터리 보조 전원으로 BIOS 구성 데이터용으로 제한된 비휘발성 스토리지 영역을 만듭니다.

- 인텔 HD 오디오 또는 AC'97 사운드 인터페이스.

- USB 인터페이스

옵션으로 사우스브리지에는 이더넷, Wi-Fi, RAID, Thunderbolt 및 대역 외 관리 지원(온보드 전용 칩 또는 사우스브리지 내장)도 포함되어 있습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ Vatto, Kristian. "Why Ivy Bridge is still Quad-core?". Anandtech. Retrieved September 27, 2015.

- ^ Stokes, Jon. "With Fusion, AMD's devils are in the details". Arstechnica. Retrieved September 27, 2015.

- ^ "Mobile Intel HM57 Express Chipset". Intel. Retrieved 2014-04-21.

- ^ Hagedoorn, Hilbert. "AMD Ryzen 3000: New Block diagram about PCIe 4.0 on Matisse and X570 chipset". Guru3D.com. Retrieved 2020-06-12.

- ^ 를 클릭합니다"What is Southbridge?", Webopedia Computer Dictionary (word definition).

- ^ a b Mujtaba, Hassan (2019-09-13). "Intel Z490, H470 Motherboards For 10th Gen Comet Lake-S CPUs Leaked". Wccftech. Retrieved 2020-10-30.

- ^ 를 클릭합니다Chipset: Northbridge and Southbridge, Rigacci.

- ^ 를 클릭합니다What is northbridge, southbridge, how northbridge, southbridge works, Edu soft max.

- ^ a b 를 클릭합니다What is a chipset?, UK: Misco.

외부 링크

- "Motherboards & Core-Logic Chipsets: The Deep Stuff > What the North Bridge and South Bridge Do". InformIT. Retrieved November 18, 2010.