EEPROM

EEPROM| 컴퓨터 메모리 및 데이터 스토리지 유형 |

|---|

| 휘발성 |

| 비휘발성 |

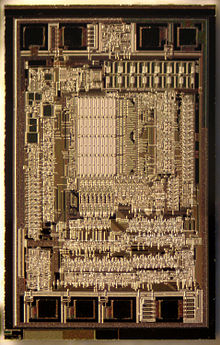

EEPROM(이라고도 불리는 E2PROM)전기적 소거형 프로그램 가능 판독 전용 기억 장치와 비 휘발성 메모리의 컴퓨터에 사용되는 스마트 카드 및 원격 키일 리스 시스템 그리고 기타 전자 장치와 reprogramme 지워질 개별 바이트를 허용함으로써 데이터는 비교적 소량의 축적하기 위해 이런으로 통합되어 서 있다.d.

EEPROM은 플로팅 게이트 트랜지스터 어레이로 구성됩니다.EEPROM은 특별한 프로그래밍 신호를 적용하여 회로 내에서 프로그래밍 및 소거할 수 있습니다.원래 EEPROM은 싱글바이트 조작으로 제한되어 있었기 때문에 속도가 느려졌지만 최신 EEPROM에서는 멀티바이트 페이지 조작이 가능합니다.EEPROM의 소거 및 재프로그래밍 수명은 제한되어 있으며, 현재 최신 EEPROM에서는 백만 번의 동작에 도달하고 있습니다.재프로그래밍이 빈번한 EEPROM에서는 EEPROM의 수명이 중요한 설계상의 고려 사항입니다.

플래시 메모리는 고속 및 고밀도를 위해 설계된EEPROM의 일종으로, 대량의 소거 블록(일반적으로 512바이트 이상)과 한정된 수의 쓰기 사이클(종종 10,000)을 희생합니다.둘을 구분하는 명확한 경계는 없지만 "EEPROM"이라는 용어는 일반적으로 소거 블록(1바이트만큼 작음)과 긴 수명(일반적으로 1,000,000 사이클)을 가진 비휘발성 메모리를 설명하는 데 사용됩니다.많은 마이크로컨트롤러에는 펌웨어용 플래시 메모리와 파라미터용 소형 EEPROM이 있습니다.

2020년 현재 플래시 메모리는 바이트 프로그래밍이 가능한 EEPROM보다 훨씬 저렴하며, 시스템에서 상당한 양의 비휘발성 솔리드 스테이트 스토리지가 필요한 메모리 유형입니다.그러나 EEPROM은 시리얼 존재 [1][2]검출과 같이 적은 양의 스토리지만 필요로 하는 애플리케이션에서는 여전히 사용됩니다.

역사

1970년대 초에는 다양한 기업 및 조직이 전기적으로 재프로그래밍 가능한 비휘발성 메모리에 대한 연구, 발명 및 개발을 수행했습니다.1971년, 최초의 연구 보고서는 일본 국립 [3]연구소인 전기 기술 연구소의 타루이 야스오, 하야시 유타카, 나가이 키요코에 의해 일본 도쿄에서 열린 제3회 솔리드 스테이트 소자 회의에서 발표되었습니다.그들은 1972년에 [4]EEPROM 장치를 제작하여 [5]이 연구를 10년 이상 계속하였다.이 논문들은 이후의 논문들과 [6][7]특허들에 의해 반복적으로 인용되고 있다.

연구 중 하나는 싱글칩 마이크로컨트롤러에 [9][10][11]내장된 르네사스 전자의 플래시 메모리를 이용한 금속산화질소반도체([8]MONOS) 기술이다.

1972년, [12]플래시 메모리의 발명가로도 알려진 도시바의 후지오 마스오카에 의해 전기적으로 재프로그래밍 가능한 비휘발성 메모리가 발명되었다.Toshiba,[12][6]산요 등 주요 반도체 제조 업체의 대부분의(나중에, 르네사스 테크놀로지)[17]IBM,[14]Intel,[15][16]NEC(나중에, ON세미 컨덕터)[13]필립스(나중에, NXP Semiconductors)[18]지멘스(나중에, 인피니온 테크놀로지스)[19]허니웰(나중에, 아트 멜)[20]텍사스 Instruments,[21]열심히 공부했고, 발명하며, 제작된 일부 el.ectrically성이 드re-programmable1977년까지의 악습.

이러한 장치의 이론적 기초는 Abranche 핫 캐리어 주입입니다.그러나 일반적으로 1970년대 초 EPROM을 비롯한 프로그래밍 가능한 메모리는 데이터 보존 기간, 지우기/쓰기 주기 [22]수 등 신뢰성과 내구성에 문제가 있었습니다.

1975년, NEC의 반도체 사업부(현재의 르네사스 전자)는 일본 특허청에 [23][24]상표명 EEPROM®을 적용했다.1978년에 이 상표권은 일본에서 제1,342,184호로 부여되어 등록되었으며, 2018년 3월 현재도 존속하고 있다.

1977년 2월 Hughes Aircraft Company의 Eliyahou Harari는 플로팅 게이트와 웨이퍼 사이의 얇은 이산화 규소 층을 통해 Fowler-Nordheim 터널을 사용하여 새로운 EEPROM 기술을 발명했습니다.Hughes는 이 새로운 EEPROM [25]장치를 생산했습니다.그러나[26] 이 특허는 NEC의 EEPROM® [17]발명을 인용했습니다.

1977년 5월 Fairchild와 Siemens에 의해 몇 가지 중요한 연구 결과가 공개되었다.파울러-노르하임 터널링 열간 캐리어 [27][28]인젝션에는 이산화규소 두께가 30Ω 미만인 SONOS(폴리실리콘-옥시질화질화질화실리콘) 구조와 SIMOS(스택드게이트 인젝션 MOS) 구조를 각각 사용했다.

1976년부터 1978년까지 George Perlegos를 포함한 인텔 팀은 이 터널링2 EPROM [29][30]테크놀로지를 개선하기 위해 몇 가지 발명을 했습니다.1978년, 그들은 얇은 이산화규소 층을 가진 16K(2K 워드×8) 비트 Intel 2816 칩을 개발했습니다.이 칩은 200Ω [31]미만이었습니다.1980년에 이 구조는 플로팅 게이트 터널 산화물인 플로팅 게이트(FLOTOX)[32]로 공개적으로 도입되었다.FLOTOX 구조는 바이트당 지우기/쓰기 사이클의 신뢰성을 최대 10,000배 [33]향상시켰습니다.그러나 이 장치는 5V 읽기 작업을 [34]: 5–86 제외하고 바이트 지우기를 위해 20-22VPP 바이어스 전압을 추가로 공급해야 했습니다.1981년 Perlegos와 다른 2명의 멤버가 인텔을 떠나 Seeq [35]Technology를 설립했습니다.Seeq Technology는 EPROM 프로그래밍에2 필요한 고전압을 공급하기 위해 장치 내 충전 펌프를 사용했습니다.Perlogos는 1984년 Seeq Technology를 떠나 Atmel에 [36][37]설립되었습니다.

FLOTOX 구조의 이론적 근거

이전 섹션에서 설명한 바와 같이 오래된 EEPROM은 높은 역파괴 전압을 가진 눈사태 파괴 기반의 열반송파 주입을 기반으로 합니다.그러나 FLOTOX의 이론적 근거는 플로팅 게이트와 웨이퍼 사이의 얇은 이산화규소 층을 통한 Fowler-Nordheim 터널링 핫 캐리어 주입입니다.즉, 터널 [38]접점을 사용합니다.

물리적 현상 자체의 이론적 근거는 오늘날의 플래시 메모리와 동일합니다.그러나 플로팅 게이트 자체가 하나의 데이터 [39]비트를 프로그래밍하고 삭제하기 때문에 각 FLOTOX 구조는 다른 읽기 제어 트랜지스터와 연계되어 있습니다.

인텔의 FLOTOX 디바이스 구조는 EEPROM의 신뢰성, 즉 쓰기/삭제 사이클의 내구성과 데이터 보유 기간을 향상시켰습니다.FLOTOX에 대한 단일 사건 효과에 대한 연구 자료를 이용할 [40]수 있다.

오늘날 FLOTOX 장치 구조에 대한 자세한 학술적 설명은 다양한 [41][42][43]자료에서 찾을 수 있습니다.

오늘날의 EEPROM 구조

현재 EEPROM은 표준 EEPROM 제품뿐만 아니라 임베디드 마이크로 컨트롤러에도 사용되고 있습니다.EEPROM에서는 메모리 내의 전용 바이트를 지우려면 비트당 2개의 트랜지스터 구조가 필요하며 플래시 메모리에는 메모리 [44]: 245, PDF:2 영역을 지우려면 비트당 1개의 트랜지스터가 있습니다.

보안 보호

EEPROM 테크놀로지는 신용 카드, SIM 카드, 키리스 엔트리 등 일부 보안 가젯에 사용되므로 [44][45]복사 방지 등의 보안 보호 메커니즘이 있는 디바이스도 있습니다.

전기 인터페이스

EEPROM 디바이스는 데이터 입출력에 시리얼 또는 패럴렐인터페이스를 사용합니다.

시리얼 버스 디바이스

일반적인 시리얼 인터페이스는 SPI, I²C, 마이크로파, UNI/O 및 1-와이어입니다.1 ~ 4개의 디바이스 핀을 사용하여 8핀 이하의 패키지를 사용할 수 있습니다.

일반적인 EEPROM 시리얼 프로토콜은 OP 코드 단계, 주소 단계 및 데이터 단계의 3가지 단계로 구성됩니다.OP 코드는 보통 EEPROM 장치의 시리얼 입력 핀에 처음 8비트를 입력(또는 대부분의 I²C 장치에서는 암묵적)한 후 장치의 깊이에 따라 8~24비트의 어드레싱을 수행한 후 읽기 또는 쓰기 데이터를 입력합니다.

일반적으로 각 EEPROM 디바이스에는 다른 기능에 매핑된 자체 OP 코드 명령 세트가 있습니다.SPI EEPROM 디바이스에서의 일반적인 조작은 다음과 같습니다.

- 쓰기 활성화(WRENAL)

- 쓰기 비활성화(WRDI)

- 읽기 상태 레지스터(RDSR)

- WRSR(Write Status Register(WSR)

- 데이터 읽기(READ)

- 데이터 쓰기(WRITE)

일부 EEPROM 디바이스에서 지원되는 기타 조작은 다음과 같습니다.

- 프로그램.

- 섹터 지우기

- 칩 삭제 명령어

병렬 버스 장치

병렬 EEPROM 디바이스에는 일반적으로 8비트 데이터 버스와 메모리 전체를 커버하기에 충분한 폭의 주소 버스가 있습니다.대부분의 디바이스에는 칩 선택 핀과 쓰기 보호 핀이 있습니다.일부 마이크로 컨트롤러에는 통합 병렬 EEPROM도 있습니다.

병렬 EEPROM 의 동작은 시리얼 EEPROM 에 비해 간단하고 고속이지만, 이러한 디바이스는 핀 수가 많아(28핀 이상) 시리얼 EEPROM 또는 플래시에 비해 인기가 떨어지고 있습니다.

기타 디바이스

EEPROM 메모리는 엄밀하게는 메모리 제품이 아닌 다른 유형의 제품에서 기능을 활성화하기 위해 사용됩니다.실시간 클럭, 디지털 전위차계, 디지털 온도 센서 등의 제품에는 소량의 EEPROM이 탑재되어 있어 교정 정보나 정전 시 사용할 수 있는 기타 데이터를 저장할 수 있습니다.또한 외장 및 내장 플래시 메모리를 사용하기 전에 게임 진행 및 구성을 저장하기 위해 비디오 게임 카트리지에 사용되었습니다.

장애 모드

저장된 정보에는 내구성과 데이터 보유라는 두 가지 제한이 있습니다.

개서 중에 플로팅 게이트 트랜지스터의 게이트 산화물은 포착된 전자를 점차 축적합니다.갇힌 전자의 전장은 플로팅 게이트의 전자에 추가되어 0 대 1의 임계값 전압 사이의 창을 낮춥니다.충분한 개서 사이클이 경과하면 차이가 너무 작아져 인식할 수 없게 되어 셀이 프로그램된 상태로 고착되어 내구성 장애가 발생합니다.제조업체는 보통 최대 개서 횟수를 100만 [46]개 이상으로 지정합니다.

저장 중에 플로팅 게이트에 주입된 전자는 절연체를 통해, 특히 온도가 상승한 상태에서 표류하여 전하 손실을 일으켜 셀을 지워진 상태로 되돌릴 수 있습니다.제조업체는 일반적으로 10년 [47]이상의 데이터 보존을 보장합니다.

관련 유형

플래시 메모리는 EEPROM의 최신 형태입니다.업계에서는 EEPROM이라는 용어를 블록 단위의 소거 가능 플래시 메모리에 비해 바이트 단위의 소거 가능 메모리에 예약하는 관례가 있습니다.EEPROM은 같은 용량의 플래시 메모리보다 더 많은 다이 영역을 차지합니다.이는 각 셀에 읽기, 쓰기 및 지우기 트랜지스터가 필요한 반면 플래시 메모리 지우기 회로는 큰 셀 블록(대부분 512×8)으로 공유되기 때문입니다.

일부 애플리케이션에서는 FeRAM이나 MRAM 등의 새로운 비휘발성 메모리 테크놀로지가 EEPROM을 서서히 대체하고 있지만, 가까운 장래에는 EEPROM 시장의 극히 일부만이 될 것으로 예상됩니다.

EPROM 및 EEPROM/플래시와의 비교

EPROM과 EEPROM의 차이는 메모리의 프로그램 및 소거 방법에 있습니다.EEPROM은 전계 전자 방출을 사용하여 전기적으로 프로그래밍 및 소거할 수 있습니다(업계에서는 일반적으로 "Fowler-Nordheim 터널링"으로 알려져 있습니다.

EPROM은 전기적으로 소거할 수 없으며 플로팅 게이트에 핫 캐리어 주입을 통해 프로그래밍됩니다.소거는 자외선에 의한 것이지만, 실제로는 많은 EPROM이 자외선에 불투명한 플라스틱으로 캡슐화되어 있어 "일회성 프로그램 가능"이 됩니다.

대부분의 NOR 플래시 메모리는 하이브리드 스타일입니다.프로그래밍은 핫캐리어 주입에 의해 이루어지며 소거는 Fowler-Nordheim 터널링을 통해 이루어집니다.

| 유형 | 게이트에 전자 주입 (비트=0으로 해석되는 값) | 지속 | 게이트에서 전자 제거 (비트=1로 해석됨) | 지속시간/모드 |

|---|---|---|---|---|

| EEPROM | 전계 전자 방출 | 0,1:5 ms, 바이트 단위 | 전계 전자 방출 | 0,1 : 5 ms, 블록 단위 |

| NOR 플래시 메모리 | 용융 주입 | 0.01 - 1 ms | 전계 전자 방출 | 0.01: 1 ms, 블록 단위 |

| EPROM | 용융 주입 | 3: 50 밀리초, 바이트 단위 | 자외선 | 5 - 30분, 칩 전체 |

「 」를 참조해 주세요.

- 눈사태 파괴

- 데이터 플래시

- EPROM

- 전계 전자 방출 δ 파울러-노르하임 터널링

- 플래시 메모리

- 플로팅 게이트 MOSFET

- 인텔 HEX – 파일 형식

- 프로그래머(하드웨어)

- 양자 터널링

- SREC – 파일 형식

- 터널 분기점

- 읽기 메모리(RMM)

레퍼런스

- ^ "TN-04-42: Memory Module Serial Presence-Detect" (PDF). Micron Technology. 2002.

- ^ "serial presence detect (SPD)". TechTarget. July 2015.

- ^ Tarui, Yasuo; Hayashi, Yutaka; Nagai, Kiyoko (1971-09-01). "Proposal of electrically reprogrammable non-volatile semiconductor memory". Proceedings of the 3rd Conference on Solid State Devices, Tokyo. The Japan Society of Applied Physics: 155–162.

- ^ Tarui, Y.; Hayashi, Y.; Nagai, K. (1972). "Electrically reprogrammable nonvolatile semiconductor memory". IEEE Journal of Solid-State Circuits. 7 (5): 369–375. Bibcode:1972IJSSC...7..369T. doi:10.1109/JSSC.1972.1052895. ISSN 0018-9200.

- ^ Tarui, Yasuo; Nagai, Kiyoko; Hayashi, Yutaka (1974-07-19). "Nonvolatile Semiconductor Memory" (PDF). Oyobuturi. 43 (10): 990–1002. doi:10.11470/oubutsu1932.43.990. ISSN 2188-2290. Archived (PDF) from the original on 2018-03-12.

- ^ a b Iizuka, H.; Masuoka, F.; Sato, Tai; Ishikawa, M. (1976). "Electrically alterable avalanche-injection-type MOS READ-ONLY memory with stacked-gate structure". IEEE Transactions on Electron Devices. 23 (4): 379–387. Bibcode:1976ITED...23..379I. doi:10.1109/T-ED.1976.18415. ISSN 0018-9383. S2CID 30491074.

- ^ Rossler, B. (1977). "Electrically erasable and reprogrammable read-only memory using the n-channel SIMOS one-transistor cell". IEEE Transactions on Electron Devices. 24 (5): 606–610. Bibcode:1977ITED...24..606R. doi:10.1109/T-ED.1977.18788. ISSN 0018-9383. S2CID 33203267.

- ^ Suzuki, E.; Hiraishi, H.; Ishii, K.; Hayashi, Y. (1983). "A low-voltage alterable EEPROM with metal—oxide-nitride—oxide—semiconductor (MONOS) structures". IEEE Transactions on Electron Devices. 30 (2): 122–128. Bibcode:1983ITED...30..122S. doi:10.1109/T-ED.1983.21085. ISSN 0018-9383. S2CID 31589165.

- ^ XTECH, NIKKEI. "Renesas Embeds 40nm Flash Memory on Chip". NIKKEI XTECH. Archived from the original on 2018-03-13.

- ^ "Renesas Electronics Develops 90 nm One-Transistor MONOS Flash Memory Technology to Accelerate Intelligence in Automotive Control Systems". Business Wire. 2016-01-03. Archived from the original on 2018-03-13.

- ^ Taito, Y.; Kono, T.; Nakano, M.; Saito, T.; Ito, T.; Noguchi, K.; Hidaka, H.; Yamauchi, T. (2015). "A 28 nm Embedded Split-Gate MONOS (SG-MONOS) Flash Macro for Automotive Achieving 6.4 GB/s Read Throughput by 200 MHz No-Wait Read Operation and 2.0 MB/s Write Throughput at Tj of 170circ$ C". IEEE Journal of Solid-State Circuits. 51 (1): 213–221. Bibcode:2016IJSSC..51..213.. doi:10.1109/JSSC.2015.2467186. ISSN 0018-9200. S2CID 23597256.

- ^ a b Masuoka, Fujio (31 August 1972). "Avalanche injection type mos memory".

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ Rai, Yasuki; Sasami, Terutoshi; Hasegawa, Yuzuru; Okazoe, Masaru (1973-05-18). "Electrically reprogrammable nonvolatile floating gate semi-conductor memory device and method of operation". Archived from the original on 2018-05-03.

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ Abbas, Shakir A.; Barile, Conrad A.; Lane, Ralph D.; Liu., Peter T (1973-03-16). "US3836992A; Electrically erasable floating gate fet memory cell". pdfpiw.uspto.gov. United States Patent and Trademark Office. Archived from the original on 2018-03-09.

- ^ Frohman, Bentchkowsky D (19 October 1973). "Electrically alterable floating gate device and method for altering same".

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ Chou, Sunlin (26 February 1973). "Erasable floating gate device".

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ a b Ohya, Shuichi; Kikuchi, Masanori (1974-12-27). "Non-volatile semiconductor memory device".

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ Verwey, J. F.; Kramer, R. P. (1974). "Atmos—An electrically reprogrammable read-only memory device". IEEE Transactions on Electron Devices. 21 (10): 631–636. Bibcode:1974ITED...21..631V. doi:10.1109/T-ED.1974.17981. ISSN 0018-9383.

- ^ B., Roessler; R. G., Mueller (1975). "Erasable and electrically reprogrammable read-only memory using the N-channel SIMOS one-transistor cell". Siemens Forschungs und Entwicklungsberichte. 4 (6): 345–351. Bibcode:1975SiFoE...4..345R.

- ^ Jack, S; Huang, T. (8 September 1975). "Semiconductor memory cell".

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ Gosney, W. M. (1977). "DIFMOS—A floating-gate electrically erasable nonvolatile semiconductor memory technology". IEEE Transactions on Electron Devices. 24 (5): 594–599. Bibcode:1977ITED...24..594G. doi:10.1109/T-ED.1977.18786. ISSN 0018-9383. S2CID 45636024.

- ^ Moskowitz, Sanford L. (2016). "reliability%20problems"+EPROM+1970s&pg=PA187 Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. ISBN 9781118986097.

- ^ "EEPROM". TMview. Archived from the original on 2018-03-10.

- ^ "Reg. No.1342184 – LIVE – REGISTRATION – Issued and Active".

- ^ "1027459330501acc.pdf" (PDF). Archived (PDF) from the original on 2015-02-07. Retrieved 2015-02-05.

- ^ Harari, Eliyahou (22 February 1977). "Electrically erasable non-volatile semiconductor memory". Archived from the original on 3 May 2018.

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ Chen, P. C. Y. (May 1977). "Threshold-alterable Si-gate MOS devices". IEEE Transactions on Electron Devices. 24 (5): 584–586. Bibcode:1977ITED...24..584C. doi:10.1109/T-ED.1977.18783. ISSN 0018-9383. S2CID 25586393.

- ^ Rossler, B. (May 1977). "Electrically erasable and reprogrammable read-only memory using the n-channel SIMOS one-transistor cell". IEEE Transactions on Electron Devices. 24 (5): 606–610. Bibcode:1977ITED...24..606R. doi:10.1109/T-ED.1977.18788. ISSN 0018-9383. S2CID 33203267.

- ^ Simko, Richard T. (17 March 1977). "Electrically programmable and electrically erasable MOS memory cell".

- ^ Frohman-Bentchkowsky, Dov; Mar, Jerry; Perlegos, George; Johnson, William S. (15 December 1978). "Electrically programmable and erasable MOS floating gate memory device employing tunneling and method of fabricating same".

- ^ Dummer, G. W. A. (2013). Electronic Inventions and Discoveries: Electronics from Its Earliest Beginnings to the Present Day. Elsevier. ISBN 9781483145211.

- ^ Johnson, W.; Perlegos, G.; Renninger, A.; Kuhn, G.; Ranganath, T. (1980). "A 16Kb electrically erasable nonvolatile memory". 1980 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. XXIII: 152–153. doi:10.1109/ISSCC.1980.1156030. S2CID 44313709.

- ^ Euzent, B.; Boruta, N.; Lee, J.; Jenq, C. (1981). "Reliability Aspects of a Floating Gate E2 PROM". 19th International Reliability Physics Symposium: 11–16. doi:10.1109/IRPS.1981.362965. S2CID 41116025.

The Intel 2816 uses the FLOTOX structure, which has been discussed in detail in the literaturel. Basically, it uses an oxide of less than 200A thick between the floating polysilicon gate and the N+ region as shown in Figure 1.

- ^ 2816A-2 PDF Datasheet - Intel Corporation - Datasheets360.com. Intel. October 1983.

- ^ "Seeq Technology » AntiqueTech". Archived from the original on 2014-10-02.

- ^ Rostky, George (July 2, 2002). "Remembering the PROM knights of Intel". EE Times. Archived from the original on September 29, 2007. Retrieved 2007-02-08.

- ^ Atmel AT28C16 datasheet (PDF) (0540B ed.). October 1998. Archived (PDF) from the original on 2017-08-29.

- ^ Gutmann, Peter (2001-08-15). "Data Remanence in Semiconductor Devices". 10th USENIX SECURITY SYMPOSIUM. IBM T. J. Watson Research Center: 39–54. Archived from the original on 2016-10-12.

- ^ Janwadkar, Sudhanshu (2017-10-24). "Fabrication of Floating Gate MOS (FLOTOX)". www.slideshare.net.

- ^ Koga, R.; Tran, V.; George, J.; Crawford, K.; Crain, S.; Zakrzewski, M.; Yu, P. "SEE Sensitivities of Selected Advanced Flash and First-In-First-Out Memories" (PDF). The Aerospace Corporation. Archived (PDF) from the original on 2018-03-14.

- ^ Fuller, Dr. Lynn (2012-02-22). CMOS Process Variations EEPROM Fabrication Technology. Microelectronic Engineering, Rochester Institute of Technology.

- ^ Groeseneken, G.; Maes, H. E.; VanHoudt, J.; Witters, J. S. Basics of Nonvolatile Semiconductor Memory Devices. CiteSeerX 10.1.1.111.9431.

- ^ Bergemont, Albert; Chi, Min-Hwa (1997-05-05). "US Patent 5856222: Method of fabricating a high density EEPROM cell". patents.google.com. National Semiconductor Corp.

- ^ a b Skorobogatov, Sergei (2017). "How Microprobing Can Attack Encrypted Memory" (PDF). 2017 Euromicro Conference on Digital System Design (DSD). 2017 Euromicro Conference on Digital System Design (DSD). Vienna. pp. 244–251. doi:10.1109/DSD.2017.69. ISBN 978-1-5386-2146-2.

- ^ "Breaking copy protection in microcontrollers". www.cl.cam.ac.uk. Archived from the original on 2017-10-22.

- ^ "Frequently Asked Questions -ROHM Semiconductor". Archived from the original on 2011-02-19.

- ^ 시스템 통합 - 트랜지스터 설계에서 대규모 집적회로까지