물리설계(전자제품)

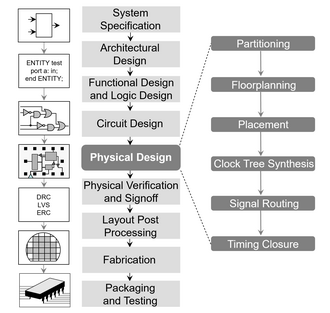

Physical design (electronics)집적회로 설계에서 물리적 설계는 회로 설계 후에 이어지는 표준 설계 사이클의 단계입니다.이 단계에서 설계의 구성요소(디바이스 및 상호접속)의 회로표현은 대응하는 재료층 내에서 제조될 때 구성요소의 필요한 기능을 보장하는 형상표시로 변환된다.이 기하학적 표현을 집적회로 레이아웃이라고 합니다.이 단계는 일반적으로 레이아웃의 [1][2]설계, 검증 및 검증을 모두 포함하는 여러 하위 단계로 나뉩니다.

현대의 집적회로(IC) 설계는 HDL을 사용한 프론트 엔드 설계와 백엔드 설계 또는 물리 설계로 나뉩니다.물리적 설계에 대한 입력은 (i) 넷리스트, (ii) 설계의 기본 장치에 대한 라이브러리 정보, (iii) 제조 제약을 포함하는 기술 파일이다.물리설계는 보통 Layout Post Processing에 의해 마무리되며, Layout Post Processing에서는 칩 레이아웃의 수정과 [3]추가가 이루어집니다.그 후 제조 또는 제조 공정에서 설계를 실리콘 다이에 옮겨 IC로 포장합니다.

위의 각 단계에는 관련된 설계 플로우가 있습니다.이러한 설계 흐름은 해당 단계의 프로세스와 가이드라인/프레임워크를 규정합니다.물리적 설계 흐름은 제조 회사에서 제공하는 기술 라이브러리를 사용합니다.이러한 기술 파일은 사용되는 실리콘 웨이퍼의 유형, 사용되는 표준 셀, 레이아웃 규칙(VLSI의 DRC 등) 등에 대한 정보를 제공합니다.

디비전

일반적으로 IC 물리 설계는 풀 커스텀 설계와 세미 커스텀 설계로 분류됩니다.

- 풀 커스텀:설계자는 레이아웃 설계를 유연하게 수행할 수 있으며 사전 정의된 셀이 사용되지 않습니다.

- 세미 커스텀: 미리 설계된 라이브러리 셀(가능하면 DFM을 사용하여 테스트)을 사용합니다.디자이너는 셀 배치와 라우팅에 유연성을 [4]가지고 있습니다.

풀 커스텀 설계에는 ASIC, 세미 커스텀 설계 플로우에는 FPGA를 사용할 수 있습니다.그 이유는 ASIC에서 [5]공급업체가 제공하는 라이브러리에서 설계 블록을 유연하게 설계/변경할 수 있기 때문입니다.FPGA(Altera 등)를 사용하는 세미 커스텀흐름에는 이 유연성이 결여되어 있습니다.

ASIC 물리 설계 흐름

ASIC 물리 설계 흐름의 주요 단계는 다음과 같습니다.

- 설계 넷리스트(합성 후)

- 플로어 플래닝

- 파티셔닝

- 배치

- 클럭 트리 합성(CTS)

- 라우팅

- 물리적인 검증

- 마스크 데이터 생성을 사용한 레이아웃 후 처리

이 단계는 기본입니다.사용하는 도구와 방법/테크놀로지에 따라 사용되는 PD 흐름의 상세 내용이 있습니다.백엔드 설계에 사용되는 도구/소프트웨어는 다음과 같습니다.

- Cadence (Cadence Except RTL 컴파일러, Except Digital 구현, Cadence Voltus IC 전력 무결성 솔루션, Cadence Tempus 타이밍 사인오프 솔루션)

- Synopsys (Design Compiler, IC Compiler II, IC Validator, Prime Time, Prime Power, Prime Rail)

- 마그마(블라스트퓨전 등)

- 멘토 그래픽스(Olympus SoC, IC-Station, Calibre)

ASIC 물리 설계 플로우에서는 제조 하우스에서 제공되는 테크놀로지 라이브러리를 사용합니다.테크놀로지는 일반적으로 최소 기능 크기에 따라 분류됩니다.표준 사이즈는 2μm, 1μm, 0.5μm, 0.35μm, 0.25μm, 180nm, 130nm, 90nm, 65nm, 45nm, 28nm, 22nm, 18nm, 14nm 등이다. 또한 주요 제조 접근법에 따라 분류할 수 있습니다. n-well 공정, twin-well 공정, SOI 공정 등입니다.

설계 넷리스트

물리적 설계는 합성 프로세스의 최종 결과인 넷리스트에 기초합니다.합성에서는 일반적으로 VHDL 또는 Verilog HDL로 코딩된 RTL 설계를 게이트 레벨의 설명으로 변환하여 다음 도구 세트를 읽고 이해할 수 있습니다.이 넷리스트에는 사용되는 셀, 그 상호접속, 사용되는 영역 및 기타 상세 정보가 포함되어 있습니다.일반적인 합성 도구는 다음과 같습니다.

- Cadence RTL 컴파일러/빌드 게이트/물리 지식 합성(PKS)

- Synopsys 디자인 컴파일러

합성 프로세스 중에는 설계가 필요한 기능 및 속도(사양)를 충족하도록 제약이 적용됩니다.netlist가 기능 및 타이밍을 확인한 후에야 물리 설계 흐름으로 전송됩니다.

순서

플로어 플래닝

물리적 설계 흐름의 두 번째 단계는 평면도입니다.플로어 플래닝은 서로 밀접하게 배치해야 하는 구조를 식별하고 사용 가능한 공간(칩 비용), 필요한 성능 및 기타 모든 것에 근접하려는 욕구라는 때때로 상충되는 목표를 충족하도록 공간을 할당하는 프로세스입니다.

설계면적 및 계층에 기초하여 적절한 평면도를 결정한다.플로어 플래닝에서는 설계, 메모리, 기타 IP 코어와 그 배치 요구, 라우팅 가능성 및 설계 전체의 영역을 고려합니다.또한 플로어 플래닝은 설계의 IO 구조와 석면비도 결정합니다.플로어 플랜이 올바르지 않으면 다이 에리어의 폐기나 라우팅의 congestion가 발생합니다.

많은 설계 방법론에서 면적과 속도는 트레이드오프의 대상이다.이는 라우팅 리소스가 한정되어 있기 때문입니다.사용하는 리소스가 많을수록 동작이 느려집니다.최소 면적을 최적화하면 설계에서 사용하는 리소스를 줄이고 설계 섹션의 근접성을 높일 수 있습니다.이를 통해 상호접속 거리가 짧아지고 사용되는 라우팅 리소스가 줄어들며 엔드 투 엔드 신호 경로가 빨라지며 장소 및 경로 시간이 더욱 빠르고 일관됩니다.올바르게 실시하면, 플로어 플랜에 부정적인 요소가 없습니다.

일반적으로 데이터 경로 섹션은 플로어 플래닝의 이점을 가장 많이 얻지만 랜덤 로직, 스테이트 머신 및 기타 구조화되지 않은 로직은 플레이스 및 루트소프트웨어의 트레이서 섹션에 안전하게 맡길 수 있습니다.

데이터 패스는 일반적으로 여러 비트가 각 비트와 같은 방식으로 병렬로 처리되며 인접 비트의 영향을 받을 수 있습니다.데이터 경로를 구성하는 구조로는 Adders, Subtractors, Counters, Registers 및 Muxes가 있습니다.

파티셔닝

파티셔닝은 칩을 작은 블록으로 나누는 과정입니다.이는 주로 다양한 기능 블록을 분리하여 배치 및 라우팅을 용이하게 하기 위해 수행됩니다.파티셔닝은 설계 엔지니어가 설계 전체를 하위 블록으로 분할한 후 각 모듈의 설계를 진행하는 RTL 설계 단계에서 수행할 수 있습니다.이러한 모듈은 TOP LEVEL 모듈이라고 하는 메인 모듈에서 함께 연결됩니다.이러한 종류의 파티션은 일반적으로 논리 파티션이라고 불립니다.파티션 분할의 목적은 파티션 간의 접속 수를 최소화하도록 회선을 분할하는 것입니다.

배치

배치 최적화를 시작하기 전에 모든 WLM(Wire Load Model)이 제거됩니다.배치에서는 Virtual Route(VR; 가상 루트)로부터의 RC 값을 사용하여 타이밍을 계산합니다.VR은 두 핀 사이의 가장 짧은 맨해튼 거리입니다.VR RC는 WLM RC보다 정확합니다.

배치는 다음 4가지 최적화 단계로 수행됩니다.

- 배치 전 최적화

- 인플레이스먼트

- 클럭 트리 합성(CTS) 전 Post Placement Optimization(PPO; 포스트 배치 최적화)

- CTS 후의 PPO

- 프리플레이스먼트 최적화에 의해 배치 전에 넷리스트가 최적화되어 HFN(High Fanout Net)이 축소됩니다.세포 크기를 줄일 수도 있습니다.

- 임플레이스 최적화는 VR을 기반으로 로직을 다시 최적화합니다.이를 통해 셀 크기 조정, 셀 이동, 셀 바이패스, 넷 분할, 게이트 복제, 버퍼 삽입, 영역 복구를 수행할 수 있습니다.최적화는 셋업 수정, 증분 타이밍 및 congestion에 의한 배치의 반복을 실행합니다.

- CTS가 이상적인 클럭을 사용하여 넷리스트 최적화를 실행하기 전의 포스트 배치 최적화.설정, 보류, 최대 트랜스/캡 위반을 수정할 수 있습니다.글로벌 루팅을 기반으로 배치 최적화를 수행할 수 있습니다.HFN 합성을 합니다.

- CTS가 전파 클럭을 사용하여 타이밍을 최적화한 후 배치 최적화.클럭 스큐를 유지하려고 합니다.

클럭 트리 합성

Clock Tree Synthesis(CTS; 클럭트리 합성)의 목적은 스큐와 삽입 지연을 최소화하는 것입니다.그림과 같이 클럭은 CTS 전에 전파되지 않습니다.CTS 후 홀드슬랙이 개선됩니다클럭 트리는 .sdc 정의 클럭소스에서 시작하여 플롭의 정지 핀에서 종료됩니다.ignore 핀과 sync 핀으로 알려진 두 가지 유형의 스톱 핀이 있습니다.프론트 엔드의 '손대지마' 회로 및 핀(논리 합성)은 '무시' 회로 또는 백엔드의 핀(물리적 합성)으로 취급됩니다.'무시' 핀은 타이밍 분석에서 무시됩니다.클럭이 분할되어 있는 경우는, 개별의 스큐 분석이 필요합니다.

- 글로벌 스큐는 논리 관계를 고려하지 않고 2개의 동기 핀 간에 제로 스큐를 실현합니다.

- 로컬 스큐는 로직 관계를 고려하면서 2개의 동기 핀 사이에 제로 스큐를 실현합니다.

- 클럭이 설정 지연을 개선하기 위해 의도적으로 기울어진 경우 유용한 스큐라고 합니다.

강성은 Astro에서 구속조건의 완화를 나타내기 위해 만들어진 용어이다.강성이 높을수록 구속조건이 더 엄격해집니다.

클럭 트리 최적화(CTO)에서는 노이즈가 다른 신호와 결합되지 않도록 클럭을 차폐할 수 있습니다.그러나 차폐는 면적을 12~15% 증가시킵니다.클럭 신호는 글로벌하기 때문에 전력 라우팅에 사용되는 것과 동일한 금속층이 클럭에도 사용됩니다.CTO는 버퍼 사이징, 게이트사이징, 버퍼 재배치, 레벨 조정 및 HFN 합성에 의해 실현됩니다.홀드 슬랙을 무시한 채 CTS 스테이지 전 배치, 배치 및 배치 후 최적화의 셋업 슬랙을 개선하려고 합니다.CTS 후의 배치 최적화에서는 홀드 슬랙이 개선됩니다.CTS의 결과로 버퍼가 많이 추가됩니다.일반적으로 10만 게이트의 경우 약 650개의 버퍼가 추가됩니다.

라우팅

물리 설계 프로세스에는 글로벌라우팅과 상세 라우팅의 2종류가 있습니다.글로벌 라우팅은 연결에 사용되는 라우팅 리소스를 할당합니다.또한 특정 네트워크에 대한 할당 추적도 수행합니다.

자세한 라우팅은 실제 연결을 수행합니다.라우팅 중에 주의해야 할 다른 제약사항은 DRC, 와이어 길이, 타이밍 등입니다.

물리적인 검증

물리적 검증은 생성된 레이아웃 설계의 정확성을 확인합니다.여기에는 레이아웃의 검증이 포함됩니다.

- 모든 테크놀로지 요건에 준거– 설계 규칙 체크(DRC)

- 원래 넷리스트와 일치– 레이아웃과개요(LVS)

- 안테나 효과 없음 – 안테나 규칙 확인

- 여기에는 풀칩 레벨에서의 밀도 검증도 포함됩니다.청소 밀도는 저테크놀로지 노드에서 매우 중요한 단계입니다.

- 모든 전기 요구 사항 – 전기 규칙 점검(ERC)[6]을 준수합니다.

레이아웃 후 처리

마스크 데이터 준비라고도 하는 Layout Post Processing(레이아웃 후 처리)은 종종 물리적 설계와 검증을 마칩니다.물리적 레이아웃(폴리곤)을 마스크 데이터(포토 마스크 라이터에 대한 지침)로 변환합니다.다음을[3] 포함합니다.

- 회사/칩 라벨 및 최종 구조(씰링, 필러 구조 등) 삽입과 같은 칩 마감

- 테스트 패턴과 얼라인먼트 마크가 있는 레티클 레이아웃 생성,

- 배치 데이터를 그래픽 조작(해상도 향상 테크놀로지, RET 등)으로 확장하여 마스크 제작 장치(포토 마스크 라이터)에 맞추어 조정하는 레이아웃 투 마스크 준비.

「 」를 참조해 주세요.

레퍼런스

- ^ N. Sherwani, "VLSI 물리 설계 자동화를 위한 알고리즘", Kluwer(1998), ISBN9780792383932

- ^ A. Kahng, J. Lienig, I. Markov, J. Hu: "VLSI 물리 설계:그래프 파티션에서 타이밍 클로징까지", 스프링어(2011), doi:10.1007/978-90-481-9591-6, ISBN 978-90-481-9590-9, 페이지 7.

- ^ a b J. Lienig, J. Scheible (2020). "Chap. 3.3: Mask Data: Layout Post Processing". Fundamentals of Layout Design for Electronic Circuits. Springer. p. 102-110. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ^ 세미 커스텀 설계 흐름

- ^ 메흐로트라, 알록, 반 긴네켄, 루카스 P P P, 트리베디, 야틴."50M 게이트 ASIC의 설계 흐름과 방법론", IEEE 컨퍼런스 출판물,ISBN 0-7803-7659-5

- ^ A. Kahng, J. Lienig, I. Markov, J. Hu: "VLSI 물리 설계:그래프 파티션에서 타이밍 클로징까지", 스프링어(2011), doi:10.1007/978-90-481-9591-6, ISBN 978-90-481-9590-9, 페이지 27.