평면도(마이크로일렉트로닉스)

Floorplan (microelectronics)

전자 설계 자동화에서 통합 회로의 평면도는 주요 기능 블록의 임시 배치를 도식으로 나타낸 것이다.null

현대적인 전자 설계 프로세스에서 바닥면은 통합 회로 설계에 대한 계층적 접근의 초기 단계인 평면 설계 단계에서 생성된다.null

준수되는 설계 방법론에 따라 평면도의 실제 정의가 다를 수 있다.null

플로어플래닝

평면도는 설계의 기하학적 제약조건 중 일부를 차지한다.이에 대한 예는 다음과 같다.

- 일반적으로 오프칩 연결을 위한 본딩 패드는 칩 원주에 위치한다.

- 라인 드라이버는 가능한 한 본딩 패드에 가깝게 배치되어야 한다.

- 따라서 필요한 수의 패드를 장착하기 위해 칩 면적이 최소로 주어진 경우도 있다.

- 캐시 RAM, 멀티플라이어, 배럴 시프터, 라인 드라이버 및 산술 논리 유닛과 같은 정의된 구조를 빈번하게 특징으로 하는 데이터 경로를 제한하기 위해 영역이 군집화된다.

- 프로세서 코어와 같은 구매한 지적재산권 블록(IP 블록)은 사전 정의된 영역 블록으로 제공된다.

- 일부 IP 블록은 블록 바로 위에 신호의 라우팅을 허용하지 않는 것과 같은 법적 제한을 수반한다.

수학적 모델 및 최적화 문제

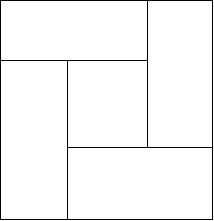

일부 접근방식에서 평면도는 IC 블록이 점유할 축 정렬 직사각형으로 전체 칩 영역의 분할일 수 있다.이 파티션은 블록 면적, 가로 세로 비율, 인터커넥트의 추정 총 측정 등 다양한 제약 조건과 최적화의 요구 조건을 따른다.null

좋은 바닥 평면을 찾는 것은 조합 최적화의 연구 영역이었다.최적의 바닥 평면을 찾는 것과 관련된 대부분의 문제는 NP-hard 즉, 방대한 계산 자원을 필요로 한다.따라서 가장 일반적인 접근법은 다양한 최적화 휴리스틱스를 사용하여 좋은 해결책을 찾는 것이다.null

또 다른 접근법은 설계 방법론을 슬라이스 가능한 바닥판과 같은 특정 등급의 바닥판으로 제한하는 것이다.null

슬라이스 가능한 바닥판

슬라이스 가능한 평면도는 아래에 설명된 대로 반복적으로 정의할 수 있는 평면도다.[1]

- 단일 사각형 블록으로 구성된 평면도를 슬라이스할 수 있다.

- 슬라이스 가능한 바닥 평면의 블록을 수직 또는 수평선에 의해 둘로 절단("슬라이징")하는 경우, 결과적인 바닥 평면은 슬라이싱이 가능하다.

여러 가지 이유로 초기 전자 설계 자동화 도구에[1] 슬라이스 가능한 바닥판이 사용되어 왔다.슬라이스 가능한 바닥판은 슬라이싱 순서에 해당하는 이진수(더 구체적으로는 k-d 나무)로 편리하게 표현될 수 있다.더 중요한 것은 바닥 평면의 많은 NP-하드 문제들이 슬라이스 가능한 바닥 평면으로 제한되었을 때 다항식 시간 알고리즘을 가지고 있다는 것이다.[2]null

추가 읽기

참조

- ^ a b "전기공학 핸드북" 리차드 C.도프 (1997년) ISBN0-8493-8574-1

- ^ Sarrafzadeh, M, "임의의 평면도를 슬라이스 가능한 평면도로 변환", Proc. 1993년 IEEE/ACM 컴퓨터 지원 설계 국제 회의(ICCAD-93) 페이지 386-389.null