상변화 메모리

Phase-change memory| 컴퓨터 메모리 및 데이터 스토리지 유형 |

|---|

| 휘발성 |

| 비휘발성 |

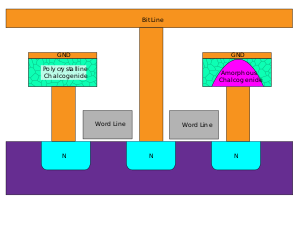

상변화 메모리(PCM, PCME, PRAM, PCRAM, OUM(ovonic Unified Memory) 및 C-RAM 또는 CRAM(chalcogenide RAM)은 비휘발성 랜덤 액세스메모리의 일종입니다.PRAM은 카르코게나이드 유리의 독특한 성질을 이용합니다.PCM에서는 일반적으로 질화티타늄으로 이루어진 발열체에 전류가 흐르면서 발생하는 열을 이용해 유리를 빠르게 가열·담금질하거나 일정 시간 동안 결정화 온도 범위 내에서 유지하여 [1]결정 상태로 전환한다.PCM 에는, 복수의 다른 중간 상태를 실현하는 기능도 있기 때문에, 1 개의 [2]셀에 복수의 비트를 보관 유지하는 기능이 있습니다만, 이러한 기능의 프로그래밍의 어려움으로 인해, 같은 기능을 가지는 다른 테크놀로지(특히 플래시 메모리)에서도 실장할 수 없게 되어 있습니다.

PCM에 대한 최근의 연구는 상변화 재료 GeSbTe225(GST)에 대한 실행 가능한 재료 대안을 찾는 것을 목표로 하고 있으며, 엇갈린 성공을 거두고 있습니다.다른 연구는 레이저 펄스로 게르마늄 원자의 조정 상태를 변화시킴으로써 비열상 변화를 달성하기 위한 GeTe-SbTe23 초격자 개발에 초점을 맞추고 있다.이 새로운 인터페이스 위상변화 메모리(IPCM)는 많은 성공을 거뒀고 계속해서 많은 활발한 [3]연구의 현장이 되고 있다.

Leon Chua는 PCM을 포함한 모든 2단자 비휘발성 메모리 디바이스를 memristor로 [4]간주해야 한다고 주장했습니다.HP Labs의 Stan Williams도 PCM을 멤리스터로 [5]간주해야 한다고 주장했습니다.단, 이 용어에는 문제가 있어 물리적으로 실현 가능한 디바이스에 대한 memristor 이론의 잠재적 적용 가능성은 [6][7]의문의 여지가 있습니다.

배경

1960년대, 스탠포드 R에서Ovshinsky 에너지 변환 장치의 잠재적인 메모리 기술로 칼 코겐의 이원 화합물 안경의 속성을 탐험한다.1969년에 찰스는~아이오와 주립 대학의 논문과 다이오드 배열과 칼 코겐의 이원 화합물 영화를 통합하여는phase-change-memory 장치의 가능성을 입증했다 설명을 발표했다.[8][9]1970년에 한 영사의 연구는 칼코게나이드 유리의phase-change-memory 메커니즘electric-field-induced 결정성 필라멘트가 자라 척추를 설립했다.[10][11]전자의 9월 1970년 4월호에, 고든 무어 인텔의 공동 창업자인 기술에서 기사를 보도했다.[12]하지만, 물질적인 품질과 전력 소비 문제들은 기술의 상업화를 방지했다.좀 더 최근에, 관심과 연구 석화 같은,와 D램 메모리 기술로 칩 반도체 인쇄 기술이 줄어들고 스케일링 어려움에 직면할 것으로 예상된다 재개되고 있다.[13]

칼코게나이드 유리의 결정성 상태와 비정질 상태는 전기 저항률 값이 극적으로 다릅니다.비정질, 고저항 상태는 이진수 0을 나타내며, 결정성, 저저항 상태는 [citation needed]1을 나타냅니다.칼코게니드는, 개서 가능한 광학 미디어(CD-RW 나 DVD-RW 등)에 사용되는 것과 같은 소재입니다.이 경우 재료 상태에 따라 칼코게니드의 굴절률도 변화하기 때문에 전기저항률보다는 재료의 광학 특성이 조작된다.

PRAM은 아직 가전제품의 상용화 단계에 이르지는 않았지만, 거의 모든 프로토타입 디바이스는 게르마늄(Ge), 안티몬(Sb), 텔루륨(Te)의 칼코게나이드 합금인 GeSbTe(GeSbTe)를 사용하고 있습니다.화학측정학(Ge:Sb:Te 원소비)은 GST에서 2:2:5입니다.GST를 고온(600°C 이상)으로 가열하면 카르코게니드의 결정성이 손실됩니다.냉각되면 비정질 유리 상태로 동결되어 전기 저항이 높아집니다.칼코게니드를 결정점 위, 녹는점 아래까지 가열하면 저항이 훨씬 낮은 결정 상태로 변한다.이 상전이를 완료하는 시간은 온도에 따라 달라집니다.칼코게니드의 냉각부분은 결정화하는데 시간이 오래 걸리고 과열부분은 재용융해도 좋다.일반적으로 100ns 정도의 결정화 시간 척도가 사용됩니다.[15]이는 약 2나노초의 스위칭 시간을 갖는 현대의 DRAM과 같은 기존의 휘발성 메모리 장치보다 길다.그러나 2006년 1월 삼성전자 특허출원에 따르면 PRAM은 5나노초까지 스위칭 속도를 달성할 수 있다.

2008년 인텔과 ST Microelectronics가 개척한 진보에 따라 재료 상태를 보다 세심하게 제어할 수 있게 되어 이전의 비정질 상태 또는 결정성 상태, 그리고 두 개의 새로운 부분 결정성 상태 중 하나로 변환할 수 있게 되었습니다.이러한 각 상태는 읽기 중에 측정할 수 있는 전기적 특성이 다르기 때문에 단일 셀이 2비트를 나타내 메모리 [16]밀도를 두 배로 높일 수 있습니다.

알루미늄/안티모니

게르마늄, 안티몬 및 텔루륨에 기반한 상변화 메모리 장치는 재료의 구성을 칼코겐으로 식각하고 연마할 수 있기 때문에 제조상의 문제를 야기합니다.알루미늄과 안티몬 소재는 GeSbTe보다 열적으로 안정적입니다.AlSb에는5050 3개의 뚜렷한 저항 레벨이 있으며, 2개의 셀이 아닌 2개의 셀에 3비트의 데이터를 저장할 수 있는 가능성이 있습니다(셀 쌍이 가능한 9개의 상태는 로그 8 = 3비트를 [17][18]산출합니다2).

PRAM과플래시

PRAM의 스위칭 시간과 고유의[19] 확장성은 플래시 메모리보다 매력적입니다.PRAM의 온도 감도는 아마도 PRAM의 가장 주목할 만한 단점일 것입니다. PRAM은 이 기술을 통합한 제조사의 생산 공정을 변경해야 할 수도 있습니다.

플래시 메모리는 MOS 트랜지스터의 게이트 내에 저장된 전하(전자)를 변조하여 작동합니다.게이트는 전하(플로팅 게이트 또는 절연체 "트랩")를 트랩하도록 설계된 특수 "스택"으로 구성됩니다.게이트 내에 전하가 존재하면 트랜지스터의 임계값 V V_mathrm {이(가) 1에서 0으로 또는 0에서 1로 변화합니다.비트의 상태를 변경하려면 축적된 전하를 제거해야 하며, 이는 플로팅 게이트에서 전자를 "흡입"하기 위해 상대적으로 큰 전압이 필요합니다.이 전압 버스트는 충전 펌프에 의해 공급되며, 이 펌프는 전력 공급에 시간이 걸립니다.일반적인 플래시 디바이스의 일반적인 쓰기 시간은 약 100μs(데이터 블록의 경우)로, 예를 들어 SRAM의 일반적인 10ns 읽기 시간(1바이트의 [citation needed]경우)의 약 10,000배입니다.

PRAM은 메모리 요소를 더 빠르게 전환할 수 있고 셀 블록 전체를 먼저 지울 필요 없이 단일 비트를 1 또는 0으로 변경할 수 있기 때문에 빠른 쓰기가 중요한 애플리케이션에서 훨씬 더 높은 성능을 제공할 수 있습니다.PRAM은 기존 하드 드라이브보다 수천 배 빠른 고성능으로 현재 메모리 액세스 타이밍에 따라 성능이 제한되는 비휘발성 메모리 역할에 특히 관심을 끌고 있습니다.

또한 플래시를 사용하면 셀 전체에서 전압이 버스트될 때마다 열화가 발생합니다.셀의 크기가 작아짐에 따라 장치의 프로그래밍에 필요한 전압이 리소그래피와 함께 스케일링되지 않기 때문에 프로그래밍에 의한 손상이 심해진다.대부분의 플래시 장치는 현재 섹터당 쓰기 횟수가 5,000건에 불과하며, 많은 플래시 컨트롤러가 쓰기 작업을 여러 물리적 섹터로 분산시키기 위해 마모 레벨링을 수행합니다.

PRAM 디바이스도 플래시와는 다른 이유로 사용 시 열화되지만 열화 속도는 훨씬 느립니다.PRAM 디바이스는 약 1억 개의 기입 [20]사이클을 견딜 수 있습니다.PRAM의 라이프 타임은 프로그래밍 중 GST 열팽창에 의한 열화, 금속(및 기타 재료) 이행 및 아직 알려지지 않은 기타 메커니즘에 의해 제한됩니다.

플래시 부품은 기판에 납땜하기 전에 프로그래밍할 수 있으며, 사전 프로그래밍된 제품을 구입할 수도 있습니다.단, PRAM의 내용은 디바이스를 보드에 납땜할 때 고온으로 인해 손실됩니다(리플로 납땜 또는 웨이브 납땜 참조).이는 높은 납땜 온도를 요구하는 무연 제조 요구로 인해 더욱 악화되었습니다.PRAM 부품을 사용하는 제조업체는 PRAM을 납땜한 후 "시스템 내"를 프로그래밍하는 메커니즘을 제공해야 합니다.

플래시 메모리에 사용되는 특수 게이트는 시간이 지남에 따라 충전(전자)이 "누출"되어 손상 및 데이터 손실을 일으킵니다.PRAM에서 메모리 소자의 저항률은 더 안정적입니다. 정상 작동 온도인 85°C에서는 300년 [21]동안 데이터를 유지할 것으로 예상됩니다.

게이트에 저장되는 전하량을 신중하게 조절함으로써 플래시 디바이스는 각 물리 셀에 여러 비트(보통 2비트)를 저장할 수 있습니다.실제로 메모리 밀도를 2배로 하여 비용을 절감합니다.PRAM 디바이스는 원래 각 셀에 1비트만 저장했지만 인텔의 최신 기술로 이 [citation needed]문제를 해결했습니다.

플래시 장치는 정보를 저장하기 위해 전자를 가두기 때문에 방사선에 의한 데이터 손상에 취약하기 때문에 많은 공간 및 군사 애플리케이션에 적합하지 않습니다.PRAM은 방사선에 대한 내성이 더 높습니다.

PRAM 셀 셀렉터는 다이오드, BJT 및 MOSFET 등 다양한 장치를 사용할 수 있습니다.다이오드 또는 BJT를 사용하면 주어진 셀 크기에 대해 가장 많은 전류를 공급합니다.단, 다이오드의 사용에 대한 우려는 인접 셀로의 기생 전류와 높은 전압 요건에서 비롯되어 소비전력이 높아집니다.칼코게니드 저항은 반드시 다이오드 저항보다 큽니다. 즉, 다이오드로부터 적절한 순방향 바이어스 전류를 보장하려면 작동 전압이 1V를 크게 초과해야 합니다.다이오드 선택 어레이, 특히 대규모 어레이를 사용할 때 가장 심각한 결과는 선택되지 않은 비트라인으로부터의 총 역바이어스 리크 전류입니다.트랜지스터 선택 어레이에서는 선택한 비트 라인만 역바이어스 누출 전류를 발생시킵니다.누출 전류의 차이는 몇 가지 크기입니다.40nm 미만의 스케일링에 대한 또 다른 우려 사항은 p-n 접합 폭 축소에 따른 이산 도판트의 영향이다.박막 베이스의 실렉터는, 메모리 레이어를 수평 또는 수직으로 적층하는 것으로써2, 4 F 미만의 셀 영역을 활용해 고밀도를 실현합니다.셀렉터의 온/오프 비율이 충분하지 않으면 절연 기능이 트랜지스터 사용보다 떨어지는 경우가 많기 때문에 이 아키텍처에서 매우 큰 어레이를 작동시키는 기능이 제한됩니다.Chalcogenide 기반의 임계값 스위치는 고밀도 PCM 어레이에 적합한 셀렉터로서 실증되었습니다.

2000년 이후

2004년 8월, Nanochip은 MEMS(마이크로 일렉트릭 메카니컬 시스템) 프로브 스토리지 디바이스에 사용하는 PRAM 기술을 라이센스 취득했습니다.이러한 디바이스는 솔리드 스테이트가 아닙니다.대신, 칼코게니드로 코팅된 매우 작은 플래터가 칼코게니드를 읽고 쓸 수 있는 수천 또는 수백만 개의 전기 프로브 아래로 끌려갑니다.Hewlett-Packard의 마이크로 무버 테크놀로지는 플래터를 3nm까지 정확하게 배치할 수 있기 때문에 테크놀로지를 완성할 수 있다면 평방 인치당 1 Tbit(125 GB) 이상의 밀도가 가능합니다.기본적인 아이디어는 온칩에서 필요한 배선량을 줄이는 것입니다.셀은 모든 셀을 배선하는 대신 MEMS 프로브를 통과하는 전류에 의해 배선처럼 서로 가까이 배치되어 판독됩니다.이 접근 방식은 IBM의 Millipede 기술과 매우 유사합니다.

삼성 46.7 nm 셀

2006년 9월 삼성은 다이오드 스위치를 [23]사용한 512MB(64MB) 장치의 시제품을 발표했다.이 발표는 놀라운 것이었고, 특히 메모리 밀도가 상당히 높다는 점이 눈에 띄었다.시제품의 셀 크기는 46.7 nm로 당시 시판되던 시판 플래시 장치보다 작았다.용량이 더 큰 플래시 장치를 사용할 수 있었지만(64Gb 또는 8GB가 막 시장에 출시됨), 일반적으로 플래시를 대체하기 위해 경쟁하는 다른 기술은 더 낮은 밀도(셀 크기 증가)를 제공했습니다.예를 들어 실제 가동 중인 MRAM 및 FeRAM 디바이스는 4Mb뿐입니다.삼성의 프로토타입 PRAM 장치는 높은 밀도로 인해 다른 장치처럼 틈새 역할에 국한되지 않고 실행 가능한 플래시 경쟁자가 될 수 있음을 시사했습니다.PRAM은 장치 용량이 NAND 플래시 장치의 용량보다 일반적으로 뒤처지는 NOR 플래시를 대체할 수 있는 잠재적인 제품으로 특히 매력적으로 보였습니다.낸드의 최첨단 용량은 얼마 전 512Mb를 넘어섰다.NOR 플래시는 삼성의 PRAM 프로토타입과 유사한 밀도를 제공하며 이미 비트 주소 지정 기능을 제공합니다(한 번에 많은 바이트의 뱅크에서 메모리에 액세스하는 NAND와 달리).

인텔의 PRAM 디바이스

삼성의 발표는 인텔과 STMicroelectronics가 10월에 [24]열린 2006 인텔 개발자 포럼에서 자체 개발한 PRAM 기기를 시연하는 것에 이어 이루어졌다.이탈리아 아그라테에 있는 ST마이크로일렉트로닉스 연구소에서 생산을 시작한 128Mb 부품을 선보였다.인텔은 이 장치들이 엄밀하게 개념 증명이라고 밝혔다.

BAE 장치

PRAM은 또한 방사선 효과가 플래시와 같은 표준 비휘발성 메모리를 실용적으로 사용하는 군사 및 항공우주 산업에서 유망한 기술입니다.PRAM 장치는 뛰어난 방사선 내성(라드 하드)과 래치업 내성을 주장하는 C-RAM이라고 불리는 BAE Systems에 의해 도입되었습니다.또한 BAE는 쓰기 사이클 내구성이 10이라고8 주장하므로 우주 시스템에서 PROM과 EEPROM을 대체할 수 있습니다.

멀티 레벨 셀

2008년 2월에 인텔과 STMicroelectronics는 최초의 멀티레벨(MLC) PRAM 어레이 프로토타입을 발표했습니다.프로토타입은 각 물리 셀에 2개의 논리 비트를 저장했으며, 실제로는 128Mb의 물리 어레이에 256Mb의 메모리를 저장했습니다.즉, 일반적인 2가지 상태(완전 비정질 상태 및 완전 결정성 상태)가 아닌 2개의 다른 중간 상태가 부분 결정화의 정도를 나타내므로 동일한 물리 [16]영역에 2배의 비트를 저장할 수 있습니다.2011년 [25]6월, IBM은 고성능과 안정성을 갖춘 안정적이고 안정적인 멀티비트 위상 변화 메모리를 개발했다고 발표했습니다.SK하이닉스는 IBM과 다단계 PRAM [26]기술 개발을 위한 공동 개발 협약과 기술 라이센스 계약을 체결했다.

인텔의 90 nm 디바이스

또, 2008년 2월에 인텔과 STMicroelectronics는, 최초의 PRAM 제품의 시제품 샘플을 고객에게 출하했습니다.90 nm, 128 Mb(16 MB) 제품의 이름은 [27]Alverstone이었습니다.

2009년 6월, 삼성과 Numonyx B.V.는 PRAM 시장 맞춤형 하드웨어 [28]제품 개발을 위한 공동 노력을 발표했습니다.

2010년 [29]4월, Numonyx는 128 Mbit NOR 호환 상변화 메모리의 Omneo 라인을 발표했습니다.삼성은 2010년 가을까지 휴대폰에 사용할 512Mb급 상변화램(PRAM)을 멀티칩 패키지(MCP)에 담아 출하했다고 발표했다.

ST 28 nm, 16 MB 어레이

2018년 12월 STMicroelectronics는 절연체 자동차 컨트롤 [30]유닛에 28nm 완전 고갈된 실리콘에 대한 16MB ePCM 어레이의 설계 및 성능 데이터를 발표했습니다.

인메모리 컴퓨팅

최근에는 인메모리 [31]컴퓨팅용 PCM(추진 제어 모듈)의 응용에 대한 관심이 높아지고 있습니다.중요한 아이디어는 PCM의 아날로그 스토리지 기능 및 Kirchhoff의 회로 법칙을 이용하여 메모리 어레이 자체에서 매트릭스 벡터 멀티플 연산 등의 연산 태스크를 수행하는 것입니다.PCM 기반의 인메모리 컴퓨팅은 매우 높은 컴퓨팅 [32]정밀도를 필요로 하지 않는 딥 러닝 추론 등의 응용 프로그램에 흥미로울 수 있습니다.2021년 IBM은 14nm CMOS 기술 [33]노드에 통합된 다단계 PCM 기반의 완전한 인메모리 컴퓨팅 코어를 발표했습니다.

과제들

상변화 메모리의 가장 큰 과제는 높은 프로그래밍 전류 밀도(일반7 트랜지스터 또는 [citation needed]다이오드의 경우 10...106 A/cm² 이상5)가 요구되었습니다.열상변화 영역과 인접한 유전체 사이의 접촉도 또 다른 근본적인 관심사입니다.더 높은 온도에서 유전체가 누출되기 시작하거나 상변화 물질과 다른 속도로 팽창할 때 접착력이 떨어질 수 있습니다.

상변화 메모리는 의도하지 않은 상변화와 의도하지 않은 상변화의 기본적인 트레이드오프에 영향을 받기 쉽습니다.이는 주로 상변화가 전자 프로세스라기보다는 열 구동 프로세스라는 사실에서 비롯됩니다.신속한 결정화를 가능하게 하는 열조건은 대기조건과 너무 비슷해서는 안 됩니다(예: 실온).그렇지 않으면 데이터를 유지할 수 없습니다.결정화를 위한 적절한 활성화 에너지로 프로그래밍 조건에서는 빠른 결정화가 가능하지만, 정상 조건에서는 매우 느린 결정화를 가질 수 있습니다.

상변화 메모리의 가장 큰 문제는 아마도 장기 저항과 임계값 전압 [34]드리프트일 것입니다.비정질 상태의 저항은 멱함수 법칙(~t0.1)에 따라 서서히 증가한다.이는 낮은 중간 상태가 나중에 높은 중간 상태와 혼동될 수 있기 때문에 다단계 작동 능력을 심각하게 제한하고, 또한 임계값 전압이 설계값을 초과하여 증가하면 표준 2단계 작동을 위태롭게 할 수 있습니다.

2010년 4월, Numonyx는 Omneo 라인의 128 Mb 병렬 및 시리얼 인터페이스를 대체한 PRAM 칩을 출시했습니다.교체하려는 NOR 플래시 칩은 -40-85°C 범위에서 작동했지만 PRAM 칩은 0-70°C 범위에서 작동하여 NOR 플래시보다 작동 윈도우가 더 작음을 나타냅니다.이는 프로그래밍에 필요한 고전류를 제공하기 위해 고온에 민감한 p-n 접합을 사용했기 때문일 수 있습니다.

타임라인

- 1955년 1월: 콜로미에츠, 고루노바 등, 칼코게나이드 [35][36]유리의 반도체 특성을 밝혀냈다.

- 1966년 9월: Stanford Ovshinsky, 상변화 테크놀로지 최초 특허 출원

- 1969년 1월: 찰스 H.Sie는 아이오와 주립대학에서 칼코게니드 위상변화기억장치에 관한 논문을 발표했다.

- 1969년 6월: Ovshinsky에 라이선스를 취득한 미국 특허 3,448,302(샤네필드)는 PRAM 디바이스의 최초 신뢰성 높은 조작을 주장하고 있습니다.

- 1970년 9월: Gordon Moore가 Electronics Magazine에 연구 발표

- 1999년 6월:PRAM 기술 상용화를 위한 오보닉스 합작법인 설립

- 1999년 11월: 록히드마틴은 우주 어플리케이션용 PRAM에서 Ovonyx와 협력

- 2000년 2월: 인텔은 라이선스 테크놀로지인 Ovonyx에 투자

- 2000년 12월: ST Microelectronics, Ovonyx에서 PRAM 테크놀로지 라이선스 취득

- 2002년 3월 : 마크롱ix, 트랜지스터리스 PRAM 특허출원

- 2003년 7월: 삼성, PRAM 테크놀로지 작업 개시

- 2003~2005년 : 도시바, 히타치, 마크롱ix, 르네사스, 엘피다, 소니, 마쓰시타, 미쓰비시, 인피니온 등의 PRAM 관련 특허출원

- 2004년 8월: Nanochip이 Ovonyx의 PRAM 테크놀로지를 MEMS 프로브 스토리지용으로 라이선스

- 2004년 8월: 삼성, 64 Mbit PRAM 어레이 성공 발표

- 2005년 2월: Elpida가 Ovonyx에서 PRAM 테크놀로지를 라이선스

- 2005년 9월: 삼성, 256 Mbit PRAM 어레이 성공 발표, 400μA 프로그래밍 전류 예측

- 2005년 10월: 인텔, Ovonyx 투자 확대

- 2005년 12월, Hitachi와 Renesas는 100μA 프로그래밍 전류 1.5V PRAM 발표

- 2005년 12월: 삼성이 Ovonyx에서 PRAM 테크놀로지 라이선스 취득

- 2006년 7월: BAE Systems, 최초의 시판 PRAM 칩 판매 개시

- 2006년 9월: 삼성, 512 Mbit PRAM 디바이스 발표

- 2006년 10월: 인텔 및 STMicroelectronics 128 Mbit PRAM 칩 발표

- 2006년 12월: IBM Research Labs가 3x20나노미터의[37] 프로토타입을 시연합니다.

- 2007년 1월: Qimonda, Ovonyx에서 PRAM 테크놀로지 라이선스 취득

- 2007년 4월: 인텔의 최고기술책임자 Justin Rattner가 동사의 PRAM(상변화RAM) 테크놀로지를 최초로 공개 시연할 예정입니다.

- 2007년 10월 하이닉스, Ovonyx 기술 라이선스 취득으로 PRAM 추진 개시

- 2008년 2월: 인텔과 STMicroelectronics는 4스테이트 MLC PRAM을[16] 발표하여 샘플 [27]발송을 시작합니다.

- 2008년 12월: Numonyx는 128 Mbit PRAM 디바이스의 양산을 특정 고객에게 발표합니다.

- 2009년 6월: 삼성의 상변화 RAM은 6월부터[39] 양산에 들어간다.

- 2009년 9월: 삼성, 512 Mbit PRAM 디바이스[40] 양산 개시 발표

- 2009년 10월:인텔과 Numonyx는 상변화 메모리 어레이를 1개의[41] 다이로 스택하는 방법을 발견했다고 발표했습니다.

- 2009년 12월 : Numonyx, 1Gb 45nm[42] 제품 발표

- 2010년 4월: Numonyx는 Omneo PRAM 시리즈(P8P 및 P5Q)를 모두 90nm로 [43]출시.

- 2010년 4월: 삼성은 65 nm 공정의 512 Mbit PRAM을 멀티칩 패키지로 [44]출시합니다.

- 2011년 2월: 삼성은 58nm 1.8V 1Gb PRAM을 [45]선보였다.

- 2012년 2월: 삼성은 20 nm 1을 발표했다.8 V 8 Gb PRAM[46]

- 2012년 7월: 마이크론, 모바일 디바이스용 위상변경 메모리 제공 발표 - 대량 생산[47] 최초의 PRAM 솔루션

- 2014년 1월: 마이크론은 모든 PCM 부품을 시장에서 철수합니다.[48]

- 2014년 5월: IBM은 PCM, 기존 NAND 및 DRAM을 단일 컨트롤러에서[49] 결합하는 방법을 시연합니다.

- 2014년 8월:Western Digital은 300만 I/O와 1.5마이크로초의[50] 레이텐시를 가진 PCM 스토리지의 프로토타입 시연

- 2015년 7월:인텔과 마이크론은 상변화 합금을 메모리 셀의 저장 부품으로 사용하는 3D X포인트 메모리를 발표했다.

「 」를 참조해 주세요.

- 강유전체 RAM(FRAM)

- 자기저항랜덤액세스메모리(MRAM)

- 읽기 메모리(RMM)

레퍼런스

- ^ Le Gallo, Manuel; Sebastian, Abu (2020-03-30). "An overview of phase-change memory device physics". Journal of Physics D: Applied Physics. 53 (21): 213002. doi:10.1088/1361-6463/ab7794. ISSN 0022-3727.

- ^ Burr, Geoffrey W.; BrightSky, Matthew J.; Sebastian, Abu; Cheng, Huai-Yu; Wu, Jau-Yi; Kim, Sangbum; Sosa, Norma E.; Papandreou, Nikolaos; Lung, Hsiang-Lan; Pozidis, Haralampos; Eleftheriou, Evangelos (June 2016). "Recent Progress in Phase-Change Memory Technology". IEEE Journal on Emerging and Selected Topics in Circuits and Systems. 6 (2): 146–162. doi:10.1109/JETCAS.2016.2547718. ISSN 2156-3357.

- ^ Simpson, R.E.; P. Fons; A. V. Kolobov; T. Fukaya; et al. (July 2011). "Interfacial phase-change memory". Nature Nanotechnology. 6 (8): 501–5. Bibcode:2011NatNa...6..501S. doi:10.1038/nnano.2011.96. PMID 21725305. S2CID 6684244.

- ^ Chua, L. O. (2011), "Resistance switching memories are memristors", Applied Physics A, 102 (4): 765–783, Bibcode:2011ApPhA.102..765C, doi:10.1007/s00339-011-6264-9

- ^ Mellor, Chris (10 October 2011), "HP and Hynix to produce the memristor goods by 2013", The Register, retrieved 2012-03-07

- ^ Meuffels, P.; Soni, R. (2012). "Fundamental Issues and Problems in the Realization of Memristors". arXiv:1207.7319 [cond-mat.mes-hall].

- ^ Di Ventra, Massimiliano; Pershin, Yuriy V. (2013). "On the physical properties of memristive, memcapacitive and meminductive systems". Nanotechnology. 24 (25): 255201. arXiv:1302.7063. Bibcode:2013Nanot..24y5201D. CiteSeerX 10.1.1.745.8657. doi:10.1088/0957-4484/24/25/255201. PMID 23708238. S2CID 14892809.

- ^ Sie, C.H. (1969). Memory cell using bistable resistivity in amorphous As-Te-Ge film. Retrospective Theses and Dissertations (PhD). Iowa State University. 3604 https://lib.dr.iastate.edu/rtd/3604.

- ^ Pohm, A.; Sie, C.; Uttecht, R.; Kao, V.; Agrawal, O. (1970). "Chalcogenide glass bistable resistivity (Ovonic) memories". IEEE Transactions on Magnetics. 6 (3): 592. Bibcode:1970ITM.....6..592P. doi:10.1109/TMAG.1970.1066920.

- ^ "As-Te-Ge 반도체에서 전계 유도 필라멘트 형성" C.H. Sie, R.Uttecht, H. Stevenson, J. D. Griener 및 K.라그하반, 비결정 고체 저널, 2, 358–370, 1970

- ^ "A Cinematic Study of Mechanisms of Phase Change Memory". YouTube. 2012-06-21. Archived from the original on 2021-12-21. Retrieved 2013-09-17.

- ^ Moore, Gordon E.; Neale, R.G.; Nelson, D.L. (September 28, 1970). "Nonvolatile and reprogramable, the read-mostly memory is here" (PDF). Electronics: 56–60.

- ^ "Is NAND flash memory a dying technology?". Techworld. Retrieved 2010-02-04.

- ^ Caravati, Sebastiano; Bernasconi, Marco; Kühne, Thomas D.; Krack, Matthias; Parrinello, Michele (2007). "Coexistence of tetrahedral- and octahedral-like sites in amorphous phase change materials". Applied Physics Letters. 91 (17): 171906. arXiv:0708.1302. Bibcode:2007ApPhL..91q1906C. doi:10.1063/1.2801626. S2CID 119628572.

- ^ Horii, H.; et al. (2003). "A novel cell technology using N-doped GeSbTe films for phase change RAM". 2003 Symposium on VLSI Technology. Digest of Technical Papers. pp. 177–8. doi:10.1109/VLSIT.2003.1221143. ISBN 4-89114-033-X. S2CID 40051862. 03CH37407.

- ^ a b c Greene, Kate (4 February 2008). "A Memory Breakthrough". Technology Review.

- ^ "Will phase-change memory replace flash memory?". KurzweilAI. Retrieved 2013-09-17.

- ^ Zhou, X.; Wu, L.; Song, Z.; Rao, F.; Ren, K.; Peng, C.; Song, S.; Liu, B.; Xu, L.; Feng, S. (2013). "Phase transition characteristics of Al-Sb phase change materials for phase change memory application". Applied Physics Letters. 103 (7): 072114. Bibcode:2013ApPhL.103g2114Z. doi:10.1063/1.4818662.

- ^ Simpson, R. E. (2010). "Toward the Ultimate Limit of Phase Change in Ge2Sb2Te5". Nano Letters. 10 (2): 414–9. Bibcode:2010NanoL..10..414S. doi:10.1021/nl902777z. PMID 20041706. S2CID 9585187.

- ^ "Intel to Sample Phase Change Memory This Year". Archived from the original on 2007-03-23. Retrieved 2007-06-30.

- ^ Pirovano, A.; Redaelli, A.; Pellizzer, F.; Ottogalli, F.; Tosi, M.; Ielmini, D.; Lacaita, A.L.; Bez, R. (2004). "Reliability study of phase-change nonvolatile memories". IEEE Transactions on Device and Materials Reliability. 4 (3): 422–7. doi:10.1109/TDMR.2004.836724. S2CID 22178768.

- ^ Karpov, I.V.; Kencke, D.; Kau, D.; Tang, S.; Spadini, G. (2010). "Phase Change Memory with Chalcogenide Selector (PCMS): Characteristic Behaviors, Physical Models and Key Material Properties". Symposium G – Materials and Physics for Nonvolatile Memories II. MRS Proceedings. Vol. 1250. Cambridge University Press. pp. G14-01–H07-01. doi:10.1557/PROC-1250-G14-01-H07-01.

- ^ 삼성, 차세대 비휘발성 메모리 출시-프램

- ^ "Intel Previews Potential Replacement for Flash".

- ^ "IBM develops 'instantaneous' memory, 100x faster than flash". engadget. 2011-06-30. Retrieved 2011-06-30.

- ^ "SK hynix and IBM Sign Joint Development for PCRAM". SK hynix Newsroom. Retrieved 2022-02-05.

- ^ a b "Intel, STMicroelectronics Deliver Industry's First Phase Change Memory Prototypes". Numonyx. 2008-02-06. Archived from the original on 2008-06-09. Retrieved 2008-08-15.

- ^ "Samsung Electronics and Numonyx Join Forces on Phase Change Memory". Samsung. 2009-06-23.

- ^ "Samsung to ship MCP with phase-change". EE Times. 2010-04-28. Retrieved 2010-05-03.

- ^ "Phase-Change Memory (PCM) - Technology, Advantages & Applications - STMicroelectronics". www.st.com. Retrieved 2022-07-08.

- ^ Burr, Geoffrey W.; Shelby, Robert M.; Sidler, Severin; di Nolfo, Carmelo; Jang, Junwoo; Boybat, Irem; Shenoy, Rohit S.; Narayanan, Pritish; Virwani, Kumar; Giacometti, Emanuele U.; Kurdi, Bulent N. (November 2015). "Experimental Demonstration and Tolerancing of a Large-Scale Neural Network (165 000 Synapses) Using Phase-Change Memory as the Synaptic Weight Element". IEEE Transactions on Electron Devices. 62 (11): 3498–3507. doi:10.1109/TED.2015.2439635. ISSN 0018-9383.

- ^ Sebastian, Abu; Le Gallo, Manuel; Khaddam-Aljameh, Riduan; Eleftheriou, Evangelos (July 2020). "Memory devices and applications for in-memory computing". Nature Nanotechnology. 15 (7): 529–544. doi:10.1038/s41565-020-0655-z. ISSN 1748-3395.

- ^ Khaddam-Aljameh, Riduan; Stanisavljevic, Milos; Mas, Jordi Fornt; Karunaratne, Geethan; Brändli, Matthias; Liu, Feng; Singh, Abhairaj; Müller, Silvia M.; Egger, Urs; Petropoulos, Anastasios; Antonakopoulos, Theodore (2022). "HERMES-Core–A 1.59-TOPS/mm² PCM on 14-nm CMOS In-Memory Compute Core Using 300-ps/LSB Linearized CCO-Based ADCs". IEEE Journal of Solid-State Circuits: 1–1. doi:10.1109/JSSC.2022.3140414. ISSN 1558-173X.

- ^ Karpov, I.V.; Mitra, M.; Kau, D.; Spadini, G.; Kryukov, Y.A.; Karpov, V.G. (2007). "Fundamental drift of parameters in chalcogenide phase change memory". J. Appl. Phys. 102 (12): 124503–124503–6. Bibcode:2007JAP...102l4503K. doi:10.1063/1.2825650.

- ^ Kolomiets, B. T. (1964). "Vitreous Semiconductors (I)". Physica Status Solidi B. 7 (2): 359–372. Bibcode:1964PSSBR...7..359K. doi:10.1002/pssb.19640070202.

- ^ Kolomiets, B. T. (1964). "Vitreous Semiconductors (II)". Physica Status Solidi B. 7 (3): 713–731. Bibcode:1964PSSBR...7..713K. doi:10.1002/pssb.19640070302.

- ^ "Phase Change to Replace Flash?". Archived from the original on September 27, 2007.

- ^ "IT news, careers, business technology, reviews". Computerworld.

- ^ Engadget Samsung PRAM 칩, 양산 시작

- ^ "Samsung moves phase-change memory to production".

- ^ "Intel and Numonyx Achieve Research Milestone with Stacked, Cross Point Phase Change Memory Technology". www.intel.com.

- ^ Numonyx, 주요 테크놀로지 업계 컨퍼런스에서 위상변화 메모리 연구 결과 발표

- ^ "Numonyx Memory Solutions - Numonyx Introduces New Phase Change Memory Devices". April 25, 2010. Archived from the original on 25 April 2010.

- ^ "Page Not Found - SAMSUNG". Samsung Electronics America. Archived from the original on August 21, 2010.

{{cite web}}:Cite는 일반 제목(도움말)을 사용합니다. - ^ Chung, H.; et al. (2011). "A 58nm 1.8V 1Gb PRAM with 6.4MB/s program BW". 2011 IEEE International Solid-State Circuits Conference. pp. 500–2. doi:10.1109/ISSCC.2011.5746415. ISBN 978-1-61284-303-2. S2CID 206996875.

- ^ A 20 nm 18V 8Gb PRAM (40MB/s 프로그램 대역폭 포함)웨이백 머신에서 2012년 1월 31일 아카이브 완료

- ^ 마이크론, 모바일 기기용 상변화 메모리 이용 가능 발표

- ^ Mellor, Chris (14 January 2014). "Micron: Hot DRAM. We don't need no steenkin' PCM". www.theregister.co.uk. The Register. Retrieved 14 January 2014.

- ^ Hruska, Joel (8 May 2014). "IBM demonstrates next-gen phase-change memory that's up to 275 times faster than your SSD". ExtremeTech.

- ^ Hruska, Joel (6 August 2014). "Western Digital's HGST division creates new phase-change SSD that's orders of magnitude faster than any NAND flash drive on the market". ExtremeTech.

(가) 1에서 0으로 또는 0에서 1로 변화합니다.비트의 상태를 변경하려면 축적된 전하를 제거해야 하며, 이는 플로팅 게이트에서 전자를 "흡입"하기 위해 상대적으로 큰

(가) 1에서 0으로 또는 0에서 1로 변화합니다.비트의 상태를 변경하려면 축적된 전하를 제거해야 하며, 이는 플로팅 게이트에서 전자를 "흡입"하기 위해 상대적으로 큰