x86

x86| 디자이너 | 인텔, AMD |

|---|---|

| 비트 | 16비트, 32비트 및 64비트 |

| 소개했다 | 1978(16비트), 1985(32비트), 2003(64비트) |

| 설계. | CISC |

| 유형 | 레지스터 – 메모리 |

| 인코딩 | 변수(1~15바이트) |

| 분기 | 상태코드 |

| 엔디안니스 | 작은 |

| 페이지크기 | 8086–i286: 없음 i386, i486: 4KB 페이지 P5Pentium: 4MB 페이지 추가 (레거시 PAE: 4KB→2MB) x86-64: 1GB 페이지 추가 |

| 확장자 | x87, IA-32, x86-64, x86-S, MMX, 3DNow!, SSE, MCA, ACPI, SSE2, NX 비트, SMT, SSE3, SSE3, SSE4, SSE4.2, AES-NI, CLMUL, RDRAND, SHA, MPX, SME, SGX, XOP, F16C, ADX, BMI, FMA, AVX, AVX2, AVX-VNI, AVX512, AVX10, VT-x, VT-d, AMD-V, AMD-Vi, TSX, ASF, TXT, APX |

| 열다. | 부분적으로. 일부 고급 기능의 경우 x86은 Intel의 라이센스가 필요할 수 있으며 x86-64는 AMD의 추가 라이센스가 필요할 수 있습니다.Pentium Pro 프로세서(및 NetBurst)는 시장에 출시된 지 21년이[1] 넘었기 때문에 특허 청구의 대상이 될 수 없습니다.따라서 x86 아키텍처의 i686 서브셋은 완전히 열려 있습니다. |

| 레지스터 | |

| 범용 |

|

| 부동점 | |

x86(80x86[2] 또는 8086 계열로도[3] 알려짐)은 인텔 8086 마이크로프로세서와 그 8088 변형을 기반으로 인텔이 처음 개발한 복합 명령어 세트 컴퓨터(CISC) 명령어 세트 아키텍처[a] 계열입니다.8086은 1978년 인텔의 8비트 8080 마이크로프로세서의 완전한 16비트 확장으로 소개되었으며, 메모리 분할은 일반 16비트 주소로 처리할 수 있는 것보다 더 많은 메모리를 처리하기 위한 솔루션으로 사용되었습니다."x86"이라는 용어는 인텔의 8086 프로세서의 여러 후계자들의 이름이 "86"으로 끝나기 때문에 생겨났습니다.구어적으로 그들의 이름은 "186", "286", "386", "486"이었습니다.

이 용어는 다른 여러 컴퓨터 하드웨어를 의미하므로 IBM PC 호환성과 동의어가 아닙니다.임베디드 시스템과 범용 컴퓨터는 PC 호환 시장이 시작되기 전에 x86 칩을 사용했는데,[b] 그 중 일부는 IBM PC(1981)가 데뷔하기 전에 사용되었습니다.

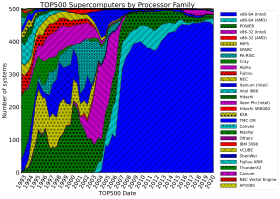

2022년[update] 6월 현재 판매되는 대부분의 데스크톱 및 노트북 컴퓨터는 x86 아키텍처 제품군을 기반으로 하며 스마트폰이나 태블릿과 같은 모바일 카테고리는 ARM이 지배하고 있습니다.[4]x86은 계산 집약적인 워크스테이션과 클라우드 컴퓨팅 부문에서 계속 우위를 점하고 있습니다.[5]2022년 6월 TOP500 목록에서 가장 빠른 슈퍼컴퓨터는 x86 ISA를 기반으로 AMD 에피크 CPU를 사용하여 구축된 [6]최초의 엑사스케일 시스템인 프론티어로, 2022년 5월 1 엑사플롭스 장벽을 깼습니다.[7]

개요

8088과 80286이 여전히 일반적으로 사용되던 1980년대와 1990년대 초반에 x86이라는 용어는 대개 8086 호환 CPU를 나타냅니다.그러나 오늘날 x86은 일반적으로 80386의 32비트 명령어 집합과의 이진 호환성을 의미합니다.이는 이 명령어 집합이 많은 현대 운영 체제에서 가장 낮은 공통분모의 것이 되었다는 사실과 1985년 80386이 도입된 이후 이 용어가 일반화되었기 때문입니다.

8086과 8088이 출시된 지 몇 년 후, 인텔은 야심적이지만 불운한 인텔 iAPX 432 프로세서의 "iAPX"가 시스템 레벨 접두사의 일종으로 적용된 [c]더 성공적인 8086 칩 제품군에서 시도되면서 이름 체계와 용어에 약간의 복잡성을 더했습니다.따라서 8087 및 8089와 같은 보조 프로세서와 더 간단한 인텔 전용 시스템 칩을 포함한 8086 시스템을 iAPX 86 시스템이라고 설명했습니다.[d][8][e]마이크로시스템 80이라는 제목 아래에 iRMX(운영 체제용), iSBC(싱글보드 컴퓨터용), iSBX(8086 아키텍처 기반 멀티모듈 보드용)라는 용어도 있었습니다.[9][10]하지만, 이 명명법은 꽤 일시적이었고, 1980년대 초 몇 년 동안 지속되었습니다.[f]

8086은 주로 임베디드 시스템과 소형 다중 사용자 또는 단일 사용자 컴퓨터를 위해 개발되었지만, 성공적인 8080 호환 Zilog Z80에 대한 대응으로 x86 제품군은 곧 기능과 처리 능력이 증가했습니다.[11]오늘날 x86은 고정식 컴퓨터와 휴대용 개인용 컴퓨터 모두에 널리 사용되며 미드레인지 컴퓨터, 워크스테이션, 서버 및 TOP500 목록의 대부분의 새로운 슈퍼컴퓨터 클러스터에도 사용됩니다.x86 운영 체제의 많은 목록을 포함한 많은 양의 소프트웨어가 x86 기반 하드웨어를 사용하고 있습니다.

그러나 최신 x86은 임베디드 시스템에서는 상대적으로 흔하지 않으며, 소형 저전력 애플리케이션(소형 배터리 사용)과 가전제품이나 장난감과 같은 저가의 마이크로프로세서 시장에서는 x86의 존재감이 크게 부족합니다.[g]RISC-V와 같은 단순한 RISC 아키텍처뿐만 아니라 간단한 8비트 및 16비트 기반 아키텍처도 일반적이지만 x86 호환 VIA C7, VIA Nano, AMD의 Geode, Athlon Neo 및 Intel Atom은 일부 상대적으로 저전력 및 저비용 세그먼트에 사용되는 32비트 및 64비트 설계의 예입니다.

인텔을 포함한 여러 시도가 있었는데, 최초의 간단한 8비트 마이크로프로세서에서 직접 설계된 "우아한" x86 아키텍처의 시장 지배력을 종식시키기 위한 것이었습니다.이러한 예로는 iAPX 432(원래 Intel 8800으로[12] 명명된 프로젝트), Intel 960, Intel 860 및 Intel/Hewlett-Packard Itanium 아키텍처가 있습니다.그러나 x86 마이크로아키텍처, 회로 및 반도체 제조의 지속적인 개선으로 인해 많은 세그먼트에서 x86을 대체하기가 어려워질 것입니다.AMD의 x86 64비트 확장(Intel이 호환 가능한 설계로 대응)[13]과 최신 멀티코어 CPU 형태의 x86 칩의 확장성은 기존 업계 표준의 지속적인 개선이 완전히 새로운 아키텍처로부터의 경쟁에 어떻게 저항할 수 있는지를 보여주는 예입니다.[14]

연표

이 기사는 검증을 위해 추가적인 인용이 필요합니다. 찾기 :– · · · (2020년 3월)(이 를 및 |

아래 표는 x86 계열의 다양한 아키텍처를 구현하는 프로세서 모델과 모델 시리즈를 시간 순서대로 나열한 것입니다.각 라인 항목은 크게 개선되거나 상업적으로 성공한 프로세서 마이크로아키텍처 디자인을 특징으로 합니다.

| 시대 | 서론 | 저명한 CPU 모델 | 주소공간 | 주목할만한 특징 | |||

|---|---|---|---|---|---|---|---|

| 선형 | 버추얼 | 물리적. | |||||

| x86-16 | 첫 번째 | 1978 | 인텔 8086, 인텔 8088 (1979) | 16비트 | NA | 20비트 | 16비트 ISA, IBM PC(8088), IBM PC/XT(8088) |

| 1982 | 인텔 80186, 인텔 80188 NEC V20/V30 (1983) | 8086-2 ISA, 내장(80186/80188) | |||||

| 두번째 | 인텔 80286 및 클론 | 30비트 | 24비트 | 보호 모드, IBM PC/XT 286, IBM PC/AT | |||

| IA-32 | 3번째 | 1985 | Intel 80386, AMD Am386 (1991) | 32비트 | 46비트 | 32비트 | 32비트 ISA, 페이징, IBM PS/2 |

| 4번째(파이프라인, 캐시) | 1989 | 인텔 80486 CyrixCx486S, DLC (1992) AMD Am486 (1993), Am5x86 (1995) | 파이프라이닝, 온다이 x87 FPU(486DX), 온다이 캐시 | ||||

| 5번째 (슈퍼스칼라) | 1993 | 인텔 펜티엄, 펜티엄 MMX (1996) | 슈퍼스칼라, 64비트 데이터 버스, 더 빠른 FPU, MMX(Pentium MMX), APIC, SMP | ||||

| 1994 | 넥스젠 Nx586 AMD 5k86/K5 (1996) | 이산형 마이크로아키텍처 (µ-op 번역) | |||||

| 1995 | 사이릭스 Cx5x86 Cyrix 6x86/MX(1997)/MII(1998) | 동적 실행 | |||||

| 6번째 (PAE, µ-op 번역) | 1995 | 인텔 펜티엄 프로 | 36비트 (PAE) | µ-op 변환, 조건부 이동 명령, 동적 실행, 추측 실행, 3-way x86 슈퍼스칼라, 슈퍼스칼라 FPU, PAE, on-chip L2 캐시 | |||

| 1997 | 인텔 펜티엄 II, 펜티엄 III (1999) Celeron (1998), Xeon (1998) | 온패키지(Pentium II) 또는 온다이(Celeron) L2 캐시, SSE(Pentium III), 슬롯 1, 소켓 370 또는 슬롯 2(Xeon) | |||||

| 1997 | AMD K6/K6-2(1998)/K6-III(1999) | 32비트 | 3D Now!, 3-레벨 캐시 시스템 (K6-III) | ||||

| 향상된 플랫폼 | 1999 | AMD 애슬론 애슬론 XP/MP (2001) 듀론 (2000) 셈프론 (2004) | 36비트 | MMX+, 3DNow!+, 이중 펌프 버스, 슬롯 A 또는 소켓 A | |||

| 2000 | 트란스메타 크루소 | 32비트 | CMS 구동 x86 플랫폼 프로세서, VLIW-128 코어, 온다이 메모리 컨트롤러, 온다이 PCI 브리지 로직 | ||||

| 인텔 펜티엄 4 | 36비트 | SSE2, HTT (Northwood), NetBurst, 쿼드-펌프 버스, Trace Cache, 소켓 478 | |||||

| 2003 | 인텔 펜티엄 M 인텔 코어 (2006) 펜티엄 듀얼 코어 (2007) | µ-op 퓨전, XD 비트 (Dothan) (인텔 코어 "요나") | |||||

| 트랜스메타 에피슨 | CMS 6.0.4, VLIW-256, NX 비트, HT | ||||||

| IA-64 | 64비트 전환 1999–2005 | 2001 | 인텔 아이테니엄 (2001-2017) | 52비트 | 64비트 EPIC 아키텍처, 128비트 VLIW 명령 번들, x86 OS 및 x86 애플리케이션을 지원하는 온다이 하드웨어 IA-32 H/W(초기 세대), x86 애플리케이션을 지원하는 소프트웨어 IA-32 EL(Itanium 2), Itanium 레지스터 파일이 x86 레지스터에 재매핑됨 | ||

| x86-64 | 64비트 확장 2001년 이래로 | x86-64는 x86의 64비트 확장 아키텍처이며, 레거시 모드는 전체 x86 아키텍처를 그대로 보존합니다.x86-64 프로세서의 기본 아키텍처: 64비트 모드에 상주하고, 세그먼트화 시 액세스 모드가 부족하며, 64비트 아키텍처 허용 선형 주소 공간을 제공합니다. 64비트 모드와 함께 호환성 모드에 상주하는 적응된 IA-32 아키텍처는 대부분의 x86 애플리케이션을 지원합니다. | |||||

| 2003 | 애슬론 64/FX/X2 (2005), 옵테론 Sempron (2004)/X2 (2008) 튜리온64(2005)/X2(2006) | 40비트 | AMD64(일부 Sempron 프로세서는 제외), 온다이 메모리 컨트롤러, HyperTransport, 온다이 듀얼 코어(X2), AMD-V(Athlon 64 Orleans), 소켓 754/939/940 또는 AM2 | ||||

| 2004 | 펜티엄4 (프레스콧) Celeron D, Pentium D (2005) | 36비트 | EM64T(펜티엄 4 및 셀러론 D의 일부 모델에서 활성화됨), SSE3, 2세대.NetBurst 파이프라이닝, 듀얼 코어(온다이:펜티엄 D 8xx, 온칩: 펜티엄 D 9xxx), 인텔 VT(펜티엄 46x2), 소켓 LGA 775 | ||||

| 2006 | 인텔 코어 2 펜티엄 듀얼 코어 (2007) Celeron 듀얼 코어 (2008) | 인텔 64 (<== EM64T), SSSE3 (65nm), 와이드 동적 실행, µ-op 퓨전, 16비트 및 32비트 모드의 매크로-op 퓨전, 온-칩 쿼드 코어 (Core 2 Quad), 스마트 공유 L2 캐시 (Intel Core 2 "Merom") | |||||

| 2007 | AMD 페놈/II (2008) 애슬론 2세 (2009) 투리온 II (2009) | 48비트 | 단일 쿼드 코어(X4)/트리플 코어(X3), SSE4a, RVI(Rapid Virtualization Indexing), HyperTransport 3, AM2+ 또는 AM3 | ||||

| 2008 | 인텔 코어 2 (45nm) | 40비트 | SSE 4.1 | ||||

| 인텔 아톰 | 넷북 또는 저전력 스마트 기기 프로세서, P54C 코어 재사용 | ||||||

| 인텔 코어 i7 코어 i5 (2009) 코어 i3 (2010) | QuickPath, on-chip GMCH(Clarkdale), SSE4.2, 가상화를 위한 확장 페이지 테이블(EPT), 64비트 모드의 매크로-op 퓨전,[15][16] (Nehalem 마이크로아키텍처를 사용한 Intel Xeon "Bloomfield") | ||||||

| 비아 나노 | 하드웨어 기반 암호화; 적응형 전원 관리 | ||||||

| 2010 | AMD FX | 48비트 | 옥타코어, CMT(클러스터 멀티 스레드), FMA, OpenCL, AM3+ | ||||

| 2011 | AMD APUA 및 E 시리즈(라노) | 40비트 | 온다이 GPGPU, PCI Express 2.0, 소켓 FM1 | ||||

| AMD APUC, E 및 Z 시리즈(Bobcat) | 36비트 | 저전력 스마트기기 APU | |||||

| 인텔 코어 i3, 코어 i5 및 코어 i7 (샌디브릿지/아이비브릿지) | 내부 Ring 연결, 디코딩된 µ-op 캐시, LGA 1155 소켓 | ||||||

| 2012 | AMD APUA 시리즈(불도저, 트리니티 이상) | 48비트 | AVX, Bulldozer 기반 APU, Socket FM2 또는 Socket FM2+ | ||||

| 인텔 Xeon Phi (기사 코너) | XEON 기반 시스템용 PCI-E 애드온 카드 보조 프로세서, Manycore Chip, In-order P54C, VPU(512비트 SSE), LRBni 명령어(8x64비트) | ||||||

| 2013 | AMD 재규어 (애슬론, 셈프론) | SoC, 게임 콘솔 및 저전력 스마트 기기 프로세서 | |||||

| 인텔 실버몬트 (Atom, Celeron, Pentium | 36비트 | SoC, 저전력/초저전력 스마트 기기 프로세서 | |||||

| 인텔 코어 i3, 코어 i5 및 코어 i7 (하스웰/브로드웰) | 39비트 | AVX2, FMA3, TSX, BMI1 및 BMI2 지침, LGA 1150 소켓 | |||||

| 2015 | 인텔 브로드웰-U (Intel Core i3, Core i5, Core i7, Core M, Pentium, Celeron) | SoC, 온칩 Broadwell-UPCH-LP (멀티칩 모듈) | |||||

| 2015–2020 | 인텔 스카이레이크/캐비레이크/캐넌레이크/커피레이크/로켓레이크 (Intel Pentium/Celeron Gold, Core i3, Core i5, Core i7, Core i9) | 46비트 | AVX-512 (캐넌 레이크-U 및 Skylake의 워크스테이션/서버 모델에 한함) | ||||

| 2016 | 인텔 Xeon Phi (기사단 상륙) | 48비트 | Xeon 시스템용 많은 코어 CPU 및 보조 프로세서, Airmont(Atom) 기반 코어 | ||||

| 2016 | AMD 브리스톨 리지 (AMD(프로) A6/A8/A10/A12) | 통합 FCH on die, SoC, AM4 소켓 | |||||

| 2017 | AMD 라이젠 시리즈/AMD 에피크 시리즈 | AMD의 SMT 온칩 다중 다이 구현 | |||||

| 2017 | 자오신 우다오커우 (KX-5000, KH-200000) | Zhaoxin의 첫 번째 새로운 x86-64 아키텍처 | |||||

| 2018–2021 | 인텔 써니 코브(Ice Lake-U and Y), 사이프러스 코브(Rocket Lake) | 57비트 | 소비자 부문을 위한 인텔 최초의 AVX-512 구현벡터 신경망 명령어(Vector Neural Network Instructions, VNNI) 추가 | ||||

| 2020 | 인텔 윌로우 코브 (타이거레이크-Y/U/H) | 이중 링 인터커넥트 아키텍처, 업데이트된 가우스 신경 가속기(GNA2), 새로운 AVX-512 벡터 교차점 명령, 제어-흐름 강제 기술(CET) 추가 | |||||

| 2021 | 인텔 올더 레이크 | 성능(Golden Cove) 및 효율성 코어(Gracemont)를 갖춘 하이브리드 디자인, PCIe Gen5 및 DDR5 지원, 업데이트된 GNA3(Gaussian Neural Accelerator) | |||||

| 시대 | 서론 | 저명한 CPU 모델 | 주소공간 | 주목할만한 특징 | |||

역사

설계자 및 제조업체

IBM, VIA, NEC,[h] AMD, TI, STM, 후지쯔, OKI, Siemens, Cyrix, Intersil, C&T, NexGen, UMC, DM&P와 같은 회사들은 개인용 컴퓨터와 임베디드 시스템을 위한 x86 프로세서(CPU)를 설계하거나 제조하기[i] 시작했습니다.x86 또는 x87 프로세서를 설계 또는 제조한 다른 회사로는 ITT Corporation, National Semiconductor, ULSI System Technology, Weitek 등이 있습니다.

이와 같은 x86 구현은 단순한 복사본이 아니라 내부 마이크로아키텍처와 전자 및 물리적 수준에서 각기 다른 솔루션을 사용하는 경우가 많았습니다.초기 호환 마이크로프로세서는 16비트인 반면 32비트 디자인은 훨씬 나중에 개발되었습니다.개인용 컴퓨터 시장에서 실제 수량은 1990년경부터 i386 및 i486 호환 프로세서와 함께 등장하기 시작했으며 종종 인텔의 오리지널 칩과 유사한 이름을 붙였습니다.

완전한 파이프라인을 갖춘 i486 이후, 1993년 인텔은 새로운 슈퍼스칼라 x86 디자인에 펜티엄 브랜드명을 도입했습니다.이제 x86 명명 방식이 법적으로 허용됨에 따라, 다른 x86 공급업체들은 x86 호환 제품의 다른 이름을 선택해야 했고, 처음에는 일부 공급업체들이 Cyrix와 협력하여 5x86(M1) 및 6x86MX(MII) 라인의 Cyrix 디자인을 계속 개발했습니다.이것은 추측 실행을 가능하게 하기 위해 레지스터 이름을 변경하는 최초의 x86 마이크로프로세서였습니다.

한편 AMD는 내부적으로 AMD의 초기 29K RISC 설계를 기반으로 한 지연된 5k86(K5)을 설계 및 제조했습니다. NexGen의 Nx586과 유사하게 전용 파이프라인 스테이지가 x86 명령어를 균일하고 쉽게 처리할 수 있는 마이크로 연산으로 디코딩하는 전략을 사용했습니다.오늘날까지 대부분의 x86 디자인의 기초로 남아있는 방법.

이러한 마이크로프로세서의 일부 초기 버전은 방열 문제가 있었습니다.6x86은 몇 가지 사소한 호환성 문제에도 영향을 받았으며, Nx586은 부동 소수점 장치(FPU)와 핀 호환성이 부족한 반면, K5는 (결국) 출시되었을 때 다소 실망스러운 성능을 보였습니다.

K5가 펜티엄 호환성이 매우 우수하고 6x86이 정수 코드의 펜티엄보다 훨씬 빠르다는 사실에도 불구하고 펜티엄 시리즈의 대안에 대한 고객의 무지는 이러한 디자인이 상대적으로 성공적이지 못한 원인이 되었습니다.[j]AMD는 나중에 아주 성공적인 애슬론과 옵테론에게 자리를 내준 K6 프로세서 세트를 가지고 강력한 경쟁자로 성장할 수 있었습니다.

센타우르 테크놀로지(구 IDT), 라이즈 테크놀로지, 트랜스메타 등 다른 경쟁사들도 있었습니다.센타우르사가 설계한 VIA Technologies의 에너지 효율적인 C3 및 C7 프로세서는 2005년 출시 이후 수년간 판매되었습니다.센타우르의 2008년 디자인인 VIA Nano는 슈퍼스칼라 및 추측 실행 기능을 갖춘 최초의 프로세서였습니다.인텔이 P5 펜티엄 이후 최초의 "주문형" 프로세서인 인텔 아톰을 선보이면서 (2008년) 거의 동시에 선보였습니다.

수년간 수많은 추가 및 확장이 원래 x86 명령어 세트에 추가되었으며 거의 일관되게 완전한 하위 호환성을 갖추고 있습니다.[k]아키텍처 제품군은 Intel, Cyrix, AMD, VIA Technologies 및 기타 많은 회사의 프로세서에 구현되었으며, Zet SoC 플랫폼(현재 비활성화 상태)과 같은 개방형 구현도 있습니다.[17]그럼에도 불구하고 이 중 인텔, AMD, VIA Technologies, DM&P Electronics만이 x86 아키텍처 라이선스를 보유하고 있으며, 이 중 처음 두 개만이 적극적으로 현대적인 64비트 디자인을 생산하여 x86 프로세서에서 인텔과 AMD의 "듀오폴리"라고 불리는 것으로 이어졌습니다.

그러나 2014년에 중국 회사와 VIA Technologies의 합작 회사인 상하이에 본사를 둔 중국 회사 Zhaoxin은 데스크톱 및 노트북용 VIA 기반 x86 프로세서를 설계하기 시작했습니다.최신 x86 프로세서[18] 제품군(예: KX-7000)은 [19]AMD 또는 인텔 칩만큼 빠르지는 않지만 여전히 최신 기술인 2021년에 출시될 예정이었지만 2022년 3월 현재 출시는 이루어지지 않았습니다.[20]

16비트 및 32비트 아키텍처에서 64비트 아키텍처까지 지원

명령어 집합 아키텍처가 두 배로 확장되어 단어 크기가 더 커졌습니다.1985년에.인텔은 32비트 80386(이후 i386으로 알려짐)을 출시하였는데, 이는 컴퓨터의 초기 16비트 칩(일반적으로 임베디드 시스템에는 없음)을 이후 몇 년 동안 점진적으로 대체하였습니다. 이 확장된 프로그래밍 모델은 원래 i386 아키텍처라고 불렸지만(첫 번째 구현과 같이) 인텔은 나중에 IA-32라고 이름 붙였습니다.(관련 없는) IA-64 아키텍처를 사용하고 있습니다.

1999년부터 2003년까지 AMD는 이 32비트 아키텍처를 64비트로 확장했으며 초기 문서에서는 x86-64, 나중에는 AMD64로 지칭했습니다.인텔은 곧 IA-32e라는 이름으로 AMD의 아키텍처 확장을 채택했고, 나중에 EM64T라는 이름을 사용했고, 마침내 인텔 64를 사용했습니다.마이크로소프트와 썬 마이크로시스템즈/오라클은 "x64"라는 용어를 사용하며, 많은 리눅스 배포판과 BSD도 "amd64"라는 용어를 사용합니다.예를 들어 마이크로소프트 윈도우는 32비트 버전을 "x86"으로, 64비트 버전을 "x64"로 지정하며, 64비트 윈도우 버전의 설치 파일은 "AMD64"라는 디렉터리에 넣어야 합니다.[21]

2023년에 Intel은 x86-S(Simpleization의 약자)라는 아키텍처에 대한 대대적인 변경을 제안했습니다. 이는 레거시 실행 모드 및 명령에 대한 지원을 제거하는 것을 목표로 합니다.이 제안을 구현하는 프로세서는 롱 모드에서 직접 실행을 시작하고 64비트 운영 체제만 지원합니다. 32비트 코드는 링 3에서 실행되는 사용자 응용 프로그램에 대해서만 지원되며 롱 모드와 동일한 단순화된 분할을 사용합니다.[22][23]

건축물의 기본적 특성

x86 아키텍처는 가변적인 명령어 길이로, 하위 호환성에 중점을 둔 "CISC" 디자인이 주를 이룹니다.명령어 집합은 일반적인 CISC가 아니라 기본적으로 간단한 8비트 8008 및 8080 아키텍처의 확장 버전입니다.바이트 주소 지정이 활성화되고 단어가 리틀 엔디언 바이트 순서로 메모리에 저장됩니다.정렬되지 않은 주소에 대한 메모리 액세스는 거의 모든 명령에 대해 허용됩니다.정수 산술 및 메모리 주소(또는 오프셋)의 최대 네이티브 크기는 아키텍처 생성에 따라 16, 32 또는 64비트입니다(새로운 프로세서에는 더 작은 정수도 직접 지원됨).여러 스칼라 값은 다음과 같이 이후 세대에 존재하는 SIMD 유닛을 통해 동시에 처리될 수 있습니다.[l]즉시 어드레싱 오프셋 및 즉시 데이터는 a가 -128인 경우 자주 발생하는 경우 또는 컨텍스트에 대해 8비트 양으로 표현할 수 있습니다.127 범위면 충분합니다.따라서 일반적인 명령어의 길이는 2바이트 또는 3바이트입니다(일부는 훨씬 더 길지만 일부는 단일 바이트입니다).

인코딩 공간을 더 절약하기 위해 대부분의 레지스터는 3비트 또는 4비트를 사용하여 opcode로 표현되며 후자는 64비트 모드에서 opcode 접두사를 통해 표현되지만 명령어에 대한 피연산자는 많아야 메모리 위치가 될 수 있습니다.[m]그러나 이 메모리 피연산자는 대상(또는 소스와 대상이 결합된)일 수도 있고, 다른 피연산자(소스)는 레지스터 또는 즉시일 수도 있습니다.다른 요소들 중에서, 이것은 8비트 시스템과 경쟁하고 명령어 캐시 메모리의 효율적인 사용을 가능하게 하는 코드 크기의 원인이 됩니다.상대적으로 적은 수의 일반 레지스터(또한 8비트 조상으로부터 상속됨)는 레지스터-상대 어드레싱(즉각 오프셋이 작음)을 피연산자, 특히 스택에서 액세스하는 중요한 방법으로 만들었습니다.따라서 상위 캐시에서 액세스된 데이터를 사용할 수 있는 대부분의 환경에서 레지스터 액세스, 즉 1주기 명령 처리량만큼 빠르게 액세스하는 데 많은 작업이 투입되었습니다.

부동 소수점 및 SIMD

8087은 80비트 내부 레지스터를 가진 전용 부동 소수점 프로세서로 오리지널 8086용으로 개발되었습니다.이 마이크로프로세서는 그 후 확장된 80387로 발전했고, 이후 프로세서는 메인 프로세서와 동일한 마이크로프로세서에 이 기능의 하위 호환 버전을 통합했습니다.이 외에도 현대 x86 디자인에는 SIMD 유닛(아래 SSE 참조)도 포함되어 있는데, 명령어는 128비트 워드에서 병렬로 작동하며, 각각 2개 또는 4개의 부동 소수점 숫자(각각 64비트 또는 32비트 너비)를 포함하거나, 2개, 4개, 8개 또는 16개의 정수(각각 64비트, 32비트, 16비트 너비)를 포함합니다.

넓은 SIMD 레지스터가 있다는 것은 기존 x86 프로세서가 단일 명령어에 최대 128비트의 메모리 데이터를 로드하거나 저장할 수 있으며, 전체 128비트 양에 대해 비트 와이즈 연산(정수 연산은[n] 아니지만)을 병렬로 수행할 수 있다는 것을 의미합니다.인텔의 Sandy Bridge 프로세서는 AVX(Advanced Vector Extensions) 명령어를 추가하여 SIMD 레지스터를 256비트로 넓혔습니다.나이츠 코너 제온 파이 프로세서가 구현한 인텔 이니셜 매니 코어 명령어와 나이츠 랜딩 제온 파이 프로세서와 스카이레이크-X 프로세서가 구현한 AVX-512 명령어는 512비트 너비의 SIMD 레지스터를 사용합니다.

현재 구현

실행 중에, 현재의 x86 프로세서들은 대부분의 명령어들을 마이크로 오퍼레이션들이라고 불리는 작은 조각들로 나누기 위해 몇 가지 추가적인 디코딩 단계들을 사용합니다.그런 다음 x86-semantics를 준수하여 버퍼링하고 스케줄링하는 제어 장치로 전달되어 부분적으로 병렬적으로 여러 개의 (전문화된) 실행 장치 중 하나에 의해 실행될 수 있습니다.따라서, 이러한 최신 x86 디자인은 파이프라인화되고, 슈퍼스칼라이며, (가지 예측, 레지스터 이름 변경, 메모리 의존성 예측을 통해) 순서를 벗어나 추측적인 실행이 가능하며, 이는 동시에 다수의 (부분적 또는 완전한) x86 명령을 실행할 수 있음을 의미합니다.그리고 반드시 명령어 스트림에 주어진 것과 같은 순서일 필요는 없습니다.[24]일부 Intel CPU(Xeon Foster MP, 일부 Pentium 4, 일부 Nehalem 및 이후 Intel Core 프로세서)와 AMD CPU(Zen부터 시작)도 코어당 2개의 스레드로 동시 멀티스레딩이 가능합니다(Xeon Phi는 코어당 4개의 스레드가 있음).일부 Intel CPU는 TSX(Transactional Memory)를 지원합니다.

1990년대 중반에 도입되었을 때, 이 방법은 때때로 "RISC 코어" 또는 "RISC 변환"이라고 불렸는데, 이는 부분적으로 마케팅 이유 때문이기도 하지만 이러한 마이크로 오퍼레이션이 특정 유형의 RISC 명령어와 일부 속성을 공유하기 때문이기도 합니다.그러나 (1950년대 이후 사용된) 전통적인 마이크로코드 또한 본질적으로 많은 동일한 속성을 공유합니다. 새로운 방법은 현재 마이크로 운영으로의 변환이 비동기적으로 발생한다는 점에서 주로 다릅니다.실행 유닛을 디코드 단계와 동기화할 필요가 없으므로 (버퍼링된) 코드 스트림을 더 많이 분석할 수 있는 가능성이 열리며, 따라서 병렬로 수행할 수 있는 작업을 탐지할 수 있으며, 동시에 하나 이상의 실행 유닛을 공급할 수 있습니다.

또한 최신 프로세서는 적절한 경우 그 반대의 작업을 수행합니다. 즉, 특정 x86 시퀀스를 실행 모델에 더 적합한 더 복잡한 마이크로 op으로 결합하여 더 빠르게 실행하거나 더 적은 머신 리소스를 사용하여 실행할 수 있습니다.

성능 향상을 시도하는 또 다른 방법은 디코딩된 마이크로 연산을 캐시하는 것입니다. 그러면 프로세서가 다시 디코딩하는 대신 특수 캐시에서 디코딩된 마이크로 연산에 직접 액세스할 수 있습니다.Intel은 NetBurst 마이크로아키텍처(Pentium 4 프로세서용)와 디코딩된 스트림 버퍼(Sandy Bridge 이후 코어 브랜드 프로세서용)에서 실행 추적 캐시 기능을 사용하여 이 접근 방식을 적용했습니다.[25]

트랜스메타는 크루소 x86 호환 CPU에서 완전히 다른 방식을 사용했습니다.그들은 적시 번역을 사용하여 x86 명령어를 CPU의 기본 VLIW 명령어 세트로 변환했습니다.Transmeta는 CPU가 보다 전통적인 x86 구현의 복잡한 디코딩 단계를 포기할 수 있기 때문에 이러한 접근 방식이 보다 전력 효율적인 설계를 가능하게 한다고 주장했습니다.

주소 지정 모드

16비트 프로세서 모드의 어드레싱 모드는 공식으로 요약할 수 있습니다.[26][27]

32비트 x86 프로세서 모드의[28] 어드레싱 모드는 다음 공식으로 요약할 수 있습니다.[29]

64비트 프로세서 모드의 어드레싱 모드는 공식으로 요약할 수 있습니다.[29]

64비트 코드(RIP + displacement, 여기서 RIP는 명령어 포인터 레지스터)의 명령어 상대 주소 지정은 위치 독립 코드(일부 운영 체제의 공유 라이브러리에서 사용됨)의 구현을 단순화합니다.[30]

8086은 64KB의 8비트(또는 32K 워드의 16비트) I/O 공간과 64KB(한 세그먼트) 스택이 컴퓨터 하드웨어에서 지원됩니다.단어(2바이트)만 스택에 푸시할 수 있습니다.스택은 숫자가 더 낮은 주소로 갈수록 커지며,SS:SP가 가장 최근에 누른 항목을 가리킵니다.256개의 인터럽트가 있으며, 이 인터럽트는 하드웨어와 소프트웨어 모두에서 호출할 수 있습니다.인터럽트는 스택을 사용하여 반송 주소를 저장함으로써 캐스케이드할 수 있습니다.

x86 레지스터

16비트

원래 인텔 8086과 8088은 14개의 16비트 레지스터를 가지고 있습니다.그 중 4개(AX, BX, CX, DX)는 범용 레지스터(GPR)이지만 각각은 추가적인 목적을 가질 수 있습니다. 예를 들어 CX만 루프 명령과 함께 카운터로 사용할 수 있습니다.각 바이트는 두 개의 개별 바이트로 액세스할 수 있습니다(따라서 BX의 높은 바이트는 BH로 액세스하고 낮은 바이트는 BL로 액세스할 수 있습니다).두 개의 포인터 레지스터에는 특별한 역할이 있습니다. SP(스택 포인터)는 스택의 "맨 위"를 가리키며 BP(베이스 포인터)는 스택의 다른 위치를 가리키는데 사용되는 경우가 많습니다. 일반적으로 로컬 변수 위를 가리키는 경우(프레임 포인터 참조).레지스터 SI, DI, BX 및 BP는 주소 레지스터이며 배열 인덱싱에 사용될 수도 있습니다.

메모리 주소를 형성하는 데는 4가지 가능한 '세그먼트 레지스터'(CS, DS, SS 및 ES) 중 하나가 사용됩니다.원래 8086/8088/80186/80188에서 모든 주소는 세그먼트 레지스터와 범용 레지스터 중 하나로 작성되었습니다.예를 들어 ds:si는 16비트가 아닌 20비트 주소 지정을 허용하기 위해 [16 * ds + si]로 형성된 주소에 대한 표기법입니다.당시에는 특정 조합만 지원되었습니다.

플래그 레지스터에는 운반 플래그, 오버플로 플래그 및 제로 플래그와 같은 플래그가 포함됩니다.마지막으로 명령 포인터(IP)는 메모리에서 가져온 다음 실행될 다음 명령을 가리킵니다. 이 레지스터는 프로그램에서 직접 액세스(읽기 또는 쓰기)할 수 없습니다.[31]

Intel 80186 및 80188은 기본적으로 각각 업그레이드된 8086 또는 8088 CPU이며, 온칩 주변 장치가 추가되었으며 8086 및 8088과 동일한 CPU 레지스터가 있습니다(주변 장치 인터페이스 레지스터 외에도).

8086, 8088, 80186 및 80188은 옵션 부동 소수점 보조 프로세서인 8087을 사용할 수 있습니다.8087은 CPU의 일부로 프로그래머에게 나타나며 st(0)에서 st(7)에 8개의 80비트 와이드 레지스터를 추가합니다. 각 레지스터는 숫자 데이터를 32비트, 64비트 또는 80비트 부동 소수점, 16비트, 32비트 또는 64비트(이진) 정수, 80비트 팩킹 10진수 중 하나의 형식으로 저장할 수 있습니다.[10]: S-6, S-13..S-15 또한 fstsw 명령어를 통해 접근 가능한 자체 16비트 상태 레지스터를 가지고 있으며, 일부 비트를 일반 FLAGS에 복사하여 분기에 사용하는 것이 일반적입니다.[32]

Intel 80286에서는 보호 모드를 지원하기 위해 3개의 특수 레지스터가 디스크립터 테이블 주소(GDTR, LDTR, IDTR)를 보유하고 있으며 작업 전환을 위해 4번째 작업 레지스터(TR)가 사용됩니다.80287은 80286의 부동소수점 코프로세서이며, 8087과 동일한 레지스터를 가지고 있으며, 동일한 데이터 형식을 가지고 있습니다.

32비트

32비트 80386 프로세서의 등장으로 세그먼트 레지스터가 아닌 16비트 범용 레지스터, 베이스 레지스터, 인덱스 레지스터, 명령어 포인터, 플래그 레지스터가 32비트로 확장되었습니다.이 명명법은 x86 어셈블리 언어로 레지스터 이름 앞에 "E"("확장")를 붙여 이를 나타냈습니다.따라서 AX 레지스터는 새로운 32비트 EAX 레지스터의 하위 16비트, SI는 ESI의 하위 16비트 등에 해당합니다.범용 레지스터, 베이스 레지스터, 인덱스 레지스터는 모두 어드레싱 모드에서 기본으로 사용할 수 있으며 스택 포인터를 제외한 모든 레지스터는 어드레싱 모드에서 인덱스로 사용할 수 있습니다.

두 개의 새로운 세그먼트 레지스터(FS 및 GS)가 추가되었습니다.레지스터, 명령어 및 피연산자의 수가 많아지면서 머신 코드 형식이 확장되었습니다.이전 버전과의 호환성을 제공하기 위해 실행 코드가 있는 세그먼트는 16비트 또는 32비트 명령어를 포함하는 것으로 표시할 수 있습니다.특수 접두사를 사용하면 16비트 세그먼트에 32비트 명령을 포함하거나 그 반대의 경우도 가능합니다.

80386은 옵션인 부동소수점 코프로세서인 80387을 가지고 있었습니다. 8087과 80287처럼 [33]8개의 80비트 와이드 레지스터(st(0)80386은 80287 코프로세서도 사용할 수 있습니다.[34]부동 소수점 처리 장치(FPU)는 80486 및 모든 후속 x86 모델과 함께 온칩으로 통합됩니다.

Pentium MMX는 8개의 64비트 MMX 정수 벡터 레지스터(MM0 ~ MM7)를 추가했으며, 이들 레지스터는 80비트 폭의 FPU 스택과 하위 비트를 공유합니다.[35]인텔은 펜티엄 III를 통해 32비트 스트리밍 SIMD 확장(SSE) 제어/상태 레지스터(MXCSR)와 8개의 128비트 SSE 부동 소수점 레지스터(XMM0 ~ XMM7)를 추가했습니다.[36]

64비트

AMD Opteron 프로세서를 시작으로 x86 아키텍처는 16비트에서 32비트로 확장된 방식과 유사한 방식으로 32비트 레지스터를 64비트 레지스터로 확장했습니다.R-prefix("register"용)는 64비트 레지스터(RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP, RFLAGS, RIP)를 식별하며, x86-64를 생성할 때 8개의 추가 64비트 일반 레지스터(R8–R15)도 도입되었습니다.또한 8개의 SSE 벡터 레지스터(XMM8–XMM15)가 추가되었습니다.그러나 이러한 확장은 롱 모드에서만 사용할 수 있는 두 가지 모드 중 하나인 64비트 모드에서만 사용할 수 있습니다.주소 지정이 64비트로 확장되고, 가상 주소가 64비트로 확장되고(가상 주소에서 모드 비트를 허용하지 않기 위해), 기타 선택기 세부 정보가 대폭 축소된 것을 제외하고는 주소 지정 모드가 32비트 모드에서 대폭 변경되지 않았습니다.또한 일부 운영 체제의 공유 라이브러리에서 사용되는 위치 독립 코드의 구현을 용이하게 하기 위해 RIP(명령 포인터)와 관련된 메모리 참조를 허용하는 어드레싱 모드가 추가되었습니다.

128비트

SIMD 레지스터 XMM0–XMM15(AVX-512가 지원되는 경우 XMM0–XMM31).

256비트

SIMD 레지스터 YMM0–YMM15(AVX-512가 지원되는 경우 YMM0–YMM31).각 YMM 레지스터의 절반 아래 부분은 해당 XMM 레지스터에 맵을 기록합니다.

512비트

SIMD 레지스터 ZMM0-ZMM31. 각 ZMM 레지스터의 절반 아래에 해당하는 YMM 레지스터에 맵을 기록합니다.

잡/특수목적

보호 모드를 갖는 x86 프로세서, 즉 80286 이상의 프로세서는 또한 3개의 디스크립터 레지스터(GDTR, LDTR, IDTR)와 태스크 레지스터(TR)를 갖습니다.

32비트 x86 프로세서(80386부터 시작)에는 컨트롤 레지스터(CR0~4, 64비트 전용 CR8), 디버그 레지스터(DR0~3, 플러스 6, 7), 테스트 레지스터(TR3~7, 80486만), 모델별 레지스터(MSR, 펜티엄과[o] 함께 표시됨) 등 다양한 특수/기타 레지스터도 포함되어 있습니다.

AVX-512에는 벡터 레지스터의 요소를 선택하기 위한 8개의 추가 64비트 마스크 레지스터 K0-K7이 있습니다.벡터 레지스터 및 요소 폭에 따라, 마스크 레지스터의 일부 비트만 주어진 명령에 의해 사용될 수 있습니다.

목적

메인 레지스터(명령어 포인터를 제외하고)는 32비트와 64비트 버전의 명령어 집합에서 "범용"이며 어떤 용도로도 사용할 수 있지만, 원래는 다음과 같은 용도로 사용되는 것으로 계획되어 있었습니다.

- AL/AH/AX/EAX/RAX: 축전지

- CL/CH/CX/ECX/RCX: 카운터(루프 및 문자열과 함께 사용)

- DL/DH/DX/EDX/RDX: 누산기의 정밀도 확장(예: 32비트 코드의 64비트 정수 연산을 위해 32비트 EAX와 EDX를 결합)

- BL/BH/BX/EBX/RBX: 기본 인덱스(배열과 함께 사용)

- SP/ESP/RSP: 스택의 최상위 주소에 대한 스택 포인터입니다.

- BP/EBP/RBP: 현재 스택 프레임의 주소를 보유하기 위한 스택 베이스 포인터.

- SI/ESI/RSI: 문자열 연산을 위한 소스 인덱스입니다.

- DI/EDI/RDI: 문자열 작업의 대상 인덱스입니다.

- IP/EIP/RIP: 명령 포인터.다음 명령의 주소인 프로그램 카운터를 보유합니다.

세그먼트 레지스터:

- CS: 코드

- DS: 데이터

- SS: 스택

- ES: 추가 데이터

- FS: 추가 데이터 #2

- GS: 추가 데이터 #3

64비트 모드에서만 사용 가능한 나머지 8개 레지스터에 대해서는 특별한 목적이 없었습니다.

일부 명령어는 이러한 레지스터를 설계된 목적에 맞게 사용할 때 보다 효율적으로 컴파일하고 실행합니다.예를 들어 AL을 누적기로 사용하고 즉시 바이트 값을 추가하면 효율적인 AL 추가 Opcode가 04h가 되는 반면 BL 레지스터를 사용하면 일반적이고 긴 추가 Opcode가 80C3h가 됩니다.또 다른 예로는 AX 및 DX 레지스터와 함께 작동하는 이중 정밀 분할 및 곱셈이 있습니다.

현대의 컴파일러는 레지스터를 균일하게 처리할 수 있는 sib 바이트(scale-index-base byte)의 도입으로 혜택을 받았습니다.그러나 필요할 때 선택적으로 사용하는 것보다 더 긴 인코딩을 생성하기 때문에 보편적으로 sibbyte를 사용하는 것은 최적이 아닙니다. (sibbyte의 주된 장점은 직교성과 더 강력한 어드레싱 모드를 제공한다는 것입니다.명령을 저장하고 인덱스를 조정하는 것과 같은 주소 계산을 위한 레지스터의 사용을 가능하게 합니다.)일부 특수 명령어는 하드웨어 설계에서 우선 순위를 잃었고 동등한 작은 코드 시퀀스보다 느려졌습니다.주목할 만한 예는 LODSW 지침입니다.

구조.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R?X | |||||||

| E?X | |||||||

| ?X | |||||||

| ?H | ?엘 | ||||||

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ? | |||||||

| 라 | |||||||

| ?W | |||||||

| ?B | |||||||

| 16 | 8 |

|---|---|

| ?S | |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R?P | |||||||

| E?P | |||||||

| ?P | |||||||

| PL | |||||||

참고: 그?PL 레지스터는 64비트 모드에서만 사용할 수 있습니다.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R?I | |||||||

| E?I | |||||||

| ?나는 | |||||||

| ?IL | |||||||

참고: 그?IL 레지스터는 64비트 모드에서만 사용할 수 있습니다.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| RIP | |||||||

| EIP | |||||||

| IP | |||||||

작동모드

리얼모드

이 섹션은 검증을 위해 추가적인 인용이 필요합니다.(2014년 1월)(이 를 및 |

Real Address 모드는 [37]일반적으로 Real 모드라고 불리는 8086 이후의 x86 호환 CPU의 동작 모드입니다.리얼 모드는 20비트 세그먼트 메모리 주소 공간(1MiB가 조금 넘는 메모리만 처리할[p] 수 있음을 의미함), 주변 하드웨어에 대한 직접적인 소프트웨어 액세스, 하드웨어 수준에서의 메모리 보호 또는 멀티태스킹 개념 없음을 특징으로 합니다.80286 시리즈 이상의 모든 x86 CPU는 전원을 켤 때 리얼 모드로 시작합니다. 80186 CPU 이하는 동작 모드가 하나밖에 없었는데, 이는 이후 칩의 리얼 모드와 맞먹습니다. (IBM PC 플랫폼에서는 BIOS가 리얼 모드용으로 작성되었기 때문에 IBM BIOS 루틴에 대한 직접 소프트웨어 액세스는 리얼 모드에서만 가능합니다.그러나 이는 x86 CPU의 속성이 아니라 IBM BIOS 설계의 속성입니다.)

64KB 이상의 메모리를 사용하려면 세그먼트 레지스터를 사용해야 합니다.이것은 "근접", "먼" 그리고 "거대"와 같은 이상한 포인터 모드를 도입하여 세그먼트화된 아키텍처의 암시적 특성을 다른 정도로 활용하는 컴파일러 구현자들에게 큰 복잡성을 야기시켰습니다.암시된 세그먼트 내에서 16비트 오프셋을 포함하는 포인터와 세그먼트 주소 및 세그먼트 내 오프셋을 포함하는 포인터가 있습니다.기술적으로 4개의 세그먼트 레지스터를 모두 한 번 설정한 다음 16비트 오프셋(선택적으로 기본 세그먼트 오버라이드 접두사를 사용하여)만 사용하여 메모리를 처리함으로써 코드 및 데이터에 최대 256KB의 메모리를 사용할 수 있지만, 이는 데이터를 처리하고 메모리 피연산자가 처리할 수 있는 방법에 상당한 제약을 가합니다.결합되며, 16비트 주소 공간이 있는 이전 8비트 프로세서에서 포팅되지 않은 새로운 프로그램에서 별도의 데이터 항목(예: 배열, 구조, 코드 유닛)을 별도의 세그먼트에 포함하고 자체 세그먼트 주소로 주소를 지정하는 것은 Intel 설계자의 아키텍처 의도에 위배됩니다.

언리얼 모드

언리얼 모드는 일부 16비트 운영 체제와 일부 32비트 부트 로더에서 사용됩니다.

시스템 관리 모드

SMM(System Management Mode)은 운영 체제 및 응용 프로그램 소프트웨어가 아닌 시스템 펌웨어(BIOS/UEFI)에서만 사용됩니다.SMM 코드가 SMRAM에서 실행되고 있습니다.

보호모드

이 섹션은 검증을 위해 추가적인 인용이 필요합니다.(2014년 1월)(이 를 및 |

인텔 80286은 리얼 모드 외에도 보호 모드를 지원하며 주소 지정 가능한 물리적 메모리를 16MB로, 주소 지정 가능한 가상 메모리를 1GB로 확장하고 프로그램 간 손상을 방지하는 보호 메모리를 제공합니다.이 작업은 세그먼트 레지스터를 사용하여 인덱스를 메모리에 저장된 디스크립터 테이블에 저장하는 경우에만 수행됩니다.GDT(Global Descriptor Table)와 LDT(Local Descriptor Table)라는 두 개의 테이블이 있으며, 각 테이블은 최대 8192개의 세그먼트 디스크립터를 보유하고 있으며, 각 세그먼트는 64KB의 메모리에 액세스할 수 있습니다.80286에서는 세그먼트 기술자가 24비트 기본 주소를 제공하고, 이 기본 주소를 16비트 오프셋에 추가하여 절대 주소를 생성합니다.표의 기본 주소는 세그먼트 레지스터의 리터럴 값이 실제 모드에서 수행하는 역할과 동일한 역할을 수행합니다. 세그먼트 레지스터가 직접 레지스터에서 간접 레지스터로 변환되었습니다.각 세그먼트에는 하드웨어 기반 컴퓨터 보안에 사용되는 네 개의 링 레벨 중 하나를 할당할 수 있습니다.각 세그먼트 설명자에는 세그먼트와 함께 사용할 수 있는 최대 오프셋을 지정하는 세그먼트 제한 필드도 포함되어 있습니다.오프셋이 16비트이므로 80286 보호 모드에서는 세그먼트가 여전히 각각 64KB로 제한됩니다.[38]

세그먼트 레지스터가 보호 모드로 로드될 때마다 80286은 메모리에서 숨겨진 내부 레지스터 세트로 6바이트 세그먼트 디스크립터를 읽어야 합니다.따라서 세그먼트 레지스터 로드는 실제 모드보다 보호 모드에서 훨씬 느리며 세그먼트를 매우 자주 변경하는 것은 피해야 합니다.80286 이후에는 명령어 실행과 병행하여 세그먼트 제한에 대한 오프셋을 확인할 수 있는 하드웨어가 있기 때문에 보호 모드 세그먼트를 사용하는 실제 메모리 동작은 많이 느려지지 않습니다.

Intel 80386은 오프셋을 확장하고 각 세그먼트 디스크립터의 세그먼트 제한 필드를 32비트로 확장하여 세그먼트가 전체 메모리 공간에 걸쳐 있도록 합니다.또한 페이징(paging)에 대한 보호 모드 지원을 도입하였는데, 이는 페이징된 가상 메모리(페이지 크기 4KB)를 사용할 수 있게 하는 메커니즘입니다.페이징을 통해 CPU는 가상 메모리 공간의 페이지를 물리적 메모리 공간의 페이지에 매핑할 수 있습니다.이를 위해 페이지 테이블이라는 메모리의 추가 매핑 테이블을 사용합니다.80386의 보호 모드는 페이징이 활성화되거나 비활성화된 상태에서 작동할 수 있습니다. 분할 메커니즘은 항상 활성화되어 있고 페이징 메커니즘이 활성화된 경우 가상 주소를 생성한 다음 페이징 메커니즘에 의해 매핑됩니다.또한 모든 세그먼트를 기본 주소가 0이고 전체 주소 공간과 동일한 크기 제한을 갖도록 설정하여 세그먼트화 메커니즘을 효과적으로 비활성화할 수 있습니다. 이를 위해서는 4개의 디스크립터로 구성된 최소 크기의 세그먼트 디스크립터 테이블이 필요합니다(FS 및 GS 세그먼트를 사용할 필요가 없으므로).[q]

페이징은 현대의 멀티태스킹 운영 체제에서 광범위하게 사용됩니다.리눅스, 386BSD, 윈도우 NT는 386용으로 개발되었는데, 그 이유는 이것이 페이징과 32비트 세그먼트 오프셋을 지원하는 최초의 인텔 아키텍처 CPU였기 때문입니다.386 아키텍처는 x86 시리즈의 모든 추가 개발의 기반이 되었습니다.

보호 모드를 지원하는 x86 프로세서는 이전 8086급 프로세서와의 하위 호환성을 위해 실제 모드로 부팅됩니다.전원을 켜면(일명 부팅) 프로세서는 실제 모드에서 초기화한 다음 명령을 실행하기 시작합니다.읽기 전용 메모리에 저장될 수 있는 운영 체제 부팅 코드는 프로세서를 보호 모드로 전환하여 페이징 및 기타 기능을 활성화할 수 있습니다.보호 모드에서는 적용하지 않습니다.반대로, 실제 모드 코드에서 일반적인 관례인 세그먼트 산술은 보호 모드에서는 허용되지 않습니다.

가상 8086 모드

32비트 보호 모드(일명 80386 보호 모드)에는 V86 모드라고도 하는 가상 8086 모드라는 하위 동작 모드도 있습니다.이 모드는 기본적으로 보호 모드 슈퍼바이저 운영 체제의 제어 하에 실제 모드 프로그램 및 운영 체제를 실행할 수 있도록 하는 특수 하이브리드 운영 모드입니다.이를 통해 보호 모드 프로그램과 실제 모드 프로그램을 동시에 실행할 수 있는 유연성을 크게 확보할 수 있습니다.이 모드는 보호 모드의 32비트 버전에서만 사용할 수 있으며, 16비트 버전의 보호 모드나 롱 모드에서는 사용할 수 없습니다.

롱모드

1990년대 중반, x86 아키텍처의 32비트 주소 공간이 대규모 데이터 세트를 필요로 하는 애플리케이션에서 성능을 제한하고 있음이 분명했습니다.32비트 주소 공간을 사용하면 프로세서가 직접 4GB의 데이터만을 처리할 수 있으며, 이는 비디오 프로세싱 및 데이터베이스 엔진과 같은 애플리케이션에서 능가하는 크기입니다.64비트 주소를 사용하면 16EiB의 데이터를 직접 처리할 수 있지만 대부분의 64비트 아키텍처는 전체 64비트 주소 공간에 대한 액세스를 지원하지 않습니다. 예를 들어 AMD64는 64비트 주소에서 48비트만 지원하며 4개의 페이징 레벨로 나뉩니다.

1999년, AMD는 x86 아키텍처의 64비트 확장에 대한 (거의) 완전한 사양을 발표했습니다. 그들은 이를 x86-64라고 불렀고 생산할 의도가 있다고 주장했습니다.이 디자인은 현재 거의 모든 x86 프로세서에 사용되고 있으며 일부 예외는 임베디드 시스템에 사용됩니다.

일반 시장용으로 대량 생산된 x86-64 칩은 4년 후인 2003년에 테스트 및 정제를 위해 프로토타입 작업에 사용할 수 있게 되었습니다. 같은 시기에 초기 이름 x86-64는 AMD64로 변경되었습니다.IA-64 아키텍처의 미지근한 수신과 함께 AMD64 프로세서 라인의 성공은 Intel이 AMD64 명령어 세트의 자체 구현을 공개하도록 강요했습니다.Intel은 이전에 AMD64에[39] 대한 지원을 구현했지만 Itanium의 새로운 IA-64 명령어 세트가 널리 채택되기 전에 AMD가 AMD64를 시장에 출시하지 않기를 바라며 지원하지 않기로 선택했습니다.AMD64를 EM64T로 브랜드화하였고, 이후 인텔64로 브랜드를 변경하였습니다.

마이크로소프트와 썬은 문헌과 제품 버전 이름에서 AMD64/인텔64를 윈도우 및 솔라리스 운영 체제에서 x64로 통칭합니다.리눅스 배포판에서는 "x86-64", 변형 "x86_64", 또는 "amd64"라고 부릅니다.BSD 시스템은 "amd64"를 사용하고 macOS는 "x86_64"를 사용합니다.

긴 모드는 대부분 32비트 명령어 집합의 확장이지만 16비트에서 32비트로 전환하는 것과는 달리 64비트 모드에서는 많은 명령어가 삭제되었습니다.이것은 실제 바이너리 하위 호환성에 영향을 미치지 않지만(이러한 명령어에 대한 지원을 유지하는 다른 모드에서 레거시 코드를 실행할 수 있음), 새로운 코드에 대한 어셈블러와 컴파일러의 작동 방식을 바꿉니다.

x86 아키텍처의 주요 확장이 인텔 이외의 제조업체에 의해 시작된 것은 이번이 처음입니다.인텔이 이 같은 기술을 외부에서 받아들인 것도 이번이 처음이었습니다.

확장자

부동 소수점 단위

초기 x86 프로세서는 8087, 80287 및 80387과 같은 이름을 가진 일련의 부동 소수점 숫자 보조 프로세서 형태의 부동 소수점 하드웨어로 확장될 수 있었습니다.이것은 NPX(Numeric Processor eXtension)라고도 알려졌는데, 이는 보조 프로세서 이후 적절한 이름이지만 주로 부동 소수점 계산에 사용되었으며 이진법과 십진법 형식 모두에서 정수 연산을 수행했습니다.아주 적은 예외를 제외하고 80486과 그 이후의 x86 프로세서는 칩에 이 x87 기능을 통합하여 x87 명령어를 x86 명령어 세트의 사실상 필수적인 부분으로 만들었습니다.

ST(0) 내지 ST(7)로 알려진 각각의 x87 레지스터는 폭이 80비트이고 IEEE 부동 소수점 표준 이중 확장 정밀도 형식으로 숫자를 저장합니다.이 레지스터들은 ST(0)를 상단으로 하여 스택으로 구성됩니다.이것은 opcode 공간을 절약하기 위해 수행되었으며 레지스터 대 레지스터 명령에서 레지스터는 피연산자에 대해서만 랜덤으로 액세스할 수 있습니다. ST0은 다른 피연산자가 ST(x)인지 메모리 피연산자인지에 관계없이 항상 소스 또는 대상 중 하나의 피연산자여야 합니다.그러나 임의의 지정된 ST(x)를 ST(0)와 교환하는 명령어를 통해 스택 레지스터에 대한 임의 액세스를 얻을 수 있습니다.

연산에는 삼각 함수 및 지수 함수를 포함한 산술 함수 및 초월 함수, 공통 상수(예: 0; 1, 자연 로그의 밑, log2(10))를 스택 레지스터 중 하나에 로드하는 명령이 포함됩니다.정수 능력은 종종 간과되지만 x87은 단일 명령어로 8086, 80286, 80386보다 더 큰 정수에서 동작할 수 있으며 64비트 확장이 없는 x86 CPU에서 동작할 수 있으며 작은 값(예: 작은 값)에서도 반복 정수 계산이 가능합니다.16비트)는 x86 CPU와 x87에서 정수 명령을 병렬로 실행하여 가속화할 수 있습니다.(x87 보조 프로세서가 계산하는 동안 x86 CPU가 계속 실행되고, x87은 신호가 끝나면 x86으로 신호를 설정하거나 오류로 인해 주의가 필요한 경우 x86을 중단합니다.)

MMX

MMX는 인텔이 설계하고 1997년 펜티엄 MMX 마이크로프로세서에 도입한 SIMD 명령어 세트입니다.[40]MMX 명령어 세트는 인텔 i860에서 처음 사용된 유사한 개념으로 개발되었습니다.대부분의 후속 IA-32 프로세서에서 인텔 및 기타 공급업체에서 지원됩니다.MMX는 일반적으로 비디오 처리를 위해 사용됩니다(예를 들어, 멀티미디어 애플리케이션에서).[41]

MMX는 MM0 ~ MM7(이하 MMn)로 알려진 아키텍처에 8개의 새로운 레지스터를 추가했습니다.실제로 이러한 새로운 레지스터는 기존 x87 FPU 스택 레지스터의 별칭에 불과했습니다.따라서 부동 소수점 스택에 수행된 모든 작업은 MMX 레지스터에도 영향을 미칩니다.FP 스택과는 달리 이러한 MMn 레지스터는 상대적인 것이 아닌 고정된 것이었기 때문에 임의로 접근할 수 있었습니다.명령어 집합은 스택과 같은 의미론을 채택하지 않아서 기존 운영 체제가 수정 없이 멀티태스킹을 수행할 때 레지스터 상태를 올바르게 저장하고 복원할 수 있었습니다.[40]

각각의 MMn 레지스터는 64비트 정수입니다.그러나 MMX 명령어 집합의 주요 개념 중 하나는 packed data type의 개념입니다. 즉, 단일 64비트 정수(쿼드워드)에 대해 레지스터 전체를 사용하는 대신 32비트 정수(더블워드) 2개, 16비트 정수(워드) 4개 또는 8비트 정수(바이트) 8개를 포함하는 데 사용할 수 있습니다.MMX의 64비트 MMn 레지스터가 FPU 스택에 앨리어싱되고 각각의 부동 소수점 레지스터가 80비트 너비임을 고려할 때, 부동 소수점 레지스터의 상위 16비트는 MMX에서 사용되지 않습니다. 이러한 비트는 임의의 MMX 명령에 의해 모든 비트로 설정되며, 이는 NaN 또는 무한대의 부동 소수점 표현에 해당합니다.[40]

3D Now!

1997년 AMD는 3DNow!를 선보였습니다.[42]이 기술의 도입은 3D 엔터테인먼트 애플리케이션의 등장과 동시에 이루어졌으며 그래픽 집약적 애플리케이션의 CPU 벡터 처리 성능을 향상시키기 위해 고안되었습니다. 3D 비디오 게임 개발자와 3D 그래픽 하드웨어 공급업체는 AMD의 K6 및 Athlon 시리즈 프로세서의 성능을 향상시키기 위해 3DNow!를 사용합니다.[43]

3DNow!는 정수에서 부동 소수점으로 MMX가 자연스럽게 진화하도록 설계되었습니다.이와 같이 MMX와 정확히 동일한 레지스터 명명 규칙, 즉 MM0 ~ MM7을 사용합니다.[44] 유일한 차이점은 정수를 이 레지스터에 채우는 대신 두 개의 단일 정밀 부동 소수점 숫자가 각 레지스터에 패킹된다는 것입니다.FPU 레지스터 얼라이징의 장점은 FPU 레지스터의 상태를 저장하는 데 사용되는 동일한 명령 및 데이터 구조를 3DNow! 레지스터 상태를 저장하는 데 사용할 수 있다는 것입니다.따라서 다른 방법으로는 운영 체제에 대해 알 수 없는 운영 체제에 대해 특별한 수정을 할 필요가 없습니다.[45]

SSE 및 AVX

1999년, 인텔은 스트리밍 SIMD 확장(SSE) 명령어 세트를 선보였고, 이어서 2000년에는 SSE2를 선보였습니다.첫 번째 추가는 x87 스택에서 기본 부동 소수점 연산을 오프로딩할 수 있게 했고 두 번째는 MMX를 거의 쓸모없게 만들었고 기존 컴파일러가 명령을 현실적으로 목표로 삼을 수 있게 했습니다.2004년 펜티엄 4 프로세서의 프레스콧 개정과 함께 소개된 SSE3는 인텔의 하이퍼의 성능을 높이기 위해 특정 메모리와 스레드 처리 명령을 추가했습니다.스레딩 기술.AMD는 SSE3 명령어 세트에 라이센스를 부여하고 대부분의 SSE3 명령어를 버전 E와 나중에 애슬론 64 프로세서에 구현했습니다.애슬론 64는 Hyper를 지원하지 않습니다.스레드화 중이며 Hyper에만 사용되는 SSE3 지침이 없습니다.스레딩.[46]

SSE는 FPU 스택에 대한 모든 레거시 연결을 폐기했습니다.이것은 또한 이 명령어 세트가 MMX와 같은 이전 세대의 SIMD 명령어 세트에 대한 모든 레거시 연결을 버렸다는 것을 의미하기도 했습니다. 그러나 설계자들을 자유롭게 하여 FPU 레지스터의 크기에 제한을 받지 않고 더 큰 레지스터를 사용할 수 있게 해주었습니다.디자이너들은 XMM0부터 XMM7까지 128비트 레지스터 8개를 만들었습니다. (AMD64에서는 SSE XMM 레지스터가 8개에서 16개로 늘었습니다.)그러나 단점은 운영 체제가 등록 상태를 저장하기 위해 이 새로운 명령어 집합을 인식해야 한다는 것이었습니다.그래서 인텔은 SSE 명령을 사용할 수 있도록 하는 Enhanced mode라는 약간 수정된 버전의 Protected mode를 만들었지만 일반 Protected mode에서는 사용할 수 없도록 설정되어 있습니다.SSE를 인식한 OS는 Enhanced 모드를 활성화하는 반면, 인식하지 못한 OS는 기존의 Protected 모드로만 전환됩니다.

SSE는 3DNow!와 같은 부동 소수점 값에서만 작동하는 SIMD 명령어 세트입니다.그러나 3DNow!와는 달리 FPU 스택에 대한 모든 레거시 연결을 차단합니다.SSE는 3D Now!보다 큰 레지스터를 가지고 있기 때문에 단일 정밀 플로트의 두 배를 레지스터에 담을 수 있습니다.원래의 SSE는 3DNow!와 같이 고정밀도의 숫자로만 제한되었습니다.SSE2는 두 배의 정밀도를 포장할 수 있는 기능도 도입했는데, 두 배의 정밀도는 한 개의 3DNow의 전체 크기인 64비트 크기이기 때문에 3DNow!는 할 수 없었습니다.MMn 레지스터.128비트로 SSE XMMn 레지스터는 두 개의 이중 정밀 플로트를 하나의 레지스터에 포장할 수 있습니다.따라서 SSE2는 단일 정밀도로만 제한되었던 SSE1 또는 3DNow!보다 과학적 계산에 훨씬 적합합니다.SSE3는 추가 레지스터를 도입하지 않습니다.[46]

AVX(Advanced Vector Extensions)는 SSE 레지스터의 크기를 256비트 YMM 레지스터로 두 배로 늘렸습니다.또한 더 큰 레지스터를 수용하기 위한 VEX 코딩 방식과 요소를 순열하기 위한 몇 가지 명령을 도입했습니다.AVX2는 추가 레지스터를 도입하지 않았지만 마스킹, 수집, 셔플 명령을 추가한 것이 눈에 띄었습니다.

AVX-512는 32개의 512비트 ZMM 레지스터와 새로운 EVX 체계로 또 다른 확장 기능을 제공합니다.모놀리식 확장 기능을 갖춘 이전 모델과는 달리 특정 모델의 CPU가 구현할 수 있는 많은 하위 집합으로 나뉩니다.

IMT2000 3GPP - 물리 주소 확장 (Physical Address Extension)

물리 주소 확장(Physical Address Extension) 또는 PAE는 Intel Pentium Pro에 처음 추가되었으며 나중에 AMD가 애슬론 프로세서에 추가하여 [47]최대 64GB의 RAM을 처리할 수 있게 되었습니다.PAE가 없으면 32비트 보호 모드의 물리적 RAM은 일반적으로 4GB로 제한됩니다.PAE는 더 넓은 페이지 테이블 항목과 세 번째 수준의 페이지 테이블로 다른 페이지 테이블 구조를 정의하여 추가적인 물리적 주소 비트를 허용합니다.32비트 프로세서의 초기 구현에서는 이론적으로 최대 64GB의 RAM을 지원했지만, 칩셋 및 기타 플랫폼 제한으로 인해 실제로 사용할 수 있는 것이 제한되는 경우가 많았습니다.x86-64 프로세서는 이론적으로 최대 52비트의 물리적 주소를 허용하는 페이지 테이블 구조를 정의하지만, 칩셋 및 기타 플랫폼 문제(예: 사용 가능한 DIMM 슬롯 수, DIMM당 가능한 최대 RAM)로 인해 이러한 큰 물리적 주소 공간이 실현되지 않습니다.x86-64 프로세서에서는 롱 모드로 전환하기 전에 PAE 모드가 활성화되어 있어야 하며 롱 모드가 활성화되어 있는 동안에는 활성 상태를 유지해야 하므로 롱 모드에서는 "비 PAE" 모드가 없습니다.PAE 모드는 선형 또는 가상 주소의 너비에 영향을 주지 않습니다.

x86-64

2000년대에 이르러 32비트 x86 프로세서의 메모리 주소 지정 한계는 고성능 컴퓨팅 클러스터와 강력한 데스크톱 워크스테이션에서 사용하는 데 걸림돌이 되었습니다.오래된 32비트 x86은 훨씬 더 많은 메모리를 처리할 수 있는 훨씬 더 진보된 64비트 RISC 아키텍처와 경쟁하고 있었습니다.인텔과 전체 x86 생태계는 x86이 64비트 컴퓨팅 시대를 살아가려면 64비트 메모리 어드레싱이 필요했습니다. 워크스테이션 및 데스크톱 소프트웨어 애플리케이션이 곧 32비트 메모리 어드레싱의 한계에 도달하기 시작했기 때문입니다.그러나 인텔은 x86 아키텍처에서 일반적으로 벗어나 64비트 데스크톱 컴퓨터로 전환하기 위해 과감한 조치를 취하고 64비트 데스크톱 컴퓨터로의 전환을 사용할 적기라고 여겼으며, 이 실험은 결국 실패했습니다.

2001년, 인텔은 IA-64라는 이름의 비 x86 64비트 아키텍처를 Itanium 프로세서에 도입하려고 시도했습니다. 처음에는 고성능 컴퓨팅 시장을 목표로 삼았고, 궁극적으로는 32비트 x86을 대체할 것으로 기대했습니다.[48]IA-64가 x86과 호환되지 않는 반면, Itanium 프로세서는 x86 명령어를 IA-64로 변환하는 에뮬레이션 기능을 제공했습니다.실제로 사용자에게 유용합니다. 프로그래머들이 IA-64 아키텍처를 위해 x86 프로그램을 다시 작성해야 합니다. 그렇지 않으면 Itanium에서의 성능이 실제 x86 프로세서보다 몇 배나 떨어질 것입니다.시장은 아이테니엄 프로세서가 하위 호환성을 깨고 x86 칩을 계속 사용하는 것을 선호한다는 이유로 거부했고, IA-64용으로 다시 작성된 프로그램은 거의 없었습니다.

AMD는 하위 호환성에 문제가 없도록 64비트 메모리 주소 지정을 위한 또 다른 길을 택하기로 결정했습니다.2003년 4월, AMD는 새로운 x86-64 확장(AMD64 또는 x64로도 알려짐)을 사용하여 4GB 이상의 가상 메모리를 처리할 수 있는 64비트 범용 레지스터를 갖춘 최초의 x86 프로세서 옵테론을 출시했습니다.x86 아키텍처에 대한 64비트 확장은 새로 도입된 롱 모드에서만 활성화되었기 때문에 32비트 및 16비트 응용 프로그램과 운영 체제는 보호 모드 또는 다른 모드에서 AMD64 프로세서를 계속 사용할 수 있었습니다.성능을[49] 조금도 희생하지 않고 16비트 Intel 8086의 원래 지침대로 완벽한 호환성을 제공합니다.[50]: 13–14 시장은 고성능 애플리케이션과 업무용 또는 가정용 컴퓨터 모두에 64비트 AMD 프로세서를 채택하면서 긍정적인 반응을 보였습니다.

시장이 호환되지 않는 Itanium 프로세서와 AMD64를 지원하는 Microsoft를 거부하는 것을 보고 Intel은 대응해야 했고 2004년 7월에 자체 x86-64 프로세서인 Prescott Pentium 4를 출시했습니다.[51]결과적으로 IA-64 명령어 세트를 갖춘 Itanium 프로세서는 거의 사용되지 않으며 x86-64의 화신을 통해 비 내장 컴퓨터에서 여전히 지배적인 CPU 아키텍처입니다.

x86-64는 또한 버퍼 오버런으로 인한 보안 버그로부터 어느 정도 보호를 제공하는 NX 비트를 도입했습니다.

AMD가 x86 계통에 64비트로 기여하고 인텔이 이를 받아들인 결과, 64비트 RISC 아키텍처는 x86 생태계에 위협이 되지 않게 되었고 워크스테이션 시장에서 거의 사라졌습니다.x86-64는 이전에는 64비트 RISC 설계(예: IBM 파워 마이크로프로세서 또는 SPARC 프로세서)의 자연 서식지였던 강력한 슈퍼컴퓨터(AMD Opteron 및 Intel Xeon 화신)에 사용되기 시작했습니다.64비트 컴퓨팅으로의 큰 도약과 32비트 및 16비트 소프트웨어와의 역호환성 유지로 x86 아키텍처는 오늘날의 유연한 플랫폼이 될 수 있었으며, x86 칩은 소형 저전력 시스템(예: Intel Quark 및 Intel Atom)에서 고속 게임용 데스크톱 컴퓨터(예: Intel)로 활용되었습니다.Core i7 및 AMD FX/Ryzen), 심지어 대형 슈퍼컴퓨팅 클러스터까지 장악하고 있어 ARM 32비트 및 64비트 RISC 아키텍처만이 스마트폰 및 태블릿 시장에서 경쟁자로 남게 되었습니다.

가상화

2005년 이전에는 x86 아키텍처 프로세서가 1974년에 Gerald J. Popek와 Robert P. Goldberg가 만든 가상화 사양인 Popek 및 Goldberg 요구 사항을 충족할 수 없었습니다.그러나 독점 제품과 오픈 소스 x86 가상화 하이퍼바이저 제품은 모두 소프트웨어 기반 가상화를 사용하여 개발되었습니다.독점 시스템으로는 Hyper-V, Parallels Workstation, VMware ESX, VMware Workstation, VMware Workstation Player 및 Windows Virtual PC가 있으며, 무료 및 오픈 소스 시스템으로는 QEMU, Kernel-based Virtual Machine, VirtualBox 및 Xen이 있습니다.

2005년 AMD-V 및 Intel VT-x 명령어 세트가 도입되면서 x86 프로세서는 Popek 및 Goldberg 가상화 요구 사항을 충족할 수 있었습니다.[52]

AES

참고 항목

- x86 어셈블리어

- x86 명령어 목록

- x86 메모리 분할

- CPUID

- 이타늄

- x86-64

- 680x0, 16~32비트 시대의 경쟁 아키텍처

- 32비트 및 64비트 시대의 경쟁 아키텍처인 PowerPC

- 마이크로아키텍처

- AMD 프로세서 목록

- 인텔 프로세서 목록

- 인텔 CPU 마이크로아키텍처 목록

- VIA 마이크로프로세서 코어 목록

- x86 제조사 목록

- 인터럽트 요청

- iAPX

- 일시적 실행 CPU 취약성

- 눈금 모형

- 가상 레거시 와이어

메모들

- ^ 특정 마이크로프로세서 설계에 사용되는 마이크로아키텍처(및 특정 전자 및 물리적 구현)와는 다릅니다.

- ^ 예를 들면 GRID Compass 노트북 말입니다.

- ^ 8088, 80186, 80188 및 80286 프로세서를 포함합니다.

- ^ 또한 이러한 시스템에는 멀티플렉서, 버퍼 및 글루 로직을 포함한 표준 7400 시리즈 지원 구성 요소가 일반적으로 혼합되어 있습니다.

- ^ iAPX의 실제 의미는 Intel Advanced Performance Architecture, 또는 때로는 Intel Advanced Processor Architecture였습니다.

- ^ 1981년 말에서 1984년 초, 대략

- ^ 임베디드 프로세서 시장은 가격 민감성, 저전력, 하드웨어 단순성 요구사항으로 인해 x86보다 많은 25개 이상의 다양한 아키텍처로 구성되어 있습니다.

- ^ 또한 NEC V20 및 V30은 구형 8080 명령어 세트를 제공하여 이러한 마이크로프로세서를 장착한 PC가 CP/M 애플리케이션을 최대 속도로 작동할 수 있도록 했습니다(즉, 소프트웨어로 8080을 시뮬레이션할 필요 없이).

- ^ 팹리스 회사들은 칩을 설계하고 다른 회사와 계약하여 제조하는 반면 팹리스 회사들은 설계와 제조를 모두 하게 됩니다.일부 회사는 팹리스 제조업체로 시작하여 나중에 팹리스 디자이너가 되었는데, 그 예로는 AMD가 있습니다.

- ^ 그러나 FPU가 더 느렸는데, 이는 Cyrix가 x86 프로세서를 위한 빠른 부동 소수점 장치의 설계자로 시작했기 때문에 약간 아이러니합니다.

- ^ 인텔은 1993년에 P5 펜티엄과 함께 "x86"이라는 이름 체계를 포기했습니다.그러나 x86이라는 용어는 기술자, 컴파일러 작성자 등 사이에서 이미 확립되어 있었습니다.

- ^ 16비트 마이크로프로세서와 32비트 마이크로프로세서는 각각 1978년과 1985년에 도입되었고, 64비트 계획은 1999년에 발표되었고 2003년 이후부터 점차 도입되었습니다.

- ^ PDP-11과 같은 일부 "CISC" 디자인은 두 가지를 사용할 수 있습니다.

- ^ 그 이유는 정수 산술이 (단순 비트 와이즈 연산과 달리) 후속 비트들 간에 반송파를 생성하기 때문입니다.

- ^ 특히 관심 있는 두 MSR은 SYSTENTER_입니다.커널 모드 시스템 서비스 핸들러의 주소와 해당 커널 스택 포인터를 저장하는 Pentium®II 프로세서에 도입된 EIP_MSR 및 SYSTENTER_ESP_MSR.시스템 시작 중 초기화, SYSENTER_EIP_MSR 및 SYSTENTER_ESP_MSR은 시스템 호출(Intel) 또는 시스템 호출(AMD) 명령에 의해 사용되며, 이는 이전에 사용된 소프트웨어 인터럽트 방법보다 약 3배 빠른 속도입니다.

- ^ 세그먼트 주소는 16비트 세그먼트에 16을 곱한 값과 16비트 오프셋의 합이므로, 1,114,095(10FFEF hex)의 최대 주소는 1,114,096바이트 = 1MB + 65,520바이트입니다.80286 이전에는 x86 CPU의 물리적 어드레스 라인(어드레스 비트 신호)이 20개밖에 없었기 때문에 어드레스의 21번째 비트인 비트 20이 삭제되고 1MB를 초과하는 어드레스는 어드레스 공간의 하단(어드레스 0부터 시작)의 미러였습니다.80286 이후로 모든 x86 CPU는 최소 24개의 물리적 주소 라인을 가지고 있으며 계산된 주소의 비트 20을 실제 모드로 주소 버스로 가져와 CPU가 x86 세그먼트 주소로 도달할 수 있는 전체 1,114,096 바이트를 주소 처리할 수 있도록 합니다.인기 있는 IBM PC 플랫폼에서는 8088/8086 기반 모델을 위해 설계된 모든 프로그램을 실행할 수 있도록 80286 이상의 컴퓨터에 21번째 주소 비트를 비활성화하는 전환 가능한 하드웨어를 추가하였으며, 최신 소프트웨어는 실제 모드에서는 "높은" 메모리를, 보호 모드에서는 16MB 이상의 주소 공간을 활용할 수 있었습니다(A20 게이트 참조).

- ^ 테이블은 0에서 시작하지만 세그먼트 레지스터에 로드할 수 있는 최소 디스크립터 인덱스는 1이므로 테이블 맨 위에 디스크립터 레코드가 추가로 필요합니다. 값 0은 세그먼트를 가리키는 세그먼트 레지스터를 나타내기 위해 예약됩니다.

참고문헌

- ^ Pryce, Dave (May 11, 1989). "80486 32-bit CPU breaks new ground in chip density and operating performance. (Intel Corp.) (product announcement) EDN" (Press release).

- ^ Rao, P.V.S. (2009). Computer System Architecture. Prentice-Hall of India. p. 402 (Section 19.1, The x86 family of processors). ISBN 978-81-203-3594-3.

- ^ Mhatre, Swapneel Chandrakant (2012). Microprocessors and Interfacing Techniques: For S. E. (Computer Engineering) Semester II of University of Pune. Jaico Publishing House. ISBN 978-81-8495-325-1.

- ^ Alcorn, Paul (February 9, 2022). "AMD Sets All-Time CPU Market Share Record as Intel Gains in Desktop and Notebook PCs". Tom's Hardware.

- ^ Brandon, Jonathan (April 15, 2015). "The cloud beyond x86: How old architectures are making a comeback". ICloud PE. Business Cloud News. Archived from the original on August 19, 2021. Retrieved November 23, 2020.

Despite the dominance of x86 in the datacentre it is difficult to ignore the noise vendors have been making over the past couple of years around non-x86 architectures like ARM...

- ^ "June 2022". TOP500.

- ^ Larabel, Michael (May 30, 2022). "AMD-Powered Frontier Supercomputer Tops Top500 At 1.1 Exaflops, Tops Green500 Too". Phoronix. Retrieved June 1, 2022.

- ^ Dvorak, John C. "Whatever Happened to the Intel iAPX432?". Dvorak.org. Archived from the original on November 25, 2017. Retrieved April 18, 2014.

- ^ iAPX 286 Programmer's Reference (PDF). Intel. 1983. Archived (PDF) from the original on August 28, 2017. Retrieved August 28, 2017.

- ^ a b iAPX 86, 88 User's Manual (PDF). Intel. August 1981. Archived (PDF) from the original on August 28, 2017. Retrieved August 28, 2017.

- ^ Edwards, Benj (June 16, 2008). "Birth of a Standard: The Intel 8086 Microprocessor". PCWorld. Archived from the original on September 26, 2010. Retrieved September 14, 2014.

- ^ Stanley Mazor (January–March 2010). "Intel's 8086". IEEE Annals of the History of Computing. 32 (1): 75–79. doi:10.1109/MAHC.2010.22. S2CID 16451604.

- ^ "AMD Discloses New Technologies At Microprocessor Forum" (Press release). AMD. October 5, 1999. Archived from the original on March 2, 2000.

"Time and again, processor architects have looked at the inelegant x86 architecture and declared it cannot be stretched to accommodate the latest innovations," said Nathan Brookwood, principal analyst, Insight 64.

- ^ Burt, Jeff (April 5, 2010). "Microsoft to End Intel Itanium Support". eWeek. Retrieved June 2, 2022.

- ^ a b "Intel 64 and IA-32 Architectures Optimization Reference Manual" (PDF). Intel. September 2019. 3.4.2.2 Optimizing for Macro-fusion. Archived (PDF) from the original on February 14, 2020. Retrieved March 7, 2020.

- ^ a b Fog, Agner. "The microarchitecture of Intel, AMD and VIA CPUs" (PDF). p. 107. Archived (PDF) from the original on March 22, 2019. Retrieved March 7, 2020.

Core2 can do macro-op fusion only in 16-bit and 32-bit mode. Core Nehalem can also do this in 64-bit mode.

- ^ "Zet: The x86 (IA-32) open implementation: Overview". OpenCores. November 4, 2013. Archived from the original on February 11, 2018. Retrieved January 5, 2014.

- ^ "Zhaoxin Preparing Linux Kernel Support For 7-Series Centaur CPUs". www.phoronix.com. Retrieved April 5, 2022.

- ^ "Zhaoxin aiming at 2021 release for its 7nm x86 CPUs - CPU - News - HEXUS.net". m.hexus.net. Retrieved April 5, 2022.

- ^ "Zhaoxin Finally Adding "Lujiazui" x86_64 CPU Tuning To GCC". www.phoronix.com. Retrieved April 5, 2022.

- ^ "Setup and installation considerations for Windows x64 Edition-based computers". Archived from the original on September 11, 2014. Retrieved September 14, 2014.

- ^ "Envisioning a Simplified Intel Architecture". Intel.

- ^ Larabel, Michael (May 20, 2023). "Intel Publishes "X86-S" Specification For 64-bit Only Architecture". Phoronix. Retrieved May 20, 2023.

- ^ "Processors — What mode of addressing do the Intel Processors use?". Archived from the original on September 11, 2014. Retrieved September 14, 2014.

- ^ "DSB Switches". Intel VTune Amplifier 2013. Intel. Archived from the original on December 2, 2013. Retrieved August 26, 2013.

- ^ "The 8086 Family User's Manual" (PDF). Intel Corporation. October 1979. p. 2-68. Archived (PDF) from the original on April 4, 2018. Retrieved March 28, 2018.

- ^ "iAPX 286 Programmer's Reference Manual" (PDF). Intel Corporation. 1983. 2.4.3 Memory Addressing Modes. Archived (PDF) from the original on August 28, 2017. Retrieved August 28, 2017.

- ^ 80386 Programmer's Reference Manual (PDF). Intel Corporation. 1986. 2.5.3.2 EFFECTIVE-ADDRESS COMPUTATION. Archived (PDF) from the original on December 28, 2018. Retrieved March 28, 2018.

- ^ a b Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture. Intel Corporation. March 2018. Chapter 3. Archived from the original on January 26, 2012. Retrieved March 19, 2014.

- ^ Andriesse, Dennis (2019). "6.5 Effects of Compiler Settings on Disassembly". Practical binary analysis: build your own Linux tools for binary instrumentation, analysis, and disassembly. San Francisco, CA: No Starch Press, Inc. ISBN 978-1-59327-913-4. OCLC 1050453850.

- ^ "Guide to x86 Assembly". Cs.virginia.edu. September 11, 2013. Archived from the original on March 24, 2020. Retrieved February 6, 2014.

- ^ "FSTSW/FNSTSW — Store x87 FPU Status Word". Archived from the original on January 25, 2022. Retrieved January 15, 2020.

The FNSTSW AX form of the instruction is used primarily in conditional branching...

- ^ Intel 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture (PDF). Intel. March 2013. Chapter 8. Archived (PDF) from the original on April 2, 2013. Retrieved April 23, 2013.

- ^ "Intel 80287 family". CPU-world. Archived from the original on August 9, 2016. Retrieved July 21, 2016.

- ^ Intel 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture (PDF). Intel. March 2013. Chapter 9. Archived (PDF) from the original on April 2, 2013. Retrieved April 23, 2013.

- ^ Intel 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture (PDF). Intel. March 2013. Chapter 10. Archived (PDF) from the original on April 2, 2013. Retrieved April 23, 2013.

- ^ iAPX 286 Programmer's Reference (PDF). Intel. 1983. Section 1.2, "Modes of Operation". Archived (PDF) from the original on August 28, 2017. Retrieved January 27, 2014.

- ^ iAPX 286 Programmer's Reference (PDF). Intel. 1983. Chapter 6, "Memory Management and Virtual Addressing". Archived (PDF) from the original on August 28, 2017. Retrieved January 27, 2014.

- ^ "Intel's Yamhill Technology: x86-64 compatible Geek.com". Archived from the original on September 5, 2012. Retrieved July 18, 2008.

- ^ a b c "Programming With the Intel MMX™ Technology". Embedded Pentium® Processor Family Technical Information Center. Intel. Archived from the original on July 25, 2003. Retrieved June 5, 2022.

- ^ Krishnaprasad, S. (January 1, 2004). "SIMD programming illustrated using Intel's MMX instruction set". Journal of Computing Sciences in Colleges. 19 (3): 268–277. ISSN 1937-4771.

- ^ Sexton, Michael Justin Allen (April 21, 2017). "The History Of AMD CPUs". Tom's Hardware. Retrieved June 5, 2022.

- ^ Shimpi, Anand Lal (October 29, 1998). "AMD's K6-2 350: Something to do..." AnandTech. Retrieved June 5, 2022.

- ^ "Intel's MMX and AMD's 3DNow! SIMD Operations". web.mit.edu. Retrieved June 5, 2022.

- ^ "3DNow!™ Technology Manual" (PDF). Advanced Micro Devices. Retrieved June 5, 2022.

- ^ a b "Upgrading And Repairing PCs 21st Edition: Processor Features". Tom's Hardware. October 31, 2013. Retrieved June 5, 2022.

- ^ AMD, Inc. (February 2002). "Appendix E" (PDF). AMD Athlon™ Processor x86 Code Optimization Guide (Revision K ed.). p. 250. Archived (PDF) from the original on April 13, 2017. Retrieved April 13, 2017.

A 2-bit index consisting of PCD and PWT bits of the page table entry is used to select one of four PAT register fields when PAE (page address extensions) is enabled, or when the PDE doesn't describe a large page.

- ^ Manek Dubash (July 20, 2006). "Will Intel abandon the Itanium?". Techworld. Archived from the original on February 19, 2011. Retrieved December 19, 2010.

Once touted by Intel as a replacement for the x86 product line, expectations for Itanium have been throttled well back.

- ^ "IBM WebSphere Application Server 64-bit Performance Demystified" (PDF). IBM Corporation. September 6, 2007. p. 14. Archived (PDF) from the original on January 25, 2022. Retrieved April 9, 2010.

Figures 5, 6 and 7 also show the 32-bit version of WAS runs applications at full native hardware performance on the POWER and x86-64 platforms. Unlike some 64-bit processor architectures, the POWER and x86-64 hardware does not emulate 32-bit mode. Therefore applications that do not benefit from 64-bit features can run with full performance on the 32-bit version of WebSphere running on the above mentioned 64-bit platforms.

- ^ "Volume 2: System Programming" (PDF). AMD64 Architecture Programmer's Manual. AMD Corporation. September 2012. Archived (PDF) from the original on February 22, 2014. Retrieved February 17, 2014.

- ^ Charlie Demerjian (September 26, 2003). "Why Intel's Prescott will use AMD64 extensions". The Inquirer. Archived from the original on October 10, 2009. Retrieved October 7, 2009.

- ^ Adams, Keith; Agesen, Ole (October 21–25, 2006). A Comparison of Software and Hardware Techniques for x86 Virtualization (PDF). Proceedings of the International Conference on Architectural Support for Programming Languages and Operating Systems, San Jose, CA, USA, 2006. ACM 1-59593-451-0/06/0010. Archived (PDF) from the original on August 20, 2010. Retrieved December 22, 2006.

추가열람

- Rosenblum, Mendel; Garfinkel, Tal (May 2005). "Virtual machine monitors: current technology and future trends". IEEE Computer. 38 (5): 39–47. CiteSeerX 10.1.1.614.9870. doi:10.1109/MC.2005.176. S2CID 10385623.