코프로세서

Coprocessor코프로세서는 프라이머리 프로세서(CPU)의 기능을 보완하기 위해 사용되는 컴퓨터 프로세서입니다.코프로세서에 의해 실행되는 연산은 부동소수점 연산, 그래픽스, 신호처리, 문자열처리, 암호화 또는 주변장치와의 I/O 인터페이스일 수 있다.프로세서 부하가 높은 태스크를 메인 프로세서에서 오프로드함으로써 코프로세서는 시스템 성능을 가속화할 수 있습니다.코프로세서를 사용하면 일련의 컴퓨터를 커스터마이즈할 수 있기 때문에 추가 성능이 필요하지 않은 고객은 비용을 지불할 필요가 없습니다.

기능

코프로세서는 자율성이 다르다.일부(FPU 등)는 CPU의 명령 스트림에 내장된 코프로세서 명령을 통한 직접 제어에 의존합니다.다른 프로세서들은 그 자체로 비동기적으로 동작할 수 있는 독립 프로세서입니다.그것들은 아직 범용 코드에 최적화되지 않았거나 특정 작업을 가속화하는 데 초점을 맞춘 제한된 명령 집합 때문에 그것을 할 수 없습니다.호스트 프로세서(CPU)가 명령어리스트를 작성하는 경우는, 이러한 메모리·액세스(DMA)에 의해서 실행되는 것이 일반적입니다.PlayStation 2의 Emotion Engine에는 두 가지 작동 모드를 모두 사용할 수 있는 특이한 DSP 유사 SIMD 벡터 유닛이 포함되어 있습니다.

역사

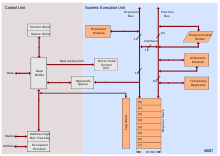

메인프레임 컴퓨터 프로세서 시간을 최대한 활용하기 위해 입출력 작업을 채널 I/O라고 하는 별도의 시스템에 위임했습니다.메인프레임은 I/O 처리를 전혀 필요로 하지 않고 입력 또는 출력 동작에 대한 파라미터를 설정한 후 채널 프로세서에 전체 동작을 수행하도록 신호를 보냅니다.시간이 많이 걸리는 I/O 포맷 및 처리를 처리하기 위해 비교적 단순한 서브 프로세서를 전용으로 사용함으로써 전체적인 시스템 성능이 향상되었습니다.

부동소수점 산술용 코프로세서는 1970년대에 데스크톱 컴퓨터에 처음 등장하여 1980년대부터 1990년대 초반까지 보편화되었다.초기의 8비트 및 16비트 프로세서는 소프트웨어를 사용하여 부동소수점 산술 연산을 수행했습니다.코프로세서가 지원되는 경우 부동소수점 계산을 몇 배 더 빠르게 수행할 수 있습니다.수학 코프로세서는 CAD(컴퓨터 지원 설계) 소프트웨어 및 과학 및 엔지니어링 계산 사용자에게 인기 있는 제품이었습니다.AMD 9511, Intel 8231/8232, Weitek FPU 등의 부동소수점 유닛은 주변기기로 취급되었으며 Intel 8087, Motorola 68881, National 32081 등의 부동소수점 유닛은 CPU와 보다 긴밀하게 통합되었습니다.

또 다른 형태의 코프로세서는 비디오 디스플레이 코프로세서로, 아타리 8비트 패밀리, 텍사스 인스트루먼트 TI-99/4A 및 MSX 가정용 컴퓨터(비디오 디스플레이 컨트롤러)에서 사용되었습니다.Commodore Amiga 커스텀 칩셋에는 Copper로 알려진 유닛과 메모리의 비트맵 조작을 가속화하기 위한 Blitter가 포함되어 있습니다.

마이크로프로세서가 개발됨에 따라 부동소수점 연산 함수를 프로세서에 통합하는 비용은 감소했습니다.또, 고속의 프로세서에서는, 긴밀하게 통합된 코프로세서를 실장하는 것도 어려워졌습니다.따로 포장된 수학 코프로세서는 이제 데스크톱 컴퓨터에서는 흔치 않습니다.그러나 특히 컴퓨터 게임에서 사실적인 3D 그래픽스에 대한 수요가 증가하면서 전용 그래픽 코프로세서에 대한 수요가 증가했습니다.

인텔(R)

최초의 IBM PC에는 인텔 8087 부동소수점 코프로세서(FPU)용 소켓이 포함되어 있어 컴퓨터 지원 설계 또는 수학 집약적인 계산을 위해 PC를 사용하는 사람들에게 인기 있는 옵션이었습니다.이 아키텍처에서는 코프로세서가 부동소수점 연산 속도를 50배 향상시킵니다.예를 들어 워드프로세서 용도로만 PC를 사용하던 사용자는 코프로세서의 높은 비용을 절약할 수 있어 텍스트 조작 성능이 향상되지 않습니다.

8087은 8086/8088과 긴밀하게 통합되어 8088 명령 스트림에 삽입된 부동 소수점 기계 코드 작동 코드에 응답했습니다.8087이 없는 8088 프로세서에서는 이러한 명령어를 해석할 수 없기 때문에 FPU 시스템과 비 FPU 시스템용 프로그램의 다른 버전 또는 적어도 실행 시 FPU를 검출하고 적절한 수학적 라이브러리 함수를 선택하기 위한 테스트가 필요합니다.

8086/8088 중앙 프로세서의 또 다른 코프로세서는 8089 입출력 코프로세서입니다.메모리에서 주변기기로의 데이터 전송 등 입출력 조작에 8087과 동일한 프로그래밍 기술을 사용했기 때문에 CPU 부하가 감소했지만 IBM PC 설계에는 사용하지 않았고 인텔은 이러한 코프로세서의 개발을 중단했다.

인텔 80386 마이크로프로세서는 옵션인 연산 코프로세서(80387)를 사용하여 하드웨어에서 직접 부동소수점 연산을 수행하였습니다.인텔 80486DX 프로세서는 칩에 부동소수점 하드웨어를 탑재했습니다.인텔은 부동소수점 하드웨어를 탑재하지 않은 비용 절감 프로세서인80486SX를 출시하고 80487SX 코프로세서를 판매하였습니다.80487SX는 핀 [1]접속이 다른 완전한 80486DX였기 때문입니다.

메인 프로세서 칩의 80486 내장 부동소수점 하드웨어보다 새로운 인텔 프로세서를 탑재.통합의 진보로 부동소수점 프로세서를 옵션 요소로 판매하는 비용상의 이점이 없어졌습니다.75MHz 프로세서 속도에서 적절한 회로 기판 기술을 채택하여 기가헤르츠 범위의 클럭 속도에서 요구되는 시간 지연, 전력 소비 및 무선 주파수 간섭 표준을 충족시키는 것은 매우 어렵습니다.이러한 온칩 부동소수점 프로세서는 메인 CPU와 병렬로 동작하기 때문에 여전히 코프로세서라고 불립니다.

8비트 및 16비트 데스크톱 컴퓨터 시대에 부동소수점 코프로세서의 또 다른 공통 소스는 Weitek였습니다.이러한 코프로세서는 인텔의 코프로세서와 다른 명령 세트를 가지고 있으며, 모든 메인보드가 지원하는 것은 아닌 다른 소켓을 사용하고 있습니다.Weitek 프로세서는 인텔 x87 패밀리와 같은 초월적인 수학 함수(예를 들어 삼각 함수)를 제공하지 않았으며 [2]함수를 지원하기 위해 특정 소프트웨어 라이브러리가 필요했습니다.

모토로라

Motorola 68000 시리즈는 68881/68882 코프로세서를 탑재하여 인텔 프로세서와 유사한 부동소수점 속도 가속을 제공하였습니다.68000 패밀리를 사용하지만 하드웨어 부동소수점 프로세서를 탑재하지 않은 컴퓨터는 소프트웨어의 부동소수점 명령을 트랩하여 에뮬레이트할 수 있었습니다.이것에 의해, 비록 저속이지만, 양쪽의 경우에 대해서 프로그램의 바이너리 버전을 1개 배포할 수 있었습니다.68451 메모리 관리 코프로세서는 68020 [3]프로세서에서 동작하도록 설계되어 있습니다.

최신 코프로세서

2001년 시점에서는[update] 그래픽 카드 형태의 전용 그래픽 처리 장치(GPU)가 일반적입니다.일부 사운드 카드 모델에는 디지털 멀티채널 믹싱과 실시간 DSP 효과를 제공하는 전용 프로세서가 탑재되어 있습니다(Gravis Ultrasound 및 Sound Blaster AWE32가 대표적인 예입니다).Sound Blaster Audigy 및 Sound Blaster X-Fi는 보다 최근의 예입니다.

2006년에 AGEIA는 PhysX PPU라고 불리는 컴퓨터용 애드인 카드를 발표했습니다.PhysX는 복잡한 물리 계산을 수행하도록 설계되어 있기 때문에 CPU와 GPU가 시간이 많이 걸리는 계산을 수행할 필요가 없습니다.이론적으로 다른 수학적 용도가 개발될 수 있지만 비디오 게임을 위해 설계되었습니다.2008년에 Nvidia는 PhysX 카드 라인을 인수하여 단계적으로 폐지했습니다.소프트웨어를 통해 기능이 추가되어 GPU는 Nvidia PhysX 엔진 소프트웨어를 사용하여 그래픽 처리에 일반적으로 사용되는 코어로 PhysX를 렌더링할 수 있게 되었습니다.

2006년에 BigFoot Systems는 Killer라는 이름의 PCI 애드인 카드를 발표했습니다.FreeScale PowerQ에서 자체 특수 Linux 커널을 실행한 NIC400MHz로 동작하는 UICC. FreeScale 칩을 Network Processing Unit(NPU; 네트워크 처리 유닛)이라고 부릅니다.

Spurs Engine은 Cell 마이크로아키텍처 기반의 코프로세서를 탑재한 미디어 지향 애드인 카드입니다.SPU 자체는 벡터 코프로세서입니다.

2008년에 Kronos Group은 범용 CPU, ATI/AMD 및 Nvidia GPU(및 기타 액셀러레이터)를 하나의 컴퓨팅 커널용 공통 언어로 지원하는 것을 목적으로 OpenCL을 출시했습니다.

2010년대에 일부 모바일 컴퓨팅 장치는 센서 허브를 보조 프로세서로 구현했습니다.모바일 디바이스에서 센서 통합 처리에 사용되는 코프로세서의 예로는 Apple M7 및 M8 모션 코프로세서, Qualcomm Snapdragon Sensor Core 및 Qualcomm Hexagon, Microsoft HoloLens용 홀로그래픽 처리 장치 등이 있습니다.

2012년에 인텔은 인텔 Xeon Phi [4]코프로세서를 발표했습니다.

2016년 현재[update] 시각 및 기타 인지 작업(예: 시각 처리 장치, TrueNorth, Zeroth)을 가속화하기 위한 다양한 기업이 코프로세서를 개발하고 있으며, 2018년 현재 이러한 AI 칩은 애플과 몇몇 안드로이드 폰 벤더 등의 스마트폰에 탑재되어 있다.

기타 코프로세서

- MIPS 아키텍처는 메모리 관리, 부동소수점 산술 및 그래픽 [5]액셀러레이터 등의 기타 태스크에 사용되는2개의 미정의 코프로세서를 최대 4개 지원합니다.

- FPGA(필드 프로그래머블 게이트 어레이)를 사용하면 디지털 신호 처리와 같은 특정 처리 작업의 가속화를 위해 사용자 정의 코프로세서를 생성할 수 있습니다(예: Zynq는 ARM 코어와 단일 다이 상의 FPGA를 결합합니다).

- 서버에서 사용되는 TLS/SSL 액셀러레이터.이러한 액셀러레이터는 이전에는 카드였지만, 현재는 메인스트림 CPU의 암호화에 관한 명령입니다.

- 일부 멀티코어 칩은 한쪽 프로세서가 프라이머리 프로세서이고 다른 한쪽 프로세서가 코프로세서를 지원하도록 프로그래밍할 수 있습니다.

- 중국의 Matrix 2000 128 코어 PCI-e 코프로세서는 CPU를 필요로 하는 독자 사양의 액셀러레이터로, 현재는 2A로 불리고 있는 17,792 노드 Tianhe-2 슈퍼컴퓨터([6]인텔 나이츠 브릿지+매트릭스 2000 각 2대)의 업그레이드에 채용되어 있으며, 속도는 세계에서 가장 빠른 95페타플롭으로 약 2배가 되었습니다.

- Acorn BBC Micro 컴퓨터에는 다양한 코프로세서가 사용 가능했습니다.이들은 특수 목적의 그래픽스나 연산 장치가 아닌 범용 CPU(8086, Zilog Z80, 6502)로 운영체제에 의해 특정 유형의 태스크가 할당되어 컴퓨터의 메인 CPU에서 오프로드되어 가속이 이루어졌습니다.또한 코프로세서를 장착한 BBC Micro는 8086 프로세서용으로 작성된 CP/M 및 DOS와 같은 다른 시스템용으로 설계된 기계 코드 소프트웨어를 실행할 수 있었습니다.

트렌드

시간이 지남에 따라 CPU는 가장 인기 있는 코프로세서의 기능을 흡수하기 위해 성장하는 경향이 있습니다.FPU는 현재 프로세서의 메인 파이프라인의 필수적인 부분으로 간주되고 있습니다.SIMD 유닛은 멀티미디어를 가속화하고 다양한 DSP 액셀러레이터 카드의 역할을 이어받으며 GPU도 CPU 다이로 통합되었습니다.다만, 전용 유닛은 데스크탑 머신으로부터 멀리 떨어져, 한층 더 파워를 얻기 위해서도 인기가 있어, 메인 프로세서 제품 라인과는 독립적으로 진화를 계속할 수 있습니다.

「 」를 참조해 주세요.

- 멀티프로세싱, 단일 컴퓨터 시스템 내에서 2개 이상의 CPU 사용

- Torrenza, AMD 프로세서에 대한 코프로세서 지원 구현 이니셔티브

- 이기종 플랫폼 간에 실행되는 프로그램 작성을 위한 OpenCL 프레임워크

- 비대칭 멀티프로세서

- AI 액셀러레이터

레퍼런스

- ^ Scott Mueller, PC 업그레이드 및 수리, Que Publishing, 2003년 15호 ISBN0-7897-2974-1, 108-110페이지

- ^ Scott Muller, PC 업그레이드 및 수리, Que출판, 1992 ISBN 0-88022-856-3, 페이지 412-413

- ^ 윌리엄 포드, 윌리엄 R.M68000 패밀리 Jones & Bartlett Learning, 1992 ISBN 0-7637-0357-5(892페이지) 및 ff용 탑 어셈블리 언어 및 시스템 프로그래밍.

- ^ "Intel Delivers New Architecture for Discovery with Intel® Xeon Phi™ Coprocessors". Newsroom.intel.com. 2012-11-12. Archived from the original on 2013-06-03. Retrieved 2013-06-16.

- ^ Erin Farquhar, Philip Bunce, MIPS 프로그래머 핸드북, Morgan Kaufmann, 1994 ISBN 1-55860-297-6, 부록 A3 페이지 330

- ^ "China's Tianhe-2A will Use Proprietary Accelerator and Boast 95 Petaflops Peak". hpcwire.com. 25 September 2017. Retrieved 7 April 2018.