하이퍼스레딩

Hyper-threading하이퍼스레딩(공식적으로는 하이퍼스레딩 테크놀로지 또는 HT테크놀로지라고 불리며, HT 또는 HT라고도 불립니다)은 x86 마이크로프로세서에서 실행되는 연산 병렬화(복수의 태스크를 동시에 실행)를 개선하기 위해 사용되는 인텔의 독자 사양의 동시 멀티스레딩(SMT) 구현입니다.2002년 2월 Xeon 서버 프로세서와 2002년 [4]11월 Pentium 4 데스크톱 프로세서에 도입되었습니다.이후 인텔은 이 기술을 Itanium, Atom, 코어 i시리즈 CPU 등에 탑재했습니다.[5]

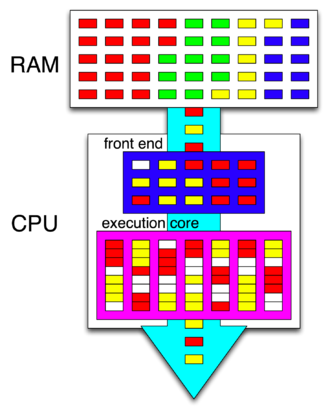

물리적으로 존재하는 각 프로세서 코어에 대해서, operating system은 2개의 가상(논리적인) 코어에 대응해, 가능한 한 그 코어와 워크로드의 공유를 실시합니다.하이퍼스레딩의 주요 기능은 파이프라인의 독립 명령어 수를 늘리는 것입니다.그것은 복수의 명령어가 다른 데이터에 병렬로 동작하는 슈퍼스케일러 아키텍처를 이용합니다.HTT 에서는, 1개의 물리 코어가 2개의 프로세서로 operating system에 표시되기 때문에, 코어 마다 2개의 프로세스를 동시에 스케줄 할 수 있습니다.또한 두 개 이상의 프로세스가 동일한 리소스를 사용할 수 있습니다.한 프로세스에 대한 리소스를 사용할 수 없는 경우 해당 리소스를 사용할 수 있으면 다른 프로세스를 계속할 수 있습니다.

하이퍼스레딩은 운영체제에서 동시 멀티스레딩 지원이 필요할 뿐만 아니라 [6]이에 맞게 최적화된 운영체제에서만 적절하게 사용할 수 있습니다.

개요

하이퍼스레딩 테크놀로지는 인텔이 도입한 동시 멀티스레딩 테크놀로지의 일종으로, 이 테크놀로지의 배후에 있는 컨셉은 Sun Microsystems가 특허를 취득했습니다.아키텍처상 하이퍼스레딩 테크놀로지를 탑재한 프로세서는 코어당2개의 논리 프로세서로 구성되어 있으며 각각 독자적인 프로세서 아키텍처 스테이트가 있습니다.각 논리 프로세서는 동일한 물리 [8]코어를 공유하는 다른 논리 프로세서와는 독립적으로 개별적으로 정지, 인터럽트 또는 특정 스레드의 실행을 지시할 수 있다.

2개의 개별 물리 프로세서를 사용하는 기존의 듀얼 프로세서 구성과 달리 하이퍼스레드 코어의 논리 프로세서는 실행 리소스를 공유합니다.이러한 리소스에는 실행 엔진, 캐시 및 시스템 버스 인터페이스가 포함됩니다. 리소스 공유를 통해 두 개의 논리 프로세서가 서로 더 효율적으로 작동하며 논리 프로세서가 정지된 논리 코어에서 리소스를 빌릴 수 있습니다(두 논리 코어가 동일한 물리적 코어와 관련되어 있다고 가정).프로세서는, 송신한 데이터를 대기하고 있을 때에 정지해, 현재의 스레드 처리를 완료할 수 있습니다.하이퍼스레드 프로세서 또는 멀티코어 프로세서를 사용할 때 얻을 수 있는 이점은 소프트웨어의 요구와 [8]프로세서를 효율적으로 관리하기 위한 소프트웨어 및 운영체제의 작성 정도에 따라 달라집니다.

하이퍼스레딩은 프로세서의 특정 섹션(아키텍처 스테이트를 저장하는 섹션)을 복제하는 것으로 동작하지만 메인 실행 리소스는 복제하지 않습니다.이것에 의해, 하이퍼스레딩 프로세서는 통상의 「물리」프로세서로서 호스트 operating system에는 「물리」프로세서로서 추가의 「논리」프로세서로 인식되기 때문에, operating system은 2개의 스레드 또는 프로세스를 동시에 적절히 스케줄 할 수 있습니다.하이퍼스레딩이 없으면 프로세서의 현재 태스크에서 실행 리소스가 사용되지 않을 경우, 특히 프로세서가 정지되어 있을 때 하이퍼스레딩 기능을 갖춘 프로세서는 이러한 실행 리소스를 사용하여 예약된 다른 태스크를 실행할 수 있습니다.(캐시 미스, 브랜치 오인 또는 데이터 의존관계로 인해 프로세서가 정지할 수 있습니다.)[9]

이 기술은 운영 체제 및 프로그램에 투명합니다.는 논리적 프로세서 기준 별도의 프로세서로 표시되는 hyper-threading을 이용하는 데 필요한 최소 운영 체제에(SMP)지원 다중 처리, 대칭이다.

그것은 다중 처리 장치 hyper-threading 수 있는 시스템에 운영 체제 행동을 최적화하는 것이 가능하다.예를 들어 둘 다hyper-threaded(4논리적 프로세서의 합계를 위해)두가지 신체적 프로세서와 원활한 SMP 시스템을 고려해다.운영 체제의 스레드 스케줄러 hyper-threading을 알아차리지 못 했다, 4개 모두가 논리적 프로세서 같은을 치료할 것이다.만약 단지 두개의 실이기 때문 출마 자격을 얻기, 똑같은 물리적 프로세서에 속하는 것을 일어난 두개의 국지적 프로세서에 나사를 예약한 반면, 다른, 오히려 낮은 성과로보다 다양한 신체 프로세서에 스레드 스케줄링에 의해 가능한 선도하고 있공회전할 프로세서 정말 바쁘게 될까 선택할 수 있습니다.이 문제는 수첩 다르게 물리적 프로세서에서 논리적 프로세서를 개선함으로써, 의미에서 불균일 기억 장치 접근 시스템에 요구되는 스케줄러의 변화, 이것은 제한된 형태는 피할 수 있습니다.

역사

현재 hyper-threading로 범용 컴퓨터에서 알려진 첫번째 미국을 기술하는 논문 에드워드 S.에 의해 쓰여졌다데이빗슨과 Leonard.E.Shar 1973년.[10]

Denelcor, Inc.1982년 Heterogeneous 요소 프로세서(HEP)과 다중계 소개했다.그 HEP 송유관은 같은 과정에서 복수의 지침을 지킬 수 없었다.주어진 과정에서 단지 1명령 파이프 라인의 어떤 지점에 참석하게 되었습니다.는 주어진 점진 블록에서 명령 파이프는 송유관 건조해, 다른 프로세스의 지시는 계속될 것입니다.

hyper-threading 뒤의 기술에 대한 미국의 특허 케네스 Okin SunMicrosystems에서 1994년 11월에서 내려진 것이다.그 당시, CMOS공정 기술로 충분히 비용 효율적인 구현을 위해 수 있게 해 주지 않았다.[11]

인텔은 2002년에 Foster MP 기반의 Xeon을 사용하여 x86 아키텍처 프로세서에 하이퍼스레딩을 구현했습니다.또한 같은 해에 3.06GHz Northwood 기반의 Pentium 4에 포함되었으며 이후 모든 Pentium 4 HT, Pentium 4 Extreme Edition 및 Pentium Extreme Edition 프로세서에 기능으로 남아 있습니다.Pentium 4 모델 라인의 뒤를 잇는 인텔 Core & Core 2 프로세서 라인(2006)은 하이퍼스레딩을 사용하지 않았습니다.코어 마이크로아키텍처를 기반으로 하는 프로세서는 하이퍼스레딩 기능을 갖추고 있지 않았습니다.코어 마이크로아키텍처는 구형 P6 마이크로아키텍처의 후속 프로세서였기 때문입니다.P6 마이크로아키텍처는 Pentium Pro, Pentium II 및 Pentium III(및 당시 Celeron 및 Xeon 파생 모델)와 같은 Pentium 프로세서의 초기 반복에 사용되었습니다.

인텔은 2008년 11월에 Nehalem 마이크로아키텍처(Core i7)를 출시하여 하이퍼스레딩으로 복귀하였습니다.1세대 Nehalem 프로세서는 4개의 물리 코어를 탑재하여 8개의 스레드로 효과적으로 확장되었습니다.이후 2코어와 6코어 모델이 출시되어 각각 [12]4 스레드와 12 스레드를 확장했습니다.이전의 인텔 Atom 코어는 저전력 모바일 PC 및 저가격 데스크톱 [13]PC용 프로세서(경우에 따라서는 하이퍼스레딩 기능을 탑재한 프로세서)였습니다.Itanium 9300은 확장 하이퍼스레딩 테크놀로지를 통해 프로세서당8 스레드(코어당2 스레드)로 출시되었습니다.다음 모델인 Itanium 9500(Poulson)은 12폭의 문제 아키텍처를 갖추고 있으며, 8개의 CPU 코어와 하이퍼스레딩을 [14]통해 8개의 가상 코어를 지원합니다.인텔 Xeon 5500 서버 칩은 쌍방향 하이퍼스레딩도 [15][16]이용합니다.

퍼포먼스 주장

인텔에 따르면 최초의 하이퍼스레딩 구현에서는 동등한 비하이퍼스레드 프로세서에 비해 금형 면적이 5%밖에 사용되지 않았지만 성능은 15~30% [17][18]향상되었습니다.인텔은 동일하지 않은 비동시 멀티스레딩 Pentium 4와 비교하여 퍼포먼스가 최대 30% 향상되었다고 주장합니다.Tom's Hardware 상태: "HT가 켜진 상태에서 3.0GHz로 실행되는 P4가 HT가 [19]꺼진 상태에서 3.6GHz로 실행되는 P4를 능가할 수도 있습니다."인텔은 또한 일부 인공지능 알고리즘에서 하이퍼스레딩 대응 Pentium 4 프로세서를 사용하여 퍼포먼스가 대폭 향상되었다고 주장합니다.

하이퍼스레딩의 퍼포먼스 이력은 처음에는 혼재되어 있었습니다.2002년 11월부터의 하이 퍼포먼스 컴퓨팅에 관한 코멘트에서는,[20] 다음과 같이 언급하고 있습니다.

하이퍼스레딩은 일부 MPI 어플리케이션의 성능을 향상시킬 수 있지만 전부는 아닙니다.클러스터 구성과 클러스터에서 실행되는 애플리케이션의 특성에 따라 성능 향상이 다르거나 부정적인 경우도 있습니다.다음 단계에서는 퍼포먼스 툴을 사용하여 퍼포먼스 향상에 기여하는 영역과 퍼포먼스 저하의 원인이 되는 영역을 파악합니다.

그 결과, 퍼포먼스의 향상은 애플리케이션에 [21]크게 의존합니다.다만, 프로세서를 완전하게 배려할 필요가 있는 2개의 프로그램을 실행하고 있는 경우는, 하이퍼스레딩 테크놀로지를 [22]온으로 하면, 어느 쪽인가 또는 양쪽의 프로그램이 약간 느려지는 것처럼 보일 수 있습니다.이는 Pentium 4의 리플레이 시스템이 귀중한 실행 리소스를 묶어 두 프로그램 간의 프로세서 리소스를 균등하게 함으로써 실행 시간이 증가하기 때문입니다.Pentium 4 "Prescott" 및 Xeon "Nocona" 프로세서는 리플레이 시스템에 필요한 실행 시간을 단축하고 [23]성능 저하를 완전히 극복하는 리플레이 큐를 받았습니다.

2009년 11월 인텔의 분석에 따르면 하이퍼스레딩의 퍼포먼스에 대한 영향은 스레드 실행으로 전체적인 throughput이 크게 향상되지 않는 경우 전체 레이텐시가 증가하며 이는 애플리케이션에[21] 따라 달라집니다.즉, 하이퍼스레딩에 [24]의해 제공되는 추가 하드웨어 리소스 활용률을 효과적으로 사용할 수 있는 동시 스레드가 많아짐에 따라 전체적인 처리 지연 시간이 크게 증가하고 부정적인 영향은 작아집니다.Network Interface Controller(NIC;[25] 네트워크인터페이스 컨트롤러)에 의해 생성된 인터럽트 요구 처리 등 네트워크트래픽 관리와 관련된 작업을 처리하기 위해 사용되는 경우 하이퍼스레딩의 효과에 대해서도 같은 퍼포먼스 분석을 사용할 수 있습니다.또 다른 백서는 [26]인터럽트 처리에 하이퍼스레딩을 사용해도 퍼포먼스가 향상되지 않는다고 주장하고 있습니다.

결점

최초의 HT 프로세서가 출시되었을 때 많은 운영체제는 하이퍼스레딩 테크놀로지에 최적화되어 있지 않았습니다(Windows 2000이나 2.[27]4보다 오래된 Linux 등).

2006년에 하이퍼스레딩은 에너지 효율이 [28]낮다는 비판을 받았습니다.예를 들어, 저전력 CPU 설계 전문업체 ARM은 동시 멀티스레딩이 일반 듀얼 코어 설계보다 최대 46% 더 많은 전력을 사용할 수 있다고 밝혔습니다.또한 시만텍은 캐시 스레싱을 42% 증가시키는 반면 듀얼 코어는 37% [29]감소한다고 주장했습니다.

2010년, ARM은 [30]향후의 칩에 동시 멀티스레딩을 포함할 가능성이 있다고 발표했지만, 2012년 [31]64비트 설계를 위해 거절당했습니다.

2013년에 Intel은 [32]Silvermont 프로세서 코어의 순서가 잘못된 실행을 선호하여 SMT를 폐기했습니다. 이는 SMT를 사용하는 코어 수가 적은 것보다 더 나은 성능과 더 나은 전력 효율성을 제공한다는 것을 발견했기 때문입니다.

2017년에는 인텔의 Skylake 및 Kaby Lake 프로세서에 데이터 [33]손실을 일으킬 수 있는 하이퍼스레딩 구현에 결함이 있음이 밝혀졌습니다.이 [34]문제에 대처하기 위해 나중에 마이크로코드 업데이트가 출시되었습니다.

2019년 Coffee Lake와 함께 인텔은 하이엔드 Core i9 부품 또는 Pentium Gold CPU를 [35]제외한 메인스트림 Core i7 데스크톱 프로세서에 하이퍼스레딩을 포함시키는 것에서 벗어나기 시작했습니다.또,[36] HT 를 무효로 하는 것으로 경감할 수 있는 새로운 CPU 의 취약성 공격이 밝혀짐에 따라, 하이퍼스레딩을 무효로 하는 것을 추천하기 시작했습니다.

보안.

2005년 5월 Colin Percival은 Pentium 4의 악의적인 스레드가 타이밍 기반의 사이드 채널 공격을 사용하여 캐시를 공유하는 다른 스레드의 메모리 액세스 패턴을 감시하고 암호화 정보를 도난할 수 있음을 증명했습니다.악의적인 스레드는 자체 실행 시간만 측정하므로 이는 실제로 타이밍 공격이 아닙니다.이에 대한 잠재적인 해결책으로는 프로세서의 캐시 제거 전략 변경이나 운영 체제가 동일한 물리적 코어로 다른 권한을 [37]가진 스레드가 동시에 실행되지 않도록 하는 것을 들 수 있습니다.2018년 더 오픈비SD 운영체제는 Foreshadow/L1로 인해 "애플리케이션에서 다른 소프트웨어로 데이터가 유출되는 것을 방지하기 위해" 하이퍼스레딩을 비활성화했습니다.TF의 [38][39]취약성2019년에는 일련의 취약성으로 인해 보안 전문가가 모든 [40]장치에서 하이퍼스레딩을 비활성화할 것을 권고했습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ Stokes, Jon (3 October 2002). "Introduction to Multithreading, Superthreading and Hyperthreading". Ars Technica. pp. 2–3. Retrieved 30 September 2015.

- ^ Deborah T. Marr; Frank Binns; David L. Hill; Glenn Hinton; David A. Koufaty; J. Alan Miller; Michael Upton (12 December 2006). "Hyper-Threading Technology Architecture and Microarchitecture" (PDF). cs.sfu.ca. Archived from the original (PDF) on 23 September 2015. Retrieved 30 September 2015.

- ^ Anand Lal Shimpi (5 October 2012). "The Haswell Front End – Intel's Haswell Architecture Analyzed". AnandTech. Retrieved 30 September 2015.

- ^ "Intel Pentium 4 3.06GHz CPU with Hyper-Threading Technology: Killing Two Birds with a Stone." X-bit labs. Archived from the original on 31 May 2014. Retrieved 4 June 2014.

- ^ "Intel® Hyper-Threading Technology (Intel® HT Technology)". Intel. Retrieved 24 October 2021.

- ^ HT 테크놀로지인텔 Pentium 4 프로세서의 인텔 필수 컴포넌트 교환 가능성 리스트에는 하이퍼스레딩 테크놀로지에 최적화된 운영체제 목록이 포함되어 있습니다.Windows XP Professional 64, Windows XP MCE, Windows XP Home, Windows XP Professional, Linux 등의 일부 버전입니다.nux 9(Professional 및 Personal 버전), RedFlag Linux Desktop 4.0 및 SuSe Linux 8.2(Professional 및 Personal 버전)

- ^ "Intel Processor Spec Finder: SL6WK".

- ^ a b Thomadakis, Michael E. (17 March 2011). "The Architecture of the Nehalem Processor and Nehalem-EP SMP Platforms" (PDF). Texas A&M University. p. 23. Archived from the original (PDF) on 11 August 2014. Retrieved 21 March 2014.

- ^ Hennessy, John L.; Patterson, David A. (7 December 2017). Computer Architecture: A Quantitative Approach. Asanović, Krste,, Bakos, Jason D.,, Colwell, Robert P.,, Bhattacharjee, Abhishek, 1984-, Conte, Thomas M., 1964- (Sixth ed.). Cambridge, MA. ISBN 978-0128119051. OCLC 983459758.

- ^ Leonard Shar and Edward Davidson, IEEE Computer, 1974년 2월, 페이지 42-51, vol.7 https://www.computer.org/csdl/magazine/co/1974/02/4251/13rRUyoyhIt의 "파이프라이닝을 통해 구현된 멀티 미니 프로세서 시스템"

- ^ Okin, Kenneth (1 November 1994), United States Patent: 5361337 - Method and apparatus for rapidly switching processes in a computer system, archived from the original on 21 September 2015, retrieved 24 May 2016

- ^ "Page Unavailable". www.intel.com.

- ^ "Intel® Atom™ Processor Microarchitecture". Intel.com. 18 March 2011. Retrieved 5 April 2011.

- ^ "Intel Discloses New Itanium Poulson Features". Tomshardware.com. 24 August 2011. Retrieved 2 July 2017.

- ^ "Server Processor Index Page". Intel.com. 18 March 2011. Retrieved 5 April 2011.

- ^ "Intel Xeon Processor 5500 Series". Intel.com. Retrieved 5 April 2011.

- ^ (PDF). 19 October 2012 https://web.archive.org/web/20121019025809/http://www.intel.com/technology/itj/2002/volume06issue01/vol6iss1_hyper_threading_technology.pdf. Archived from the original (PDF) on 19 October 2012.

{{cite web}}:누락 또는 비어 있음title=(도움말) - ^ "How to Determine the Effectiveness of Hyper-Threading Technology with an Application". software.intel.com. 28 April 2011.

- ^ "Summary: In Some Cases The P4 3.0HT Can Even Beat The 3.6 GHz Version : Single CPU in Dual Operation: P4 3.06 GHz with Hyper-Threading Technology". Tomshardware.com. 14 November 2002. Retrieved 5 April 2011.

- ^ Tau Leng; Rizwan Ali; Jenwei Hsieh; Christopher Stanton (November 2002). "A Study of Hyper-Threading in High-Performance Computing Clusters" (PDF). Dell. p. 4. Retrieved 12 November 2012.

- ^ a b Joel Hruska (24 July 2012). "Maximized performance: Comparing the effects of Hyper-Threading, software updates". extremetech.com. Retrieved 2 March 2015.

- ^ "CPU Performance Evaluation - Benchmark - Pentium 4 2.8 and 3.0". users.telenet.be.

- ^ "Replay: Unknown Features of the NetBurst Core. Page 15". Replay: Unknown Features of the NetBurst Core. Xbitlabs. Archived from the original on 14 May 2011. Retrieved 24 April 2011.

- ^ Valles, Antonio (20 November 2009). "Performance Insights to Intel Hyper-Threading Technology". Intel. Archived from the original on 17 February 2015. Retrieved 26 February 2015.

- ^ "Network Tuning and Performance". calomel.org. 12 November 2013. Retrieved 26 February 2015.

- ^ "Linux kernel documentation: Scaling in the Linux Networking Stack". kernel.org. 1 December 2014. Retrieved 2 March 2015.

Per-cpu load can be observed using the mpstat utility, but note that on processors with hyperthreading (HT), each hyperthread is represented as a separate CPU. For interrupt handling, HT has shown no benefit in initial tests, so limit the number of queues to the number of CPU cores in the system.

- ^ "Hyper-Threading Technology – Operating systems that include optimizations for Hyper-Threading Technology". Intel.com. 19 September 2011. Retrieved 29 February 2012.

- ^ Sustainable Practices: Concepts, Methodologies, Tools and Applications. Information Resources Management Association. December 2013. p. 666. ISBN 9781466648524.

- ^ "ARM is no fan of HyperThreading". theinquirer.net. 2 August 2006. Archived from the original on 6 September 2009. Retrieved 29 February 2012.

{{cite web}}: CS1 유지보수: 부적합한 URL(링크) - ^ Jermoluk, Tom (13 October 2010). "About MIPS and MIPS TOP500 Supercomputing Sites". Top500.org. Archived from the original on 13 June 2011. Retrieved 5 April 2011.

- ^ "ARM launches first 64bit processor core for servers and smartphones". Tech Design Forum. 30 October 2012.

- ^ Rik Myslewski (8 May 2013). "Deep inside Intel's first viable mobile processor: Silvermont". The Register. Retrieved 13 January 2014.

- ^ Chirgwin, Richard (25 June 2017). "Intel's Skylake and Kaby Lake CPUs have nasty hyper-threading bug". The Register. Retrieved 4 July 2017.

- ^ "Skylake, Kaby Lake Chips Have a Crash Bug with Hyperthreading Enabled". Ars Technica. 26 June 2017. Retrieved 25 November 2017.

- ^ Cutress, Ian (23 April 2019). "Intel 9th Gen Core Processors: All the Desktop and Mobile 45W CPUs Announced". AnandTech.

- ^ Armasu, Lucian (14 May 2019). "Intel's New Spectre-Like Flaw Affects Chips Made Since 2008". Tom's Hardware.

- ^ Percival, Colin (14 May 2005). "Cache Missing for Fun and Profit" (PDF). Daemonology.net. Retrieved 14 June 2016.

- ^ "OpenBSD disables Intel's hyper-threading over CPU data leak fears". Retrieved 24 August 2018.

- ^ "'Disable SMT/Hyperthreading in all Intel BIOSes' - MARC". marc.info. Retrieved 24 August 2018.

- ^ Greenberg, Andy (14 May 2019). "Meltdown Redux: Intel Flaw Lets Hackers Siphon Secrets from Millions of PCs". WIRED. Retrieved 14 May 2019.

외부 링크

- 인텔은 2001년 8월에 발매된 인텔 프로세서 설계의 비약적인 발전을 실증하고 있습니다.

- 인텔 – 하이퍼스레딩 개요

- MSDN 매거진에서의 하이퍼스레딩

- Ars Technica의 소개 기사

- 미국 특허번호 4,847,755

- Merom, Conroe, Woodcrest가 하이퍼를 잃음스레드화

- ZDnet: 하이퍼스레딩은 서버 퍼포먼스를 해친다고 개발자는 말합니다.

- ARM은 Hyper 팬이 아니다.스레드화 - SMT 솔루션의 문제 개요

- 하이퍼스레딩이 실가동 어플리케이션의 프로세서 리소스 사용률에 미치는 영향