대칭형 멀티프로세서

Symmetric multiprocessing대칭 다중 처리 또는 공유 메모리 multiprocessing[1](SMP)두개를 동일한 프로세서는 단일, 공유 주 기억 장치에, 모든 입력 및 출력 장치에 대한 모든 권한을 갖는 프로에게 잘 대해 주는 단일 운영 체제 인스턴스에 의해 연결되어 있는 멀티 프로세서 컴퓨터 하드웨어와 소프트웨어 아키텍처를 포함한다.ces특별한 목적을 위해 예약하지 않고 균등하게 보관합니다.오늘날 대부분의 멀티프로세서 시스템은 SMP 아키텍처를 사용합니다.멀티코어 프로세서의 경우 SMP 아키텍처는 코어에 적용되며 코어는 개별 프로세서로 취급됩니다.

존 D 교수Kubiatowicz는 전통적으로 SMP 시스템이 [2]캐시가 없는 프로세서를 포함하고 있다고 생각합니다.Culler와 Pal-Singh는 1998년 저서 "병렬 컴퓨터 아키텍처: 하드웨어/소프트웨어 접근법"에서 다음과 같이 언급하고 있습니다.「SMP라는 용어는 널리 사용되고 있습니다만, 조금 혼란이 있습니다.[...] SMP가 의도하는 것은 공유 메모리 멀티프로세서입니다.메모리 위치에 액세스하는 비용은 모든 프로세서에서 동일합니다.즉, 메모리에 대한 액세스가 실제로 이루어지는 경우 균일한 액세스 비용이 발생합니다.로케이션을 캐시하면 액세스 속도는 빨라지지만 캐시 액세스 시간과 메모리 액세스 시간은 모든 [3]프로세서에서 동일합니다."

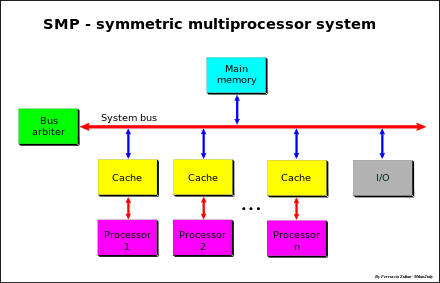

SMP 시스템은 서로 독립적으로 작동하는 동종 프로세서의 풀을 가진 긴밀하게 결합된 멀티프로세서 시스템입니다.각 프로세서는 서로 다른 프로그램을 실행하고 서로 다른 데이터 세트에서 작업하며 시스템 버스 또는 크로스바를 사용하여 연결된 공통 자원(메모리, I/O 장치, 인터럽트 시스템 등)을 공유할 수 있습니다.

설계.

SMP 시스템에는, 복수의 동종의 프로세서를 탑재한 단일의 operating system으로 동작하는 메인 메모리(MM)라고 불리는 중앙 집중형 공유 메모리가 있습니다.통상, 각 프로세서에는, 메인 메모리 데이터 액세스의 고속화와 시스템 버스 트래픽 삭감을 위해서, 캐시 메모리(또는 캐시)라고 불리는 전용 고속 메모리가 관련지어져 있습니다.

프로세서는 버스, 크로스바 스위치 또는 온칩 메쉬 네트워크를 사용하여 상호 접속할 수 있습니다.버스 또는 크로스바 스위치를 사용한SMP의 scalability의 병목현상은 다양한 프로세서, 메모리 및 디스크 어레이 간의 인터커넥트의 대역폭과 소비전력입니다.메쉬 아키텍처는 이러한 보틀 넥을 회피하고 프로그래머빌리티를 희생시키면서 프로세서 수를 크게 늘릴 수 있는 거의 선형적인 확장성을 제공합니다.

이러한 아키텍처에는 CPU 자체와 CPU 간의 상호 접속이라는 두 가지 다른 프로그래밍 모드가 필요하기 때문에 여전히 심각한 프로그래밍 과제가 남아 있습니다.단일 프로그래밍 언어는 워크로드를 분할할 수 있을 뿐만 아니라 메시 기반 [4]아키텍처에서 심각한 메모리 인접성을 이해할 수 있어야 합니다.

SMP 시스템은 시스템 내의 각 작업이 동시에 2개 이상의 프로세서에서 실행되지 않는 한 해당 태스크의 데이터가 메모리 내의 어디에 위치하는지에 관계없이 모든 프로세서에서 작업을 수행할 수 있도록 합니다.적절한 운영체제를 지원하면 SMP 시스템은 프로세서 간에 작업을 쉽게 이동하여 워크로드의 균형을 효율적으로 유지할 수 있습니다.

역사

여러 개의 동일한 프로세서를 갖춘 최초의 생산 시스템은 Burroughs B5000으로, 1961년경에 작동되었습니다.그러나 런타임에는 한쪽 프로세서가 애플리케이션 프로그램으로 제한되고 다른 쪽 프로세서는 주로 운영체제와 하드웨어 인터럽트를 처리하는 등 비대칭이었습니다.Burroughs D825는 [5][6]1962년에 처음으로 SMP를 구현했습니다.

IBM은 System/360 Model 65와 밀접하게 관련된[7] Model 67 [8]및 67-2에 기반한 듀얼 프로세서 컴퓨터 시스템을 제공했습니다.이들 머신에서 동작한 운영체제는 OS/360 M65MP와[9] TSS/360입니다.대학에서 개발된 다른 소프트웨어, 특히 미시간 터미널 시스템(MTS)은 두 CPU를 모두 사용했습니다.두 프로세서 모두 데이터 채널에 액세스하여 I/O를 시작할 수 있습니다.OS/360 M65MP 에서는, operating system의 커널이 양쪽의 프로세서에서 동작하고 있기 때문에(I/[10]O핸들러에 「큰 잠금」이 붙어 있는 경우) 주변기기를 어느쪽의 프로세서에 접속할 수 있었습니다.MTS 슈퍼바이저(UMPS)는 IBM System/360 모델67 ~ 2의 양쪽 CPU에서 실행할 수 있습니다.슈퍼바이저 잠금은 작고 CPU에서 [11]동시에 액세스할 수 있는 개별 공통 데이터 구조를 보호하기 위해 사용되었습니다.

SMP를 지원했던 다른 메인프레임으로는 1965년에 출시된 UNIVAC 1108 II와 GE-635 및 [12][13]GE-645가 있습니다.다만, 멀티프로세서 GE-635 시스템의 GECOS는 대칭적인 [14]방식으로 실행되는 것과 달리 마스터 슬레이브 비대칭 방식으로 동작했습니다.

Digital Equipment Corporation의 운영체제 TOPS-10이 SMP 기능을 구현한 버전 7.0(1972년) 이후 SMP를 실행하는 최초의 시스템은 DECSystem 1077 듀얼 KI10 프로세서 [15]시스템입니다.이후 KL10 시스템은 SMP 방식으로 최대 8개의 CPU를 집약할 수 있었습니다.이와는 대조적으로 DEC 최초의 멀티프로세서 VAX 시스템인 VAX-11/782는 [16]비대칭이었지만 이후 VAX 멀티프로세서 시스템은 SMP였습니다.[17]

초기 상용 Unix SMP 구현에는 Sequent Computer Systems Balance 8000(1984년 출시)과 Balance 21000(1986년 [18]출시)이 포함되어 있습니다.두 모델 모두 10MHz National Semiconductor NS32032 프로세서를 기반으로 하며, 각 프로세서는 공유 메모리 시스템을 형성하기 위해 공통 메모리에 연결된 작은 쓰기 캐시를 가지고 있습니다.또 다른 초기 상용 Unix SMP 구현은 1985년 VAST Corporation의 Dan Gielan이 설계한 NUMA 기반의 Honeywell Information Systems 이탈리아 XPS-100입니다.그 디자인은 최대 14개의 프로세서를 지원했지만 전기적 한계로 인해 가장 큰 시판 버전은 듀얼 프로세서 시스템이었다.운영체제는 AT&T 내에서 내부적으로 사용되는 AT&T 3B20 Unix SysVr3 코드로부터 VAST Corporation에 의해 파생되어 이식되었습니다.

1975년까지 [19]해군 대학원(Naval Passemble School)에 만들어진 MUNIX라는 이름의 포트를 포함하여 이전의 비상업적 다중 처리 UNIX 포트가 존재했습니다.

사용하다

시분할 및 서버 시스템은 여러 프로세스를 병렬로 실행하고 여러 프로세스를 실행하는 시스템이 서로 다른 프로세서에서 서로 다른 프로세스를 실행할 수 있기 때문에 애플리케이션 변경 없이 SMP를 사용하는 경우가 많습니다.

퍼스널 컴퓨터에서는, SMP 는 변경되지 않은 애플리케이션에는 그다지 유용하지 않습니다.시스템이 한 번에 여러 프로세스를 실행하는 경우가 거의 없는 경우 SMP는 멀티스레드(멀티태스킹) 처리를 위해 변경된 응용 프로그램에만 유용합니다.커스텀 프로그래밍된 소프트웨어는 여러 스레드를 사용하도록 작성 또는 수정할 수 있으므로 여러 프로세서를 사용할 수 있습니다.

멀티스레드 프로그램은 멀티스레딩을 지원하는 시분할 및 서버 시스템에서도 사용할 수 있으므로 여러 프로세서를 더 많이 사용할 수 있습니다.

장점/단점

현재의 SMP 시스템에서는, 모든 프로세서가 버스나 스위치와 같은 박스내에 단단히 결합되어 있습니다.이전 SMP 시스템에서는, 1개의 CPU가 캐비닛 전체를 차지했습니다.공유되는 구성 요소에는 글로벌 메모리, 디스크 및 I/O 디바이스가 있습니다.OS 의 카피는, 모든 프로세서에서 1 개 밖에 동작하지 않기 때문에, OS 는 이 아키텍쳐(architecture)를 활용할 수 있도록 설계할 필요가 있습니다.기본적인 장점 중 일부는 스루풋을 향상시키는 비용 효율적인 방법을 포함합니다.다양한 문제와 태스크를 해결하기 위해 SMP는 병렬 프로그래밍이라고 하는 하나의 문제에 여러 프로세서를 적용합니다.

단, 캐시의 일관성과 공유 객체에 의해 SMP의 scalability에는 몇 가지 제한이 있습니다.

프로그래밍

유니프로세서 시스템과 SMP 시스템은 성능을 최대화하기 위해 서로 다른 프로그래밍 방법을 필요로 합니다.SMP 시스템에서 실행되고 있는 프로그램은 단일 프로세서시스템용으로 작성된 경우에도 퍼포먼스가 향상될 수 있습니다.하드웨어 인터럽트는 보통 프로그램 실행을 중단하지만 하드웨어 인터럽트를 처리하는 커널은 유휴 프로세서에서 대신 실행할 수 있기 때문입니다.대부분의 애플리케이션(예: 게임)에서 효과는 성능 향상보다는 외관상 프로그램이 훨씬 원활하게 실행되도록 하는 데 있습니다.일부 애플리케이션(특히 소프트웨어 구축 및 분산 컴퓨팅 프로젝트)은 추가 프로세서의 수만큼 (거의) 고속으로 실행됩니다.(컴파일러 자체는 단일 스레드이지만 여러 컴파일 유닛으로 소프트웨어 프로젝트를 구축하는 경우 각 컴파일 유닛이 개별적으로 처리되면 e-프로세서가 생성됩니다.다중 컴파일 유닛 프로젝트 전체에 걸쳐 병렬 상황이 발생하므로 컴파일 시간을 거의 선형적으로 확장할 수 있습니다.분산 컴퓨팅 프로젝트는 본질적으로 병렬입니다.)

시스템 프로그래머는 운영체제에 SMP 지원을 내장해야 합니다.그렇지 않으면 추가 프로세서는 아이돌 상태로 유지되며 시스템은 단일 프로세서시스템으로 기능합니다.

또한 SMP 시스템은 명령어세트에 관해 더 복잡해질 수 있습니다.동종의 프로세서 시스템은, 통상, SIMD(MMX, SSE 등)등의 「특수한 명령」을 위해서 추가의 레지스터를 필요로 합니다.또, 이종 시스템에서는, 다른 명령/사용법에 대해서 다른 종류의 하드웨어를 실장할 수 있습니다.

성능

여러 프로그램이 동시에 실행될 경우 SMP 시스템은 단일 프로세서보다 훨씬 뛰어난 성능을 발휘합니다.이는 서로 다른 프로그램이 서로 다른 CPU에서 동시에 실행될 수 있기 때문입니다.반대로 Asymmetric Multiprocessing(AMP; 비대칭 멀티프로세서)에서는 보통 한 번에 하나의 프로세서만 프로그램 또는 태스크를 실행할 수 있습니다.예를 들어 AMP는 작업 완료의 우선 순위와 중요도에 따라 특정 작업을 CPU에 할당하는 데 사용할 수 있습니다.AMP는 여러 CPU를 처리하는 측면에서 SMP보다 훨씬 전에 작성되었습니다.이것은, 다음의 예에 근거해 퍼포먼스의 부족을 설명하고 있습니다.

SMP 환경에서 많은 작업이 처리되는 경우 관리자는 하드웨어 효율이 저하되는 경우가 많습니다.소프트웨어 프로그램은 프로세서의 사용률이 최대치에 도달할 수 있도록 컴퓨터의 작업 및 기타 기능을 스케줄링하도록 개발되었습니다.적절한 소프트웨어 패키지는 각 CPU를 개별적으로 스케줄 하는 것 외에 여러 SMP 머신과 클러스터를 통합할 수 있기 때문에 이 가능성을 최대한 높일 수 있습니다.

RAM에의 액세스는 시리얼화 됩니다.이러한 문제와 캐시의 일관성 문제로 인해 시스템 내 추가 프로세서의 수에 비해 성능이 약간 저하됩니다.

대체 수단

SMP는 멀티프로세서 머신 아키텍처의 초기 스타일 중 하나를 나타내는 단일 공유 시스템버스를 사용합니다.일반적으로 최대 8개의 프로세서를 탑재한 소형 컴퓨터를 구축하는 데 사용됩니다.

대형 컴퓨터 시스템에서는 서로 다른 메모리 뱅크를 서로 다른 프로세서 전용으로 사용하는 NUMA(Non-Uniform Memory Access)와 같은 최신 아키텍처를 사용할 수 있습니다.NUMA 아키텍처에서는 프로세서가 로컬 메모리에 빠르게 액세스하고 원격 메모리에 더 느리게 액세스할 수 있습니다.데이터가 특정 프로세스(및 프로세서)에 현지화되어 있는 한, 메모리 스루풋이 큰폭으로 향상할 수 있습니다.단점으로는 NUMA를 사용하면 워크로드 밸런싱과 같이 프로세서에서 다른 프로세서로 데이터를 이동하는 비용이 더 많이 듭니다.NUMA의 이점은 특정 워크로드, 특히 데이터가 특정 작업 또는 사용자와 강하게 연관된 서버에서 제한됩니다.

마지막으로 컴퓨터 클러스터형 멀티프로세서(Beowulf 등)가 있습니다.이 경우 모든 프로세서가 모든 메모리를 사용할 수 있는 것은 아닙니다.클러스터링 기술은 매우 큰 슈퍼컴퓨터를 구축하는 데 상당히 광범위하게 사용됩니다.

가변 SMP

vSMP(Variable Symmetric Multiprocessing)는 NVIDIA가 시작한 특정 모바일 사용 사례 기술입니다.이 테크놀로지에는 모바일액티브 스탠바이 모드, 비디오 재생, 음악 재생 중 낮은 주파수로 작업을 수행하기 위해 특별히 제작된 Companion 코어라고 불리는 쿼드코어 디바이스에 추가 5번째 코어가 포함되어 있습니다.

NVIDIA가 특허를 취득한 Project Kal-El(Tegra [20]3)은 이 새로운 vSMP 테크놀로지를 최초로 구현한 SoC(System on Chip)입니다.이 테크놀로지는 액티브 스탠바이 상태에서의 모바일 소비 전력을 삭감할 뿐만 아니라 부하가 높은 모바일 애플리케이션에서의 액티브한 사용시의 쿼드 코어 퍼포먼스를 최대화합니다.전체적으로 이 테크놀로지는 모바일 프로세서의 소비전력을 줄임으로써 액티브 및 스탠바이 사용 시의 배터리 지속시간 퍼포먼스 향상에 대한 요구에 대응합니다.

현재의 SMP 아키텍처와 달리 vSMP Companion 코어는 OS 투과형입니다.즉, 운영체제와 실행 중인 애플리케이션은 이 추가 코어를 전혀 인식하지 못하지만 여전히 활용할 수 있습니다.vSMP 아키텍처의 장점에는 캐시 일관성, OS 효율성 및 전원 최적화가 있습니다.이 아키텍처의 장점은 다음과 같습니다.

- 캐시 일관성:vSMP에서는 Companion 코어와 메인 코어를 동시에 실행할 수 없기 때문에 서로 다른 빈도로 실행되는 코어 간에 캐시를 동기화해도 아무런 영향이 없습니다.

- OS 효율성:여러 CPU 코어가 서로 다른 비동기 주파수로 실행되는 경우 스케줄링 [how?]문제가 발생할 수 있으므로 비효율적입니다.vSMP를 사용하면 OS 스케줄링을 최적화하기 위해 활성 CPU 코어가 유사한 빈도로 실행됩니다.

- 전력 최적화:비동기 크로킹 기반 아키텍처에서는 각 코어가 다른 전원 플레인에 배치되어 서로 다른 동작 주파수에 대한 전압 조정을 처리합니다.그 결과 [how?]퍼포먼스에 영향을 줄 수 있습니다.vSMP 테크놀로지는 액티브 및 스탠바이 사용에 대해 특정 코어를 동적으로 활성화 또는 비활성화할 수 있으므로 전체적인 소비전력을 줄일 수 있습니다.

이러한 이점을 통해 vSMP 아키텍처는 비동기 크로킹테크놀로지를 사용하는 다른 아키텍처에 비해 큰 이점을[peacock prose] 얻을 수 있습니다.

「 」를 참조해 주세요.

- 비대칭 멀티프로세서

- 바이너리 모듈러 데이터 플로우 머신

- 로케일(컴퓨터 하드웨어)

- 대규모 병렬화

- 분할된 글로벌 주소 공간

- 동시 멀티스레딩– CPU 코어의 기능 요소가 여러 실행 스레드에 걸쳐 할당됩니다.

- 소프트웨어 록아웃

- 시온파이

레퍼런스

- ^ Patterson, David; Hennessy, John (2018). Computer Organisation and Design: The Hardware/Software Interface (RISC-V ed.). Cambridge, United States: Morgan Kaufmann. p. 509. ISBN 978-0-12-812275-4.

- ^ John Kubiatowicz. Introduction to Parallel Architectures and Pthreads. 2013 Short Course on Parallel Programming.

- ^ David Culler; Jaswinder Pal Singh; Anoop Gupta (1999). Parallel Computer Architecture: A Hardware/Software Approach. Morgan Kaufmann. p. 47. ISBN 978-1558603431.

- ^ Lina J. Karam, Ismail AlKamal, Alan Gatherer, Gene A. Frantz, David V. Anderson, Brian L. Evans (2009). "Trends in Multi-core DSP Platforms" (PDF). IEEE Signal Processing Magazine. 26 (6): 38–49. Bibcode:2009ISPM...26...38K. doi:10.1109/MSP.2009.934113. S2CID 9429714.

{{cite journal}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ Gregory V. Wilson (October 1994). "The History of the Development of Parallel Computing".

- ^ Martin H. Weik (January 1964). "A Fourth Survey of Domestic Electronic Digital Computing Systems". Ballistic Research Laboratories, Aberdeen Proving Grounds. Burroughs D825.

- ^ IBM System/360 Model 65 Functional Characteristics (PDF). Fourth Edition. IBM. September 1968. A22-6884-3.

- ^ IBM System/360 Model 67 Functional Characteristics (PDF). Third Edition. IBM. February 1972. GA27-2719-2.

- ^ M65MP: OS/360 멀티프로세싱 실험

- ^ Program Logic Manual, OS I/O Supervisor Logic, Release 21 (R21.7) (PDF) (Tenth ed.). IBM. April 1973. GY28-6616-9.

- ^ Mike Alexander의 Time Sharing Supervisor Programs(1971년 5월)에는 MTS, TSS, CP/67 및 멀티틱에 대한 정보가 있습니다.

- ^ GE-635 System Manual (PDF). General Electric. July 1964.

- ^ GE-645 System Manual (PDF). General Electric. January 1968.

- ^ Richard Shetron (May 5, 1998). "Fear of Multiprocessing?". Newsgroup: alt.folklore.computers. Usenet: 354e95a9.0@news.wizvax.net.

- ^ DEC 1077 및 SMP

- ^ VAX 제품 판매 가이드(1-23페이지 및 1-24페이지): VAX-11/782는 1982년에 비대칭 멀티프로세싱 시스템으로 설명되었습니다.

- ^ VAX 8820/8830/8840 시스템 하드웨어 사용자 가이드: 1988년까지 VAX 운영체제는 SMP가 되었습니다.

- ^ Hockney, R.W.; Jesshope, C.R. (1988). Parallel Computers 2: Architecture, Programming and Algorithms. Taylor & Francis. p. 46. ISBN 0-85274-811-6.

- ^ Hawley, John Alfred (June 1975). "MUNIX, A Multiprocessing Version Of UNIX" (PDF). core.ac.uk. Retrieved 11 November 2018.

- ^ 가변 SMP – 저소비전력 및 고성능을 실현하는 멀티코어 CPU 아키텍처.NVIDIA. 2011.