PA-RISC

PA-RISC | |

| 디자이너 | 휴렛패커드 |

|---|---|

| 비트 | 64비트(32→64) |

| 소개했다 | 1986(1996년 PA-RISC 2.0) |

| 버전 | 2.0 (1996) |

| 설계. | RISC |

| 부호화 | 고정된. |

| 분기 | 비교 및 분기 |

| 엔디안니스 | 큰. |

| 내선번호 | 멀티미디어 액셀러레이션 eXtensions(MAX), MAX-2 |

| 열다. | 아니요. |

| 레지스터 | |

| 범용 | 32 |

| 부동 소수점 | 32 64비트(PA-RISC 1.0에서는 1664비트) |

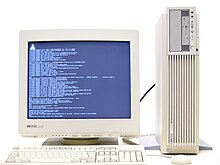

PA-RISC는 Hewlett-Packard가 개발한 Instruction Set Architecture(ISA; 명령 집합 아키텍처)입니다.이름에서 알 수 있듯이 PA는 Precision Architecture의 약자인 RISC(Reduced Instruction Set Computer) 아키텍처입니다.이 설계는 HP/PA for Hewlett Packard Precision Architecture라고도 불립니다.

이 아키텍처는 1986년 2월 26일 HP 3000 시리즈930 및 HP 9000 모델840 컴퓨터가 최초로 구현된 TS1을 [1][2]탑재하여 출시되었습니다.

PA-RISC는 HP와 [3]인텔이 공동 개발한 Itanium(원래 IA-64) ISA에 의해 계승되었습니다.HP는 2008년 말에 PA-RISC 기반 HP 9000 시스템의 판매를 중단했지만 2013년까지 [4]PA-RISC 칩을 실행하는 서버를 지원했습니다.

역사

1980년대 후반 HP는 CISC CPU를 기반으로 4시리즈의 컴퓨터를 구축하고 있었습니다.1986년에 시작된 IBM PC 호환 인텔 i286 기반 벡트라 시리즈가 그 중 하나입니다.그 외는 모두 인텔 이외의 시스템입니다.그 중 하나는 Motorola 68000 기반 워크스테이션의 HP 시리즈 300, 커스텀 실리콘 온 사파이어(SOS) 칩 설계를 기반으로 한 또 다른 시리즈 200 테크니컬 워크스테이션, SOS 기반 16비트 HP 3000 클래식 시리즈, 마지막으로 자체(16비트 및 32비트) 마이크로프로세서를 기반으로 한 HP 9000 시리즈 500 미니 컴퓨터입니다.

Precision 아키텍처는 Hewlett-Packard 내부에서 Spectrum 프로그램으로 알려진 것의 결과입니다.[5]HP는 Spectrum을 사용하여 PC와 호환되지 않는 모든 머신을 단일 RISC CPU 패밀리로 이행할 계획이었다.

1982년 초 HP Laboratories의 Precision Architecture에서 명령어 세트와 가상 메모리 시스템을 정의하는 작업이 시작되었습니다.첫 번째 TTL 실장은 1983년 4월에 시작되었습니다.프로세서의 시뮬레이션은 1983년에 이루어졌으며, 완전한 프로세서는 1984년 7월에 소프트웨어 개발자에게 제공되었습니다.시스템 프로토타이핑이 이어졌고 1985년에 "랩 프로토타입"이,[6] 1986년에 제품 프로토타입을 제작했습니다.

최초의 프로세서는 1986년에 제품에 도입되었습니다.32비트 정수 레지스터가 32개, 64비트 부동소수점 레지스터가 16개 있습니다.부동소수점 레지스터의 수는 1.1 버전에서는 16이 불충분하고 퍼포먼스가 제한된 것이 판명된 후 32로 2배가 되었습니다.건축가로는 Allen Baum, Hans Jeans, Michael J. Mahon, Ruby Bei-Loh Lee, Russel Kao, Steve Muchnick, Terrence C 등이 있습니다.밀러, 데이비드 포틀랜드, 윌리엄 S.월리[7]

첫 번째 구현은 TS1로, 개별 트랜지스터-트랜지스터 로직(74F TTL) 소자로 구성된 중앙 처리 장치입니다.이후 구현은 NMOS 프로세스(NS1 및 NS2) 및 CMOS(CS1 및 PCX)[8]에서 제작된 멀티칩 VLSI 설계입니다.1980년대 후반에 HP 3000 머신 시리즈인 930과 950에서 처음 사용되었습니다.이때 Spectrum system이라고 불리는 것은 개발 연구소에서 붙여진 이름입니다.이 기계들은 MPE-XL을 실행했습니다.HP 9000 머신은 곧 PA-RISC 프로세서와 함께 업그레이드되어 HP-UX 버전의 UNIX가 가동되었습니다.

PA-RISC 아키텍처로 이식된 다른 운영 체제에는 Linux, OpenBSD, NetBSD 및 NeXTSTEP가 있습니다.

PA-RISC 회선의 흥미로운 점은 대부분의 세대에는 레벨2 캐시가 없다는 것입니다.대신 이전에는 버스로 연결된 개별 칩으로 사용되던 대규모 레벨1 캐시가 온칩으로 통합되었습니다.L2 캐시가 있는 것은 PA-7100LC와 PA-7300LC뿐입니다.PA-RISC의 또 다른 혁신은 PA-7100LC에 최초로 도입된 MAX 형식의 벡터명령(SIMD)의 추가입니다.

HP가 이끄는 업계 그룹인 Precision RISC Organization은 PA-RISC 아키텍처를 촉진하기 위해 1992년에 설립되었습니다.회원에는 콘벡스, 히타치, 휴즈 에어크래프트, 미쓰비시, NEC, OKI, 프라임, 스트라투스, 요코가와, 레드브릭 소프트웨어, 알레그로 컨설턴트 주식회사 등이 포함됐다.

ISA는 1996년에 64비트로 확장되어 PA-RISC 2.0이라는 이름의 리비전이 추가되었습니다.PA-RISC 2.0은 또한 특정 부동 소수점 집약 알고리즘을 지원하는 다중 추가 명령과 멀티미디어 애플리케이션을 가속화하는 명령을 제공하는 MAX-2 SIMD 확장을 추가했습니다.최초의 PA-RISC 2.0 실장은 PA-8000으로, 1996년 1월에 도입되었습니다.

CPU 사양

| 이미지 | 모델 | 마케팅. 이름. | 연도 | 빈도수. [MHz] | 메모리 버스 [MB/s] | 과정 [μm] | 트랜지스터 [아쉬움] | 다이 사이즈 [mm²] | 힘 [W] | Dcache [KB] | 이카체 [KB] | L2 캐시 [MB] | ISA | 메모들 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TS-1 | ? | 1986 | 8 | ? | ? | — | — | ? | ? | ? | — | 1.0 | ||

| CS-1 | ? | 1987 | 8 | ? | 1.6 | 0.164 | 72.93 | 1 | — | 0.25 | — | 1.0 | [9] | |

| NS-1 | ? | 1987 | 25/30 | ? | 1.5 | 0.144 | 70.56 | ? | ? | ? | — | 1.0 | [10] | |

| NS-2 | ? | 1989 | 27.5/30 | ? | 1.5 | 0.183 | 196 | 27 | 512 | 512 | — | 1.0 | [11] |

| PCX | ? | 1990 | ? | ? | ? | ? | ? | ? | ? | ? | ? | 1.0 | ||

| PCX-S | PA-7000 | 1991 | 66 | ? | 1.0 | 0.58 | 201.6 | ? | 256 | 256 | — | 1.1a | |

| PCX-T | PA-7100 | 1992 | 33–100 | ? | 0.8 | 0.85 | 196 | ? | 2048 | 1024 | — | 1.1b | |

| PCX-T | PA-7150 | 1994 | 125 | ? | 0.8 | 0.85 | 196 | ? | 2048 | 1024 | — | 1.1b | |

| PCX-T' | PA-7200 | 1994 | 120 | 960 | 0.55 | 1.26 | 210 | 30 | 1024 | 2048 | — | 1.1c | |

| PCX-L | PA-7100LC | 1994 | 60–100 | ? | 0.75 | 0.9 | 201.6 | 7–11 | — | 1 | 2 | 1.1d | |

| PCX-L2 | PA-7300LC | 1996 | 132–180 | ? | 0.5 | 9.2 | 260.1 | ? | 64 | 64 | 0–8 | 1.1e | |

| PCX-U | PA-8000 | 1996 | 160–180 | 960 | 0.5 | 3.8 | 337.68 | ? | 1024 | 1024 | — | 2.0 | |

| PCX-U+ | PA-8200 | 1997 | 200–240 | 960 | 0.5 | 3.8 | 337.68 | ? | 2048 | 2048 | — | 2.0 | |

| PCX-W | PA-8500 | 1998 | 300–440 | 1920 | 0.25 | 140 | 467 | ? | 1024 | 512 | — | 2.0 | [12] |

| PCX-W+ | PA-8600 | 2000 | 360–550 | 1920 | 0.25 | 140 | 467 | ? | 1024 | 512 | — | 2.0 | [12] |

| PCX-W2 | PA-8700(+) | 2001 | 625–875 | 1920 | 0.18 | 186 | 304 | 7.1 @ 1.5 V 미만 | 1536 | 768 | — | 2.0 | |

| 마코 | PA-8800 | 2003 | 800–1000 | 6400 | 0.13 | 300 | 361 | ? | 768/코어 | 768/코어 | 0 또는 32 | 2.0 | |

| 쇼트핀 | PA-8900 | 2005 | 800–1100 | 6400 | 0.13 | ? | ? | ? | 768/코어 | 768/코어 | 0 또는 64 | 2.0 |

「 」를 참조해 주세요.

레퍼런스

- ^ '1년 전'(1987년 2월 26일).컴퓨터 비즈니스 리뷰

- ^ Rosenbladt, Peter (September 1987). "In this Issue" (PDF). Hewlett-Packard Journal. 38 (9): 3. Archived (PDF) from the original on 2019-04-26. Retrieved 2018-06-08.

... In the March 1987 issue we described the HP 3000 Series 930 and HP 9000 Model 840 Computers, which were HP's first realizations of HP Precision Architecture in off-the-shelf TTL technology. ...

- ^ "HP Completes Its PA-RISC Road Map With Final Processor Upgrade". Archived from the original on 2008-02-13. Retrieved 2007-07-24.

- ^ "How long will HP continue to support HP 9000 systems?". Archived from the original on 2012-02-19. Retrieved 2008-02-29.

- ^ Worley, William S. (August 1986). "Hewlett-Packard Precision Architecture: The Processor" (PDF). Hewlett-Packard Journal. 37 (8): 4–22.

The HP Precision Architecture development program, known within HP as the Spectrum program, ...

- ^ Fotland, David A.; Shelton, John F.; Bryg, William R.; La Fetra, Ross V.; Boschma, Simin I.; Yeh, Allan S.; Jacobs, Edward M. (March 1987). "Hardware Design of the First HP Precision Architecture Computers". Hewlett-Packard Journal. 38 (3): 4–17. Retrieved 6 October 2020.

- ^ Smotherman, Mark(2009년 7월 2일).2012-09-10년 웨이백 머신에 아카이브된 최신 프로세서 아키텍트

- ^ 폴 바이스만."Early PA-RISC Systems" Wayback Machine에 2014-10-02 아카이브되었습니다.

- ^ Marston, A.; et al. (1987). "A 32b CMOS single-chip RISC type processor". 1987 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. pp. 28–29. doi:10.1109/ISSCC.1987.1157145. S2CID 61007482.

- ^ Yetter, J.; et al. (1987). "A 15 MIPS 32b Microprocessor". ISSCC 1987. pp. 26–27. doi:10.1109/ISSCC.1987.1157220. S2CID 58782915.

- ^ Boschma, Brian D.; et al. (1989). "A 30 MIPS VLSI CPU". IEEE International Solid-State Circuits Conference, 1989 ISSCC. Digest of Technical Papers. pp. 82–83, 299. doi:10.1109/ISSCC.1989.48191. S2CID 53932361.

- ^ a b "HP L1000 및 L2000 (rp5400/rp5450)" Wayback Machine, openpa에서 2018-01-02 아카이브 완료.네트워크

외부 링크

- LostCircuits Hewlett Packard PA8800 RISC 프로세서 개요

- HP 문서– PA-RISC 페이지 다운, 아키텍처 PDF 이용 가능

- OpenPA.net 포괄적인 PA-RISC 칩 및 컴퓨터 정보

- chipdb.org 다양한 PA-RISC 프로세서 이미지