PDP-8

PDP-8 PDP-8은 영국 Bletchley에 있는 국립컴퓨팅박물관에 전시되어 있습니다.이 예는 1세대 PDP-8에서 가져온 것으로, 이산 트랜지스터로 구축되어 나중에 Straight 8로 알려졌습니다. | |

| 개발자 | 디지털 이그니션 코퍼레이션 |

|---|---|

| 제품 패밀리 | 프로그래밍된 데이터 프로세서 |

| 유형 | 미니 컴퓨터 |

| 발매일 | 1965년 3월 22일, 전( |

| 초기 가격 | US$18,500 2021년 약 159,100에 상당 |

| 판매대수 | 50,000+ |

| 플랫폼 | DEC 12비트 |

| 전임자 | PDP-5 |

| 후계자 | PDP-12 |

PDP-8은 Digital Equipment Corporation(DEC)에서 제조된 12비트 미니 컴퓨터입니다.이 모델은 상업적으로 성공한 최초의 미니컴퓨터로, 모델 수명 동안 50,000대 이상이 판매되었다.기본 설계는 선구적인 LINC를 따르지만 PDP-5 명령 [1]집합의 확장된 버전인 더 작은 명령 집합을 가지고 있습니다.DEC의 유사한 기계로는 PDP-12와 PDP-8 및 LINC 개념을 현대화한 PDP-14 산업용 컨트롤러 시스템이 있습니다.

개요

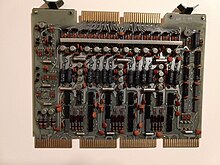

최초의 PDP-8 모델은 비공식적으로 "Straight-8"로[2] 알려져 있으며, 1965년[3] 3월 22일 18,500달러(2021년 약 160,000달러 상당)의 가격이 책정되었다.소형 가정용 냉장고 크기의 기계에 플립 칩 카드에 포장된 다이오드 트랜지스터 로직을 사용했습니다.그것은 20,000달러 [4]미만에 판매된 최초의 컴퓨터였고,[5][failed verification][6][failed verification] 그 당시 역사상 가장 많이 팔린 컴퓨터가 되었다.Straight-8은 1966년에 PDP-8/S로 대체되었습니다.PDP-8/S는 데스크톱 및 랙마운트 모델에서 사용할 수 있습니다.1비트 시리얼 산술로직 유닛(ALU)을 사용하면, 원래의 PDP-8보다 속도가 느리지만, PDP-8/S 를 소형으로 저비용으로 할 수 있었습니다.기본 8/S는 $10,000 미만으로 판매되며,[4][7] 이 이정표를 달성한 최초의 기계입니다.

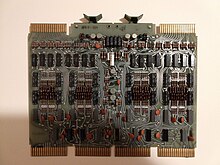

이후의 시스템(PDP-8/I 및 /L, PDP-8/E, /F 및 /M 및 PDP-8/A)은 고속 완전 병렬 구현으로 돌아왔지만 비용이 훨씬 적게 드는 트랜지금은 트랜지스터-트랜지스터 로직(TTL) MSI 로직을 사용합니다.현존하는 대부분의 PDP-8은 이 시대의 것입니다.PDP-8/E는 일반적이며 다양한 유형의 I/O 장치를 사용할 수 있기 때문에 널리 알려져 있습니다.1979년에 소개된 마지막 상용 PDP-8 모델은 CMOS 마이크로프로세서를 기반으로 한 "CMOS-8s"라고 불립니다.가격이 경쟁력 있게 책정되지 않아 제공이 실패했습니다.인터실은 1982년까지 집적회로를 Intersil 6100 제품군으로 상업적으로 판매했습니다.CMOS 테크놀로지 덕분에 전력 요건이 낮았고 일부 임베디드 군사 시스템에 사용되었습니다.

PDP-8의 초기 버전을 설계한 수석 엔지니어는 나중에 Data General을 [8]설립한 Edson de Castro였습니다.

아키텍처의 중요성

PDP-8은 저비용,[2] 단순성, 확장성 및 가치를 위한 세심한 엔지니어링을 결합합니다.역사적으로 가장 큰 의의는 PDP-8의 저비용과 대용량으로 인해 많은 신규 고객이 컴퓨터를 새로운 용도로 사용할 수 있게 되었다는 것입니다.가치 엔지니어링된[9] 컴퓨터 설계의 역사적 예로서 그 의의가 지속되고 있습니다.

복잡성이 낮기 때문에 다른 비용이 발생합니다.이 기사의 예와 "페이지"와 "필드"에 대한 논의에서 보듯이 프로그래밍을 번거롭게 만들었습니다.코드의 대부분은 알고리즘을 설정하는 것이 아니라 필요한 메카니즘을 실행했습니다.예를 들어, 숫자를 빼는 것은 두 개의 보수를 계산하고 그것을 더하는 것을 포함한다. 조건부 점프를 쓰는 것은 점프를 중심으로 조건 건너뛰기를 쓰고, 건너뛰기는 원하는 것에 대해 조건을 부정적으로 코딩한다.일부 야심찬 프로그래밍 프로젝트는 메모리에 맞지 않거나 해결할 수 없는 설계 결함을 개발하기도 했다.예를 들어 다음과 같이 서브루틴이 잘못 재귀하면 문제의 서브루틴으로 추적하기 어려운 결함이 발생합니다.

설계의 진보로 로직과 메모리의 비용이 줄어들면서 프로그래머의 시간은 상대적으로 더 [10]중요해졌다.이후의 컴퓨터 설계에서는 프로그래밍의 용이성을 강조하여 일반적으로 더 크고 직관적인 명령 [11]세트를 사용했습니다.

결국 대부분의 기계 코드는 컴파일러와 보고서 [12]생성기에 의해 생성되었습니다.축소된 명령어 집합 컴퓨터는 PDP-8이 단순 명령어 집합을 강조하고 실행 속도를 극대화하기 위해 단일 명령어 사이클에서 여러 작업을 수행하는 것을 강조했던 것으로, 새로운 컴퓨터가 훨씬 더 긴 명령어를 가지고 있음에도 불구하고 완전히 원상태로 되돌렸다.

묘사

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

PDP-8은 W.A.가 설계한 LINC를 비롯한 여러 12비트 이전 버전들의 아이디어를 사용했습니다. Clark와 C.E. Molnar는 Seymour Cray의 CDC 160 미니컴퓨터에서 [1][13]영감을 얻었다.

PDP-8은 워드크기와 산술에 12비트를 사용합니다(0~4095의 부호없는 정수 또는 -2048~+2047의 부호있는 정수).그러나 소프트웨어는 다중 정밀도 계산을 수행할 수 있습니다.예를 들어 2워드(24비트) significant(manita) 및 1워드 지수를 [14]가진 36비트 부동소수점 표현을 사용하는 부동소수점 연산에 인터프리터를 사용할 수 있었습니다.속도 및 메모리 제한에 따라 PDP-8은 IBM 1130 및 IBM System/360의 다양한 모델과 같은 고가의 현대 전자 컴퓨터와 유사한 계산을 수행하면서도 외부 장치와 더 쉽게 인터페이스할 수 있습니다.

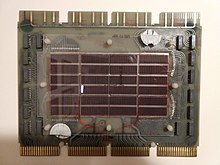

메모리 주소 공간도 12비트이므로 PDP-8의 기본 설정에는 메인 메모리가 4,096(2)12비트12 워드입니다.옵션 메모리 확장 유닛은 IOT 명령을 사용하여 메모리 뱅크를 전환할 수 있습니다.메모리는 사이클 시간이 1.5마이크로초(0.667MHz)인 자기 코어 메모리이므로 일반적인 2사이클(Fetch, Execute) 메모리 참조 명령은 0.333MIPS 속도로 실행됩니다.1974년 PDP-8/E용 포켓 레퍼런스 카드는 메모리를 참조하는 명령의 경우 1.2마이크로초의 기본 명령 시간을 제공합니다.

PDP-8은 부분적으로 현대의 통신과 텍스트를 처리하기 위해 설계되었다.당시 6비트 문자 코드가 널리 사용되었으며, PDP-8의 12비트 단어는 이러한 두 개의 문자를 효율적으로 저장할 수 있습니다.또한 텔레타이프 설정 또는 TTS 코드라고 불리는 6비트 텔레프린터 코드가 뉴스 와이어 서비스에 의해 널리 사용되었으며, PDP-8의 초기 애플리케이션은 이 [15]코드를 사용하여 조판되었습니다.

PDP-8 명령어에는 3비트의 opcode가 있기 때문에 명령어는 8개뿐입니다.어셈블러는 I/O 및 운영 모드 명령을 운영 코드와 명령 필드의 조합으로 변환함으로써 프로그래머에게 더 많은 명령 니모닉을 제공합니다.또한 프로그래머가 볼 수 있는 레지스터는 12비트 어큐뮬레이터(AC), 프로그램 카운터(PC) 및 "링크 레지스터"(L)라는 캐리 플래그 3개뿐입니다.

PDP-8은 입출력을 위해 모든 디바이스에서 공유되는 단일 인터럽트, I/O 명령에 의해 액세스되는 I/O 버스 및 DMA(Direct Memory Access) 채널을 갖추고 있습니다.프로그래밍된 I/O버스는 일반적으로 프린터, 텔레타입, 종이테이프 펀치, 리더 등의 저속 주변기기를 작동하며 DMA는 가벼운 펜, 아날로그/디지털 변환기, 디지털/아날로그 변환기, 테이프 드라이브 및 디스크 드라이브를 갖춘 브라운관 스크린에 사용됩니다.

비용 절감을 위해 이 설계는 보조 카운터 및 서브루틴 링크와 같은 다른 컴퓨터의 [16]더 비싼 플립 플랍 레지스터에 의해 제공되는 다양한 용도로 저렴한 메인 메모리를 사용합니다.

기본 모델은 소프트웨어를 사용하여 곱셈과 나눗셈을 수행합니다.더 빠른 계산을 위해 EAE(확장 산술 요소)는 추가 레지스터인 MQ(승수/쿼티언트) 레지스터와 함께 곱셈 및 나누기 명령을 제공합니다.EAE는 원래 PDP-8,[17] 8/[18]I 및 8/E의 옵션이었지만 Intersil 6100 마이크로프로세서의 일부입니다.

PDP-8은 심플한 설계를 위해 최적화되어 있습니다.복잡한 기계에 비해 불필요한 기능을 제거하고 가능하면 논리를 공유했습니다.명령어는 자동 증가, 자동 학습 및 간접 액세스를 사용하여 소프트웨어 속도를 높이고 메모리 사용을 줄이며 값비싼 레지스터 대신 저렴한 메모리를 사용합니다.

기본 PDP-8 CPU의 전자기기에는 어큐뮬레이터, 프로그램카운터, 메모리버퍼 레지스터 및 메모리주소 레지스터의 4개의 12비트 레지스터만 있습니다.비용 절감을 위해 운영 주기의 서로 다른 지점에서 여러 가지 목적을 달성했습니다.예를 들어 메모리 버퍼 레지스터는 연산 연산자를 제공하고 명령 레지스터의 일부이며 코어 메모리를 다시 쓰기 위한 데이터를 저장한다(이것에 의해 판독에 의해 파괴된 코어 데이터가 복원된다).

초기 PDP-8 모델은 단순하기 때문에 시판되는 대부분의 컴퓨터보다 가격이 저렴했습니다.그러나 그들은 종종 프로토타입에 사용되는 고가의 생산 방법을 사용했습니다.이들은 금색 커넥터가 달린 매우 작고 표준화된 수천 개의 로직 모듈을 사용했으며, 큰 캐비닛에 값비싼 복잡한 와이어로 포장된 백플레인으로 통합되었습니다.

1966년 [7]8월에 도입된 이후 8/S 모델에서는 두 개의 서로 다른 로직 전압이 저렴한 다이오드 트랜지스터 로직의 [19]팬아웃을 증가시켰습니다.또한 8/S는 직렬 단일 비트 폭 데이터 경로를 사용하여 계산을 수행함으로써 로직 게이트 수를 줄였습니다.PDP-8/S의 CPU에는 약 519개의 로직게이트밖에 없어요이에 비해 소규모 마이크로 컨트롤러(2008년 기준)는 보통 15,000개 이상을 보유하고 있습니다.전자제품의 감소로 빵 상자 크기의 훨씬 작은 케이스가 가능해졌다.8/S는 Saul Dinman이 [20]디자인했습니다.

한층 더 최신의 PDP-8/E는, 보다 크고, 보다 뛰어난 기능을 갖춘 컴퓨터이지만, 한층 더 가치를 높이기 위해서 재설계되고 있습니다.집적회로에서 보다 빠른 트랜지스터-트랜지스터 로직을 사용합니다.코어 메모리가 재설계되었습니다.이전 모델에서는 와이어로 포장된 백플레인 대신 OMNIBUS를 사용하기 때문에 적은 비용으로 확장할 수 있습니다.(PDP-8/E의 개발에 대한 개인적인 설명은 엔지니어링 및 테크놀로지 히스토리 Wiki에서 참조할 수 있습니다.[21]

PDP-8 버전

PDP-8 패밀리의 총 판매량은 30만대 이상으로 추정되고 있습니다.제조된 모델은 다음과 같습니다.

| 모델 | 묘사 | 연도 | 가격. | 생산수량 | 체중 |

|---|---|---|---|---|---|

| PDP-8 | 반분리 구성 요소.하이브리드 IC, DTL을 사용했어요 | 1965 | $18,000 | 1450 | 250파운드(150kg)[23] |

| LINC-8 | LINC 코드 또는 PDP-8 코드 중 하나를 실행할 수 있습니다. | 1966 | $38,500 | 142 | |

| PDP-8/S | PDP-8의 저비용 시리얼 버전 | 1966 | $10,000 | 1024 | 84파운드(38kg)[24] |

| PDP-8/I | 표준 TTL IC로 제조된 최초의 PDP-8 | 1968 | $12,800 | 3698 | 250파운드(110kg)[25] |

| PDP-8/L | PDP-8/I의 저비용 대응 | 1968 | $8,500 | 3902 | 80파운드(36kg)[26] |

| PDP-12 | LINC 명령을 지원하는 PDP-8/I(LINC-8을 대체) | 1969 | $27,900 | 755 | |

| PDP-8/E | 더 적은 수의 대형 보드를 사용하여 가격과 효율성을 향상 | 1970 | $6,500 | 90파운드 (41 kg) (표준)[27] | |

| PDP-8/F | PDP-8/E의 저비용 대응 | 1972 | 57파운드 (26 kg) (표준)[28] | ||

| PDP-8/M | 전면 패널이 변경된 OEM PDP-8/F | 1972 | 5,000달러[29] | 57파운드 (26 kg) (표준)[30] | |

| PDP-8/A | LSI 로직으로 CPU를 단일 보드에 장착 가능 | 1974 | $1,835 | ||

| 인터실 6100 | 싱글칩 PDP-8 호환 마이크로프로세서(VT78에서 사용) | 1975년[31][32] | |||

| 해리스 6120 | CMOS 싱글칩 PDP-8 호환 마이크로프로세서(DECmate 워드프로세서에 사용) | 1976년[32] |

최신 도입

PDP-8은 명령 세트가 현대 아키텍처보다 훨씬 단순하기 때문에 쉽게 에뮬레이트됩니다.애호가들은 단일 FPGA 디바이스를 사용하여 PDP-8 전체를 만들었습니다.

PDP-8의 몇 가지 소프트웨어 시뮬레이션을 인터넷에서 이용할 수 있으며 오픈 소스 하드웨어의 [33][34]재실장도 이용할 수 있습니다.이 중 가장 좋은 것은 DEC의 운영 체제와 진단 소프트웨어를 올바르게 실행하는 것입니다.소프트웨어 시뮬레이션에서는 가능한 모든 주변기기를 사용하여 최신 모델의 PDP-8을 시뮬레이션하는 경우가 많습니다.이마저도 현대 PC 용량의 극히 일부만을 사용합니다.

PDP-8/S 가상 머신의 첫 번째 상용 버전 중 하나는 Kaypro 386(80386 기반 컴퓨터)에서 실행되었으며, C 컴퓨터 언어(ANSI-C 표준이 확정되기 전)로 작성되었으며 콜로라도 덴버의 David Beecher에 의해 어셈블러로 작성되었습니다.그것은 콜로라도 원자력 연료 발전소의 플래트빌 85번 원자로에서 연료 취급 기계를 작동시킨 고장난 PDP-8/S 컴퓨터를 대체했다.세인트 브레인그것은 Rockwell International에 의해 검토되었고 원자로 노심으로부터 연료를 제거하고 발전소를 폐쇄하는 데 사용되는 동안 연료 핸들링 기계 작동 중 2.5년 동안 흠잡을 데 없이 수행되었다.모의 페이퍼 로더와 전면 패널이 포함되어 있습니다.

입력/출력

PDP-8 시대에 I/O 시스템은 큰 변화를 겪었습니다.초기 PDP-8 모델은 전면 패널 인터페이스, 용지 테이프 리더 및 옵션의 용지 테이프 펀치를 갖춘 텔레타이프 프린터를 사용합니다.시간이 지남에 따라 자기 테이프, RS-232 및 전류 루프 덤 터미널, 펀치 카드 리더 및 고정 헤드 디스크와 같은 I/O 시스템이 추가되었습니다.PDP-8 시대가 끝날 무렵에는 플로피 디스크와 이동식 헤드 카트리지 디스크 드라이브가 인기 있는 I/O 장치였습니다.현대의 애호가들은 실제 및 시뮬레이션된 PDP-8 컴퓨터용 표준 PC 스타일의 IDE 하드 디스크 어댑터를 개발했습니다.

몇 가지 유형의 I/O가 지원됩니다.

- I/O 컨트롤러 전용 백플레인 내 전용 슬롯

- "음" I/O 버스(음전압 신호 사용)

- "긍정적" I/O 버스(TTL 시그널링을 사용하는 동일한 아키텍처)

- PDP-8/E에 도입된 Omnibus(비전용 시스템버스 슬롯의 백플레인) (자세한 내용은 아래 참조된 IEEE 문서를 참조하십시오.)

「3 사이클 데이터 브레이크」라고 불리는 심플하고 저렴한 형식의 DMA가 서포트되고 있습니다.이를 위해서는 프로세서의 지원이 필요합니다.「데이터 브레이크」방법은, 각 I/O 디바이스로부터 DMA I/O를 실장하기 위해서 필요한 공통 로직의 일부를, 프로세서내의 로직의 1개의 공통 카피로 이동합니다."데이터 브레이크"는 프로세서가 DMA 주소 및 워드 수 레지스터를 관리하는 역할을 합니다.연속되는 3개의 메모리 사이클에서 프로세서는 워드 카운트를 갱신하고 전송 주소를 갱신하며 실제 I/O 데이터 워드를 저장 또는 검색합니다.

코어 메모리에서 전송해야 하는 것은 타깃 데이터뿐이기 때문에 1사이클의 데이터 중단은 DMA 전송 속도를 3배로 효과적으로 증가시킵니다.다만, I/O 디바이스는, 독자적인 워드수와 주소 레지스터를 관리하기 위해서, 보다 전자적인 로직이 필요합니다.PDP-8/E가 도입될 무렵에는 전자 로직의 비용이 낮아져 「1사이클 데이터 브레이크」가 보급되어 있었습니다.

프로그래밍 설비

초기 PDP-8 시스템에는 소프트웨어가 프리 인스톨 되어 있지 않았습니다.PDP-8의 전원을 켤 때마다 사용자는 12개의 토글스위치를 사용하여 수동으로 명령을 입력했습니다.통상, 이러한 순서는, 용지 테이프 리더로부터 프로그램을 읽기 위한 부트 스트랩 로더입니다.그런 다음 종이 테이프를 사용하여 프로그램 개발을 진행할 수 있습니다.

DEC의 FOCAL 인터프리터[35], 4K FORTRAN 컴파일러 및 런타임 등 여러 프로그래밍 언어의 종이 테이프 버전을 사용할 수 있게 되었습니다.

PDP-8 시대가 끝날 무렵 OS/8 및 COS-310과 같은 운영체제는 PAL-III 어셈블리 언어, FORTRAN, BASIC 및 DIBOL과 같은 언어를 사용하는 기존의 라인 모드 에디터와 명령줄 컴파일러 개발 시스템을 가능하게 했습니다.

상당히 현대적이고 고도의 실시간 운영체제(RTOS)와 프리엠프티브 멀티태스킹 멀티 사용자 시스템을 이용할 수 있었습니다.멀티 유저 상용 시스템(COS-300 및 COS-310)과 전용 싱글 유저 워드 프로세싱 시스템(WPS-8)도 이용할 수 있었습니다.

시분할 시스템인 TSS-8도 이용할 수 있었다.TSS-8에서는 여러 사용자가 110-baud 단말기를 통해 시스템에 로그인하여 프로그램을 편집, 컴파일 및 디버깅할 수 있습니다.언어에는 특수 버전의 BASIC, FORTRAN-1과 유사한 FORTRAN 서브셋(사용자 작성 서브루틴 또는 함수 없음), ALGOL 서브셋, FOCAL 및 PAL-D라고 하는 어셈블러가 포함됩니다.

상당한 양의 PDP-8용 사용자 기부 소프트웨어는 DECUS, Digital Equipment Corporation User Society에서 구할 수 있었고, 대부분의 경우 완전한 소스 목록과 문서와 함께 제공되었습니다.

명령 집합

12비트 명령어 상위3비트(라벨 비트0 ~ 2)가 동작 코드입니다.메모리를 참조하는 6가지 동작의 경우 비트5 ~ 11은 7비트주소를 제공합니다.비트 4(설정되어 있는 경우)는 프로그램카운터(PC) 레지스터의 상위5비트를 사용하여 주소를 완성하도록 지시합니다.즉, 주소 지정된 위치가 명령과 동일한 128워드 내에 있음을 의미합니다.비트 4가 클리어인 경우 0이 사용되므로 주소 지정 위치는 메모리의 첫 번째 128워드 내에 있습니다.비트 3은 인다이렉션을 지정합니다.설정되어 있는 경우 지금까지 설명한 바와 같이 취득한 주소는 명령의 실제 유효 주소를 제공하는 메모리 내의 12비트 값을 가리킵니다.이것에 의해, 오퍼랜드는 추가 워드를 희생해 메모리내의 임의의 장소에 존재할 수 있습니다.JMP 명령은 indirection이 지정되어 있는 경우를 제외하고 메모리 워드에서는 동작하지 않지만 비트필드는 동일합니다.

| 0 | 2 | 3 | 4 | 5 | 11 | ||||||

| 작동 | I | Z | 오프셋 | ||||||||

- 메모리 페이지

이 명령어를 사용하면 4,096 워드 메모리가 128 워드 페이지로 분할됩니다.이 명령어의 비트4는 현재 페이지 또는 페이지0 중 하나를 선택합니다(8진수에서는 0000 ~0177 의 주소).여기에 배치되는 변수는 어느 페이지에서나 직접 처리할 수 있기 때문에 0페이지의 메모리는 프리미엄입니다.(게다가, 주소 0000은 인터럽트 서비스 루틴이 개시되는 장소이며, 주소 0010 ~0017은, 그것들을 개입시켜 간접 참조를 실시하기 전에 자동적으로 증가시키는 특별한 속성을 가지고 있습니다).

표준 어셈블러는 현재 페이지에 산술에 대한 상수 값을 배치합니다.마찬가지로 크로스 페이지 점프 및 서브루틴 콜에서도 현재 페이지의 간접 주소가 사용됩니다.

128단어 이내의 루틴을 작성하거나 페이지 전환을 최소화하기 위해 루틴을 배열하는 것이 중요했습니다. 참조 및 현재 페이지 이외의 점프는 추가 단어를 필요로 하기 때문입니다.그 결과, 많은 시간이 하나 또는 여러 단어를 현명하게 보존하는 데 소비되었다.프로그래머들은 PC가 증가하면 다음 페이지로 자유롭게 이동할 수 있도록 의도적으로 페이지 끝에 코드를 배치했습니다.

기본 절차

- 000 – AND – 및 메모리 오퍼랜드(AC 포함).

- 001 – TAD – 2는 메모리 오퍼랜드를 <L,AC>(L로 반송하는 12비트 부호값(AC))에 ADd를 보완합니다.

- 010 – ISZ – 결과가 제로일 경우 메모리 오퍼랜드를 증가시키고 다음 명령을 건너뜁니다.

- 011 – DCA – AC를 메모리 오퍼랜드에 저장하고 AC를 클리어합니다.

- 100 – JMS – Jump to Subroutine (서브루틴의 첫 번째 단어로 반환 주소 저장!)

- 101 – JMP – JUMP.

- 110 – IOT – 입력/출력 전송(아래 참조).

- 111 – OPR – 마이크로코드화된 OPeations (아래 참조).

IOT(Input-Output Transfer) 명령

PDP-8 프로세서는 IOT 명령 중 몇 가지를 정의했지만 프레임워크만 제공했습니다.대부분의 IOT 명령은 개별 I/O 장치에 의해 정의되었습니다.

| 0 | 2 | 3 | 8 | 9 | 11 | ||||||

| 6=IOT | 장치 | 기능. | |||||||||

- 장치

IOT 명령의 비트 3~8은 I/O 디바이스를 선택한다.이러한 디바이스 주소의 일부는 통례로 표준화되어 있습니다.

- 00는 프로세서에 의해 처리되며 I/O 장치로 전송되지 않습니다(아래 참조).

- 01은 보통 고속 종이 테이프 리더입니다.

- 02는 고속 테이프 펀치입니다.

- 03은 콘솔 키보드(및 관련된 저속 종이 테이프 리더)입니다.

- 04는 콘솔 프린터(및 관련된 저속 테이프 펀치)입니다.

디바이스 0 의 순서는, CPU 전체에 영향을 줍니다.예를 들어 ION(6001)은 인터럽트 처리를 이노블로 하고 IOFF(6002)는 인터럽트 처리를 디세블로 합니다.

- 기능.

IOT 명령의 비트 9~11은 디바이스가 실행하는 기능을 선택한다.종이 테이프 리더나 펀치, 콘솔 키보드나 프린터 등, 심플한 디바이스에서는, 표준적인 방법으로 비트를 사용합니다.

- 비트 11은 I/O 디바이스가 준비되면 프로세서가 다음 명령을 건너뜁니다.

- 비트 10은 AC를 클리어합니다.

- 비트 9는 AC와 디바이스 간에 워드를 이동하고 다른 I/O 전송을 시작하여 디바이스의 "ready" 플래그를 지웁니다.

이러한 작업은 둘 이상의 비트가 설정된 경우 유용한 결과를 제공하는 명확한 순서로 수행됩니다.

디스크 드라이브 등 보다 복잡한 디바이스에서는 이들 3비트를 디바이스 고유의 방법으로 사용합니다.일반적으로 장치는 3비트를 디코딩하여 8개의 기능 코드를 제공합니다.

OPR(OPeRate)

대부분의 조건을 포함하여 많은 연산이 OPR을 사용하여 달성됩니다.OPR은 메모리 위치를 지정하지 않습니다.조건부 실행은 1개의 명령(통상은 JMP)을 조건부로 건너뛰는 것으로 실현됩니다.

OPR 명령은 "마이크로 코딩"되어 있다고 합니다.이것은 오늘날 그 단어가 의미하는 바가 아니라(하위 수준의 프로그램이 OPR 명령을 가져오고 해석하는) 명령어의 각 비트가 특정 동작을 지정하며 프로그래머는 여러 비트를 설정함으로써 단일 명령 사이클에서 여러 동작을 수행할 수 있다는 것을 의미합니다.사용 시에 프로그래머는 여러 명령어 니모닉을 서로 병기할 수 있으며 어셈블러는 이를 OR과 결합하여 실제 명령어를 고안한다.많은 I/O 디바이스는 "마이크로코드" IOT 명령을 지원합니다.

마이크로코드화된 액션은 많은 조합의 효용을 최대화하기 위해 설계된 명확한 순서로 수행됩니다.

OPR 지침은 그룹으로 제공됩니다.비트 3, 8, 11은 OPR 명령의 그룹을 식별하기 때문에 다른 그룹의 마이크로코드 액션을 조합할 수 없습니다.

그룹 1

00 01 02 03 04 06 07 08 09 10 11 _______________________________________CLA CMA RAR BSW CML RAL IAC 2 - 1 - 1 _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

- 7200 – CLA – 클리어 어큐뮬레이터

- 7100 – CLL – L비트 클리어

- 7040 – CMA –1개의 보완 어큐뮬레이터

- 7020 – CML – 보완 L 비트

- 7001 – IAC – 증가 < L,AC>

- 7010 – RAR –오른쪽 회전 <L, AC>

- 7004 – RAL – 왼쪽으로 회전 <L, AC>

- 7012 – RTR – <L, AC> 우회전 2회

- 7006 – RTL – <L, AC> 왼쪽으로 2회 회전

- 7002 – BSW – 바이트 스왑 6비트 "바이트" (PDP 8/e 이후)

대부분의 경우 작업은 가장 유용한 방법으로 결합될 수 있도록 시퀀스가 지정됩니다.예를 들어 CLA(CLEAR 어큐뮬레이터), CLL(CLEAR Link) 및 IAC(Increment ACcumulator)를 조합하면 먼저 AC와 링크가 클리어되고 다음으로 어큐뮬레이터가 증가하여 1로 설정됩니다.RAL을 혼합에 추가하면(따라서 CLA CLL IAC RAL), 축전지 클리어, 증가, 왼쪽으로 회전하여 2로 설정됩니다.이러한 방식으로 작은 정수 상수가 하나의 명령으로 축적기에 배치되었습니다.

어셈블러에서 CIA로 생략할 수 있는 CMA IAC의 조합은 AC의 산술 역수인 2개의 보완 부정(twos-completment negration)을 생성합니다.감산 명령어가 없기 때문에, 2개의 오퍼랜드의 차이를 계산하는 2개의 보완 덧셈(TAD)만이 먼저 서브 헨드를 부정할 필요가 있습니다.

그룹 1 OPR 명령에서는 마이크로프로그래밍된 비트세트가 존재하지 않습니다.프로그래머는 NOP(No Operation)를 작성하여 이러한 명령을 조립할 수 있습니다.

그룹 2, 또는 그룹

00 01 02 03 04 06 07 08 09 1011 _________________________________________________________________________________________________________________________________

- 7600 – CLA – 클리어 AC

- 7500 – SMA – AC < 0 (또는 그룹)의 스킵

- 7440 – SZA – AC = 0(또는 그룹)을 건너뜁니다.

- 7420 – SNL – L 0 0 (또는 그룹)을 건너뜁니다.

- 7404 – OSR – 논리적으로 AC를 탑재한 프론트 패널 스위치

- 7402 – HLT – 정지

비트 8이 클리어되면 지정된 조건 중 하나에 해당하는 경우 건너뛰기가 수행됩니다.예를 들어 "SMA SZA", opcode 7540은 AC가 0이면 건너뜁니다.

그룹 2 OPR 명령어 중 마이크로프로그래밍된 비트세트가 없는 것도 No-Op 명령어입니다.

그룹 2, 및 그룹

00 02 03 04 06 07 08 09 10 11 ____________________________________________ SNA OSR SPA SZLT 2 1 1 3 2

- 7410 – SKP – 무조건 건너뛰기

- 7610 – CLA – 클리어 AC

- 7510 – SPA – AC 00 (및 그룹)의 스킵

- 7450 – SNA – AC 00 (및 그룹)의 스킵

- 7430 – SZL – L = 0(및 그룹)을 건너뜁니다.

비트 8을 설정하면 De Morgan의 법칙에 따라 그룹 2, 또는 건너뛰기 조건이 반전됩니다. 즉, 그룹 2, 또는 조건이 모두 참이면 건너뛰기가 수행되지 않습니다. 즉, 지정된 모든 건너뛰기 조건이 참이어야 합니다.예를 들어 "SPA SNA", opcode 7550은 AC > 0이면 건너뜁니다.비트 5 ~7이 설정되어 있지 않으면 건너뜁니다.

그룹 3

사용되지 않는 OPR의 비트 조합은 주로 MQ(Multiplier/Quotient) 레지스터에 영향을 미치는 세 번째 마이크로 프로그래밍된 액션 그룹으로 정의됩니다.MQ 레지스터 및 확장 산술 요소(EAE) 명령은 옵션이며 EAE 옵션을 [36]구입한 경우에만 존재합니다.

00 01 02 03 04 06 07 08 09 10 11 ________________________________________________________________________________________________ CLA SCA SCA SCA \ _/ MQA SCA MQA MQL 코드 1 2 2 2 2 - 1 - 2 - 2

- 7601 – CLA – AC 클리어

- 7501 – MQA – AC를 사용하는 승수 지수(논리 또는 MQ를 AC로 입력)

- 7441 – SCA – AC로의 스텝 카운터 로드

- 7421 – MQL – 승수 비율 부하 (AC에서 MQ로 전송, AC 클리어)

- 7621 – CAM – CLA + MQL은 AC와 MQ를 모두 클리어합니다.

일반적으로 CLA와 MQA는 MQ를 AC로 전송하기 위해 결합되었습니다.또 다른 편리한 조합은 2개의 레지스터를 교환하기 위한 MQA와 MQL입니다.

3비트가 다음을 수행하기 위해 곱셈/나눗셈 명령을 지정했습니다.

- 7401 – 동작 없음

- 7403 – SCL – 스텝카운터 로드 (즉시 PDP-8/I 이후)

- 7405 – MUY – 곱셈

- 7407 – DVI – 분할

- 7411 – NMI – 정상화

- 7413 – SHL – 왼쪽으로 이동(즉각 단어 뒤에 있음)

- 7415 – ASR – 산술 시프트 우측

- 7417 – LSR –논리 시프트 우측

메모리 컨트롤

12비트 워드는 4,096개의 다른 값을 가질 수 있습니다.이것은 원래 PDP-8이 워드 포인터를 통해 간접적으로 주소를 지정할 수 있는 최대 워드 수입니다.4,096개의 12비트 워드는 현대 용어로는 6,144바이트, 즉 6kB를 나타냅니다.프로그램이 복잡해지고 메모리 가격이 떨어지면서 이 제한을 확대하는 것이 바람직해졌다.

기존 프로그램과의 호환성을 유지하기 위해 원래 설계 외의 새로운 하드웨어는 프로그램에 의해 생성된 유효 주소에 상위 비트를 추가했습니다.메모리 확장 컨트롤러는 주소 지정 가능한 메모리를 8배 확장하여 총 32,768 워드로 확장합니다.코어 메모리의 경우 워드당 약 50센트의 비용이 들기 때문에 32K의 메모리 풀은 CPU의 비용과 같기 때문에 이 확장은 충분하다고 생각되었습니다.

각 4K의 메모리를 필드라고 부릅니다.메모리 확장 컨트롤러에는 DF(데이터 필드)와 IF(인스트럭션 필드)의 2개의 3비트 레지스터가 있습니다.이러한 레지스터는 CPU의 각 메모리 기준의 필드를 지정하여 총 15비트의 주소를 허용합니다.IF 레지스터는 명령 가져오기 및 직접 메모리 참조 필드를 지정하고, DF 레지스터는 간접 데이터 액세스 필드를 지정합니다.한 필드에서 실행되는 프로그램은 직접 어드레싱으로 같은 필드의 데이터를 참조하고 간접 어드레싱으로 다른 필드의 데이터를 참조할 수 있다.

6200~6277 범위의 일련의 I/O 명령은 메모리 확장 컨트롤러에 의해 처리되며 DF 및 IF 레지스터에 액세스할 수 있습니다.62X1 명령(CDF, 데이터 필드 변경)은 데이터 필드를 X로 설정합니다.마찬가지로 62X2(CIF)는 명령 필드를 설정하고 62X3은 둘 다 설정합니다.기존 프로그램은 CIF 또는 CDF를 실행하지 않습니다. DF 레지스터와 IF 레지스터는 모두 동일한 필드, 즉 이들 프로그램이 제한된 단일 필드를 가리킵니다.CIF 명령의 효과는 다음 JMP 또는 JMS 명령과 일치하도록 지연되었습니다.따라서 CIF를 실행하면 점프가 발생하지 않습니다.

필드 경계와 DF 및 IF 레지스터를 처리하는 것은 단순히 15비트 주소를 생성할 수 있는 경우보다 더 복잡했지만 설계는 하위 호환성을 제공했으며 PDP-8 전체에서 사용되는 12비트 아키텍처와 일관성이 있습니다.새로운 인텔 8086을 비교합니다.이 인텔 8086의 16비트 메모리 주소는 지정된 세그먼트레지스터 또는 암묵적인 세그먼트레지스터의 컨텐츠와 조합해 20비트로 확장됩니다.

확장 메모리 스킴을 사용하면 기존 프로그램이 최소한의 변경으로 늘어난 메모리를 처리할 수 있습니다.예를 들어, 4K FOCAL은 보통 약 3K의 코드를 가지고 있었고, 사용자 프로그램 및 데이터에는 1K의 코드만 남아 있었습니다.몇 가지 패치를 적용하면 FOCAL은 사용자 프로그램 및 데이터에 두 번째 4K 필드를 사용할 수 있습니다.또한 4K 필드를 별도의 사용자에게 할당하여 4K FOCAL을 다중 사용자 시분할 시스템으로 만들 수 있습니다.

- 가상화

PDP-8/E 이후 모델에서는 메모리 확장 컨트롤러가 확장되어 머신의 가상화가 가능하게 되었습니다.PDP-8의 전체 리소스를 사용하도록 작성된 프로그램은 가상 시스템 관리자의 제어 하에 동일한 PDP-8의 다른 프로그램과 공존할 수 있습니다.매니저는 모든 I/O 명령(메모리 확장 컨트롤러에서 동작하는 명령 포함)을 트랩(매니저가 처리하는 인터럽트)을 발생시킬 수 있습니다.이렇게 하면 관리자는 메모리 참조를 매핑하거나 데이터 또는 명령 필드를 매핑하거나 I/O를 다른 장치로 리디렉션할 수 있습니다.각 원래 프로그램은 관리자가 제공하는 "가상 머신"에 완전히 액세스할 수 있습니다.

Memory Extension Controller에 대한 새로운 I/O 명령은 데이터 및 명령 필드의 현재 값을 가져오므로 소프트웨어가 트랩을 통해 대부분의 시스템 상태를 저장하고 복원할 수 있습니다.그러나 프로그램은 CPU가 CIF 명령의 효과를 지연시키는 처리 중인지(CIF를 실행했는지, 매칭 점프 명령을 아직 실행하지 않았는지)를 감지할 수 없다.매니저는 완전한 PDP-8 에뮬레이터를 포함해야 합니다(8 명령 머신에서는 어렵지 않습니다).CIF 명령이 매니저에게 트랩될 때마다 다음 점프까지 명령을 에뮬레이트해야 합니다.다행히 점프는 보통 CIF 다음 명령이기 때문에 이 에뮬레이션은 프로그램 속도를 크게 낮추지는 않지만, [citation needed]외관상으로는 작은 설계 결함을 해결하는 데 큰 도움이 됩니다.

PDP-8/A가 출시될 무렵에는 메모리 가격이 32K를 초과하는 것이 바람직할 정도로 하락했습니다.8/A에는 8개 이상의 메모리 필드를 처리하기 위한 새로운 명령 세트가 추가되었습니다.이제 필드 번호를 명령에 하드 코딩하지 않고 AC에 배치할 수 있습니다.그러나 이때까지 PDP-8은 쇠퇴하고 있었기 때문에 이러한 새로운 기능을 사용하기 위해 변경된 표준 소프트웨어는 거의 없었습니다.

예

다음으로 PAL-III 어셈블러에 쓸 수 있는 코드를 PDP-8 어셈블리 언어로 표시하는 예를 나타냅니다.

두 숫자의 비교

다음 코드는 두 숫자를 비교하는 데 필요한 내용을 보여 줍니다.

OPD1과 OPD2 CLA CLL의 메모리 내 숫자를 비교합니다.AC에서 0으로 시작하여 TAD OPD1/Load first 피연산자를 AC로 링크합니다(0에 추가). 링크는 여전히 clear CIA/Completment, 다음으로 증가 AC, TAD OPD2/AC2를 부정합니다.링크가 클리어 JMP OP2GT / Jump일 경우 SZL / Skip 이 설정됩니다.OPD2' OPD1의 경우, /Jump 이 설정되어 있지 않은 경우는, 이하의 코드로 넘어갑니다.

그림과 같이 일반적인 PDP-8 프로그램의 텍스트 대부분은 저자가 의도한 알고리즘이 아니라 저수준의 메커니즘에 초점을 맞추고 있습니다.또 다른 가독성 문제는 위와 같은 조건부 점프에서는 조건부 명령(JMP를 건너뛰는 명령)이 관심 조건의 반대가 강조된다는 것입니다.

문자열 출력

이 완전한 PDP-8 어셈블리 언어 프로그램은 텔레프린터에 "Hello, world!"를 출력합니다.

*10 / 현재 어셈블리 원점을 주소 10, STPTR, STRNG-1 / 자동 증분 레지스터(10-17에서 8개 중 하나) *200 / 현재 어셈블리 원점을 프로그램 텍스트 영역 HELLO, CLL / Clear AC 및 Link로 설정(tls에서 루프백할 때 필요) TAD IZ STPTR Get Ne/xt 문자, 제로 페이지의 SNA에서 PRE-auto-increment 주소를 경유하여 간접적으로 HLT(문자 끝이 아님)/0에서 정지한 경우 건너뛰기(문자 끝) TLS/텔레프린터 TSF로 AC 문자 출력/문자 준비 완료 시 건너뛰기JMP .-1 / 점프백 후 재시도 JMP HELLO / 다음 문자 STRNG, 310 / H 345 / e 354 / l 354 / l 357 / o 254 / 240 / (스페이스) 367/ w 357 / o 362 / r 354 / l 344 / d 241 / ! 0 / 문자열 끝 $HELLO / DEFAULT 터미네이터

서브루틴

PDP-8 프로세서는 서브루틴이 호출되거나 인터럽트가 발생했을 때 레지스터나 다른 콘텍스트를 저장하는 스택을 실장하지 않습니다(다음 섹션에서 설명하듯이 스택은 소프트웨어로 실장할 수 있습니다).대신 JMS 명령은 업데이트된 PC(JMS를 지나 리턴 주소를 가리키며)를 유효 주소에 저장하고 유효 주소+1로 점프합니다.서브루틴은 서브루틴의 첫 번째 워드에 주소를 지정하는 간접 JMP 명령을 사용하여 발신자에게 반환되었습니다.

예를 들어 서브루틴을 사용하기 위해 고쳐 쓴 "Hello, World!"가 여기에 있습니다.JMS 명령이 서브루틴으로 점프하면 위치 OUT1:

*10 / 현재 어셈블리 원점을 주소 10, STPTR, STRNG-1 / 자동 증분 레지스터(10-17에서 8개 중 하나) *200 / 어셈블리 원점(로드 주소) LOUP 설정, TAD I STPTR / 사전 증분 메모리 위치 10, 메시지 S의 다음 문자를 가져오기 위해 간접적으로 가져옵니다.NA / 0이 아닌 AC HLT의 건너뛰기 / 메시지 끝에 정지 JMS OUT1 / 1글자의 JMP LOUP 쓰기 / 기타 OUT1, 0 / 프린터 준비 완료 시 Skip으로 대체됩니다./ 플래그 TLS / AC CLA CLL / Clear AC 및 Link에서 다음 패스 JMP I OUT1 / Return to caller STRNG, "H / A well-known message "e / " l / 메모 : "l / o "/ PAL-8 및 PAL-III 문자열은 "6비트", / ASCII를 사용하기 위해 / "w / o / r / " l / " d / " !/ 015 / 012 / 0 / null 끝 문자열(.)의 끝을 표시합니다.ASCIZ는 아직 발명되지 않았어!)

JMS 명령은 서브루틴의 코드 바로 앞에 있는 단어를 사용하여 리턴 주소를 저장하기 때문에 프로그래머에 의한 추가 작업 없이 재진입과 재귀가 방지됩니다.또, PDP-8 로의 ROM 를 사용하는 것도 어려워집니다.이것은, 주소 공간내의 읽기 전용의 코드 스토리지와 읽기/쓰기 리턴 주소 스토리지가 혼재하고 있기 때문입니다.ROM 에 배치하는 것을 목적으로 하는 프로그램에서는, 이 문제에 다음의 몇개의 방법으로 대처합니다.

- 실행 전에 자신을 읽기/쓰기 메모리에 복사합니다.

- 이것들은, 몇개의 워드의 읽기/쓰기 메모리를 제공하는 특수한 ROM 카드에 배치되어 각 ROM 워드의 13번째 플래그 비트를 사용해 간접적으로 액세스 됩니다.

- 서브루틴을 사용하지 않거나 JMS 명령 대신 다음과 같은 코드를 사용하여 반환 주소를 읽기/쓰기 메모리에 저장합니다.

JUMPL, DCA TEMP / 어큐뮬레이터를 임시 위치에 보관 TAD JUMPL+3 / 반환 주소를 어큐뮬레이터에 로드합니다.하드코드화된 JMP SUBRO / 서브루틴으로 이동하여 JUMPL+3으로 점프백합니다.

JMS 명령어를 사용하면 디버깅이 어려워집니다.프로그래머가 직접 또는 중간 서브루틴에 의해 서브루틴 콜 자체를 갖는 실수를 하면 외부 콜의 리턴 주소가 후속 콜의 리턴 주소에 의해 파괴되어 무한 루프가 발생합니다.1개의 모듈이 서브루틴에 대해 올바르지 않거나 오래된 주소로 코드화되어 있는 경우 서브루틴의 코드 시퀀스 전체를 실행하는 데 실패할 뿐만 아니라 서브루틴 코드의 워드를 수정하여 서브루틴에 대한 후속 올바른 호출 중에 프로세서가 명령으로 해석할 수 있는 리턴 주소를 저장할 수 있습니다.올바르게 기술된 코드를 실행하는 동안 두 가지 유형의 오류가 모두 나타날 수 있습니다.

소프트웨어 스택

PDP-8에는 하드웨어 스택이 없지만 [37]스택은 소프트웨어로 구현할 수 있습니다.다음으로 PUSH 서브루틴과 POP 서브루틴의 예를 나타냅니다.스택 오버플로우나 언더플로우 테스트 등의 문제를 생략할 수 있습니다.

* 100 / make 루틴을 다음 예에서 PUSH, 0 DCA DATA CMA / - 1 TAD SP TAD DATA DCA I JMP I PUSH / Return POP, 0 CLL TAD I SP ISZ SP JMP 0, 0 SP 데이터

다음은 이 "stack"을 구현한 "Hello World"와 "OUT" 서브루틴입니다.

* 200 MAIN, CLA CLL / 메시지 포인터 TAD (MESG / 메시지 (리터럴) DCA SP 루프, JMS POP SNA / HLT JMS OUT이 0이면 실행 중지 / 그렇지 않으면 JMP LOUP MESG, HE를 출력합니다.l " l " o " , " w " o " r " d " ! 015 012 0 OUT , 0 / 발신자의 갱신된 PC TSF / 프린터가 준비되면 건너뛰기 / 1 /플래그 TLS / AC CLA CLL / Clear AC and Link for next pass JMP I OUT / Return to caller

링크 리스트

PDP-8에 대해 생각할 수 있는 다른 서브루틴은 링크 리스트입니다.

GETN, 0 / 포인터 CLA CLL / Clear accumulator TAD I PTR / DCA TEMP / 현재 값 ISZ PTR / 증분 포인터 TAD I PTR / Get next address DCA PTR / Get next address DCA PTR / Get IMP 포인터의 포인터를 가져오고 이동합니다.

인터럽트

PDP-8 I/O버스에 인터럽트 회선이1개 있어요프로세서는 더 이상의 인터럽트를 디세블로 하고 다음 인터럽트를 실행하여 모든 인터럽트를 처리합니다.JMS로케이션 0000으로 이동합니다.재진입 서브루틴을 쓰는 것은 어렵기 때문에 인터럽트를 네스트하는 것은 어렵고 이것은 보통 실행되지 않습니다.각 인터럽트는 완료까지 실행되며 인터럽트를 실행 직전에 다시 유효하게 합니다.JMP I 0인터럽트에서 반환되는 명령입니다.

I/O 버스에는 인터럽트 행이1개밖에 없기 때문에 인터럽트가 발생해도 프로세서에 인터럽트의 소스가 통지되지 않습니다.대신 인터럽트 서비스 루틴은 각 활성 I/O 디바이스를 시리얼 폴링하여 소스인지 여부를 확인해야 합니다.이를 실행하는 코드는 일련의 PDP-8 "test and skip if flag set" I/O 명령으로 구성되기 때문에 건너뛰기 체인이라고 불립니다.(스킵 체인이 서비스를 필요로 하는 디바이스를 발견하지 않고 끝까지 도달한 것은 전례가 없는 일이 아닙니다.)I/O 디바이스의 상대적 인터럽트 우선순위는 건너뛰기 체인 내의 위치에 따라 결정됩니다.여러 디바이스가 중단되는 경우 먼저 건너뛰기 체인으로 테스트된 디바이스가 먼저 서비스됩니다.

책들

1980년대에 인기를 끌었던 공학 교과서 데이비드 빙클과 프랭클린 프로서의 디지털 디자인의 예술은 저자들이 PDP-8/I와 호환되는 컴퓨터를 설계하는 과정을 보여주는 몇 개의 장에 걸쳐 예시적인 문제를 포함하고 있다.모든 구성 요소의 기능에 대해 설명합니다.실가동 설계는 아니지만 코어 메모리가 아닌 보다 현대적인 SSI 및 MSI 컴포넌트와 솔리드 스테이트를 사용하기 때문에 이 연습에서는 컴퓨터 동작에 대한 자세한 설명을 제공합니다.

라이선스가 없는 클론

소련은 PDP-8과 PDP-8/E를 복제한 미니컴퓨터 사라토프-1과 사라토프-2를 각각 생산했다.

레퍼런스

- ^ a b "PDP-8 Summary of Models and Options". Section - What is a PDP-5.

- ^ a b Douglas W. Jones. "The Digital Equipment Corporation PDP-8 -- Frequently Asked Questions".

- ^ 1634–1699:McCusker, J.J.(1997년).얼마나 리얼 머니에 그렇죠?역사적 가격 지수를 사용하여 경제 미국의 안의 돈 가치에 관한 Deflator로:.부칙 et Corrigenda(PDF).미국 골동품 협회입니다.1700–1799:McCusker, J.J.(1992년).얼마나 리얼 머니에 그렇죠?역사적 가격 지수 이용 돈은 가치관의 경제 미국(PDF)의 Deflator로.미국 골동품 협회입니다.1800–present:연방 준비 은행이 미니애 폴리스의."소비자 물가 지수(추정)1800–".4월 16일 2022년 Retrieved.

- ^ a b Schein, Edgar H. (2004). DEC is dead, long live DEC: the lasting legacy of Digital Equipment Corporation. San Francisco, Calif.: Berrett-Koehler Publishers. p. 271. ISBN 1576753050.

- ^ Douglas W. Jones. "The Digital Equipment Corporation PDP-8".

- ^ "PDP-8 1965". History Wired. Smithsonian Institution. 16 March 2012. Archived from the original on 2015-02-17. Retrieved February 17, 2015.

- ^ a b "PDP-8/S #1". Rhode Island Computer Museum. Aug 18, 2020. Archived from the original on 2021-02-26. Retrieved May 7, 2021.

- ^ Glenn Rifkin; George Harrar (1988). The ultimate entrepreneur: the story of Ken Olsen and Digital Equipment Corporation. ISBN 978-1-55958-022-9.

- ^ Small Computer Handbook, NEW PDP 8/I edition (Forward). Digital Equipment Corporation. 1968.

- ^ "Benchmarking the Languages". PC Magazine. Vol. 4, no. 22. October 29, 1985. p. 112.

the best use of today's most precious computer resource: a programmer's time ...

- ^ Texas Instruments 마이크로컴퓨터에 "TMS320C28x CPU and Instruction Set (Rev. F)" (PDF).관한 2007년 문서의 "중앙처리장치(CPU) 소개" 섹션 1.1에 사용된 문구.

- ^ Torben Ægidius Mogensen (August 20, 2010). Basics of Compiler Design (PDF). p. 1.

Another advantage of using a high-level level language is that the same program can be compiled to many different machine languages and, hence, be brought to run on many different machines.

- ^ C. Gordon Bell; J. C. Mudge; J. E. McNamara (1978). Computer Engineering: A DEC View of Hardware Systems Design (PDF). Digital Press. p. 175. ISBN 0-932376-00-2.

- ^ PDP-8 Floating-Point System Programmers Reference Manual (PDF). Digital Equipment Corporation. September 1969. DEC-08-YQYB-D.

- ^ "PDP-8 Typesetting System" (PDF). Digital Equipment Corporation. 1965.

- ^ C. Gordon Bell 등;Computer Structures, Principle and Organization, 1982, PDP-8 장

- ^ "Chapter 8: Extended Arithmetic Element Type 182". PDP-8 User's Handbook. Digital Equipment Corporation. 1966. p. 41.

- ^ "Chapter 4: System Description and Operation". Introduction to Programming (PDF). Digital Equipment Corporation. 1969. pp. 4–22.

- ^ PDP-8/S Maintenance Manual. Digital Equipment Corporation. 1971.

- ^ "PDP -8/S". PDP-8 Technology Before The Millennium. Archived from the original on 2000-10-23. Retrieved 2021-05-13.

- ^ Remo J. Vogelsang (2013). "First-Hand:PDP-8/E OMNIBUS Ride".

- ^ "PDP-8 Summary of Models and Options (posted every other month)". www.faqs.org.

- ^ "PDP-8 - A High Speed Digital Computer" (PDF). 1965. p. 18.

- ^ PDP-8/S Maintenance Manual (PDF) (5th ed.). October 1970. p. 1-2.

- ^ "Table 11. Installation data". Small Computer Handbook (PDF) (1967-68 ed.). 1968. p. 290 (300).

- ^ "Table 13-1 Installation data". Small Computer Handbook (PDF) (1970 ed.). 1970. p. 277 (291).

- ^ "PDP-8 Family Specifications". PDP-8/e/f/m Sales Brochure (PDF). p. 17.

- ^ "PDP-8 Family Specifications". PDP-8/e/f/m Sales Brochure (PDF). p. 17.

- ^ "System Source Computer Museum: PDP-8M".

- ^ "PDP-8 Family Specifications". PDP-8/e/f/m Sales Brochure (PDF). p. 17.

- ^ "The Explosion 1975-1976 » AntiqueTech". AntiqueTech.com. 2009-04-21. Archived from the original on 2017-07-03. Retrieved 2017-06-19.

- ^ a b Bell, Gordon (1980), Family Tree of Digital's Computers, (Poster), Digital Equipment Corporation, retrieved 2017-06-19

- ^ "SBC6120". 2011-12-05. Retrieved 2016-05-14.

- ^ "Obsolescence Guaranteed". Retrieved 2016-05-14.

- ^ FOCAL Programming Manual for PDP-8, PDP-8/S, PDP-8/I, LAB-8, LINC-8 (PDF). Digital Equipment Corporation. 1968. DEC-08-AJAB-D.

- ^ Small Computer Handbook 1967-1968. Digital Equipment Corporation. 1968. pp. 130–136.

- ^ 마크 스머더맨."DEC PDP-8 서브루틴"2002.

외부 링크

- pdp-8 매뉴얼: Small Computer Handbook(1966년판), 섹션 1 및 섹션 2 등은 Simon Fraser University에서 구할 수 있습니다.

- "PDP-8 Frequently Asked Questions". www.faqs.org. Single page. 27 March 2014. Retrieved 2018-12-16.

{{cite web}}:외부 링크others= - http://homepage.cs.uiowa.edu/~http/pdp8/

- "PDP-8 Summary of Models and Options". www.faqs.org. Single page. 27 March 2014. Retrieved 2018-12-16.

{{cite web}}:외부 링크others= - pdp8online.com에는 Java 애플릿을 통해 누구나 제어할 수 있는 PDP8이 실행 중이며 결과를 표시하는 웹캠도 있습니다.

- dpa, 휴대용 PDP-8 크로스어셈블러

- 스페어 타임 Gizmos의 SBC6120 PDP-8 호환 컴퓨터(옵션 프론트 패널 포함)

- 독일 컴퓨터 박물관에서 Classic 8, PDP 8e 및 8i 작업 중

- Bernhard Bahr의 매끄러운 Macintosh용 PDP-8/E 시뮬레이터

- Java에서의 Willem van der Mark의 PDP-8/E 시뮬레이터

- http://simh.trailing-edge.com는 거의 모든 최신 OS에서 작동하는 PDP-8용 휴대용 시뮬레이터입니다.

- PDP-8의 오픈 소스 복제본은 PDP-8 전면 패널 복제본에 연결된 SIMH를 실행하는 Rasberry Pi를 사용합니다.

- Digital Equipment Corporation PDP-8, 1965 – Smithsonian의 컴퓨터 이력 컬렉션

- 독일에서 모든 도이체방크 센터 및 기타 금융기관에 PDP8을 적용한 과거 사례:올림피아 멀티플렉스 80(올림픽 비즈니스 시스템)

- PDP-8 컴퓨터 보존 및 복원 가이드

- Digital Equipment Corporation의 PDP-8 Steve Gibson의 PDP-8 작동 원리와 프로그램 방법에 대한 설명.

- 유튜브에는 PDP-8을 보여주는 비디오 시리즈가 있다.

- "Index of PDP-8 documents". BitSavers.Org web site. Retrieved May 29, 2011.