알파 21064

Alpha 21064Alpha 21064는 Digital Equipment Corporation에서 개발 및 제조한 마이크로프로세서이며 Alpha(Alpha AXP) 명령 집합 아키텍처(ISA)를 구현했습니다.그것은 1994년에 이름이 바뀌기 전에 DEC칩 21064로 소개되었다.21064는 EV4라는 코드네임으로도 알려져 있다.1992년 2월에 발표되었으며 1992년 9월에 판매될 예정입니다.21064는 Alpha ISA의 첫 상용 구현이며, Digital의 첫 마이크로프로세서입니다.1993년 10월에 파생 모델인 알파 21064A가 그 뒤를 이었다.

역사

최초의 알파 프로세서는 EV3라는 이름의 테스트 칩이었습니다.이 테스트 칩은 디지털 1.0마이크로미터(μm) CMOS-3 공정을 이용해 제작됐다.테스트 칩에는 부동소수점 유닛이 없어 캐시가 1KB밖에 없었습니다.테스트 칩은 공격적인 회로 설계 기법의 작동을 확인하기 위해 사용되었습니다.테스트 칩은 시뮬레이터 및 에뮬레이터와 함께 회사가 지원하는 펌웨어 및 다양한 운영 체제 부팅에도 사용되었습니다.

코드네임 EV4라고 불리는 이 생산 칩은 Digital의 0.75 μm CMOS-4 공정을 사용하여 제작되었습니다.더크 마이어와 에드워드 맥렐란은 마이크로 아키텍트였다.Ed는 문제 로직을 설계하고 Dirk는 다른 주요 블록을 설계했습니다.Jim Montanaro는 서킷 구현을 주도했습니다.EV3는 EV4 [1]부품이 출시되기 전에 디지털이 알파 플랫폼용 소프트웨어를 개발하기 위해 사용한 멀티프로세서 시스템인 Alpha 데모 유닛(ADU)에 사용되었습니다.

21064는 1992년 2월 중순 제39회 국제고체회로회의(ISSCC)에서 공개되었다.1992년 2월 25일 발표되었으며, 같은 날 150MHz 샘플이 도입되었다.가격은 100개 수량 3,375달러, 100개에서 1,000개 수량 1,650달러, 1,000개 이상 수량 1,560달러였다.대량 출하는 1992년 9월에 시작되었다.

1993년 2월 초, 150MHz 버전의 가격은 1,000개 이상의 수량으로 1,559달러에서 1,096달러로 인하되었다.

1993년 2월 25일, 200 MHz가 출시되었고 샘플 키트를 이용할 수 있으며 가격은 $3,495입니다.수량으로는 개당 1,231달러(약 1만 대 이상)로 책정됐다.대량 주문은 1993년 6월에 접수되었고, 선적도 1993년 8월에 접수되었다.이에 대응하여 150MHz 버전의 가격이 인하되었습니다.샘플 키트는 1993년 4월 발효된 3,375달러에서 1,690달러로 인하되었고, 물량으로는 1993년 7월부터 10,000달러 이상의 수량으로 개당 1,355달러에서 853달러로 인하되었다.

1993년 9월 10일 Alpha 21066과 Alpha 21068의 출시와 함께, 디지털은 기존의 21064의 위치를 조정하고 5,000개의 수량으로 유닛당 499달러의 166 MHz 버전을 출시했다.150MHz 버전은 5,000개의 수량으로 개당 455달러로 가격이 인하되었다.

1994년 6월 6일, 200 MHz 버전의 가격은 $544로 31% 인하되어 60 MHz Pentium에 비해 포지셔닝 되었습니다.또, 166 MHz 버전은 유닛당 $404로 19% 인하되어 1994년 7월 3일부터 유효하게 되었습니다.

Alpha 21064는 디지털의 매사추세츠 허드슨 시설과 스코틀랜드 사우스 퀸즈페리에서 제작되었습니다.

사용자

21064는 주로 워크스테이션이나 서버와 같은 하이엔드 컴퓨터에 사용되었습니다.포함된 사용자:

- Alpine 워크스테이션의 Aspen 시스템

- 헤라클레스 150, 헤라클레스 200 및 판테라 II 워크스테이션의 Carrera Computers

- Cray T3D 슈퍼컴퓨터에 150MHz 21064를 사용한 Cray Research

- 디지털, DECpc AXP 150 엔트리 레벨 워크스테이션, DEC 2000 AXP 엔트리 레벨 서버, DEC 3000 AXP 워크스테이션 및 엔트리 레벨 서버, DEC 4000 AXP 미드레인지 서버 및 DEC 7000/10000 AXP 하이엔드 서버

- Encor Computer, Infinity R/T 하이엔드 실시간 컴퓨터 내

성능

21064는 도입 당시부터 1993년 IBM(International Business Machines)이 멀티칩 POWER2를 도입할 때까지 최고의 성능을 발휘한 마이크로프로세서입니다.이후 최고 성능의 싱글 칩 마이크로프로세서가 되었으며,[2] 1993년 10월 275 MHz 21064A가 출시될 때까지 그 위치를 유지했습니다.

묘사

Alpha 21064는 명령을 순서대로 실행하는 슈퍼파이프라인 듀얼 이슈 슈퍼스칼라 마이크로프로세서입니다.클럭 사이클마다 최대 2개의 명령어를 4개의 기능 유닛(정수 유닛, 부동소수점 유닛(FPU), 주소 유닛, 브랜치 유닛)에 발행할 수 있습니다.정수 파이프라인의 길이는 7단계이고 부동소수점 파이프라인의 길이는 10단계입니다.두 파이프라인의 처음 4단계는 동일하며 I-Box에 의해 구현됩니다.

아이박스

I-box는 제어 장치이며, 명령을 가져오고 디코딩하며,[3] 명령을 발행하고 파이프라인을 제어합니다.1단계에서는 두 가지 명령이 I-캐시에서 가져옵니다.분기 예측은 2단계 동안 I박스 내의 논리에 의해 실행된다.정적 예측 또는 동적 예측 중 하나가 사용됩니다.정적 예측은 분기 명령의 변위 필드의 부호 비트를 검사하고, 해당 부호 비트가 역방향 분기(부호 비트에 1이 포함된 경우)를 나타내는 경우 취해진 것으로 분기를 예측했습니다.다이내믹 예측에서는 2,048 엔트리의 엔트리를 1비트의 브랜치 이력 테이블로 조사했습니다.엔트리에 1이 포함되어 있는 경우 브랜치는 [4]취득된 것으로 예측됩니다.동적 예측을 사용할 경우 대부분의 [5]프로그램에서 분기 예측이 약 80% 정확합니다.브랜치 오심의 패널티는 4 사이클입니다.[6]

이러한 명령은 3단계에서 디코딩됩니다.그런 다음 I-box는 4단계에서 두 가지 지침에 필요한 리소스를 사용할 수 있는지 확인합니다.페어링이 가능한 경우 지침이 발행됩니다.페어링할 수 있는 명령어는 정수 레지스터 [7]파일의 읽기 및 쓰기 포트 수에 따라 결정됩니다.21064에서는 부동소수점 연산, 임의의 연산 명령에 의한 로드/스토어 명령, 정수 브랜치로 연산, 부동소수점 분기로 연산 등의 문제가 발생할 수 있습니다.정수 연산과 부동 소수점 저장, 부동 소수점 연산과 정수 저장의 두 가지 조합은 허용되지 않습니다.두 가지 명령 중 하나를 함께 발행할 수 없는 경우 나머지 명령이 발행될 때까지 처음 4단계는 정지됩니다.자원 사용 불가능, 의존관계 또는 유사한 조건으로 인해 명령을 발행할 수 없는 경우에도 처음 4단계는 정지됩니다.

I박스에는 가상 주소를 물리 주소로 변환하기 위한2개의 Translation Lookaside Buffer(TLB; 변환 룩사이드버퍼)가 포함되어 있습니다.이러한 TLB는 Instruction Translation Buffer(ITB; 명령 변환 버퍼)라고 불립니다.ITB 캐시는 최근에 명령 스트림에 페이지 테이블 엔트리를 사용했습니다.8 KB 페이지에는 8 엔트리의 ITB가, 4 MB 페이지에는 4 엔트리의 ITB가 사용됩니다.양쪽 ITB는 완전히 관련지어져 있으며 마지막으로 사용되지 않은 교환 [8]알고리즘을 사용합니다.

실행

모든 명령에 대한 실행은 5단계 중에 시작됩니다.레지스터 파일은 4단계에서 읽힌다.5단계부터 시작되는 파이프라인은 정지할 수 없습니다.

정수 단위

정수 단위는 정수 명령 실행을 담당합니다.이것은 정수 레지스터 파일(IRF)과 E-box로 구성됩니다.IRF에는 32개의 64비트 레지스터가 있으며 4개의 읽기 포트와 2개의 쓰기 포트가 있으며 정수 유닛과 브랜치 [9]유닛 간에 균등하게 분할되어 있습니다.E박스에는 가산기, 로직 유닛, 배럴 시프터 및 멀티플라이어가 포함되어 있습니다.곱셈, 시프트 및 바이트 조작 명령을 제외하고 대부분의 정수 명령은 5단계가 끝날 때까지 완료되므로 1사이클의 지연 시간이 있습니다.배럴 시프터는 파이프라인으로 되어 있지만, 6단계가 끝날 때까지 시프트 및 바이트 조작 명령이 완료되지 않기 때문에 2사이클의 지연이 발생합니다.멀티플라이어는 다이 면적을 절약하기 위해 파이프라인되지 않았습니다.따라서 멀티플 명령어는 오퍼랜드에 [5]따라 19 ~23 사이클의 가변 지연을 가집니다.7단계에서는 정수 명령어가 그 결과를 IRF에 쓴다.

주소 단위

"A-box"라고도 하는 주소 장치는 로드 및 저장 명령을 실행했습니다.주소 유닛과 정수 유닛이 병렬로 동작할 수 있도록 주소 유닛에는 정수 유닛에 [10]가산기를 사용하는 대신 가상 주소 계산에 사용하는 자체 변위 가산기가 있습니다.32 엔트리의 완전 관련 변환 Lookaside Buffer(TLB)를 사용하여 가상 주소를 물리 [10]주소로 변환합니다.이 TLB는 Data Translation Buffer(DTB; 데이터 변환 버퍼)라고 불립니다.21064는 43비트의 가상 주소와 34비트의 물리 주소를 실장하고 있기 때문에, 8TB의 가상 메모리와 16GB의 물리 메모리에 대응할 수 있습니다.

스토어 명령어는 4엔트리에 32바이트 쓰기 버퍼에 의해 데이터가 버퍼링됩니다.쓰기 버퍼는 인접 저장소의 데이터를 Marge하여 시스템 버스의 쓰기 횟수를 줄이고 일시적으로 저장 시간을 늦춤으로써 성능을 향상시켰으며 시스템 버스를 [10]자주 사용하지 않기 때문에 부하를 신속하게 처리할 수 있었습니다.

부동 소수점 단위

부동소수점 유닛은 부동소수점 레지스터 파일(FRF)과 [7]F박스로 구성됩니다.FRF에는 32개의 64비트 레지스터가 있으며 3개의 읽기 포트와 2개의 쓰기 포트가 있습니다.F박스에는 부동소수점 파이프라인과 사이클당 1비트를 폐기하는 비파이프라인 분할 유닛이 포함되어 있습니다.

4단계에서는 부동소수점 레지스터 파일이 읽혀지고 데이터가 분수, 지수 및 서명 형식으로 포맷됩니다.덧셈 명령을 실행하는 경우, 가산기는 지수차를 계산하고, 그 결과를 정규화하기 위한 입력 오퍼랜드를 이용한 예측 선행 1 또는 제로 검출기를 개시한다.곱셈 명령을 실행할 경우 3X 곱셈이 생성됩니다.

5단계 및 6단계에서는 덧셈 및 뺄셈에 대해 얼라인먼트 또는 정규화 시프트와 스틱 비트 계산을 실시한다.곱셈 명령은 기수 8 Booth [5][11]알고리즘을 사용하는 파이프라인의 양방향 인터리브 배열에 곱셈됩니다.스테이지 8에서는 반올림과 병행하여 최종 덧셈을 실시한다.부동소수점 명령은 [11]10단계에서 결과를 FRF에 씁니다.

파이프라인에서 실행되는 명령에는 6사이클의 [11]지연 시간이 있습니다.비파이프라인 분할 단위로 실행되는 단정도(32비트) 분할과 배정도(64비트) 분할은 각각 [12]31사이클과 61사이클의 지연을 가진다.

캐시

21064에는 쓰기 정책을 사용하는 8KB 데이터 캐시(D-캐시)와 8KB 명령 캐시(I-캐시)의 2개의 온다이 프라이머리 캐시가 있습니다.양쪽 캐시는 단일 사이클액세스용으로 직접 매핑되어 32바이트의 회선 사이즈를 가집니다.캐시는 면적이 98μm인2 6 트랜지스터 스태틱랜덤 액세스 메모리(SRAM) 셀로 구성됩니다.캐시의 폭은 1,024셀, 높이는 66셀입니다.상단의 2행은 용장성에 사용됩니다.

128KB~16MB 용량의 옵션의 외부 세컨더리 캐시(B-캐시)가 지원되었습니다.캐시는 내부 클럭 주파수의 1/3~16분의 1 또는 200MHz에서 [13]12.5~66.67MHz로 동작했습니다.B 캐시는 직접 매핑되며 기본적으로는 128바이트의 회선 크기를 가지며 더 많은 양을 사용하도록 설정할 수 있습니다.시스템 버스를 통해 B-캐시에 액세스합니다.

외부 인터페이스

외부 인터페이스는 128비트 데이터 버스이며 내부 클럭환율의 1/2 ~8 또는 200MHz에서는 25 ~100MHz로 동작합니다.버스의 폭은 설정 가능하며, 21064를 사용하는 시스템은 64비트 외부 인터페이스를 가질 수 있습니다.외부 인터페이스도 34비트주소 버스로 구성되어 있습니다.

제조

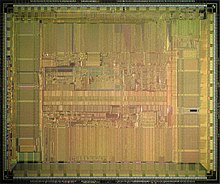

21064는 168만 개의 [14]트랜지스터를 포함하고 있었다.원래 EV4는 Digital이 CMOS-4 프로세스에서 제작했으며, CMOS-4 프로세스는 0.75μm의 피처 사이즈와 3가지 수준의 알루미늄 인터커넥트를 [14]갖추고 있습니다.EV4는 면적 233.52mm에2 대해 13.9mm x 16.8mm입니다.이후의 EV4S는 CMOS-4S로 제조되었습니다.CMOS-4는 기능 사이즈가 0.675μm인 CMOS-4의 10 % 광수축입니다.이 버전은 면적 186mm에2 대해 12.4mm [15]x 15.0mm로 측정되었습니다.

21064에서는 3.3V 전원장치를 사용했습니다.[14]EV4는 200MHz에서 최대 30W의 방산되었습니다.EV4S는 150MHz에서 최대 21.0W, 166MHz에서 22.5W, 200MHz에서 [16]27.0W의 방산됩니다.

패키지

21064는 61.72mm [17]x 61.72mm 크기의 431핀 알루미나-세라믹 핀 그리드 어레이(PGA)로 패키지되어 있습니다.431핀 중 291핀은 신호용이었고 140핀은 전원 및 [14][18]접지용이었다.히트 싱크는 패키지에 직접 부착되며 텅스텐 히트 스프레더에서 돌출된 2개의 스터드에 부착된 너트로 고정됩니다.

파생상품

알파 21064a

DEC칩 21064A(코드명 EV45)로 소개된 알파 21064A는 1993년 10월에 소개된 알파 21064를 더욱 발전시킨 모델입니다.200, 225, 233, 275 및 300MHz의 클럭 주파수로 작동했습니다.225MHz 모델은 1994년 7월 6일 233MHz 모델로 대체되었으며, 도입 당시 가격은 225MHz 모델보다 10% 낮은 5,000달러로 책정되었다.같은 날 275MHz 가격도 25% 인하된 1,083달러(약 5,000만원)로 책정됐다.300MHz 모델은 1995년 10월 2일에 발표 및 샘플링을 거쳐 1995년 12월에 출하되었습니다.또한 21064A-275-PC라는 한 가지 모델도 있었는데, 이는 Windows NT 또는 Windows NT 메모리 관리 모델을 사용하는 운영 체제만 실행하도록 제한되었습니다.

21064A는 최초의 21064를 계승하여 하이엔드 알파 마이크로프로세서가 되었습니다.그 후 하이엔드 시스템에서 가장 많이 사용되었습니다.포함된 사용자:

- DEC 3000 AXP, DEC 4000 AXP 및 DEC 7000/10000 AXP 시스템의 일부 모델에서 디지털 지원

- Alpine 워크스테이션의 Aspen Systems

- BTG, Action AXP275 RISC PC에서 275MHz 모델을 사용

- Cobra AXP 275 워크스테이션의 Carrera 컴퓨터

- 마하 2-289-T 워크스테이션에서 5%~289MHz 오버클럭된 275MHz 모델을 사용한 NekoTech

- 스토리지 시스템에서 275MHz 모델을 사용한 네트워크 어플라이언스(현 NetApp)

21064A는 21064보다 마이크로아키텍처가 많이 개선되었습니다.프라이머리 캐시는 I-캐시 및 D-캐시의 용량이 8KB에서 16KB로 2배 향상되고 캐시 태그 및 캐시 데이터 어레이에 패리티 보호가 추가되었습니다.부동소수점 분할은 사이클당 평균 2비트를 리트라이닝하는 향상된 디바이다로 인해 지연 시간이 단축됩니다.분기 예측은 2비트 BHT에 의해 4,096엔트리가 커졌습니다.

21064A는 280만 개의 트랜지스터를 포함하고 있으며 크기는 14.5 x 10.5 mm이며 면적은 152.252 mm입니다.Digital이 5세대 CMOS 프로세스인 CMOS-5에서 제작했으며, 이 프로세스는 4단계 알루미늄 [19]인터커넥트로 0.5μm 공정입니다.

알파 21066

DEC칩 21066(코드명 LCA4)으로 소개된 Alpha 21066은 Alpha 21064의 저비용 변형입니다.샘플은 1993년 9월 10일에 도입되어 1994년 초에 대량 출하되었다.도입 당시 166MHz Alpha 21066의 가격은 5,000개 수량으로 385달러였다.임베디드 시스템용으로 설계된 100MHz 모델도 존재했습니다.샘플링은 1994년 말에 시작되었으며 1995년 3분기에 대량 출하되었다.Microprocessor Report에서는 Alpha 21066이 내장 PCI 컨트롤러를 탑재한 최초의 마이크로프로세서로 인식되었습니다.

Alpha 21066은 저비용 애플리케이션, 특히 Windows NT를 실행하는 퍼스널 컴퓨터용으로 설계되었습니다.디지털은 멀티아 클라이언트, AXPci 33 OEM(Original Equipment Manufacturer) 메인보드 및 AXPvme 싱글보드 컴퓨터에서 Alpha 21066의 다양한 모델을 사용했습니다.Digital 이외에서는 Alphine 워크스테이션에 Aspen Systems, Pantera I 워크스테이션에 Carrera Computers, 마하 1~166 PC에 166 MHz 모델을, TransAlpha TA9000 시리즈 슈퍼컴퓨터에 Parsys를 사용했습니다.

프로세스 축소로 인해 비용에 민감한 임베디드 시스템에 적합한 기능을 포함할 수 있었습니다.이러한 기능에는 ECC를 지원하는 온다이 B-캐시 및 메모리 컨트롤러, 최대 8MB의 VRAM을 지원하는 기능 제한 그래픽 액셀러레이터, PCI 컨트롤러 및 33MHz 외부 클럭 신호를 원하는 내부 클럭 주파수에 곱하는 PLL(Phase Locked Loop) 클럭 제너레이터 등이 있습니다.

메모리 컨트롤러는 64KB~2MB의 B-캐시와 2~512MB의 메모리를 지원했습니다.ECC 실장은 1비트, 2비트 및 4비트 오류를 검출하고 1비트 오류를 수정할 수 있었습니다.비용 절감을 위해 Alpha 21066에는 64비트 시스템버스가 탑재되어 있어 핀의 수와 패키지의 사이즈를 줄였습니다.시스템 버스의 폭도 감소하여 대역폭이 20% 감소하였고, 이는 허용 가능한 것으로 간주되었습니다.

21066은 175만 개의 트랜지스터를 포함하고 있으며 면적 209.1mm에2 대해 17.0x12.3mm로 측정되었다.3레벨의 상호접속을 가진 0.675μm 프로세스인 CMOS-4S로 제작되었습니다.21066은 27.404 x 57.404 mm 크기의 287 핀 CPGA로 포장되었습니다.

알파 21066a

코드명 LCA45인 Alpha 21066A는 Alpha 21064A의 저비용 모델입니다.1994년 11월 14일 발표되었으며, 같은 날 100 및 233 MHz 모델의 샘플이 소개되었다.두 모델 모두 1995년 3월에 출하되었습니다.발표 당시 100MHz와 233MHz 모델의 가격은 각각 $175와 $360으로 5,000이었다.266MHz 모델이 나중에 출시되었습니다.

21066A는 미쓰비시 전기에 의해 M36066A로 두 번째로 공급되었다.이 회사는 알파 마이크로프로세서를 최초로 제작했다.100 및 233 MHz 부품은 1994년 11월에 발표되었습니다.발표 당시 엔지니어링 샘플은 1994년 12월, 상용 샘플은 1995년 7월, 대량 수량은 1995년 9월로 설정됐다.233MHz 부품의 가격은 1,000개 [20]수량으로 490달러였습니다.

21064A를 기반으로 했지만 21066A에는 16KB 명령 및 데이터 캐시가 없습니다.21066A의 특징은 전원 관리입니다.마이크로프로세서의 내부 클럭 주파수는 소프트웨어로 조정할 수 있습니다.

디지털은 이전에 21066을 사용하던 제품에 21066A의 다양한 모델을 사용했습니다.디지털 이외에도 태드폴 테크놀로지는 알파북 1 노트북에 233MHz 모델을 사용했습니다.

21066A는 면적 161.32mm의 142.8x10.9mm 크기의 다이 위에 180만개의 트랜지스터를 포함했습니다.이것은 Digital의 5세대 CMOS 프로세스인 CMOS-5로 제작되었습니다.CMOS-5는 0.5μm의 프로세스로, 3레벨의 상호접속을 갖추고 있습니다.M36066A는 미쓰비시전기가 0.5μm의 3단 금속 공정으로 제작했다.

알파 21068

DEC칩 21068로 소개된 Alpha 21068은 임베디드 시스템용으로 배치된 21066의 버전입니다.21066과 동일하지만 클럭환율이 낮아 전력 소실과 비용을 절감할 수 있습니다.샘플은 1993년 9월 10일에 도입되어 1994년 초에 대량 출하되었다.66MHz에서 작동하며 최대 9W의 전력 소실을 보였습니다.도입 당시 21068의 가격은 5000개 단위로 221달러였다.1994년 6월 6일, Digital은 가격을 16% 인하한 186달러로 1994년 7월 3일부터 시행한다고 발표했습니다.

AXPci 33 메인보드 및 AXPvme 64 및 64LC 싱글보드 컴퓨터에서 Alpha 21068을 Digital에서 사용했습니다.

알파 21068a

DEC칩 21068A로 소개된 Alpha 21068A는 임베디드 시스템용 Alpha 21066A의 변형입니다.100MHz의 클럭 주파수로 동작했습니다.

칩셋

당초 21064와 21064A에는 표준 칩셋이 없었습니다.Digital의 컴퓨터는 커스텀 어플리케이션 고유의 집적회로(ASIC)를 사용하여 마이크로프로세서를 시스템에 접속했습니다.이에 따라 알파 기반 제품을 개발하려는 서드파티의 개발 비용이 높아지자 디지털은 OEM(Original Equip Manufacturer)을 위한 표준 칩셋인 DEC칩 21070(Apecs)을 개발했다.

21070에는 DEC칩 21071과 DEC칩 21072의 두 가지 모델이 있었다.21071은 워크스테이션용으로 설계되었으며, 21072는 하이엔드 워크스테이션 또는 로우엔드 유니프로세서 서버용으로 설계되었습니다.2개의 모델은 메모리 서브시스템의 기능이 다릅니다.21071은 64비트 메모리버스를 탑재하여 8MB~2GB의 패리티 보호 메모리를 지원하는 반면 21072는 128비트 메모리버스를 탑재하여 16MB~4GB의 ECC 보호 메모리를 지원합니다.

칩셋은 COMANCHE B-캐시 및 메모리 컨트롤러, DECIDE 데이터 슬라이스 및 EPIC PCI 컨트롤러의 3가지 칩 설계로 구성되어 있습니다.DECIDE 칩은 데이터 경로를 32비트 슬라이스로 구현했습니다.따라서 21071에는 2개의 칩이 있고 21072에는 4개의 칩이 있습니다.EPIC 칩에는 DECE 칩에 대한 32비트 경로가 있습니다.

21070은 1994년 [21]1월 10일에 도입되었으며 샘플이 제공되고 있다.대량 출하는 1994년 중반에 시작되었다.5,000개의 수량으로, 21071은 90달러, 21072는 120달러였다.

21070명의 사용자는 Pantera 워크스테이션용 Carrera Computers와 AlphaServers 일부 모델에 Digital을 포함시켰습니다.

메모들

- ^ Charles P. Thacker; David G. Conroy; Lawrence C. Stewart (1992). "The Alpha Demonstration Unit: A High-performance Multiprocessor for Software and Chip Development" (PDF). Digital Technical Journal. 4 (4).

- ^ 라이언 1994

- ^ 디지털 이그니션 코퍼레이션 1996, 페이지 2-3-2-4

- ^ 디지털 이그니션 코퍼레이션 1996, 2-5페이지

- ^ a b c 맥렐런 1993, 페이지 42

- ^ 도버펄 1992, 37페이지

- ^ a b 도버펄 1992, 36페이지

- ^ 디지털 이그니션 코퍼레이션 1996, 2-6페이지

- ^ 도버펄 1992, 35-36페이지

- ^ a b c 맥렐런 1993, 43페이지

- ^ a b c 도버펄 1992, 38페이지

- ^ 구내프 1994

- ^ 맥렐란 1993, 44페이지

- ^ a b c d 도버펄 1992, 페이지 35

- ^ Bandarkar 1995, 2-4페이지

- ^ 디지털 이그니션 코퍼레이션 1996, 8-3페이지

- ^ 디지털 이그니션 코퍼레이션 1996, 8-2페이지

- ^ Bandarkar 1995, 2페이지

- ^ Bandarkar 1995, 3페이지

- ^ 크라우스 1994

- ^ 디지털 이그니션 코퍼레이션 1994

레퍼런스

- Alpha 21064 및 21064A 마이크로프로세서 하드웨어 레퍼런스 매뉴얼, 1996년 6월주문번호: EC-Q92UC-TE. 디지털 이그니션 코퍼레이션.

- Apiki, Steve; Grehan, Rick (March 1995). "Fastest NT Workstations". Byte.

- Bhandarkar, Dileep. "Alpha Implementations", IEEE Computer Society Technical Committee on Computer Architecture Newsletter, December 1995.

- Computergram(1992년 2월 25일).「DEC는, Hewlett-Packard의 Precision Architecture RISC에 도전하는 Alpha에 관한 더 많은 정보를 공개합니다.」컴퓨터 비즈니스 리뷰

- Computergram(1992년 2월 26일)."DEC, 알파 RISC 설명, 쿠보타 계획 공개"컴퓨터 비즈니스 리뷰

- Computergram(1994년 6월 7일)."DEC, 알파 AXP 칩 가격 최대 31% 인하"컴퓨터 비즈니스 리뷰

- Computergram(1993년 9월 13일)."DEC는 퍼스널 컴퓨터, 컨트롤용 알파벳을 추가합니다."컴퓨터 비즈니스 리뷰

- Computergram(1994년 1월 11일).「마이크로프로세서 리포트의 연간 칩 어워드, Motorola 88110을 가장 가능성이 낮은 부품…」컴퓨터·비즈니스·리뷰.

- Computergram(1994년 11월 11일)."미쓰비시 전기는 드디어 첫 알파를 시식할 준비가 되었습니다."컴퓨터 비즈니스 리뷰

- Computergram(1994년 11월 25일)."미쓰비시의 첫 번째 알파는 DEC의 21066A와 동일한 기능을 제공합니다."컴퓨터 비즈니스 리뷰

- Digital Equipment Corporation (10 January 1994). "Digital Introduces PCI-Based System Logic Chipsets For Alpha AXP 21064 Microprocessors And Announces The Industry's First PCI To PCI Bridge Chip". Press release.

- Dobberpuhl, Daniel W., Witek, Richard T. et al. "A 200-MHz 64-bit Dual-issue CMOS Microprocessor", Digital Technical Journal, Volume 4, Number 4, Special Issue 1992, pp. 35–50.

- Gwennap, Linley (12 September 1994). "Digital Leads the Pack with 21164", Microprocessor Report, Volume 8, Number 12.

- 라인하르트 크라우스(1993년 9월 13일)."DEC, PCI 내장 드라이브 2종류의 Alpha 공개"전자 뉴스

- 크라우스, 라인하르트(1993년 10월 18일)."DEC readies 225/275MHz Alphas"전자 뉴스

- Krause, Reinhardt (21 November 1994). "Alpha partners roll 233MHz 21066A". Electronic News.

- McKinney, Dina L. et al. "Digital's DECchip 21066: The First Cost-focused Alpha AXP Chip". Digital Technical Journal, Volume 6, Number 1, Winter 1994, pp. 66–77.

- McLellan, Edward (June 1993). "The Alpha AXP Architecture and 21064 Processor". IEEE Micro. pp. 36–47.

- Ryan, Bob; Thompson, Tom (January 1994). "RISC Grows Up". Byte.

추가 정보

- "DEC, Alpha로 마이크로프로세서 사업 진출" (1992년 3월 4일)마이크로프로세서 보고서, 제6권, 제3호

- 「DEC의 알파 아키텍처 프리미어」(1992년 3월 4일).마이크로프로세서 보고서, 제6권, 제3호

- 「디지털 플랜의 브로드 알파 프로세서 패밀리」(1992년 11월 18일).마이크로프로세서 보고서, 제6권, 제3호

- 「디지털에 의해서, Alpha 용 PCI 칩 세트가 공개됩니다」(1993년 7월 12일).마이크로프로세서 보고서, 제7권, 제9호

- "알파, 디지털의 21066으로 로우엔드에 도달"(1993년 9월 13일).마이크로프로세서 보고서, 제7권, 제12호

- Bandarkar, 딜레프 P. (1995년)알파 아키텍처 및 구현디지털 프레스

- 폭스, 토마스 F.(1994)"디지털의 고성능 마이크로프로세서 설계"제31회 ACM-IEEE 설계 자동화 회의의 진행. 페이지 586-591.

- 그로노스키, Paul E. 등(1998년 5월)."하이 퍼포먼스 마이크로프로세서 설계"IEEE Journal of Solid-State Circuit 33(5): 676–686페이지.