레이스 트랙 메모리

Racetrack memory이 문서는 갱신할 필요가 있습니다.(2021년 12월) |

| 컴퓨터 메모리 및 데이터 스토리지 유형 |

|---|

| 휘발성 |

| 비휘발성 |

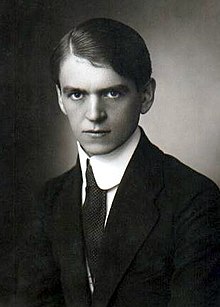

Racetrack 메모리 또는 도메인 월 메모리(DWM)는 물리학자 Stuart Parkin이 [1]이끄는 팀이 IBM의 Almaden Research Center에서 개발 중인 실험용 비휘발성 메모리 장치입니다.2008년 초에 3비트 버전이 성공적으로 [2]시연되었습니다.성공적으로 개발된다면, 레이스 트랙 메모리는 플래시 메모리와 [citation needed]같은 동급 솔리드 스테이트 메모리 장치보다 높은 스토리지 밀도를 제공할 것입니다.

묘사

레이스 트랙 메모리는 스핀-코히런트 전류를 사용하여 약 200nm의 지름과 100nm 두께의 나노경 과량 합금 와이어를 따라 자기 영역을 이동합니다.전류가 와이어를 통과하면 도메인은 와이어 근처에 위치한 자기 읽기/쓰기 헤드를 통과합니다.이것에 의해, 도메인은 비트 패턴을 기록하도록 변경됩니다.레이스 트랙 메모리 디바이스는 이러한 와이어와 읽기/쓰기 요소로 구성되어 있습니다.일반적인 운영 개념에서 레이스 트랙 메모리는 1960년대와 1970년대의 초기 버블 메모리와 유사합니다.1940년대와 1950년대의 수은 지연선과 같은 지연선 메모리는 UNIVAC 및 EDSAC 컴퓨터에 사용된 것과 같은 유사한 기술의 더 오래된 형태입니다.버블 메모리와 마찬가지로 레이스 트랙 메모리는 전류를 사용하여 일련의 자기 영역을 기판과 과거의 읽기/쓰기 요소를 통해 "푸시"합니다.스핀트로닉 자기저항 센서의 개발에 기초한 자기 검출 기능의 향상으로 훨씬 더 작은 자기 영역을 사용하여 훨씬 더 높은 비트 밀도를 제공할 수 있습니다.

생산 과정에서 와이어는 약 50 nm까지 축소될 것으로 예상되었습니다[citation needed].레이스 트랙 메모리에는 두 가지 배열이 고려되었습니다.가장 간단한 것은 일련의 플랫 와이어가 그리드에 배치되어 있고 근처에 읽기 및 쓰기 헤드가 배치되어 있는 것입니다.보다 광범위하게 연구된 배열에서는 기본 기판의 읽기/쓰기 헤드의 그리드 위에 수직으로 배치된 U자형 와이어를 사용했습니다.이렇게 하면 와이어가 읽기/쓰기 헤드에 도달하기 전에 와이어를 따라 개별 도메인을 더 멀리 이동해야 하지만 와이어가 2D 영역을 늘리지 않고도 훨씬 더 길어질 수 있습니다.두 배치 모두 거의 동일한 스루풋 성능을 제공했습니다.시공 측면에서 가장 큰 관심사는 3차원 수직 배치가 대량 생산될 수 있는지 여부였다.

다른 메모리 디바이스와의 비교

2008년의 예측에서는, 레이스 트랙 메모리는 랜덤 비트를 읽거나 쓸 수 있는 약 20 ~32 ns 의 퍼포먼스를 제공합니다.이는 하드 드라이브의 경우 약 10,000,000ns, 기존 DRAM의 경우 20-30ns와 비교됩니다.주요 저자들은 "저류량"을 약 9.5ns로 사용하여 접속 시간을 개선하는 방법을 논의했다.총 스루풋은 저장소의 유무에 관계없이 약 250~670 Mbit/s입니다.단일 DDR3 DRAM의 경우 12800 Mbit/s, 고성능 하드 드라이브의 경우 1000~4000 Mbit/s, 플래시 메모리 디바이스의 경우 1000~4000 Mbit/s입니다.현재 레이스 트랙 메모리에 비해 확실한 지연 시간을 제공하는 유일한 기술은 SRAM으로, 약 0.2ns이지만 비용이 더 높습니다.약 45nm(2011년 기준)의 더 큰 특징 크기 "F"와 약 140F의2 [3][4]셀 영역.

Racetrack 메모리는 DRAM이나 플래시 등의 기존 메모리를 대체하는 것을 목표로 하는 새로운 테크놀로지 중 하나로 다양한 역할에 적용할 수 있는 범용 메모리 디바이스를 제공할 가능성이 있습니다.다른 후보로는 자기저항 랜덤 액세스 메모리(MRAM), 위상변화 메모리(PCRAM) 및 강유전체 RAM(FeRAM)이 있다.이러한 기술의 대부분은 플래시 메모리와 유사한 밀도를 제공하며, 대부분의 경우 플래시 메모리와 같은 쓰기 방지 제한이 없다는 것이 주된 장점입니다.Field-MRAM은 3ns의 높은 액세스 시간을 제공하지만 25~40F²의 큰 셀 사이즈가 필요합니다.SRAM 대체품으로 사용할 수 있지만 대용량 스토리지 디바이스로는 사용할 수 없습니다.이러한 장치 중 가장 높은 밀도는 PCRAM에 의해 제공되며, 약 5.8F²의 셀 크기는 플래시 메모리와 유사할 뿐만 아니라 약 50ns의 꽤 좋은 성능을 제공합니다.그럼에도 불구하고 이들 중 어느 것도 전체적인 측면, 특히 밀도로 볼 때 레이스 트랙 메모리에 필적할 수 없습니다.예를 들어, 50ns는 레이스 트랙 메모리 장치에서 약 5비트를 작동시킬 수 있으므로 유효 셀 크기는 20/5=4F²로 PCM의 성능 밀도 제품을 쉽게 초과합니다.한편 비트 밀도를 희생하지 않고 동일한 20F² 영역을 2.5비트 8F² 대체 메모리 셀(저항 RAM(RRAM)이나 스핀토크 전송 MRAM 등)에 장착할 수 있으며, 각각이 훨씬 더 빠르게(~10ns) 동작합니다.

대부분의 경우 메모리 장치는 주어진 위치에 1비트를 저장하기 때문에 일반적으로 1비트를 저장하는 셀인 "셀 크기"로 비교됩니다.셀 크기 자체는 F² 단위로 지정됩니다. 여기서 "F"는 피쳐 크기 설계 규칙이며, 일반적으로 금속 선 폭을 나타냅니다.플래시와 레이스 트랙은 모두 셀당 여러 비트를 저장하지만 비교는 가능합니다.예를 들어, 하드 드라이브는 이론적으로 약 650 nm²/[5]bit에 도달한 것으로 보이며, 이는 주로 자기 표면의 특정 영역에 대한 읽기 및 쓰기 능력에 의해 정의됩니다.D램은 셀 크기가 약 6F²이고 SRAM은 120F²로 밀도가 훨씬 낮습니다.NAND 플래시 메모리는 현재 널리 사용되는 비휘발성 메모리에서 가장 밀도가 높은 형태이며 셀 크기는 약 4.5F²이지만, 1.5F²의 유효 크기에 대해 셀당 3비트를 저장합니다. NOR 플래시 메모리는 4.75F²로 9.5F²의 [4]셀 크기에서 2비트 작동을 고려하므로 밀도가 약간 낮습니다.수직방향(U자형) 레이스 트랙에서는 셀당 거의 10~20비트가 저장되며, 셀 자체의 물리적 크기는 최소 약 20F²입니다.또한 "트랙"의 다른 위치에 있는 비트는 읽기/쓰기 센서를 통해 도메인을 ~100m/s의 고정 속도로 이동하기 때문에 읽기/쓰기 센서에 의해 액세스되는 데 서로 다른 시간(최대 10~1000ns 또는 10ns/bit)이 걸립니다.

개발 과제

초기 실험 장치의 한 가지 제한 사항은 자기 영역을 와이어를 통해 천천히 밀어낼 수 있다는 점이었고, 성공적으로 이동하려면 마이크로초 단위의 전류 펄스가 필요합니다.이는 예상외로 하드 드라이브와 거의 동일한 성능, 즉 예상보다 무려 1000배나 느린 성능으로 이어졌습니다.최근의 연구는 이 문제를 와이어의 결정 구조의 미세한 결함으로 추적하여 도메인이 이러한 결함에서 "고착"하게 만들었다.X선 현미경을 사용하여 도메인 사이의 경계를 직접 촬영함으로써, 그들의 연구는 이러한 결함이 없을 때 도메인 벽이 몇 나노초 정도의 짧은 펄스에 의해 움직인다는 것을 발견했다.이는 약 110m/[6]s의 거시적 성능에 해당한다.

레이스 트랙을 따라 도메인을 구동하는 데 필요한 전압은 와이어 길이에 비례합니다.전류 밀도는 도메인 벽을 누르는 데 충분히 높아야 합니다(전기 조영 등).레이스 트랙 테크놀로지의 어려움은 높은 전류 밀도(10A/cm² 이상8)가 필요하기 때문에 발생합니다.단면 30nm x 100nm는 3mA를 초과해야 합니다.결과적으로 소비전력은 스핀-전송 토크 메모리(STT-RAM)나 플래시 메모리 등 다른 메모리보다 높아집니다.

Racetrack 메모리와 관련된 또 다른 과제는 도메인 벽이 이동하는 확률적 특성, 즉 랜덤 위치에서 [7]이동 및 정지하는 것입니다.나노와이어 [8]가장자리에 노치를 만들어 이 과제를 극복하려는 시도가 있었다.연구자들은 또한 도메인 벽을 정확하게 [9]고정하기 위해 서로 다른 나노와이어를 사용할 것을 제안했다.실험적인 조사 결과 도메인[10] 월 [11]메모리의 효과가 나타났다.최근 연구자들은 성분 수정을 통해 자기 성질을 국소적으로 변조하는 것과 같은 비기하학적 접근법을 제안했다.아닐 유도[12] 확산 및 이온 주입[13] 등의 기술을 사용한다.

「 」를 참조해 주세요.

- 거대 자기저항(GMR) 효과

- 자기저항랜덤액세스메모리(MRAM)

- 스핀트로닉스

- 스핀 트랜지스터

레퍼런스

- ^ Spintronics 디바이스 연구, 자기 레이스 트랙 메모리 프로젝트

- ^ Masamitsu Hayashi et al. (April 2008). "Current-Controlled Magnetic Domain-Wall Nanowire Shift Register". Science. 320 (5873): 209–211. Bibcode:2008Sci...320..209H. doi:10.1126/science.1154587. PMID 18403706.

{{cite journal}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ "ITRS 2011". Retrieved 8 November 2012.

- ^ a b Parkin; et al. (11 April 2008). "Magnetic Domain-Wall Racetrack Memory". Science. 320 (5873): 190–4. Bibcode:2008Sci...320..190P. doi:10.1126/science.1145799. PMID 18403702.

- ^ 1 Tbit/in²는 약 650nm²/비트입니다.

- ^ Swarup, Amarendra (11 May 2007). "'Racetrack' memory could gallop past the hard disk". New Scientist.

- ^ Kumar, D.; Jin, T.; Risi, S. Al; Sbiaa, R.; Lew, W. S.; Piramanayagam, S. N. (March 2019). "Domain Wall Motion Control for Racetrack Memory Applications". IEEE Transactions on Magnetics. 55 (3): 2876622. Bibcode:2019ITM....5576622K. doi:10.1109/TMAG.2018.2876622. ISSN 0018-9464.

- ^ Hayashi, M.; Thomas, L.; Moriya, R.; Rettner, C.; Parkin, S. S. P. (2008). "Current-Controlled Magnetic Domain-Wall Nanowire Shift Register". Science. 320 (5873): 209–211. doi:10.1126/science.1154587. ISSN 0036-8075.

- ^ Mohammed, H. (2020). "Controlled spin-torque driven domain wall motion using staggered magnetic wires". Applied Physics Letters. 116 (3): 032402. arXiv:1908.09304. doi:10.1063/1.5135613.

- ^ Prem Piramanayagam (24 February 2019), Staggered Domain Wall Memory, archived from the original on 21 December 2021, retrieved 13 March 2019

- ^ Al Bahri, M.; Borie, B.; Jin, T.L.; Sbiaa, R.; Kläui, M.; Piramanayagam, S.N. (8 February 2019). "Staggered Magnetic Nanowire Devices for Effective Domain-Wall Pinning in Racetrack Memory". Physical Review Applied. 11 (2): 024023. Bibcode:2019PhRvP..11b4023A. doi:10.1103/PhysRevApplied.11.024023.

- ^ Jin, T. L.; Ranjbar, M.; He, S. K.; Law, W. C.; Zhou, T. J.; Lew, W. S.; Liu, X. X.; Piramanayagam, S. N. (2017). "Tuning magnetic properties for domain wall pinning via localized metal diffusion". Scientific Reports. 7 (1): 16208. Bibcode:2017NatSR...716208J. doi:10.1038/s41598-017-16335-z. PMC 5701220. PMID 29176632.

- ^ Jin, Tianli; Kumar, Durgesh; Gan, Weiliang; Ranjbar, Mojtaba; Luo, Feilong; Sbiaa, Rachid; Liu, Xiaoxi; Lew, Wen Siang; Piramanayagam, S. N. (2018). "Nanoscale Compositional Modification in Co/Pd Multilayers for Controllable Domain Wall Pinning in Racetrack Memory". Physica Status Solidi RRL. 12 (10): 1800197. Bibcode:2018PSSRR..1200197J. doi:10.1002/pssr.201800197.

외부 링크

- 메모리 아키텍처의 재정의

- IBM, 새로운 메모리 등급으로 이동(YouTube 동영상)

- IBM Racetrack 메모리 프로젝트