콘텐츠 주소 지정 가능 메모리

Content-addressable memoryContent-Addressable Memory(CAM; 콘텐츠 주소 지정 가능 메모리)는 특정 초고속 검색 애플리케이션에서 사용되는 특수한 유형의 컴퓨터 메모리입니다.또한 연상 메모리 또는 연상 스토리지라고도 하며 입력 검색 데이터를 저장된 데이터 테이블과 비교하고 일치하는 [1]데이터의 주소를 반환합니다.

CAM은 정보 기반 및 라우팅 테이블의 전송 속도를 높이는 네트워킹디바이스에서 자주 사용됩니다.이러한 종류의 연상 메모리는 캐시 메모리에도 사용됩니다.어소시에이션 캐시 메모리에는, 주소와 컨텐츠의 양쪽 모두가 나란히 격납되어 있다.주소가 일치하면, 대응하는 컨텐츠가 캐시 메모리에서 취득됩니다.

하드웨어 관련 어레이

사용자가 메모리 주소를 제공하고 RAM이 해당 주소에 저장된 데이터 워드를 반환하는 표준 컴퓨터 메모리, 랜덤 액세스 메모리(RAM)와는 달리 CAM은 사용자가 데이터 워드를 공급하고 CAM이 메모리 전체를 검색하여 데이터 워드가 저장되어 있는지 여부를 확인합니다.데이터 워드가 검출되면 CAM은 워드가 검출된1개 또는 복수의 스토리지 주소의 리스트를 반환합니다.따라서 CAM은 소프트웨어 용어로는 어소시에이션 어레이라고 불리는 것을 하드웨어로 구현한 것입니다.

유사한 개념은 1955년 Dudley Allen Buck이 제안한 데이터 단어 인식 단위에서 찾을 수 있다.[2]

표준

CAM 및 기타 네트워크 검색 엔진의 메이저인터페이스 정의는 Network Processing [3]Forum이 개발한 Look-Aside Interface(LA-1 및 LA-1B)라고 불리는 상호운용성 계약으로 지정되어 있습니다.Integrated Device Technology, Cypress Semiconductor, IBM, Broadcom 등에 의해 상호운용성 계약에 부합하는 수많은 장치가 생산되었습니다.2007년 12월 11일 OIF는 시리얼 룩사이드(SLA) 인터페이스 [citation needed]계약을 발표했습니다.

반도체 구현

데이터 검색 어플리케이션에서는 CAM이 RAM보다 훨씬 빠릅니다.단, CAM에는 비용상의 단점이 있습니다.단순한 기억 셀을 가진 RAM 칩과 달리 완전 병렬 CAM 내의 각 메모리 비트는 저장된 비트와 입력 비트 간의 일치를 검출하기 위해 관련된 자체 비교 회로를 가져야 합니다.또한 데이터 워드의 각 셀로부터의 일치 출력을 조합하여 완전한 데이터 워드 일치 신호를 생성해야 합니다.추가 회로에 의해 CAM 칩의 물리 사이즈와 제조 코스트가 증가합니다.또한 모든 비교회로가 모든 클럭사이클에서 활성화되므로 추가 회로는 전력 소모를 증가시킵니다.따라서 CAM은 비용이 적게 드는 방법으로 검색 속도를 달성할 수 없는 특수한 어플리케이션에서만 사용됩니다.성공적인 초기 구현 중 하나는 범용 관련 프로세서 IC와 [4]시스템입니다.

2000년대 초 사이프레스, IDT, 넷로직, 시버코어,[5] MOSAID 등 여러 반도체 회사가 네트워킹 애플리케이션을 대상으로 한 CAM 제품을 선보였습니다.이러한 제품에는 Network Search Engine(NSE; 네트워크 검색 엔진), Network Search Accelerator(NSA; 네트워크 검색 액셀러레이터) 및 Knowledge-based Processor(KBP; 지식 기반 프로세서)라는 라벨이 붙어 있었습니다만, 기본적으로는 네트워크에 최적화된 전용 인터페이스와 기능을 갖춘 CAM이었습니다.현재 Broadcom은 여러 KBP [6]패밀리를 제공하고 있습니다.

대체 구현

속도, 메모리 크기 및 비용 간의 다른 균형을 달성하기 위해 일부 구현에서는 하드웨어에서 표준 트리 검색 또는 해시 설계를 사용하여 CAM 기능을 에뮬레이트하고 레플리케이션이나 파이프라인 등의 하드웨어 기술을 사용하여 효과적인 성능을 고속화합니다.이러한 설계는 [citation needed]라우터에서 자주 사용됩니다.Lulea 알고리즘은 인터넷라우팅 테이블에서 필요한 최장 프리픽스 일치 검색을 위한 효율적인 구현입니다.

삼진법 CAM

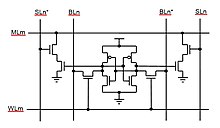

바이너리 CAM은 CAM의 가장 단순한 유형으로 1과 0으로 구성된 데이터 검색어를 사용합니다.Ternary CAM(TCAM)[7]은 X의 세 번째 일치 상태를 허용하거나 저장된 워드의 하나 이상의 비트를 신경쓰지 않으므로 검색에 유연성을 더합니다.예를 들어 3진 CAM에 저장된 10XX0은 4개의 검색어 "10000", "10010", "10100" 또는 "10110" 중 하나에 일치합니다.내부 메모리 셀은 바이너리 CAM의 2가지 상태가 아닌 3가지 상태를 부호화할 필요가 있기 때문에 검색 유연성은 바이너리 CAM에 대해 추가 비용이 발생합니다.이 추가 상태는 일반적으로 모든 메모리 셀에 마스크 비트("care" 또는 "Don't care" 비트)를 추가하여 구현됩니다.

응용 프로그램 예시

컨텐츠 주소 지정 가능 메모리는 컴퓨터 네트워킹 장치에서 자주 사용됩니다.예를 들어, 네트워크 스위치는 포트 중 하나로부터 데이터 프레임을 수신하면 프레임의 송신원 MAC 주소와 수신처 포트를 사용하여 내부 테이블을 업데이트합니다.다음으로, 테이블내의 행선지 MAC 주소를 검색해, 프레임을 전송 할 필요가 있는 포토를 특정해, 그 포토로 송신합니다.MAC 주소 테이블은 보통 바이너리 CAM과 함께 구현되기 때문에 수신처 포트를 매우 빠르게 찾을 수 있기 때문에 스위치의 지연이 줄어듭니다.

3차 CAM은 네트워크라우터에서 자주 사용됩니다.각 주소에는 서브넷 설정에 따라 크기가 다를 수 있는 네트워크프리픽스와 나머지 비트를 차지하는 호스트주소의 2부분이 있습니다.각 서브넷에는, 주소의 어느 비트가 네트워크 프리픽스인지, 어느 비트가 호스트 주소인지를 지정하는 네트워크 마스크가 있습니다.라우팅은 라우터에 의해 유지되는 라우팅 테이블을 참조함으로써 이루어집니다.라우터에는, 기존의 행선지 네트워크 프리픽스, 관련 붙여진 네트워크 마스크, 및 그 행선지에의 패킷 라우팅에 필요한 정보가 포함되어 있습니다.단순한 소프트웨어 실장에서는, 라우터는 라우팅 테이블의 각 엔트리와 라우팅 되는 패킷의 행선지 주소를 비교하고, 네트워크 마스크와 비트 단위로 AND 를 실행해, 네트워크 프리픽스와 비교합니다.동일할 경우 대응하는 라우팅 정보가 패킷 전송에 사용됩니다.라우팅 테이블에 3진 CAM을 사용하면 검색 프로세스가 매우 효율적입니다.주소는 Don't care for host part of the address를 사용하여 저장됩니다.따라서, 행선지 주소를 CAM 로 검색하면, 곧바로 올바른 라우팅 엔트리가 취득됩니다.마스크와 비교는 모두 CAM 하드웨어에 의해서 실행됩니다.이것은 (a) 엔트리가 네트워크 마스크 길이를 줄이는 순서로 저장되고 (b) 하드웨어가 최초로 일치하는 엔트리만을 반환하는 경우에 기능합니다.따라서 가장 긴 네트워크 마스크와의 일치(가장 긴 프리픽스 일치)가 사용됩니다.[8]

기타 CAM 어플리케이션에는 다음이 있습니다.

- 캐시 컨트롤러와 변환 룩사이드[9] 버퍼를 완전히 연관지을 수 있습니다.

- 데이터베이스 엔진

- 데이터 압축 하드웨어

- 인공신경망[10]

- 침입 방지 시스템

- 네트워크 프로세서

- Goodyear STARAN과 같은 몇 개의 커스텀 컴퓨터가 CAM을 구현하기 위해 구축되었습니다.

「 」를 참조해 주세요.

- 콘텐츠 주소 지정 가능 네트워크

- 콘텐츠 어드레싱 가능한 병렬 프로세서

- 컨텐츠 주소 지정이 가능한 스토리지 또는 파일 시스템

- 스퍼스 분산 메모리

- 태플 공간

레퍼런스

- ^ "K. Pagiamtzis* and A. Sheikholeslami, Content-addressable memory (CAM) circuits and architectures: A tutorial and survey, IEEE Journal of Solid-State Circuits, pp. 712-727, March 2006" (PDF). Archived (PDF) from the original on 2007-03-15.

- ^ TRW Computer Division Archived 2011년 8월 5일 Wayback Machine, 1963년 페이지 17.

- ^ Look-Aside (LA-1B) Interface Implementation Agreement (PDF), 2004-08-04

- ^ Stormon, C. D.; Troullinos, N. B.; Saleh, E. M.; Chavan, A. V.; Brule, M. R.; Oldfield, J. V. (December 1992). "C. Stormon, N. Troullinos, E. Saleh, A. Chavan, M. Brule and J. Oldfield, "A general-purpose CMOS associative processor IC and system", IEEE Micro, vol. 12, no. 6, pp. 68-78, December 1992". IEEE Micro. 12 (6): 68–78. doi:10.1109/40.180249. S2CID 206432751.

{{cite journal}}: CS1 maint :url-status (링크) - ^ "Sibercore Technologies - Silicon Solutions for Cyberspace". Archived from the original on 2003-04-19.

- ^ "16nm Heterogeneous Knowledge-Based Processors (KBPs)". Archived from the original on 2017-05-19.

- ^ Hucaby, David (2004). CCNP BCMSN Exam Certification Guide: CCNP Self-study. ISBN 9781587200779.

- ^ Varghese, George, 네트워크 알고리즘: 고속 네트워크 디바이스 설계를 위한 학제간 접근법, Morgan Kaufmann, 2005

- ^ Smith, Alan Jay (September 1982). "Cache Memories" (PDF). Computing Surveys. 14 (3): 473–530. doi:10.1145/356887.356892. S2CID 6023466. Retrieved April 3, 2022.

The TLB is a small associative memory which maps virtual to real addresses.

- ^ Hinton, Geoffrey E. (1984). "Distributed representations".

참고 문헌

- 아나르기로스 크리켈리스, 찰스 C윔즈(편집자)(1997년).Associative Processors and Processors, IEEE Computer Science Press.ISBN 0-8186-7661-2

- US 6823434, Hannum 등, "전원 투입 시 또는 머신 고유의 상태를 통해 완전히 연관된 어레이를 기존의 상태로 리셋 및 초기화하는 시스템 및 방법", 2004년 발행

- Pagiamtis, K.; Sheikholeslami, A. (2006). "Content-Addressable Memory (CAM) Circuits and Architectures: A Tutorial and Survey" (PDF). IEEE Journal of Solid-State Circuits. 41 (3): 712–727. Bibcode:2006IJSSC..41..712P. doi:10.1109/JSSC.2005.864128. S2CID 11178331.

- Stormon, C.D., N.B., Trowlinos, E.M., Saleh, Chavan, A.V., Brule, M.R., Oldfield, J.V. 범용 CMOS 어소시에이티브 프로세서 IC 및 시스템, NY 시러큐스.

- TRW 컴퓨터부(1963년)선상 무기관리시스템에서의 컴퓨터 및 컴퓨팅 기술의 최적 활용에 관한 첫 중간보고서(BuWeps-Project RM1004 M88-3U1)버지니아 주 알렉산드리아:국방문서 과학 기술 정보 센터.