타일64

TILE64| 일반 정보 | |

|---|---|

| 개시. | 2007 |

| 공통 제조원 | |

| 성능 | |

| 최대 CPU 클럭 속도 | 600MHz~900MHz |

| 아키텍처 및 분류 | |

| 테크놀로지 노드 | 45 nm ~ 90 nm |

| 물리 사양 | |

| 코어 |

|

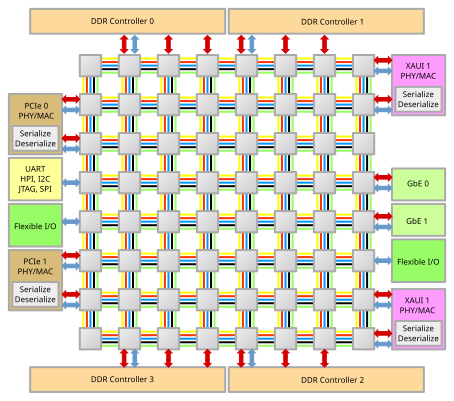

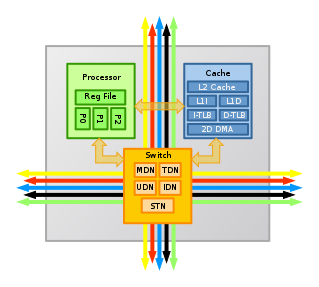

Tile64는[1] Tilera가 제조한 VLIW ISA 멀티코어 프로세서입니다.64개의 "타일"로 이루어진 메시 네트워크로 구성되어 있으며, 각 타일에는 범용 프로세서, 캐시 및 프로세서의 다른 타일과의 통신에 사용하는 논블로킹 라우터가 포함되어 있습니다.

짧은 파이프라인의 순서대로 3개의 코어가 MIPS에서 영감을[2] 받은 VLIW 명령 세트를 구현합니다.각 코어는 레지스터 파일과 2개의 정수 연산 로직 유닛과 로드 스토어 유닛의 3개의 기능 유닛을 가진다.각 코어("타일")에는 자체 L1 및 L2 캐시와 모든 L2 [3]캐시의 집약인 전체 가상 L3 캐시가 있습니다.코어는 자체 운영 체제를 완전히 실행할 수 있으며, 여러 코어를 사용하여 대칭적인 멀티 프로세싱 운영 체제를 실행할 수 있습니다.

TIL64에는 4개의 DDR2 컨트롤러, 2개의 10기가비트이더넷 인터페이스, 2개의 4레인 PCIe 인터페이스 및 "유연한" 입출력 인터페이스가 있어 다수의 프로토콜을 처리하도록 소프트웨어를 구성할 수 있습니다.프로세서는 90nm 프로세스를 사용하여 제조되며 600~900MHz의 속도로 동작합니다.

기술책임자(CTO)이자 공동창업자 아난트 아가월(Anant Agarwal)에 따르면 틸레라는 컴퓨팅 처리 수요가 [4]높은 네트워크 장비 및 디지털 비디오 시장을 공략할 예정이다.

TIL64 아키텍처에 대한 지원이 Linux 커널 버전 2[5].6.36에 추가되었지만 커널 [6]버전 4.16에서 중단되었습니다.Tilera의 비공식 LLVM 백엔드가 존재합니다.[7]

레퍼런스

- ^ Keckler, Stephen W.; Olukotun, Kunle; Peter Hofstee, H. (August 29, 2009). Multicore Processors and Systems - Google Books. ISBN 9781441902634.

- ^ "Compiler construction - What instruction set is used by Tilera microprocessors?".

- ^ Kingman, Henry (August 20, 2007). "Massively multicore processor runs Linux". linuxdevices.com. Archived from the original on September 6, 2012.

- ^ Boslet, Mark (August 20, 2007). "Start-up Tilera to Unveil 64-core chip". San Jose Mercury News. Archived from the original on November 12, 2007.

- ^ "Tilera architecture support". Kernel Newbies. October 20, 2010.

- ^ Simon Sharwood (April 3, 2018). "Linux 4.16 arrives, erases eight CPUs and keeps melting Meltdown". theregister.co.uk. Situation Publishing. Archived from the original on April 3, 2018. Retrieved April 3, 2018.

- ^ Tilera TIL64 백엔드 for LLVM 공개 // Phoronix, 2012년 9월 6일

외부 링크

- 틸레라 웹사이트

- 새로운 64코어 CPU로 멀티코어 바를 높이다

- 칩메이커는 아카이브에서 데이터 경로의 클로깅을 해제하는 것을 목표로 하고 있습니다(2013년 1월 19일 아카이브).