디지털 일렉트로닉스

Digital electronics디지털 전자제품은 디지털 신호의 연구와 디지털 신호를 사용하거나 생산하는 장치의 엔지니어링을 포함하는 전자제품 분야입니다.아날로그 전자제품이나 아날로그 신호와는 대조적입니다.

디지털 전자회로는 보통 논리 게이트의 큰 어셈블리로 만들어지며, 종종 집적회로로 패키지화됩니다.복잡한 디바이스는 부울 논리함수의 [1]간단한 전자표현을 가질 수 있다.

역사

이진수 체계는 고트프리트 빌헬름 라이프니츠(1705년 출판)에 의해 개선되었고, 그는 또한 이진수 체계를 사용함으로써 산술과 논리의 원리를 결합할 수 있다는 것을 확립했다.디지털 논리는 19세기 중반 조지 불의 뇌아입니다찰스 샌더스 피어스는 1886년 편지에서 논리 연산이 전기 스위칭 [2]회로에 의해 어떻게 수행될 수 있는지를 설명했습니다.결국 진공관은 논리 연산을 위한 릴레이를 대체했다.1907년 Lee De Forest가 플레밍 밸브를 개조하여 AND 게이트로 사용할 수 있었습니다.루드비히 비트겐슈타인은 논리철학제(1921)의 제안 5.11로서 16행 진리표의 버전을 도입했다.우연 회로를 발명한 발터 보테는 1924년 최초의 현대적인 전자 AND 게이트를 만든 공로로 1954년 노벨 물리학상을 공동 수상했다.

기계식 아날로그 컴퓨터는 1세기에 등장하기 시작했고 중세에는 천문학적 계산을 위해 사용되었다.제2차 세계 대전에서는 어뢰 조준 계산과 같은 특수 군사 용도로 기계식 아날로그 컴퓨터가 사용되었습니다.이 기간 동안 최초의 전자 디지털 컴퓨터가 개발되었고, 디지털이라는 용어는 1942년 조지 스티비츠에 의해 제안되었습니다.원래는 큰 방 크기였고, 최신 PC 수백 [3]대에 달하는 전력을 소비했습니다.

Z3는 Konrad Zuse가 설계한 전기 기계식 컴퓨터였다.1941년에 완성된 이 컴퓨터는 세계 최초로 프로그램 가능한 완전 자동 디지털 [4]컴퓨터였다.1904년 존 암브로즈 플레밍이 진공관을 발명하면서 이 장치의 작동이 촉진되었다.

디지털 계산이 아날로그를 대체함과 동시에 순수 전자 회로 소자가 곧 기계적 및 전기 기계적 요소를 대체했습니다.존 바딘과 월터 브래튼은 1947년 벨 연구소에서 포인트 접점 트랜지스터를 발명했고, 윌리엄 쇼클리는 1948년 [5][6]벨 연구소에서 양극 접합 트랜지스터를 발명했다.

맨체스터 대학에서는 톰 킬번의 지휘 하에 진공관 [7]대신 새로 개발된 트랜지스터를 사용하여 기계를 설계하고 만들었다.1953년 세계 최초의 트랜지스터형 컴퓨터(Transistrated Computer)가 가동됐고 1955년 4월 두 번째 버전이 완성됐다.1955년 이후 트랜지스터는 컴퓨터 디자인에서 진공관을 대체하여 "2세대" 컴퓨터를 탄생시켰다.진공 튜브에 비해 트랜지스터는 크기가 작고 신뢰성이 높으며 수명이 짧으며 진공 튜브보다 적은 전력을 필요로 했습니다. 따라서 상대적으로 좁은 공간에 최대 수만 개의 고밀도 회로를 방출할 수 있었습니다.

1958년 7월 텍사스 인스트루먼트에서 일하는 동안 잭 킬비는 집적회로(IC)에 대한 초기 아이디어를 기록했고,[8] 1958년 9월 12일 첫 번째 작동 집적회로를 성공적으로 시연했습니다.킬비의 칩은 게르마늄으로 만들어졌다.이듬해 Fairchild Semiconductor의 Robert Noyce가 실리콘 집적회로를 발명했다.노이스의 실리콘 IC의 기초는 1959년 초 장 호르니에 의해 개발된 평면 공정으로,[9] 그는 1957년 모하메드 아탈라의 실리콘 표면 패시베이션 방법을 기반으로 제작되었습니다.이 새로운 기술인 집적회로는 반도체 재료(일반적으로 실리콘)의 작은 플레이트("칩")에 전자 회로 세트를 장착함으로써 복잡한 회로를 빠르고 저렴한 비용으로 제작할 수 있었습니다.

MOS 트랜지스터로도 알려진 금속 산화물 반도체 전계효과 트랜지스터([10][11][12]MOSFET)는 1959년 벨 연구소에서 모하메드 아탈라와 다원 칸에 의해 발명되었다.MOSFET의 장점은 높은 확장성,[13] 저렴한 가격,[14] 낮은 전력 소비 및 높은 트랜지스터 [15]밀도를 포함합니다.또한 빠른 온-오프 전자 [16]전환 속도는 사인파와 유사한 아날로그 신호를 더 느리게 생성하는 BJT와 대조적으로 [17][18]전자 디지털 신호의 기반인 펄스 [16]트레인 생성에 이상적입니다.이러한 요인에 의해 MOS Large Scale Integration(LSI; 대규모 집적)과 함께 MOSFET는 디지털 [19]회선의 중요한 스위칭디바이스가 됩니다.MOSFET는 전자 [20][21]산업에 혁명을 일으켰고, 가장 일반적인 반도체 [11][22]장치이다.

집적회로 초기에는 각 칩이 몇 개의 트랜지스터에 한정되어 있었으며 집적도가 낮았기 때문에 설계 프로세스가 비교적 간단했습니다.제조업의 수율도 오늘날 기준으로 볼 때 상당히 낮았다.1970년대 초까지 MOSFET 트랜지스터가 널리 채택되면서 단일 [23]칩에 10,000개 이상의 트랜지스터가 탑재된 최초의 대규모 집적회로(LSI) 칩이 탄생했습니다.1980년대까지 MOSFET 로직의 일종인 CMOS가 널리 채택된 이후,[24] 기술이 발전함에 따라 수백만, 그리고 수십억 개의 MOSFET를 하나의 칩에 배치할 수 있게 되었고, 좋은 설계에는 철저한 계획이 요구되어 새로운 설계 방법이 생겨났다.소자의 트랜지스터 수와 총 생산량이 전례 없는 수준으로 증가했습니다.2018년까지 생산된 트랜지스터의 총량은 1.3×1022(13조3000억 [25]개)으로 추정되고 있다.

무선 혁명(무선 네트워크의 도입과 확산)은 1990년대에 시작되었으며 MOSFET 기반의 RF 파워 앰프(전력 MOSFET 및 LDMOS)와 RF 회로(RF CMOS)[26][27][28]의 광범위한 채택에 의해 실현되었습니다.무선 네트워크는 케이블 없이도 공공 디지털 전송을 가능하게 하여 1990-2000년대에 디지털 텔레비전, GPS, 위성 라디오, 무선 인터넷 및 휴대전화로 이어졌다.

특성.

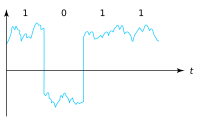

아날로그 회로에 비해 디지털 회로의 장점은 디지털로 표현되는 신호를 [29]노이즈에 의한 열화 없이 전송할 수 있다는 것입니다.예를 들어, 전송 중에 픽업된 노이즈가 1과 0의 식별을 방해하기에 충분하지 않다면 1과 0의 시퀀스로 전송된 연속 오디오 신호를 오류 없이 재구성할 수 있습니다.

디지털 시스템에서는 신호를 나타내기 위해 더 많은 이진수를 사용함으로써 신호의 보다 정확한 표현을 얻을 수 있다.이렇게 하면 신호를 처리하기 위해 더 많은 디지털 회로가 필요하지만, 각 자릿수는 동일한 종류의 하드웨어에 의해 처리되므로 쉽게 확장할 수 있는 시스템이 됩니다.아날로그 시스템에서 추가 분해능은 신호 사슬의 각 단계의 선형성 및 노이즈 특성에 대한 근본적인 개선을 필요로 한다.

컴퓨터로 제어되는 디지털 시스템에서는 소프트웨어 리비전을 통해 새로운 기능을 추가할 수 있으며 하드웨어를 변경할 필요가 없습니다.대부분의 경우 이 작업은 제품 소프트웨어를 업데이트하여 공장 밖에서 수행할 수 있습니다.이렇게 하면 제품이 고객에게 맡겨진 후에도 제품의 디자인 오류를 수정할 수 있습니다.

디지털 시스템에서는 아날로그 시스템보다 정보 스토리지가 더 쉽습니다.디지털 시스템의 노이즈 내성 덕분에 성능 저하 없이 데이터를 저장하고 검색할 수 있습니다.아날로그 시스템에서는 노후화 및 마모로 인한 노이즈가 저장된 정보를 저하시킵니다.디지털 시스템에서는 총 노이즈가 일정 수준 이하이면 정보를 완벽하게 복구할 수 있다.더 큰 노이즈가 존재하는 경우에도 오류가 너무 많이 발생하지 않는 한 용장성을 사용하여 원래 데이터를 복구할 수 있습니다.

경우에 따라 디지털 회로는 아날로그 회로보다 더 많은 에너지를 사용하여 동일한 작업을 수행하므로 더 많은 열을 발생시켜 히트 싱크의 포함과 같은 회로의 복잡성을 증가시킵니다.노트북 또는 배터리 구동 시스템에서는 디지털 시스템의 사용이 제한될 수 있습니다.예를 들어 배터리로 구동되는 휴대 전화는 저전력 아날로그 프론트 엔드를 사용하여 기지국으로부터의 무선 신호를 증폭 및 튜닝합니다.단, 기지국에는 그리드 전력이 있어 전력 소모가 크지만 매우 유연한 소프트웨어 무선을 사용할 수 있습니다.이러한 기지국은 새로운 셀룰러 표준에서 사용되는 신호를 처리하기 위해 쉽게 재프로그래밍할 수 있습니다.

많은 유용한 디지털 시스템은 연속 아날로그 신호에서 이산 디지털 신호로 변환해야 합니다.이로 인해 양자화 오류가 발생합니다.시스템이 신호를 원하는 충실도로 표현하기에 충분한 디지털 데이터를 저장하면 양자화 오류를 줄일 수 있습니다.나이키스트-셰넌 샘플링 정리는 주어진 아날로그 신호를 정확하게 묘사하는 데 필요한 디지털 데이터의 양에 대한 중요한 지침을 제공합니다.

일부 시스템에서는 디지털 데이터 한 조각이 손실되거나 잘못 해석되면 관련 데이터의 큰 블록의 의미가 완전히 바뀔 수 있습니다.예를 들어 선형 펄스 코드 변조로 직접 저장된 오디오 데이터의 단일 비트 오류가 발생하면 최악의 경우 클릭 한 번이 발생합니다.그럼에도 불구하고 많은 사람들은 단일 비트 오류로 인해 큰 중단이 발생할 수 있음에도 불구하고 스토리지 공간을 절약하고 다운로드 시간을 절약하기 위해 오디오 압축을 사용합니다.

벼랑 효과 때문에 사용자는 특정 시스템이 고장 직전에 있는지 또는 고장 전에 훨씬 더 많은 소음을 견딜 수 있는지 구별하기가 어려울 수 있습니다.디지털 취약성은 견고성을 위한 디지털 시스템을 설계함으로써 줄일 수 있다.예를 들어 패리티 비트 또는 기타 오류 관리 방법을 신호 경로에 삽입할 수 있습니다.이러한 스킴은, 에러를 검출해, 에러를 수정하거나 데이터의 재발송신을 요구하는데 도움이 됩니다.

건설

디지털 회로는 일반적으로 논리 게이트라고 불리는 작은 전자 회로로 구성되며 조합 논리를 만드는 데 사용될 수 있습니다.각 로직 게이트는 로직 신호에 대해 동작할 때 부울 로직 기능을 수행하도록 설계되어 있습니다.논리 게이트는 일반적으로 하나 이상의 전기 제어 스위치(일반적으로 트랜지스터)에서 생성되지만, 열전자 밸브는 역사적으로 사용되었습니다.로직 게이트의 출력은 제어하거나 더 많은 로직 게이트에 공급될 수 있습니다.

또 다른 형태의 디지털 회로는 룩업 테이블로 구성됩니다(다른 종류의 PLD가 존재하지만 많은 경우 "프로그래머블 논리 디바이스"로 판매됩니다).룩업 테이블은 로직 게이트를 기반으로 기계와 동일한 기능을 수행할 수 있지만 배선을 변경하지 않고 쉽게 재프로그래밍할 수 있습니다.즉, 설계자는 와이어 배치를 변경하지 않고 설계 오류를 복구할 수 있습니다.따라서 소규모 제품에서는 프로그래밍 가능한 로직 디바이스가 권장되는 솔루션이 많습니다.일반적으로 전자 설계 자동화 소프트웨어를 사용하여 엔지니어에 의해 설계됩니다.

집적회로는 하나의 실리콘 칩에 여러 개의 트랜지스터로 구성되어 있으며 많은 수의 상호 연결된 논리 게이트를 만드는 가장 저렴한 방법입니다.집적회로는 보통 전기부품을 유지하는 기판인 프린트회로기판에 상호접속되어 있으며, 이 기판은 구리 트레이스와 함께 접속되어 있습니다.

설계.

엔지니어는 회선의 복잡성을 줄이기 위해 로직의 용장성을 최소화하기 위해 많은 방법을 사용합니다.복잡성을 줄이면 컴포넌트 수와 잠재적인 오류가 줄어들기 때문에 일반적으로 비용이 절감됩니다.논리 중복성은 이진 결정 다이어그램, 부울 대수, 카노 맵, Quine-McCluskey 알고리즘, 휴리스틱 컴퓨터 방법 등 잘 알려진 몇 가지 기술로 제거할 수 있습니다.이러한 작업은 일반적으로 컴퓨터 지원 설계 시스템 내에서 수행됩니다.

마이크로 컨트롤러와 프로그래머블 로직 컨트롤러를 갖춘 임베디드 시스템은 최적의 성능을 필요로 하지 않는 복잡한 시스템에 디지털 로직을 구현하기 위해 자주 사용됩니다.이러한 시스템은 보통 소프트웨어 엔지니어 또는 전기 기술자에 의해 사다리 논리를 사용하여 프로그래밍됩니다.

표현

표현은 엔지니어의 디지털 회로 설계에 매우 중요합니다.표현을 선택하기 위해 엔지니어는 다양한 유형의 디지털 시스템을 고려합니다.

디지털 회로를 나타내는 고전적인 방법은 동등한 논리 게이트 세트를 사용하는 것입니다.각 논리 기호는 다른 형상으로 나타납니다.실제 모양 세트는 1984년 IEEE/ANSI 표준 91-1984에 따라 도입되었으며, 현재는 집적회로 [30]제조업체에서 일반적으로 사용되고 있습니다.또 다른 방법은 동등한 전자 스위치 시스템(일반적으로 트랜지스터)을 구축하는 것입니다.이것은 진실 표로 나타낼 수 있다.

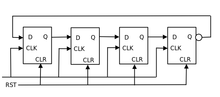

대부분의 디지털 시스템은 조합 시스템과 순차 시스템으로 나뉩니다.조합 시스템은 동일한 입력이 주어졌을 때 항상 동일한 출력을 제공합니다.시퀀셜 시스템은 출력의 일부를 입력으로 피드백하는 조합 시스템입니다.이것에 의해, 디지털 머신은 일련의 조작을 실시합니다.가장 간단한 순차 시스템은 아마도 2진수 또는 "비트"를 나타내는 메커니즘인 플립 플랍입니다.시퀀셜 시스템은 종종 스테이트 머신으로 설계됩니다.이와 같이, 엔지니어는 논리 함수의 모든 세부 사항을 고려하지 않고 시스템의 총동작을 설계하고 시뮬레이션으로 테스트할 수 있습니다.

순차 시스템은 두 가지 하위 범주로 나뉩니다.클럭 신호가 상태가 바뀌면 "동기식" 순차 시스템이 한꺼번에 상태를 변경합니다."비동기" 순차 시스템은 입력이 변경될 때마다 변경을 전파합니다.동기식 시퀀셜시스템은 플립 플랍스 등의 특성을 잘 갖춘 비동기회선으로 구성되어 있으며 클럭이 변경되었을 때만 변경되며 타이밍 마진이 신중하게 설계되어 있습니다.

논리 시뮬레이션을 위해 디지털 회로 표현은 컴퓨터 프로그램에서 처리할 수 있는 디지털 파일 형식을 가집니다.

동기 시스템

동기 순차 상태 머신을 구현하는 일반적인 방법은 그것을 조합 로직과 상태 레지스터라고 불리는 플립 플랍 세트로 나누는 것입니다.상태 레지스터는 상태를 이진수로 나타냅니다.조합 로직은 다음 상태에 대한 이진 표현을 생성합니다.각 클럭 사이클에서 상태 레지스터는 조합 로직의 이전 상태에서 생성된 피드백을 캡처하여 상태 머신의 조합 부분에 대한 불변 입력으로 피드백한다.클럭 레이트는 조합 로직에서 가장 시간이 많이 걸리는 로직 계산에 의해 제한됩니다.

비동기 시스템

대부분의 디지털 로직은 동기 설계를 생성하고 검증하기 쉽기 때문에 동기식입니다.그러나 비동기 로직은 속도가 임의의 클럭에 의해 제한되지 않고 [a]논리 게이트의 최대 속도로 실행된다는 장점이 있습니다.더 빠른 부품을 사용하여 비동기 시스템을 구축하면 회로가 더 빨라집니다.

그럼에도 불구하고 대부분의 시스템은 외부 비동기 신호를 동기 로직 회로에 수신해야 합니다.이 인터페이스는 본질적으로 비동기이므로 분석해야 합니다.널리 사용되는 비동기 회선의 예로는 싱크로나이저 플립 플랍, 스위치 디바운서 및 아비트레이터가 있습니다.

비동기 논리 컴포넌트는 가능한 모든 상태, 가능한 모든 타이밍을 고려해야 하기 때문에 설계가 어려울 수 있습니다.통상적인 방법은 이러한 각 상태가 존재할 수 있는 최소 및 최대 시간의 테이블을 작성한 후 회선을 조정하여 그러한 상태의 수를 최소화하는 것입니다.설계자는 회로가 모든 부품이 호환 상태가 될 때까지 정기적으로 대기하도록 강제해야 합니다(이것을 「자기 재동기」라고 부릅니다).신중하게 설계하지 않으면 비동기 로직이 잘못 생성되기 쉬운데, 이는 전자 부품 값의 작은 변동으로 인한 누적 지연으로 인해 실제 전자 제품이 예측할 수 없는 결과를 낳기 때문입니다.

전송 시스템 등록

많은 디지털 시스템은 데이터 흐름 기계입니다.이들은 보통 동기 레지스터 전송 로직을 사용하여 설계되며 VHDL이나 Verilog 등의 하드웨어 기술 언어로 작성됩니다.

레지스터 전송 로직에서 이진수는 레지스터라고 불리는 플립 플랍 그룹에 저장됩니다.시퀀셜 스테이트 머신은, 각 레지스터가 그 입력으로부터 새로운 데이터를 받아 들이는 타이밍을 제어한다.각 레지스터의 출력은 버스라고 불리는 와이어의 번들로, 그 수치를 다른 계산에 전달합니다.계산은 단순히 조합 논리의 한 조각일 뿐이다.각 계산에는 출력 버스도 있어, 복수의 레지스터의 입력에 접속할 수 있다.레지스터는 입력에 멀티플렉서가 있어 여러 버스 [b]중 하나의 번호를 저장할 수 있습니다.

비동기 레지스터 전송 시스템(컴퓨터 등)에는 일반적인 솔루션이 있습니다.1980년대에 일부 연구자들은 거의 모든 동기 레지스터 전송 머신이 선입선출 동기 로직을 사용하여 비동기 설계로 변환될 수 있다는 것을 발견했습니다.이 스킴에서 디지털 머신은 데이터 흐름의 세트로 특징지어진다.흐름의 각 스텝에서 동기회로는 그 스텝의 출력이 유효한지를 판단하고 [citation needed]이들 출력을 언제 사용해야 하는지를 다음 스텝에 지시한다.

컴퓨터 설계

가장 범용적인 레지스터 전송 로직 머신은 컴퓨터입니다.이것은 기본적으로 자동 바이너리 주판입니다.컴퓨터의 제어 장치는 보통 마이크로시퀀서에 의해 실행되는 마이크로프로그램으로 설계됩니다.마이크로 프로그램은 연주자-피아노 롤과 매우 유사합니다.마이크로 프로그램의 각 테이블 엔트리는 컴퓨터를 제어하는 모든 비트의 상태를 명령합니다.다음으로 시퀀서가 카운트되고 카운트는 마이크로 프로그램을 포함하는 메모리 또는 조합 로직 머신에 대처합니다.마이크로프로그램의 비트는 연산 로직 유닛, 메모리 및 마이크로시퀀서 자체를 포함한 컴퓨터의 다른 부분을 제어합니다.이와 같이 컴퓨터의 제어장치를 설계하는 복잡한 작업은 훨씬 단순한 논리기계의 집합을 프로그래밍하는 단순한 작업으로 감소한다.

거의 모든 컴퓨터가 동기화되어 있습니다.그러나 비동기 컴퓨터도 만들어졌다.예를 들어 ASPIDA DLX [32]코어가 있습니다.또 하나는 ARM [33]홀딩스에 의해 제공되었다.그러나 현대의 컴퓨터 디자인은 이미 가장 느린 컴포넌트인 보통 메모리의 속도로 동작하기 때문에 속도상의 이점이 없습니다.클럭 분배 네트워크가 필요하지 않기 때문에 소비전력이 다소 낮습니다.예상치 못한 장점은 비동기 컴퓨터가 스펙트럼 순도의 무선 노이즈를 발생시키지 않는다는 것입니다.무선에 민감한 일부 휴대 전화 베이스 스테이션컨트롤러에서 사용됩니다.전기 및 무선 방출을 [33]해독하기가 더 어려울 수 있기 때문에 암호화 애플리케이션에서 더 안전할 수 있습니다.

컴퓨터 아키텍처

컴퓨터 아키텍처는 레지스터, 계산 로직, 버스 및 기타 컴퓨터의 부품을 특정 목적에 맞게 가능한 한 최적으로 배열하는 전문 엔지니어링 활동입니다.컴퓨터 설계자들은 프로그래밍 오류에 대한 내성을 높일 뿐만 아니라 비용 절감과 컴퓨터 속도 향상에 많은 노력을 기울였습니다.컴퓨터 설계자의 일반적인 목표는 스마트폰과 같은 배터리 구동식 컴퓨터 시스템에서 사용되는 전력을 줄이는 것입니다.

디지털 회선의 설계상의 문제

이 섹션은 어떠한 출처도 인용하지 않습니다.(2015년 9월 (이 및 ) |

디지털 회로는 아날로그 부품으로 만들어진다.설계는 컴포넌트의 아날로그 특성이 원하는 디지털 동작을 지배하지 않도록 해야 합니다.디지털 시스템은 노이즈 및 타이밍 여유, 기생 인덕턴스 및 캐패시턴스를 관리해야 합니다.

불량 설계에는 글리치, 일부 로직은 트리거하지만 다른 로직은 트리거하지 않는 고속 펄스, 유효한 임계값 전압에 도달하지 않는 런트 펄스 등의 간헐적인 문제가 있습니다.

또한 클럭된 디지털 시스템이 아날로그 시스템 또는 다른 클럭에서 구동되는 시스템에 인터페이스하는 경우 입력의 변경이 디지털 입력 래치의 셋업 시간을 위반하는 경우 디지털 시스템은 준안정성이 발생할 수 있습니다.

디지털 회로는 아날로그 부품으로 만들어지기 때문에 디지털 회로는 비슷한 공간과 전력을 사용하는 고정밀 아날로그 회로보다 더 느리게 계산된다.단, 노이즈 내성이 높기 때문에 디지털 회선은 보다 반복적으로 계산됩니다.

자동 설계 도구

이 섹션은 어떠한 출처도 인용하지 않습니다. 2021년 6월 (이를 에 대해 설명합니다) |

대형 로직 머신을 설계하는 작업의 대부분은 전자 설계 자동화(EDA)를 통해 자동화되었습니다.

논리에 대한 간단한 진실 테이블 스타일의 설명은 논리 게이트의 축소된 시스템 또는 원하는 출력을 생성하는 더 작은 룩업 테이블을 자동으로 생성하는 EDA에 의해 최적화되는 경우가 많습니다.이러한 종류의 소프트웨어의 가장 일반적인 예는 에스프레소 휴리스틱 로직 미니마이저입니다.대규모 로직 시스템의 최적화는 Quine-McCluskey 알고리즘 또는 바이너리 결정 다이어그램을 사용하여 수행할 수 있습니다.유전자 알고리즘과 아닐 최적화에 대한 유망한 실험이 있다.

비용이 많이 드는 엔지니어링 프로세스를 자동화하기 위해 일부 EDA는 상태 머신을 설명하는 상태 테이블을 가져와 상태 머신의 조합 로직을 위한 진실 테이블 또는 함수 테이블을 자동으로 생성할 수 있습니다.상태 테이블은 각 상태와 각 상태와 관련된 출력 신호 간의 전환을 제어하는 조건을 나열하는 텍스트입니다.

대부분의 경우 실제 논리 시스템은 일련의 하위 프로젝트로 설계되며, 이러한 프로젝트들은 툴 플로우를 사용하여 결합됩니다.도구 흐름은 보통 스크립트 언어를 사용하여 제어됩니다. 스크립트 언어는 소프트웨어 설계 도구를 올바른 순서로 호출할 수 있는 단순화된 컴퓨터 언어입니다.마이크로프로세서와 같은 대형 논리 시스템의 도구 흐름은 수천 개의 명령어 길이가 될 수 있으며 수백 명의 엔지니어의 작업을 결합할 수 있습니다.쓰기 및 디버깅 도구 흐름은 디지털 설계를 생산하는 기업에서 확립된 엔지니어링 전문 분야입니다.도구 흐름은 일반적으로 로직을 물리적으로 구성하는 방법을 설명하는 상세 컴퓨터 파일 또는 파일 집합으로 종료됩니다.종종 집적회로 또는 프린트회로 기판에 트랜지스터와 와이어를 그리는 방법에 대한 지침으로 구성됩니다.

툴 플로우의 일부는 예상되는 입력에 대해 시뮬레이션된 로직의 출력을 검증함으로써 디버깅됩니다.테스트 도구는 입력 및 출력 세트가 포함된 컴퓨터 파일을 가져와 시뮬레이션된 동작과 예상 동작 간의 불일치를 강조 표시합니다.입력 데이터가 정확하다고 판단되면 설계 자체의 정확성을 검증해야 합니다.일부 도구 흐름은 먼저 설계를 생성한 다음 설계를 스캔하여 도구 흐름에 적합한 입력 데이터를 생성함으로써 설계를 검증합니다.스캔한 데이터가 입력 데이터와 일치할 경우 툴 플로우에 오류가 발생하지 않았을 수 있습니다.

함수 검증 데이터는 일반적으로 검정 벡터라고 합니다.기능 테스트 벡터는 공장에서 보존되어 새로 구성된 로직이 올바르게 작동하는지 테스트하기 위해 사용될 수 있습니다.단, 기능 테스트패턴이 모든 제조 장애를 검출하는 것은 아닙니다.생산 테스트는 많은 경우 자동 테스트 패턴 생성 소프트웨어 도구로 설계됩니다.이들은 로직의 구조를 검사하고 특정 잠재적 결함을 대상으로 하는 테스트를 체계적으로 생성함으로써 테스트 벡터를 생성합니다.이렇게 하면 설계가 적절하게 테스트 가능한 경우 결함 커버리지가 100%에 근접할 수 있습니다(다음 섹션 참조).

설계가 존재하고 검증 및 테스트 가능한 경우, 많은 경우 설계를 제조할 수 있도록 처리해야 합니다.현대의 집적회로에는 포토 레지스트의 노출에 사용되는 빛의 파장보다 작은 특징이 있습니다.제조성을 위해 설계된 소프트웨어는 노출 마스크에 간섭 패턴을 추가하여 개방 회로를 제거하고 마스크의 대비 효과를 높입니다.

테스트성을 위한 설계

논리회로를 테스트하는 데는 몇 가지 이유가 있습니다.회로를 처음 개발할 때 설계 회로가 필요한 기능 및 타이밍 사양을 충족하는지 확인해야 합니다.올바르게 설계된 회로의 복수의 카피를 제조하고 있는 경우는, 각 카피를 테스트하고, 제조 공정에서 [34]어떠한 결함도 발생하지 않은 것을 확인하는 것이 중요합니다.

대형 논리 기계(예를 들어, 100개 이상의 논리 변수가 있음)는 천문학적인 수의 가능한 상태를 가질 수 있습니다.분명히, 그러한 기계의 모든 상태를 공장에서 테스트하는 것은 불가능하다. 왜냐하면 각 상태를 테스트하는 데 1마이크로초밖에 걸리지 않는다고 해도, 우주가 시작된 이후 마이크로초보다 더 많은 가능한 상태가 있기 때문이다.

대형 로직 머신은 거의 항상 소형 로직 머신의 어셈블리로 설계됩니다.시간을 절약하기 위해 작은 서브머신은 테스트 회로용으로 영구적으로 설치되는 설계에 의해 격리되어 독립적으로 테스트됩니다.하나의 일반적인 테스트 방식은 로직 머신의 일부가 테스트 사이클에 들어가도록 강제하는 테스트 모드를 제공합니다.테스트 사이클은 일반적으로 기계의 큰 독립 부품을 연습합니다.

경계 스캔은 스캔 체인으로 알려진 하나 이상의 시프트 레지스터를 통해 외부 테스트 장비와의 시리얼 통신을 사용하는 일반적인 테스트 방식입니다.시리얼 스캔에는 데이터를 반송하기 위한 와이어가 1개 또는 2개뿐이며, 자주 사용하지 않는 테스트 로직의 물리적 크기와 비용을 최소화합니다.모든 테스트 데이터 비트가 제자리에 배치된 후 설계가 정상 모드로 재구성되고 하나 이상의 클럭 펄스가 적용되어 고장(예: 낮은 위치에서 고착 또는 높은 위치에서 고착)을 테스트하고 테스트 결과를 스캔 시프트 레지스터의 플립 플랍 또는 래치에 캡처합니다.마지막으로 테스트 결과를 블록 경계로 이동하여 예측된 양호한 기계 결과와 비교한다.

보드 테스트 환경에서는 시리얼에서 병렬로 테스트하는 것이 JTAG 표준으로 정식화되어 있습니다.

트레이드오프

디지털 로직 시스템의 실용성은 비용, 신뢰성, 팬아웃 및 속도에 따라 결정됩니다.엔지니어들은 이러한 요소들의 바람직한 조합을 찾기 위해 수많은 전자 장치를 탐색해 왔습니다.

비용.

논리 게이트의 비용은 매우 많은 게이트가 컴퓨터나 다른 첨단 디지털 시스템을 구축하기 위해 필요하기 때문에 매우 중요합니다.게이트가 더 많은 시스템이 더 적합합니다.디지털 컴퓨터의 대부분은 단순히 논리 게이트의 상호 연결된 네트워크이기 때문에, 컴퓨터 구축의 전체적인 비용은 논리 게이트의 비용과 강하게 관련되어 있습니다.1930년대에, 최초의 디지털 논리 시스템은 저렴하고 상대적으로 신뢰성이 높았기 때문에 전화 릴레이로 구성되었다.

최초의 집적회로는 무게를 줄이고 아폴로 유도 컴퓨터가 우주선의 관성 유도 시스템을 제어할 수 있도록 하기 위해 만들어졌다.최초의 집적회로 로직 게이트의 가격은 거의 US$50이며, 2021년에는 $458에 해당합니다.놀랍게도 회로가 대량 생산될 무렵에는 디지털 로직을 구축하는 가장 저렴한 방법이 되었습니다.이 테크놀로지의 향상에 의해, 그 후의 코스트의 향상이 모두 추진되고 있습니다.

집적회로의 등장으로 칩의 절대사용수를 줄이는 것도 비용절감을 위한 또 다른 방법이 되었습니다.설계자의 목표는 단순한 회로를 만드는 것이 아니라 컴포넌트의 수를 줄이는 것입니다.이로 인해 기반이 되는 디지털 로직과 관련하여 설계가 더 복잡해질 수 있지만 컴포넌트의 수, 보드 크기, 소비 전력까지 감소합니다.

신뢰성.

프린트 회로 기판의 컴포넌트 수를 줄이는 또 다른 주된 이유는 납땜 접속 장애로 인한 제조 결함률을 낮추고 신뢰성을 높이는 것입니다.결함과 고장률은 컴포넌트 핀의 총수와 함께 증가하는 경향이 있습니다.

디지털 기계는 종종 수백만 개의 논리 게이트를 가지고 있습니다.대부분의 디지털 머신 설계자는 비용 절감을 위해 최적화합니다.그 결과 단일 로직 게이트의 장애로 인해 디지털 머신이 고장나는 경우가 많습니다.단일 게이트의 장애로 인해 오작동이 발생하지 않는 다중 로직을 사용하여 기계를 보다 신뢰할 수 있도록 설계할 수 있지만, 이는 반드시 더 많은 컴포넌트를 사용해야 하므로 비용이 증가하고 일반적으로 기계의 무게가 증가하며 소비 전력이 증가할 수 있습니다.

로직 게이트의 신뢰성은 평균 고장 간격(MTBF)으로 설명할 수 있습니다.디지털 머신은 스위치의 MTBF가 수백 시간 이상 증가했을 때 처음으로 유용하게 되었습니다.그럼에도 불구하고, 이 기계들 중 많은 것들은 복잡하고 잘 연구된 수리 절차를 거쳤으며, 튜브가 타거나 나방이 릴레이에 끼어서 몇 시간 동안 작동하지 않았습니다.최신 트랜지스터형 집적회로 로직 게이트는 820억 시간(8.2×1010 h)[35] 이상의 MTBF를 가집니다.집적회로는 논리 게이트가 매우 많기 때문에 이 수준의 신뢰성이 필요합니다.

팬아웃

팬아웃은 게이트 [36]출력의 전류 정격을 초과하지 않고 단일 로직 출력으로 제어할 수 있는 로직 입력 수를 나타냅니다.실용적인 최소 팬아웃은 약 [citation needed]5개입니다.스위치용 CMOS 트랜지스터를 사용하는 최신 전자 로직 게이트는 팬아웃이 더 높습니다.

속도

스위칭 속도는 논리 출력이 true에서 false로 또는 그 반대로 변경되기까지 걸리는 시간을 나타냅니다.로직 속도가 빨라지면 더 짧은 시간에 더 많은 작업을 수행할 수 있습니다.현대의 전자 디지털 로직은 통상적으로 5GHz에서 전환되며 일부 실험실 시스템은 1THz [citation needed]이상에서 전환됩니다.

로직 패밀리

디지털 설계는 비교적 저렴하고 신뢰성이 높지만 느린 릴레이 로직에서 시작되었습니다.경우에 따라서는 기계적인 고장이 발생할 수 있습니다.팬아웃은 보통 10개 정도였는데, 코일의 저항과 고전압 접점의 아크에 의해 제한되었습니다.

나중에 진공관이 사용되었습니다.이것들은 매우 빨랐지만 열을 발생시켰고 필라멘트가 타버리기 때문에 신뢰할 수 없었습니다.팬아웃은 일반적으로 5에서 7까지였으며, 튜브 전류에 의한 가열에 의해 제한되었다.1950년대에 실리콘과 같은 휘발성 요소를 생략한 필라멘트로 특수 컴퓨터 튜브가 개발되었다.이것들은 수십만 시간 동안 계속되었다.

최초의 반도체 로직 패밀리는 저항-트랜지스터 로직이었습니다.이것은 튜브보다 신뢰성이 천 배 높고, 발열량이 낮으며, 소비 전력은 적지만, 팬 아웃은 3으로 매우 낮았습니다.다이오드-트랜지스터 로직은 팬아웃을 약 7까지 향상시키고 전력을 줄였습니다.일부 DTL 설계에서는 팬아웃을 증가시키기 위해 NPN 트랜지스터와 PNP 트랜지스터의 층이 번갈아 있는 2개의 전원장치를 사용했습니다.

트랜지스터-트랜지스터 로직(TTL)은 이러한 기능보다 크게 향상되었습니다.초기 디바이스에서는 팬아웃이 10으로 개선되었으며, 그 후의 변형은 확실히 20을 달성했습니다.또한 TTL은 속도가 빨랐으며, 일부 변형은 20ns의 낮은 전환 시간을 달성했습니다.일부 설계에서는 아직 TTL이 사용되고 있습니다.

이미터 결합 로직은 매우 빠르지만 많은 전력을 소비합니다.많은 중규모 컴포넌트로 구성된 Illiac IV와 같은 고성능 컴퓨터에 널리 사용되었습니다.

지금까지 오늘날 구축된 가장 일반적인 디지털 집적회로는 CMOS 로직을 사용합니다. CMOS 로직은 고속으로 높은 회로 밀도와 게이트당 낮은 전력을 제공합니다.이는 IBM System z와 같은 크고 빠른 컴퓨터에서도 사용됩니다.

최근의 동향

2009년 연구자들은 멤리스터가 부울 상태 스토리지를 구현할 수 있고 익숙한 CMOS 반도체 [37]프로세스를 사용하여 매우 적은 공간과 전력으로 완전한 로직 패밀리를 제공할 수 있다는 것을 발견했습니다.

초전도 발견으로 트랜지스터 대신 조지프슨 접합을 사용하는 고속단유속 양자(RSFQ) 회로 기술이 개발됐다.최근에는 비선형 광학 요소를 사용하여 디지털 정보를 처리할 수 있는 순수 광학 컴퓨팅 시스템을 구축하려는 시도가 이루어지고 있습니다.

「 」를 참조해 주세요.

메모들

레퍼런스

- ^ Null, Linda; Lobur, Julia (2006). The essentials of computer organization and architecture. Jones & Bartlett Publishers. p. 121. ISBN 978-0-7637-3769-6.

We can build logic diagrams (which in turn lead to digital circuits) for any Boolean expression...

- ^ Peirce, C.S. "편지, Peirce to A. 1886년 찰스 1세의 저서 '마르캉드' Peirce, v. 5, 1993, 페이지 541-3.구글 프리뷰Burks, Arthur W. 참조 "리뷰:찰스 S.피어스, 수학의 새로운 요소," 미국수학회 회보 v. 84, n. 5(1978), 페이지 913–18, 917을 참조한다.PDF E프린트

- ^ 1946년에 ENIAC는 약 174 kW를 필요로 했다.이에 비해 최신 노트북은 약 30W(약 6000배)의 전력을 소비합니다."Approximate Desktop & Notebook Power Usage". University of Pennsylvania. Archived from the original on 3 June 2009. Retrieved 20 June 2009.

- ^ "A Computer Pioneer Rediscovered, 50 Years On". The New York Times. April 20, 1994.

- ^ Lee, Thomas H. (2003). The Design of CMOS Radio-Frequency Integrated Circuits (PDF). Cambridge University Press. ISBN 9781139643771.

- ^ Puers, Robert; Baldi, Livio; Voorde, Marcel Van de; Nooten, Sebastiaan E. van (2017). Nanoelectronics: Materials, Devices, Applications, 2 Volumes. John Wiley & Sons. p. 14. ISBN 9783527340538.

- ^ Lavington, Simon (1998), A History of Manchester Computers (2 ed.), Swindon: The British Computer Society, pp. 34–35

- ^ "The Chip that Jack Built". Texas Instruments. 2008. Retrieved 29 May 2008.

- ^ Bassett, Ross Knox (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. p. 46. ISBN 9780801886393.

- ^ "1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine. Computer History Museum.

- ^ a b "Who Invented the Transistor?". Computer History Museum. 4 December 2013. Retrieved 20 July 2019.

- ^ "Triumph of the MOS Transistor". YouTube. Computer History Museum. 6 August 2010. Archived from the original on 2021-12-11. Retrieved 21 July 2019.

- ^ Motoyoshi, M. (2009). "Through-Silicon Via (TSV)". Proceedings of the IEEE. 97 (1): 43–48. doi:10.1109/JPROC.2008.2007462. ISSN 0018-9219. S2CID 29105721.

- ^ "Tortoise of Transistors Wins the Race - CHM Revolution". Computer History Museum. Retrieved 22 July 2019.

- ^ "Transistors Keep Moore's Law Alive". EETimes. 12 December 2018. Retrieved 18 July 2019.

- ^ a b "Applying MOSFETs to Today's Power-Switching Designs". Electronic Design. 23 May 2016. Retrieved 10 August 2019.

- ^ B. SOMANATHAN NAIR (2002). Digital electronics and logic design. PHI Learning Pvt. Ltd. p. 289. ISBN 9788120319561.

Digital signals are fixed-width pulses, which occupy only one of two levels of amplitude.

- ^ Joseph Migga Kizza (2005). Computer Network Security. Springer Science & Business Media. ISBN 9780387204734.

- ^ 2000 Solved Problems in Digital Electronics. Tata McGraw-Hill Education. 2005. p. 151. ISBN 978-0-07-058831-8.

- ^ Chan, Yi-Jen (1992). Studies of InAIAs/InGaAs and GaInP/GaAs heterostructure FET's for high speed applications. University of Michigan. p. 1.

The Si MOSFET has revolutionized the electronics industry and as a result impacts our daily lives in almost every conceivable way.

- ^ Grant, Duncan Andrew; Gowar, John (1989). Power MOSFETS: theory and applications. Wiley. p. 1. ISBN 9780471828679.

The metal-oxide-semiconductor field-effect transistor (MOSFET) is the most commonly used active device in the very large-scale integration of digital integrated circuits (VLSI). During the 1970s these components revolutionized electronic signal processing, control systems and computers.

- ^ Golio, Mike; Golio, Janet (2018). RF and Microwave Passive and Active Technologies. CRC Press. pp. 18–2. ISBN 9781420006728.

- ^ Hittinger, William C. (1973). "Metal-Oxide-Semiconductor Technology". Scientific American. 229 (2): 48–59. Bibcode:1973SciAm.229b..48H. doi:10.1038/scientificamerican0873-48. ISSN 0036-8733. JSTOR 24923169.

- ^ Peter Clarke (14 October 2005). "Intel enters billion-transistor processor era". EE Times.

- ^ "13 Sextillion & Counting: The Long & Winding Road to the Most Frequently Manufactured Human Artifact in History". Computer History Museum. April 2, 2018. Retrieved 12 October 2020.

- ^ Golio, Mike; Golio, Janet (2018). RF and Microwave Passive and Active Technologies. CRC Press. pp. ix, I-1, 18–2. ISBN 9781420006728.

- ^ Rappaport, T. S. (November 1991). "The wireless revolution". IEEE Communications Magazine. 29 (11): 52–71. doi:10.1109/35.109666. S2CID 46573735.

- ^ "The wireless revolution". The Economist. January 21, 1999. Retrieved 12 September 2019.

- ^ 폴 호로위츠와 윈필드 힐, 아트 오브 일렉트로닉스 제2판케임브리지 대학 출판부, 1989년 ISBN 0-521-37095-7페이지 471

- ^ 마이니 A.K. (2007년)디지털 전자 제품의 원리, 장치 및 응용 프로그램.치체스터(영국):John Wiley & Sons Ltd.

- ^ 펜타곤 심포지엄:시판 범용 전자 디지털 컴퓨터, 워싱턴 D.C., 1952년 5월 14일

- ^ "ASODA sync/async DLX Core". OpenCores.org. Retrieved September 5, 2014.

- ^ a b Clarke, Peter. "ARM Offers First Clockless Processor Core". eetimes.com. UBM Tech (Universal Business Media). Retrieved 5 September 2014.

- ^ Brown S & Vranesic Z.(2009).VHDL 설계를 사용한 디지털 로직의 기초.제3판뉴욕, 뉴욕:맥그로 힐입니다

- ^ MIL-HDBK-217F 통지 2, 섹션 5.3에서는 40C에서 100,000 게이트 0.8 마이크로미터 CMOS 상용 IC에 대해 설명합니다.라인 사이즈가 0.045 마이크로미터로 감소하여 게이트마다 필요한 오프칩 접속이 적기 때문에 2010년의 장애율이 향상되었습니다.

- ^ 클라이츠, 윌리엄(2002).디지털 및 마이크로프로세서의 기초:이론과 응용제4판어퍼 새들러 리비버, 뉴저지주: 피어슨/펜티스 홀

- ^ Lehtonen, Eero; Laiho, Mika (2009). Stateful implication logic with memristors. 2009 IEEE/ACM International Symposium on Nanoscale Architectures. pp. 33–36. doi:10.1109/NANOARCH.2009.5226356.

추가 정보

- 더글라스 르윈, 스위칭 회로의 논리 설계, 넬슨, 1974.

- R. H. Katz, 컨템포러리 로직 디자인, The Benjamin/Cummings Publishing Company, 1994.

- P. K. Lala, Prentice Hall, Practical Digital Logic Design and Testing, 1996.

- Y. K. Chan과 S. Y. Lim, 전자학 연구 B, Vol. 1, 269-290, 2008, "합성 개구 레이더(SAR) 신호 생성, 멀티미디어 대학 공학 및 기술학부, 잘란 아예르 케로, 북베랑 베루이타"

외부 링크

- 디지털 회선 프로젝트: 집적회로 구현을 통한 디지털 회로 개요(2014)

- Wayback Machine에서의 전기회로의 레슨 - Volume IV (디지털) (2012-11-27)

- MIT OpenCourseWare 디지털 디자인 클래스 자료 소개("6.004: Computation Structures")