전기화학 RAM

Electrochemical RAM| 컴퓨터 메모리 및 데이터 스토리지 유형 |

|---|

| 휘발성 |

| 비휘발성 |

Electrochemical Random-Access Memory(ECRAM)는 딥 러닝 아날로그 가속용으로 설계된 Multiple Level per Cell(MLC; 셀당 멀티레벨)[1][2]을 갖춘 비휘발성 메모리(NVM)의 일종입니다.ECRAM 셀은 도전성 채널, 절연 전해질, 이온 리저버 및 금속 접점으로 이루어진 3단자 디바이스이다.채널의 저항은 전계 적용 시 채널과 전해질 사이의 인터페이스에서 이온 교환에 의해 변조됩니다.전하 전송 프로세스를 통해 전원이 공급되지 않은 상태 유지 및 여러 개별 레벨 프로그래밍이 가능하며, 둘 다 전계효과 트랜지스터(FET)와 ECRAM 작동을 구별합니다.쓰기 조작은 결정론적이고 대칭적인 증강과 저하의 원인이 될 수 있으므로 ECRAM 어레이는 인공신경망(ANN)의 물리적인 구현에서 인위적인 시냅스 가중치 역할을 하는 데 매력적입니다.기술적 과제에는 에너지 재료와 관련된 개방 회로 전위(OCP) 및 반도체 주조 공장 호환성이 포함됩니다.대학, 정부 연구소 및 기업 연구팀이 아날로그 컴퓨팅용 ECRAM 개발에 기여하고 있습니다.특히 산디아 국립 연구소는lithium-based 세포 solid-state 배터리 materials,[3]스탠포드 대학에 의해 영감을 받은 유기proton-based cell,[4]을 건립하고 천공 카아드 회계 방식(IBM)금속 산화물 ECRAM의 배열을 디자인했습니다에 물류로 회귀하는 일에 메모리 내selector-free 병렬 프로그래밍을 디자인했다. inserBEOL(Back End of [5]Line)을 사용합니다.

작동

기입하다

게이트에 가해지는 응력은 채널 전극에 대해 고정 전류 또는 바이어스의 형태로 작용하여 이온을 자유 캐리어를 통해 전하 전달이 발생하는 전해질/채널 인터페이스 쪽으로 또는 멀어지게 할 수 있습니다.채널에 삽입하면 이온 전하가 중화되고 원자종이 전도성 숙주 매트릭스에 인터컬레이트 또는 결합하며, 경우에 따라 변형 및 국소 위상 변환을 생성한다.이러한 가역 프로세스는 배터리 셀 또는 전자크롬 장치의 양극/음극 반응과 동등하다.ECRAM에서는 메모리 소자의 프로그래밍은 용량이나 불투명도의 변화가 아니라 스트레스 신호의 결과로 삽입 또는 제거되는 원자종에 관련된 채널 전도율의 변화에 의해 정의된다.

읽어주세요

3개의 전극이 존재하기 때문에 읽기 동작과 쓰기 동작이 분리되므로 읽기 교란이 제한됩니다.채널 전극 사이에 소량의 바이어스가 인가되어 결과 판독 전류가 채널 전도율에 비례하여 디바이스의 프로그램 상태를 검출한다.

스피드

ECRAM 셀의 프로그래밍 속도는 이온의 대량 확산에 의해 제한되지 않습니다.실제로 전해질과 채널 사이의 인터페이스 평면을 교차하면 전도성의 변화를 유도할 수 있습니다.실제로 나노초 쓰기 펄스는 프로그래밍을 [6]트리거할 수 있습니다.게이트 캐패시턴스, 전자 전도율 등의 트레이드오프는 안착 과도현상을 발생시켜 최대 읽기-쓰기 [7]빈도를 제한할 수 있습니다.

어레이

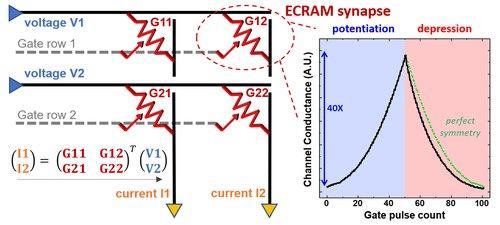

ECRAM 어레이는 의사 크로스바 레이아웃에 통합되어 있으며 게이트 액세스 라인은 행 또는 열의 모든 디바이스에 공통입니다.채널과 게이트 전극 간의 이온 교환 시 배터리의 구동력인 전기화학적 전위 변화가 발생할 경우 게이트 접점에 개방 회로 전위(OCP)가 존재하며 프로그래밍된 상태에 따라 장치마다 다릅니다.게이트 회선을 공유하는 셀 간의 크로스 토크를 방지하기 위해 메모리 [8]소자와 직렬로 각 셀을 분리하는 액세스 장치를 추가한다.ECRAM 설계에서 OCP를 억제하여 셀 크기/복잡도를 최소화하여 셀렉터가 필요 없는 디바이스 [5]어레이의 병렬 읽기/프로그래밍을 가능하게 합니다.

시냅스 함수

원칙

NVM(비휘발성 메모리)을 메모리 내 컴퓨팅에 활용할 수 있기 때문에 스토리지와 프로세싱 유닛 간의 데이터 전송 빈도를 줄일 수 있습니다.이를 통해 Von Neumann의 병목 현상을 해소함으로써 계층형 시스템 아키텍처보다 궁극적으로 컴퓨팅 시간과 에너지 효율을 향상시킬 수 있습니다.따라서 크로스바 어레이의 노드에서 멀티레벨셀(MLC)을 사용하면 아날로그 연산을 제때 실행할 수 있으며 벡터(행입력신호)×매트릭스(메모리 어레이) 곱셈 등의 전압 부호화 데이터도 가능하다.키르히호프와 옴의 법칙에 따라 각 컬럼에서 수집된 전류를 적분하여 결과 벡터를 구합니다.ECRAM 셀은 프로그래밍 사이클 중에 셀을 쓰기 위해 각 행에 추가 라인을 추가하여 의사 크로스바 아키텍처를 생성한다.인공지능(AI) 분야에서는 다수의 매트릭스 다중 연산에 의존하여 분류 및 학습 작업에 심층 신경망(DNN)이 사용된다.따라서 이러한 작업에 NVM 기술을 사용하는 아날로그 컴퓨팅은 매우 매력적입니다.ECRAM 셀은 저항성 RAM(ReRAM 또는 RRAM) 및 위상 변화 메모리(PCM)와 같은 다른 장치와 비교할 때 고유의 결정론적 대칭 프로그래밍 특성 때문에 아날로그 딥 러닝 가속기에 사용할 수 있도록 고유하게 배치되어 있습니다.

요구 사항들

| 미터법 | 구성 단위 | NVM 시냅스 세포[9] 표적 |

|---|---|---|

| G범위 | ns | 9-72 |

| 온/오프 비율 | n.a. | 8 |

| 상태 수 | n.a. | 1000 |

| 상하 비대칭 | % | 5 |

| 기입 시간 | ns | 1 |

인공신경망(ANN)의 물리적 구현은 소프트웨어의 부동소수점 정밀도 가중치에 대해 벤치마킹할 때 Iso-정확도로 수행되어야 한다.아날로그 딥 러닝액셀러레이터에 필요한 디바이스 속성의 경계를 설정합니다.IBM Resistive Processing Unit(RPU) 설계에서 IBM Resistive Processing Unit(RPU)는 이러한 요구사항을 발표했으며, 이 [9]중 일부는 여기에 나열되어 있습니다.알고리즘과 하드웨어의 공동설계는 이들을 다소 완화시킬 수 있지만 다른 [10]단점이 없다면 그렇지 않습니다.

스토리지 대신 NVM을 시냅스 가중치로 사용하는 것은 목표 저항 범위, 레벨 수 및 프로그래밍 속도와 대칭에 대해 크게 다른 요구 사항을 의미합니다.메모리 내 연산은 어레이를 통해 병렬로 이루어지기 때문에 많은 디바이스가 동시에 처리되므로 에너지 소산을 제한하기 위해 높은 평균 저항을 가져야 합니다.고정밀 계산을 수행하고 노이즈에 대한 복원력을 갖추기 위해 NVM 셀에는 다수의 개별 상태가 필요합니다.프로그래밍 시간은 최고 저항 상태에서 최저 저항 상태로가 아니라 레벨 간에만 빠르면 됩니다.각 프로그래밍 사이클(백 전파) 동안 가중치 업데이트는 음수 또는 양수일 수 있으며, 따라서 업/다운 트레이스는 학습 알고리즘을 수렴하기 위해 대칭이 필요합니다.모든 NVM 테크놀로지는 이러한 타겟에 대해 어려움을 겪고 있습니다.ECRAM 개별 셀은 이러한 엄격한 메트릭을 [5]충족할 수 있지만 고밀도 어레이 수율 및 확률성을 입증해야 합니다.

ECRAM Synaptic 어레이를 사용한 데모

산디아 국립 연구소

2019년 사이언스지에 발표된 것처럼 앨릭 A. 엘리엇 풀러에 의해 보도되었다. Sandia National Laboratories의 Talin 등, 스탠포드 대학, 매사추세츠 대학 Amherst와의 [8]협력:

CBM(conductive bridge memory) 장치로 격리된 공동 평면 유기 다단계 셀을 사용하여 최대 3×3 어레이에서 병렬 프로그래밍 및 주소 지정을 시연합니다.특히 2층 뉴럴 네트워크는 2진수 입력 벡터에 대해 XOR 연산을 초래하는 추론 태스크를 수행하기 위해 필요한 가중치를 전송함으로써 어레이에 매핑된다.

개개의 셀은 (모든 것이 같은 디바이스 구성에서 달성되는 것은 아니다), 속도 = 1 MHz 읽기/쓰기 사이클, 상태 수 > 50(조정 가능), 저항 범위 = 50-100 nS(조정 가능), 내구성 > 108 쓰기 ops, 크기 = 50×50 μm의2 특성을 가지고 있는 것으로 나타납니다.

IBM 리서치

IEEE International Electron Device Meeting(IEDM; IEEE International Electron Device Meeting)의 2019년 진행에서 보고한 바와 같이 IBM [5]Research의 Kim Seyoung, John Rozen 등은 다음과 같이 말합니다.

셀렉터가 없는 금속 산화 ECRAM 셀을 사용하여 2×2 배열로 병렬 프로그래밍 및 주소 지정을 시연합니다.특히 로지스틱 회귀 태스크를 1,000개의 2×1 벡터를 트레이닝 세트로 메모리 내에서 실행해, 12에폭으로 2D 커브 핏을 실현한다.

개별 셀은 (모든 것이 동일한 디바이스 구성에서 달성되는 것은 아님), 속도 = 10 ns 쓰기 펄스, 상태 수 > 1,000(조정 가능), 저항 범위 = 0 ~ 50 μS(조정 가능), 10 쓰기 ops7, 크기 < 1 × 1 μm의2 특성을 갖는 것으로 나타납니다.

셀의 실장

다양한 기관에서 ECRAM 셀을 매우 다른 소재, 레이아웃 및 성능으로 시연했습니다.

이산 셀에 대한 예제가 표에 나열되어 있습니다.

| 이온 | 채널. | 디바이스 사이즈 | 쓰기 펄스 길이 | 언급 |

|---|---|---|---|---|

| 리+ | WO 3 | 100 x 100 nm2 | 5 ns | [6] |

| 리+ | 리코 1−x 2 | 최대 1 mm2 | 0.5초 | [3] |

| 리+ | 그래핀 | 36μm2 | 10 밀리초 | [11] |

| 리+ | α-MO 3 | 최대 1 mm2 | 10 밀리초 | [12] |

| H+ | PEDOT:PSS | 0.001mm2 | 5 밀리초 | [4] |

| H+ | WO 3 | 0.05mm2 | 5 밀리초 | [13] |

| H+ | WO 3 | 0.025mm2 | 210 밀리초 | [14] |

| H+ | WO 3 | 0.01mm2 | 0.1초 | [15] |

Li-ECRAM

리튬 이온을 기반으로 한 Li-ECRAM 소자는 배터리 기술로부터 알려진 재료를 메모리 [3][11][12]설계에 적용하여 반복 가능하고 제어된 스위칭을 입증했습니다.따라서 이러한 셀은 프로그래밍된 상태에 따라 몇 볼트 이상의 OCP를 나타낼 수 있습니다.

H-ECRAM

수소 이온을 기반으로 한 H-ECRAM 소자는 프로그래밍을 [4][13][14]유도하기 위해 작은 구동력을 필요로 하는 것으로 입증되었습니다.다양한 재료의 높은 확산 계수는 메모리 셀 내의 유지 부족과 함께 내구성에도 영향을 미칠 수 있습니다.대부분의 H-ECRAM 설계에서는 액체 및/또는 유기 전해질을 사용합니다.

MO-ECRAM

금속 산화물 기반 ECRAM은 OxRam 재료와 상업용 반도체 제품에 사용되는 고k/메탈 게이트 기술에서 영감을 받았습니다.MO-ECRAM을 사용하면 OCP 및 μs 미만의 쓰기 [5]조작을 무시할 수 있습니다.

VLSI

고도의 반도체 메모리 또는 컴퓨팅 애플리케이션의 경우, 테크놀로지는 매우 대규모 집적(VLSI)과 호환성이 있어야 합니다.이로 인해 사용되는 재료와 기능적 장치를 제작하는 데 사용되는 기술에 제약이 가해집니다.여기에서는 ECRAM의 의미를 설명합니다.

반도체 주조 공장

반도체 주조 공장에서는 여러 기술을 다룰 수 있으며, 교차 오염과 장치 수율 손실을 방지하기 위해 고가의 도구 세트에 재료를 도입할 때 엄격한 규칙을 가지고 있습니다.특히 금속성 이동 이온은 활성 영역에 존재할 경우 디바이스 드리프트를 유도하여 신뢰성에 영향을 미칠 수 있습니다.주조 공장에는 안전성, 비용, 부피 등 몇 가지 다른 고려사항이 있습니다.따라서 리튬 이온 기반의 Li-ECRAM은 OCP의 존재를 넘어서는 독특한 과제에 직면해 있습니다.

백엔드오브라인(BEOL)

메모리 어레이는 논리 주변기기를 사용하여 컴퓨팅 시스템의 나머지 부분과 인터페이스해야 합니다.이러한 주변은 전계효과 트랜지스터(FET)를 기반으로 실리콘 웨이퍼 기판 표면에 구축되며 FEOL(Front End of Line)에 높은 열버젯이 적용됩니다.메모리 셀은 백엔드오브라인(BEOL) 상단의 금속 레벨 사이에 삽입할 수 있지만 다음 단계에서 사용되는 최대 400°C의 온도에 영향을 받지 않아야 합니다.고밀도 패턴화의 과제와 함께, 이러한 제약은 유기 장치를 그러한 통합에 적합하지 않게 만듭니다.

이기종 통합(HI)

새로운 메모리 재료를 도입하는 한 가지 방법은 디바이스 어레이가 논리 제어로부터 독립적으로 제조되어 FET 포함 칩에 결합되어 HBM(High Bandwidth Memory)으로 사용할 수 있도록 하는 이기종 집적(HI)을 사용하는 것입니다.그러나 이러한 스킴과 관련된 비용과 복잡성은 기존 메모리 기술을 대체하기 위한 가치 제안에 부정적인 영향을 미칩니다.

레퍼런스

- ^ Tang, Jianshi; Bishop, Douglas; Kim, Seyoung; Copel, Matt; Gokmen, Tayfun; Todorov, Teodor; Shin, SangHoon; Lee, Ko-Tao; Solomon, Paul (2018-12-01). "ECRAM as Scalable Synaptic Cell for High-Speed, Low-Power Neuromorphic Computing". 2018 IEEE International Electron Devices Meeting (IEDM). pp. 13.1.1–4. doi:10.1109/IEDM.2018.8614551. ISBN 978-1-7281-1987-8. S2CID 58674536. Retrieved 2020-07-16.

- ^ "Finite element modeling of electrochemical random access memory - iis-projects". iis-projects.ee.ethz.ch. Zürich, Switzerland: ETH Zurich. Retrieved 2020-07-16.

- ^ a b c 'E. J. Fuller et al., Adv. Mater, 29, 1604310 (2017)

- ^ a b c Y. van de Burgt et al., Nature Electronics, 1,386 (2018)

- ^ a b c d e Kim, S. (2019). "Metal-oxide based, CMOS-compatible ECRAM for Deep Learning Accelerator". 2019 IEEE International Electron Devices Meeting (IEDM). pp. 35.7.1–4. doi:10.1109/IEDM19573.2019.8993463. ISBN 978-1-7281-4032-2. S2CID 211211273.

- ^ a b Tang, J. (2018). "ECRAM as Scalable Synaptic Cell for High-Speed, Low-Power Neuromorphic Computing". 2018 IEEE International Electron Devices Meeting (IEDM). pp. 13.1.1–4. doi:10.1109/IEDM.2018.8614551. ISBN 978-1-7281-1987-8. S2CID 58674536.

- ^ D. 비숍 외, 솔리드 스테이트 디바이스 및 재료(SSDM) 국제회의 진행, 페이지 23-24 (2018)

- ^ a b Fuller, E.J.; Keene, S.T.; Melianas, A.; Wang, Z.; Agarwal, S.; Li, Y.; Tuchman, Y.; James, C.D.; Marinella, M.J.; Yang, J.J.; Salleo, A.; Talin, A.A. (2019). "Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing". Science. 364 (6440): 570–4. Bibcode:2019Sci...364..570F. doi:10.1126/science.aaw5581. PMID 31023890. S2CID 133605392.

- ^ a b Tayfun, G.; Yurii, V. (2016). "Acceleration of Deep Neural Network Training with Resistive Cross-Point Devices: Design Considerations". Frontiers in Neuroscience. 10: 333. doi:10.3389/fnins.2016.00333. PMC 4954855. PMID 27493624.

- ^ Tayfun, G.; Haensch, H. (2020). "Algorithm for Training Neural Networks on Resistive Device Arrays". Frontiers in Neuroscience. 14: 103. doi:10.3389/fnins.2020.00103. PMC 7054461. PMID 32174807.

- ^ a b Sharbati, M.T.; Du, Y.; Torres, J.; Ardolino, N.D.; Yun, M.; Xiong, F. (2018). "Artificial Synapses: Low-Power, Electrochemically Tunable Graphene Synapses for Neuromorphic Computing". Adv. Mater. 30: 1870273. doi:10.1002/adma.201870273.

- ^ a b Yang, C.-S.; Shang, D.-S.; Liu, N.; Fuller, E.J.; Agrawal, S.; Alec Talin, A.; Li, Y.-Q.; Shen, B.-G.; Sun, Y. (2018). "All-Solid-State Synaptic Transistor with Ultralow Conductance for Neuromorphic Computing". Adv. Funct. Mater. 28 (42): 1804170. doi:10.1002/adfm.201804170. OSTI 1472248. S2CID 104934211.

- ^ a b Yao, X.; Klyukin, K.; Lu, W. (2020). "Protonic solid-state electrochemical synapse for physical neural networks". Nat Commun. 11 (1): 3134. Bibcode:2020NatCo..11.3134Y. doi:10.1038/s41467-020-16866-6. PMC 7371700. PMID 32561717.

- ^ a b Yang, J.-T.; Ge, C.; Du, J.-Y.; Huang, H.-Y.; He, M.; Wang, C.; Lu, H.-B.; Yang, G.-Z.; Jin, K.-J. (2018). "Artificial Synapses Emulated by an Electrolyte-Gated Tungsten-Oxide Transistor". Adv. Mater. 30 (34): 1801548. doi:10.1002/adma.201801548. PMID 29974526. S2CID 49655665.

- ^ J. Lee 등, IEEE 국제 Silicon Nano Electronics Workshop(SNW), 31-32 (2018)의 진행 상황

외부 링크

- Moore, S.K. (11 December 2018). "Searching for the Perfect Artificial Synapse for AI". IEEE Spectrum.

- Ambrogio, S.; Adusumilli, P.; Eleftheriou, E. (11 December 2019). "The path to the "perfect" analog material and system: IBM at IEDM and NeurIPS". IBM Research Blog.

- Chandler, D.L. (19 June 2020). "Engineers design a device that operates like a brain synapse". MIT News.

- Kubota, T. (25 April 2019). "Stanford researchers' artificial synapse is fast, efficient and durable". Stanford News.

- "Sandia Powers Breakthroughs in Neuromorphic Computing". inside HPC. 1 May 2019.