priority 인코더

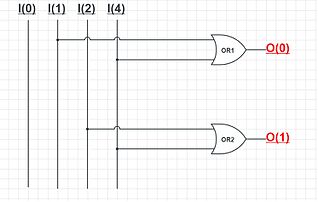

Priority encoderpriority 인코더는 복수의 바이너리 입력을 보다 적은 수의 출력으로 압축하는 회로 또는 알고리즘입니다.priority 인코더의 출력은 최상위 액티브라인 인덱스의 바이너리 표현으로 제로부터 시작합니다.이 명령어는 보통 가장 우선순위가 높은 인터럽트 입력에 따라 동작함으로써 인터럽트 요구를 제어하기 위해 사용됩니다.

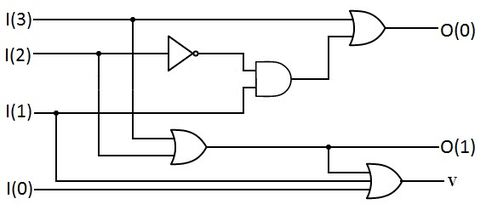

2개 이상의 입력이 동시에 주어질 경우 우선순위가 가장 높은 입력이 [1]우선됩니다.단일 비트 4 ~ 2 인코더의 예를 나타냅니다.여기서 가장 우선순위가 높은 입력은 왼쪽에 있고 "x"는 관련이 없는 값을 나타냅니다.즉, 모든 입력 값은 더 우선순위가 높은 입력으로 대체되었기 때문에 동일한 출력을 생성합니다.출력 V는 입력이 유효한지 여부를 나타냅니다.

| 나3 | 나2 | 나1 | 나0 | 오1 | 오0 | V |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | x | x | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | x | 0 | 1 | 1 |

| 0 | 1 | x | x | 1 | 0 | 1 |

| 1 | x | x | x | 1 | 1 | 1 |

priority 인코더는 어레이로 쉽게 접속할 수 있습니다.예를 들어, 6개의 4대 2의 priority 인코더로 제조된1개의 16대 4 인코더, 4대의 신호 소스를 입력에 접속한4대의 4대 2 인코더, 나머지 2대의 인코더는 처음 4대의 출력을 입력으로 받아들입니다.priority 인코더는 사용 가능한 모든 입력 설정을 처리하는 점에서 단순한 인코더 회선의 개량입니다.

priority 인코더[2][3][4] 재귀 구성

선행 영점 검출기(LZD) 또는 선행 영점 카운터(LZC)라고도 불리는 priority 인코더는 n}비트 입력 벡터를 수신하여 입력 벡터 내의 첫 번째 이진수 '1'의 인덱스를 검출합니다.유효한 신호는 입력 벡터에서 바이너리 '1'이 검출되었는지 여부를 나타내므로 인덱스는 유효하다.

priority-encoder는 재귀로 효율적으로 구성할 수 있습니다.입력 벡터는n n/k) 비트의 k 으로 분할됩니다.각 fragment에는 폭이 좁은 priority n/ { { 가 적용됩니다.각 k ndisplaystyle {의 유효한 비트는 k PE}) n/displaystyle {})로 이동하여 첫 번째 유효한 fragment를 검출합니다.이 fragment의 위치는 전체 인덱스의 상위 부분이며 fragment 자체의 정확한 위치를 지시하여 전체 인덱스의 하위 부분을 생성합니다.

제안된 구조의 깊이는 k n {\ \ \ \_ { } \ 이고 하드웨어 영역의 복잡도는 () \ \{ 。Altera의 Stratix V 또는 동등한 디바이스를 사용하는 k 4 n 4 44。n, 6-LUT를 사용하여 mux를 구현할 수 있으므로 전체 ALM이 구현됩니다.

재귀 우선 순위 인코더용 오픈 소스 Verilog 생성기는 [5]온라인에서 사용할 수 있습니다.

Verilog의 priority 인코더 동작 설명은 다음과 같습니다.[5]

// 우선순위 인컨버터의 동작 설명; // https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM 모듈 pe_paramv #( 파라미터 오우 = 512 ) // 인코더 원핫 입력 폭 ( 입력 째깍째깍 소리를 내다 , // 파이프라인 우선 인코더 클럭 입력 rst , // 파이프라인 priority 인코더의 레지스터 리셋 입력 [ 오우 -1:0] 하지 않다 , // 원핫 입력 / [OHW - 1 : 0 ] 산출량 조정하다 ['log2(오우)-1:0] 휴지통 , // 첫 번째 '1' 인덱스 / ['log2(OHW)-1:0] 산출량 조정하다 비디오 ); // 이진수가 발견된 경우 이진수가 유효합니다. // 고정되지 않은 루프 길이에 while loop 사용 // 인텔 Quartus와 잘 합성 가능II 항상 @(*) 시작한다. 휴지통 = {'log2(오우){1b0}}; 비디오 = 하지 않다[휴지통] ; 하는 동안에 ((!비디오) & & (휴지통!=(오우-1))) 시작한다. 휴지통 = 휴지통 + 1 ; 비디오 = 하지 않다[휴지통]; 끝. 끝. 엔드 모듈 심플 인코더

심플 인코더 회로는 1-핫-바이너리 변환기입니다.즉, 2개의 입력 라인이 있고n 그 중 최대 1개만 하이일 경우 이 '핫' 라인의 바이너리 코드가 n비트 출력 라인에서 생성됩니다.

레퍼런스

- ^ M. Morris Mano, Michael D.Ciletti, "디지털 디자인", 프렌티스 홀, 제4판, 2006, ISBN978-0-13-198924-5.

- ^ Abdelhadi, Ameer M. S. (2016). Architecture of block-RAM-based massively parallel memory structures : multi-ported memories and content-addressable memories (Thesis). University of British Columbia.

- ^ Abdelhadi, Ameer M.S.; Lemieux, Guy G.F. (May 2015). "Modular SRAM-Based Binary Content-Addressable Memories". 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines: 207–214. doi:10.1109/FCCM.2015.69. ISBN 978-1-4799-9969-9.

- ^ Abdelhadi, Ameer M. S.; Lemieux, Guy G. F. (December 2014). "Deep and narrow binary content-addressable memories using FPGA-based BRAMs". 2014 International Conference on Field-Programmable Technology (FPT): 318–321. doi:10.1109/FPT.2014.7082808. ISBN 978-1-4799-6245-7.

- ^ a b Abdelhadi, A.M.S.; Lemieux, G.G.F. (2014). "Modular SRAM-based Indirectly-indexed 2D Binary Content Addressable Memory II2DCAM". The University of British Columbia.

Abdelhadi, A.M.S.; Lemieux, G.G.F. (2015). "Modular SRAM-Based Binary Content-Addressable Memories" (PDF). 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines. IEEE. pp. 207–214. doi:10.1109/FCCM.2015.69. ISBN 978-1-4799-9969-9.

적용됩니다.각

적용됩니다.각