양극 접합 트랜지스터

Bipolar junction transistor | |

| 작동 원리 | 반도체 |

|---|---|

| 발명된 | 1947년 12월 |

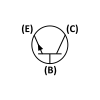

| 핀 구성 | 수집기, 베이스, 이미터 |

| 전자 기호 | |

BJT PNP 및 NPN 도식 기호 | |

양극 접합 트랜지스터(BJT)는 전자와 전자 구멍을 모두 전하 운반체로 사용하는 트랜지스터의 한 종류입니다.반면 전계효과 트랜지스터와 같은 단극 트랜지스터는 한 종류의 전하 캐리어만 사용합니다.바이폴라 트랜지스터는 단자 중 하나에 주입되는 소량의 전류가 단자 간에 흐르는 훨씬 더 큰 전류를 제어하여 장치를 증폭 또는 전환할 수 있도록 합니다.

BJT는 단일 재료 결정 영역인 n형과 p형 두 반도체 유형 사이에 두 개의 접합부를 사용합니다.접합은 성장하면서 반도체 재료의 도핑을 변경하거나 금속 펠릿을 퇴적시켜 합금 접합을 형성하거나 n형 및 p형 도핑 물질을 결정으로 확산시키는 방법 등 여러 가지 방법으로 이루어질 수 있습니다.접합 트랜지스터의 우수한 예측 가능성과 성능은 원래의 포인트 접점 트랜지스터를 빠르게 대체했습니다.확산 트랜지스터는 다른 부품과 함께 아날로그 및 디지털 기능을 위한 집적회로 소자입니다.수백 개의 양극성 접합 트랜지스터를 매우 낮은 비용으로 하나의 회로에서 만들 수 있습니다.

바이폴라 트랜지스터 집적회로는 메인프레임 및 미니 컴퓨터의 주요 활성 장치였지만, 현재 대부분의 컴퓨터 시스템은 전계효과 트랜지스터에 의존하는 집적회로를 사용합니다.바이폴라 트랜지스터는 여전히 신호 증폭, 스위칭 및 디지털 회로에 사용됩니다.특수 유형은 고전압 스위치, 무선 주파수 증폭기 또는 고전류 전환에 사용됩니다.

현재의 방향 표기법

관례상 도표상의 전류방향은 정전하가 이동하는 방향으로 나타난다.이를 관습 전류라고 합니다.그러나 많은 금속 도체의 전류는 전자의 흐름 때문입니다.전자는 음전하를 띠기 때문에 기존 [a]전류와 반대 방향으로 움직인다.한편 바이폴라 트랜지스터 내에서는 전류가 양전하된 구멍과 음전하된 전자로 구성될 수 있다.이 기사에서는 전류 화살표가 일반적인 방향으로 나타나지만, 구멍과 전자의 이동에 대한 라벨은 트랜지스터 내부의 실제 방향을 나타냅니다.

화살표 방향

바이폴라 트랜지스터 기호의 화살표는 베이스와 이미터 사이의 p-n 접합과 재래식 전류가 흐르는 방향의 점을 나타냅니다.

기능.

이 섹션은 너무 전문적이어서 대부분의 독자들이 이해할 수 없을 수도 있습니다.(2012년 7월 (이 및 에 대해 ) |

BJT는 3개의 주요 말단 영역의 도핑 유형에 따라 PNP 및 NPN 유형으로 존재합니다.NPN 트랜지스터는 얇은 p도프 영역을 공유하는 2개의 반도체 접합부를 포함하고, PNP 트랜지스터는 얇은 n도프 영역을 공유하는 2개의 반도체 접합부를 포함한다.N형 수단은 이동 전자를 제공하는 불순물(인이나 비소 등)이 도핑된 반면 P형 수단은 전자를 쉽게 받아들이는 구멍을 제공하는 불순물(붕소 등)이 도핑된 수단은 도핑된 것입니다.

BJT의 전하 흐름은 전하 캐리어의 농도가 다른 두 영역 사이의 접점을 통해 전하 캐리어가 확산되기 때문입니다.BJT의 영역은 이미터, 베이스 및 [b]컬렉터라고 불립니다.이산 트랜지스터에는 이러한 영역에 접속하기 위한 3개의 리드가 있습니다.통상, 이미터 영역은 다른 2개의 레이어에 비해 도핑이 심하고, 콜렉터는 베이스보다 가볍게 도핑됩니다(콜렉터 도핑은 일반적으로 베이스[2] 도핑보다 10배 가볍습니다).설계상 BJT 컬렉터 전류의 대부분은 도프된 이미터로부터 집전기를 향해 확산되는 소수 캐리어인 베이스에 주입된 전하 캐리어(전자 또는 홀)의 흐름에 기인하기 때문에 BJT는 소수 캐리어 소자로 분류된다.

일반적인 동작에서 베이스-이미터 접합부는 전방 바이어스입니다.즉, 접합부의 p도프측이 n도프측보다 더 양의 전위에 있고 베이스-콜렉터 접합부는 역바이어스입니다.베이스-이미터 접합부에 전방 바이어스가 적용되면 열 발생 반송파와 n 도프된 이미터 고갈 영역의 역전계 사이의 평형이 흐트러집니다.이것에 의해, 열적으로 들뜬 전자(NPN에서는, PNP에서는 구멍)가 이미터에서 베이스 영역으로 주입됩니다.이러한 전자는 이미터 근처의 고농도 영역에서 컬렉터 근처의 저농도 영역으로 베이스를 통해 확산됩니다.베이스의 전자는 베이스가 도프된 p형이기 때문에 마이너리티 캐리어라고 불리며, 이는 구멍을 베이스의 주요 캐리어로 만듭니다.PNP 디바이스에서는 유사한 동작이 발생하지만 주요 전류 캐리어로서 구멍이 있다.

컬렉터-베이스 접합에 도달하기 전에 재결합하는 반송파의 비율을 최소화하려면 트랜지스터의 베이스 영역이 반도체의 마이너리티 반송파 수명보다 훨씬 짧은 시간에 트랜지스터 전체에 확산될 수 있을 만큼 충분히 얇아야 합니다.도프 베이스가 가볍게 되어 있기 때문에 재조합률이 낮아집니다.특히 베이스 두께는 캐리어의 확산 길이보다 훨씬 작아야 한다.콜렉터 베이스 접점은 역바이어스이기 때문에 콜렉터에서 베이스로 캐리어 주입이 거의 이루어지지 않지만 이미터에서 베이스로 주입되어 콜렉터 베이스 고갈 영역에 도달하기 위해 확산된 캐리어는 고갈 영역의 전계에 의해 콜렉터 안으로 스위프됩니다.얇은 공유 베이스와 비대칭 콜렉터-이미터 도핑은 바이폴라 트랜지스터를 직렬로 연결된 두 개의 다이오드와 구별하는 것입니다.

전압, 전류 및 충전 제어

컬렉터-이미터 전류는 베이스-이미터 전류(전류 제어) 또는 베이스-이미터 전압(전압 제어)에 의해 제어되는 것으로 볼 수 있습니다.이러한 뷰는 기본-이미터 접점의 전류-전압 관계와 관련이 있으며, 이는 p-n [3]접점(다이오드)의 일반적인 지수 전류-전압 곡선입니다.

컬렉터 전류에 대한 설명은 베이스 [3][4][5]영역 내 마이너 캐리어 농도 구배입니다.(일반 다수 통신사보다 초과 통신사가 훨씬 적은) 저수준 주입으로 인해 (초과 다수 통신사와 소수 통신사가 같은 속도로 흐르는) 양극성 운송 요금이 초과 소수 통신사에 의해 사실상 결정된다.

Gummel-Poon 모델과 같은 트랜지스터 동작의 상세 트랜지스터 모델은 트랜지스터 동작을 보다 [6]정확하게 설명하기 위해 이 전하의 분포를 명확하게 설명합니다.전하 제어 뷰는 광자의 흡수에 의해 베이스 영역의 마이너리티 캐리어가 생성되는 포토 트랜지스터를 쉽게 취급하고, 베이스 영역의 전하에 따라 재결합하는 오프, 즉 회복 시간의 역학을 처리합니다.그러나 기본 전하가 단자에서 볼 수 있는 신호가 아니기 때문에 전류 및 전압 제어 뷰는 일반적으로 회로 설계 및 분석에 사용됩니다.

아날로그 회로 설계에서는 전류 제어 뷰가 거의 선형이기 때문에 때때로 사용됩니다.즉, 컬렉터의 전류는 Ftext})입니다.에 기본 전류를 곱합니다.일부 기본 회로는 베이스 이미터 전압이 대략 일정하고 컬렉터 전류가 베이스 전류의 β배라고 가정하여 설계할 수 있습니다.그러나 생산 BJT 회로를 정확하고 안정적으로 설계하려면 전압 제어(예: Ebers-Moll) 모델이 필요합니다.[3]전압 제어 모델에서는 지수 함수를 고려해야 하지만 Ebers-Moll 모델과 같이 트랜지스터를 트랜스컨덕턴스로 모델링할 수 있도록 선형화할 경우 차동 증폭기와 같은 회로 설계는 다시 대부분 선형 문제가 되므로 전압 제어 뷰가 선호됩니다.지수 I-V 곡선이 작동에 핵심인 선형 회로의 경우 트랜지스터는 일반적으로 트랜지스터가 컬렉터 전류에 비례하는 전압 제어 전류원으로 모델링됩니다.일반적으로 트랜지스터 레벨의 회로 해석은 SPICE 또는 동등한 아날로그 회로 시뮬레이터를 사용하여 이루어지기 때문에 수학적 모델의 복잡성은 설계자에게 큰 관심사가 되지 않지만 특성을 단순화한 뷰로 논리 프로세스에 따라 설계를 작성할 수 있다.

켜기, 끄기 및 저장 지연

바이폴라 트랜지스터, 특히 파워 트랜지스터는 포화 상태가 되면 베이스 스토리지 시간이 길어집니다.베이스 스토리지는 스위칭 애플리케이션에서의 오프 시간을 제한합니다.베이커 클램프는 트랜지스터가 심하게 포화되는 것을 방지하여 베이스에 저장되는 전하량을 줄여 스위칭 시간을 단축할 수 있습니다.

트랜지스터 특성: 알파(α) 및 베타(β)

베이스를 가로질러 콜렉터에 도달할 수 있는 캐리어의 비율은 BJT 효율의 척도입니다.이미터 영역의 심한 도핑과 베이스 영역의 가벼운 도핑은 베이스에서 이미터로 주입되는 구멍보다 더 많은 전자가 이미터에서 베이스로 주입됩니다.얇고 가볍게 도핑된 베이스 영역은 베이스에 주입된 대부분의 마이너 캐리어들이 콜렉터로 확산되어 재결합하지 않는다는 것을 의미합니다.

공통 이미터 전류 이득은 β 또는 h-파라미터FE h로 표시됩니다F.이것은 DC 컬렉터 전류 대 DC 베이스 전류의 대략적인 비율입니다.일반적으로 작은 신호 트랜지스터의 경우 50보다 크지만, 고출력 용도로 설계된 트랜지스터에서는 더 작을 수 있습니다.베이스의 주입 효율과 재조합은 모두 BJT 게인을 감소시킨다.

또 다른 유용한 특성은 공통 기저 전류 이득α이다F.공통 베이스 전류 게인은 포워드 액티브 영역의 이미터에서 컬렉터까지의 전류 게인입니다.이 비율의 값은 보통 0.980 ~0.998입니다베이스 영역을 통과할 때 전하 캐리어가 재결합해 통일성이 떨어진다.

Alpha와 Beta는 다음 ID로 관련지어집니다.

베타는 바이폴라 트랜지스터의 성능을 설명하기에 편리한 수치이지만 소자의 기본적인 물리적 특성은 아닙니다.바이폴라 트랜지스터는 전압 제어 소자로 간주할 수 있습니다(기본적으로 컬렉터 전류는 베이스-에미터 전압에 의해 제어됩니다). 베이스 전류는 결함으로 간주될 수 있으며 베이스-에미터 접합 및 베이스 재결합의 특성에 의해 제어됩니다).많은 설계에서 베타는 기본 전류가 회로에 거의 영향을 미치지 않도록 충분히 높다고 가정합니다.일부 회로(일반적으로 스위칭 회로)에서는 특정 장치가 가질 수 있는 가장 낮은 베타 값이라도 필요한 컬렉터 전류가 흐를 수 있도록 충분한 기본 전류가 공급됩니다.

구조.

BJT는 이미터 영역, 베이스 영역 및 컬렉터 영역의 세 가지 다른 도프된 반도체 영역으로 구성됩니다.이들 영역은 PNP 트랜지스터에서는 각각 p형, n형 및 p형이며 NPN 트랜지스터에서는 n형, p형 및 n형입니다.각 반도체 영역은 이미터(E), 베이스(B) 및 콜렉터(C)라는 적절한 라벨이 붙은 단자에 접속되어 있다.

베이스는 이미터와 컬렉터 사이에 물리적으로 배치되어 있으며 가볍게 도핑된 고저항 재료로 제작됩니다.컬렉터는 이미터 영역을 둘러싸고 있기 때문에 베이스 영역에 주입된 전자가 수집되지 않고서는 빠져나가는 것이 거의 불가능하므로 결과적으로 α의 값이 단일성에 매우 가깝기 때문에 트랜지스터에 큰 β를 제공합니다.BJT의 단면도는 콜렉터-베이스 접합부가 이미터-베이스 접합부보다 훨씬 큰 면적을 가지고 있음을 나타냅니다.

바이폴라 접합 트랜지스터는 다른 트랜지스터와 달리 일반적으로 대칭 장치가 아닙니다.즉, 콜렉터와 이미터를 교환하면 트랜지스터가 순방향 액티브모드에서 벗어나 역방향 모드로 동작하기 시작합니다.트랜지스터의 내부 구조는 보통 전방 모드 동작에 최적화되어 있기 때문에 콜렉터와 이미터를 교환하면 역방향 동작의 α와 β의 값이 전방 동작의 값보다 훨씬 작아집니다.대부분 역방향 모드의 α는 0.5보다 낮아집니다.대칭의 결여는 주로 이미터와 컬렉터의 도핑 비율에 기인합니다.이미터는 심하게 도핑되고 컬렉터는 가볍게 도핑되므로 컬렉터와 베이스 접합부가 고장나기 전에 큰 역바이어스 전압을 인가할 수 있습니다.콜렉터-베이스 접합부는 정상 작동 시 역편향됩니다.이미터가 심하게 도핑되는 이유는 이미터 주입 효율을 높이기 위해서입니다.즉, 이미터에 의해 주입된 캐리어와 베이스에 의해 주입된 캐리어의 비율입니다.고전류 게인의 경우, 이미터 베이스 접합부에 주입된 대부분의 캐리어가 이미터로부터 와야 합니다.

CMOS 프로세스에서 사용되는 저성능 "가로형" 바이폴라 트랜지스터는 때때로 대칭으로 설계됩니다. 즉, 전진 및 후진 작동 간에 차이가 없습니다.

베이스 이미터 단자에 인가되는 전압의 작은 변화는 이미터와 컬렉터 사이의 전류를 크게 변화시킵니다.이 효과는 입력 전압 또는 전류를 증폭하는 데 사용할 수 있습니다.BJT는 전압 제어 전류원으로 간주할 수 있지만 베이스의 임피던스가 낮기 때문에 전류 제어 전류원 또는 전류 증폭기로 보다 간단하게 특징지어집니다.

초기 트랜지스터는 게르마늄으로 만들어졌지만 대부분의 현대 BJT는 실리콘으로 만들어졌다.현재는 특히 매우 빠른 애플리케이션(아래 HBT 참조)을 위해 갈륨 비소로도 상당한 소수가 제조되고 있습니다.

헤테로 접합 바이폴라 트랜지스터(HBT)는 최대 수백 GHz의 매우 높은 주파수의 신호를 처리할 수 있는 BJT를 개량한 것입니다.이는 현대의 초고속 회선(주로 RF 시스템)[7][8]에서 흔히 볼 수 있습니다.

일반적으로 사용되는 두 가지 HBT는 실리콘-게르마늄과 알루미늄 비소화 갈륨이지만, HBT 구조에는 다양한 반도체가 사용될 수 있습니다.HBT 구조는 보통 MOCVD 및 MBE와 같은 에피택시 기술로 성장합니다.

동작 지역

| 분기점 유형 | 응용의 전압 | 접합 바이어스 | 모드 | |

|---|---|---|---|---|

| B~E | B~C | |||

| NPN | E < B < C | 앞으로 | 리버스 | 전진-액티브 |

| E < B > C | 앞으로 | 앞으로 | 포화도 | |

| E > B < C | 리버스 | 리버스 | 컷오프 | |

| E > B > C | 리버스 | 앞으로 | 리버스 액티브 | |

| PNP | E < B < C | 리버스 | 앞으로 | 리버스 액티브 |

| E < B > C | 리버스 | 리버스 | 컷오프 | |

| E > B < C | 앞으로 | 앞으로 | 포화도 | |

| E > B > C | 앞으로 | 리버스 | 전진-액티브 | |

바이폴라 트랜지스터에는 BJT 정션 바이어스에 의해 정의된 네 가지 작동 영역이 있습니다.

- 포워드 액티브(또는 단순히 액티브)

- 베이스-이미터 접합은 전방 바이어스이고 베이스-콜렉터 접합은 후방 바이어스입니다.대부분의 바이폴라 트랜지스터는 전진-액티브 모드에서 가장 큰 공통 이미터 전류 게인 β를 제공하도록F 설계되었습니다.이 경우 컬렉터-이미터 전류는 베이스 전류에 거의 비례하지만 작은 베이스 전류 변동의 경우 몇 배나 커집니다.

- 역액티브(또는 역액티브 또는 반전)

- 포워드 액티브 영역의 바이어스 조건을 반전시킴으로써 바이폴라 트랜지스터가 리버스 액티브 모드가 된다.이 모드에서는 이미터 영역과 수집기 영역이 역할을 바꿉니다.대부분의 BJT는 전진-액티브 모드에서 전류 게인을 최대화하도록 설계되어 있기 때문에 반전 모드의 β는F 몇 배(일반 게르마늄 트랜지스터의 경우 2~3배) 작습니다.이 트랜지스터 모드는 거의 사용되지 않으며, 일반적으로 페일 세이프 조건 및 일부 유형의 바이폴라 로직에서만 고려됩니다.베이스에 대한 역바이어스 파괴전압은 이 영역에서 훨씬 낮을 수 있다.

- 포화도

- 양쪽 접점이 전방으로 바이어스 되어 있는 경우, BJT는 포화 모드가 되어, 이미터에서 콜렉터로 고전류 전도를 용이하게 합니다(NPN의 경우는 음전하 캐리어가 이미터에서 콜렉터로 흐릅니다).이 모드는 논리적인 "ON" 또는 닫힌 스위치에 해당합니다.

- 컷오프

- 컷오프에서는 포화도와 반대되는 바이어스 조건(두 접합부 모두 역편향)이 존재합니다.논리적인 "OFF" 또는 열린 스위치에 해당하는 전류는 매우 적습니다.

- 눈사태 파괴 지역

동작 모드는 인가 전압의 관점에서 설명할 수 있습니다(이 설명은 NPN 트랜지스터에 적용되며 PNP 트랜지스터의 경우 극성이 반전됩니다).

- 전진-액티브

- 베이스가 이미터보다 높고 컬렉터가 베이스보다 높음(이 모드에서는 컬렉터 전류가 베이스 전류에 F {\ _{\text 비례함)

- 포화도

- 베이스는 이미터보다 높지만 컬렉터는 베이스보다 높지 않습니다.

- 컷오프

- 베이스는 이미터보다 낮지만 컬렉터는 베이스보다 높습니다.즉, 트랜지스터가 콜렉터에서 이미터로 재래식 전류를 통과시키지 않습니다.

- 리버스 액티브

- 베이스가 이미터보다 낮고 컬렉터가 베이스보다 낮음: 역방향 재래식 전류가 트랜지스터를 통과합니다.

접합 바이어싱 측면에서: (역 바이어스 베이스-콜렉터 접합은bc NPN의 경우 V < 0, PNP의 경우 반대)

이러한 영역은 충분히 큰 인가 전압에 대해 잘 정의되어 있지만, 작은(수백 밀리볼트 미만) 바이어스에는 다소 오버랩됩니다.예를 들어 디지털로직에서 풀다운스위치로 사용되는 NPN BJT의 일반적인 접지 이미터 구성에서는 베이스전압이 접지 아래로 내려가지 않기 때문에 "off" 상태에는 역바이어스 접점이 포함되지 않습니다.그러나 포워드 바이어스는 기본적으로 전류가 흐르지 않을 정도로 충분히 제로에 가깝기 때문에 포워드 액티브한 이 끝입니다.gion은 컷오프 영역으로 간주할 수 있습니다.

회로의 액티브 모드 트랜지스터

이 다이어그램은 두 개의 전압 소스에 연결된 NPN 트랜지스터의 개략도를 보여 줍니다.(전류의 방향이 반대이고 전압이 인가된 PNP 트랜지스터에도 동일한 설명이 적용됩니다.)이 인가전압에 의해 하부 P-N 접합부가 전방 바이어스가 되어 이미터에서 베이스로 전자가 흐를 수 있게 됩니다.활성 모드에서는 베이스와 콜렉터 사이에 존재하는 전계(V에 의해CE 발생)로 인해 이들 전자의 대부분이 콜렉터 상단의 P-N 접합부를 통과하여 콜렉터 전류C I를 형성합니다.나머지 전자는 베이스의 주요 캐리어인 구멍과 재결합하여 베이스 연결을 통해 전류를 만들어 베이스 전류 I를B 형성합니다.다이어그램에 표시된 것처럼 이미터 전류 I는E 다른 단자 전류의 합계인 총 트랜지스터 전류입니다(즉E, I = IB + IC).

다이어그램에서 화살표는 재래식 전류의 방향을 가리키며, 전자는 음의 전하를 전달하기 때문에 전자의 흐름은 화살표의 반대 방향입니다.액티브 모드에서는 컬렉터 전류의 베이스 전류에 대한 비율을 DC 전류 게인이라고 합니다.이 이득은 보통 100 이상이지만 견고한 회로 설계는 정확한 값에 의존하지 않습니다(예를 들어 op-amp 참조).DC 신호의 이 게인 값은 FEtext})라고 불립니다.FE 작은 신호에 대한 이 게인 은 hfe(\라고 .즉, 전류의 작은 변화가 발생하고 새로운 상태가 정상 에 도달할 때까지 충분한 시간이 경과한 경우 는 콜렉터의 전류에 대한 변화 비율입니다.e 베이스 전류의 변화.β(\는 text}) 에 사용됩니다.FE 스타일 [9]입니다.

이미터 전류는 BE와 관련되어 있습니다.BE입니다.실온에서 V의 (\BE은(는) 이미터 전류를 약 60mV 증가시킵니다.베이스 전류는 컬렉터 전류와 이미터 전류에 거의 비례하기 때문에 같은 방식으로 변화합니다.

역사

양극성 점 접촉 트랜지스터는 1947년 12월[10] 벨 전화 연구소에서 윌리엄 쇼클리의 지시로 존 바딘과 월터 브래튼에 의해 발명되었다.1948년 [11]쇼클리에 의해 발명된 바이폴라 접합 트랜지스터(BJT)로 알려진 접합 버전은 30년 동안 이산 및 집적회로 설계에서 선택된 장치였습니다.오늘날 BJT의 사용은 디지털 집적회로 설계에서 CMOS 기술을 선호하지 않고 있다.그러나 CMOS IC에 내재된 부수적인 저성능 BJT는 종종 밴드갭 전압 기준, 실리콘 밴드갭 온도 센서 및 정전 방전을 처리하기 위해 사용됩니다.

게르마늄 트랜지스터

게르마늄 트랜지스터는 1950년대와 1960년대에 더 흔했지만 열적 폭주 현상을 보이는 경향이 더 큽니다.

초기 제조 기술

바이폴라 트랜지스터를 제조하는 다양한 방법이 [12]개발되었습니다.

- 포인트 접점 트랜지스터 – 사상 최초로 제작된 트랜지스터(1947년 12월), 바이폴라 트랜지스터. 고비용과 노이즈로 인해 상업적으로 사용이 제한되었습니다.

- 테트로이드 포인트 컨택트랜지스터– 2개의 이미터가 있는 포인트 컨택트랜지스터그것은 1950년대 중반에 구식이 되었다.

- 접합 트랜지스터

- 성장 접합 트랜지스터 – 최초의 바이폴라 접합 트랜지스터가 [13]제작되었습니다.1948년 [14]6월 23일 벨 연구소에서 윌리엄 쇼클리에 의해 발명되었습니다.1948년 6월 26일 특허 출원

- 합금 접합 트랜지스터 – 이미터 및 컬렉터 합금 비드가 베이스에 융합됩니다.1951년 제너럴 일렉트릭과[15] RCA에서 개발.

- 테트로이드 트랜지스터 – 베이스에 2개의 연결부가 있는 성장 접합 트랜지스터[17] 또는 합금 접합[18] 트랜지스터의 고속 변형입니다.

- 표면 장벽 트랜지스터 – 고속 금속 장벽 접합 트랜지스터.1953년 [20]필코에서[19] 개발.

- 드리프트 필드 트랜지스터 – 고속 양극 접합 트랜지스터.1953년 독일 우체국 중앙통신기술국의 헤르베르트 크로이머에[21][22] 의해 발명되었습니다.

- Spacistor – 약 1957년.

- 확산 트랜지스터 – 최신형 양극 접합 트랜지스터.시제품은[23] 1954년 벨 연구소에서 개발되었습니다.

- 에피택셜 트랜지스터[25] – 기상 증착을 사용하여 만들어진 양극 접합 트랜지스터.에피택시 참조.도핑 수준과 구배를 매우 정밀하게 제어할 수 있습니다.

이론과 모델링

BJT는 마이너리티 캐리어가 통과할 수 있는 공통 영역을 공유하는 2개의 다이오드(P–N 접합부)로 간주할 수 있습니다.PNP BJT는 N형 음극 영역을 공유하는 2개의 다이오드처럼 기능하며 NPN은 P형 양극 영역을 공유하는 2개의 다이오드처럼 기능합니다.마이너 캐리어가 와이어를 통해 한 P-N 접점에서 다른 P-N 접점으로 이동할 수 없기 때문에 두 개의 다이오드를 와이어로 연결하면 BJT가 생성되지 않습니다.

두 유형의 BJT는 모두 베이스에 입력되는 소량의 전류로 컬렉터의 증폭 출력을 제어함으로써 작동합니다.그 결과 BJT는 기본 입력에 의해 제어되는 양호한 스위치를 만듭니다.또한 BJT는 약한 입력 신호를 원래 강도의 약 100배까지 증가시킬 수 있기 때문에 좋은 앰프를 만듭니다.BJT 네트워크는 다양한 용도로 강력한 증폭기를 만드는 데 사용됩니다.

다음 설명에서는 NPN BJT에 초점을 맞춥니다.액티브 모드라고 불리는 모드에서는 베이스 이미터 BE(\V_text{\} 및 콜렉터 베이스 CBCB은(는) 양수이며, 이미터-베이스 접합을 전진 바이어싱하고 콜렉터-베이스 접합을 역바이어싱합니다.이 모드에서 전자는 순방향 바이어스 n형 이미터 영역에서 p형 베이스로 주입되며, 여기서 소수 캐리어로서 역방향 바이어스 n형 컬렉터로 확산되어 역방향 바이어스 콜렉터-베이스 접합부의 전계에 의해 스위프된다.

정방향 및 역방향 바이어스의 그림은 반도체 다이오드를 참조하십시오.

대형 신호 모델

1954년 Jewel James Ebers와 John L. Moll은 트랜지스터 [26]전류의 수학적 모델을 발표했습니다.

Evers-Moll 모델

액티브 모드의 DC 이미터 및 컬렉터 전류는 Ebers-Moll 모델에 대한 근사치로 잘 모델링됩니다.

기본 내부 전류는 주로 확산에 의해 발생합니다(픽의 법칙 참조).

어디에

- 는 /q {300K µ 상온에서 약 26mV)입니다.

- 는 이미터 전류입니다.

- 은(는) 수집기 전류입니다.

- 은 공통 베이스 순방향 단락 전류 게인(0.98~0.998)입니다.

- 은 베이스-이미터 다이오드의 역포화 전류(10~10암페어−15−12)입니다.

- 은 베이스 이미터 전압입니다.

- 은 p형 베이스에 있는 전자의 확산 상수입니다.

- W는 베이스 폭입니다.

α(\displaystyle 및 β 파라미터(\는 앞에서 설명한 바와 같습니다.가 모델에 포함될 수 있습니다.

모든 작동 영역에서 세 가지 전류를 설명하는 데 사용되는 근사치 Ebers-Moll 방정식은 아래에 나와 있습니다.이 방정식은 바이폴라 접합 트랜지스터의 [28]트랜스포트 모델에 기초하고 있습니다.

어디에

- 은(는) 수집기 전류입니다.

- 이(가) 기본 전류입니다.

- 는 이미터 전류입니다.

- 은 순방향 공통 이미터 전류 게인(20 ~500)입니다.

- R은(는) 역공통 이미터 전류 게인(0~20)입니다.

- 는 역포화−15 전류(10~10암페어−12)입니다.

- 는 열전압(300K µ 상온에서 약 26mV)입니다.

- 은 베이스 이미터 전압입니다.

- 은 베이스-콜렉터 전압입니다.

베이스폭 변조

콜렉터 베이스 전압( CB CE - { BE는 다양하며, 수집기 기반 고갈 영역의 크기는 합니다.예를 들어 콜렉터 베이스 전압이 증가하면 콜렉터 베이스 접점 전체에서 역바이어스가 커져 콜렉터 베이스 고갈 영역 폭이 증가하고 베이스 폭이 감소합니다.이러한 기저 폭의 변화는 종종 발견자인 제임스 M. 얼리(James M. Early)의 이름을 따서 얼리 효과(Early effect)라고 불립니다.

베이스 폭을 좁히면 다음 두 가지 결과가 발생합니다.

- "더 작은" 베이스 영역 내에서는 재결합 가능성이 낮다.

- 전하 구배는 베이스 전체에 걸쳐 증가하며, 결과적으로 이미터 접합부에 주입된 마이너 캐리어 전류가 증가한다.

두 요인 모두 컬렉터 기본 전압의 증가에 따라 트랜지스터의 컬렉터 또는 "출력" 전류를 증가시킵니다.

순방향 활성 영역에서는 Early Effect에 의해 수집기 전류가 변경됩니다( C\ i _ { \ { \ text 。 및 포워드 공통 이미터 전류 게인(F {\ _text})에 의해 [citation needed]지정됩니다.

여기서:

- 은 컬렉터-이미터 전압입니다.

- 은(는) 초기 전압(15~150V)입니다.

- 은(는 V {\text{\text}일 때 전송 공통 이미터 전류 게인입니다. = 0 V

- o {\는 출력 임피던스입니다.

- 은(는) 수집기 전류입니다.

펀치 스루

베이스 컬렉터 전압이 특정(디바이스 고유) 값에 도달하면 베이스 컬렉터 고갈 영역 경계는 베이스 이미터 고갈 영역 경계에 도달합니다.이 상태에서는 트랜지스터에 사실상 베이스가 없습니다.따라서 디바이스는 이 상태에 있으면 모든 게인을 잃습니다.

Gummel-Poon 충전 제어 모델

Gummel-Poon 모델은[29] BJT 다이내믹스의 상세한 전하 제어 모델이며, 트랜지스터 다이내믹스를 일반적으로 단자 기반 [30]모델보다 더 상세하게 설명하기 위해 채택 및 정교하게 설명되었습니다.이 모델에는 β - 트랜지스터의 직류 레벨에 대한 의존성도 포함됩니다.이것은 Ebers-Moll [31]모델에서는 전류에 의존하지 않는 것으로 간주됩니다.

소형 신호 모델

하이브리드 PI 모델

하이브리드 파이 모델은 바이폴라 접합 및 전계 효과 트랜지스터의 작은 신호 및 AC 동작을 분석하는 데 사용되는 일반적인 회로 모델입니다.1969년에 L.J. Giacoletto에 의해 소개되었기 때문에 때때로 Giacoletto 모델이라고도 불린다.이 모델은 저주파 회로에 대해 상당히 정확할 수 있으며 적절한 전극 간 캐패시턴스 및 기타 기생 소자를 추가하여 고주파 회로에 쉽게 적응할 수 있습니다.

h-모수 모형

BJT 회로 분석에 일반적으로 사용되는 또 다른 모델은 하이브리드 등가 모델이라고도 하는 h-파라미터 모델입니다. 하이브리드 등가 모델 및 y-파라미터 2포트와 밀접하게 관련되어 있지만 입력 및 출력 전압이 아닌 독립 변수로 사용됩니다.이 2포트 네트워크는 회로 동작을 쉽게 분석할 수 있으므로 BJT에 특히 적합합니다.또한 보다 정확한 모델을 개발하는 데 사용할 수 있습니다.그림과 같이 모델에서 x라는 용어는 사용된 토폴로지에 따라 다른 BJT 리드를 나타냅니다.Common-Emiter 모드의 경우 다음과 같이 다양한 기호가 특정 값을 취합니다.

- 터미널 1, 베이스

- 터미널 2, 콜렉터

- 터미널 3(공통), 이미터, x를 e로 지정

- ii, 베이스 전류(ib)

- io, 수집기 전류(ic)

- Vin, 베이스 투 이미터 전압(VBE)

- Vo, Collector-to-Emiter 전압(VCE)

h 파라미터는 다음과 같이 지정됩니다.

- hix = h(공통 이미터ie 구성의 경우), 트랜지스터의 입력 임피던스(기본 저항pi r에 해당).

- hrx = hre(역방향 전달 관계), 트랜지스터(입력)의 의존성을 나타냅니다.(출력BCE) V 값에 대한 I-VBE 곡선.이것은 보통 매우 작으며 DC에서 무시되는 경우가 많습니다(제로로 추정).

- hfx = hfe, 트랜지스터의 "전류" 전류 게인(때로는 h로 표기됨21).이 매개 변수와 소문자"fe"을 의미하는 것 작은 신호(AC)증가, 또는 더 자주"FE"(지정한 대로 hFE)은" 큰 신호"또는 DCcurrent-gain(βDC 또는 종종 단순히 β)을 의미하기 위해 대문자로, 하나이다 데이터 시트까지의 주요 매개 변수의 열, 그리고 전형적인 컬렉터 전류와 전압이나 수집가 입방의 함수로 음모를 꾸밀 수 있다.rrent. 아래를 참조해 주세요.

- hox = 1/hoe, 트랜지스터의 출력 임피던스.파라미터oe h는 보통 바이폴라 트랜지스터의 출력 어드미턴스에 해당하며 이를 임피던스로 변환하려면 반전해야 합니다.

그림과 같이 h-모수에는 소문자 첨자가 있으므로 AC 조건 또는 분석을 나타냅니다.DC 조건의 경우 대문자로 지정합니다.CE 토폴로지에서는 회로 분석을 더욱 단순화하는 대략적인h 파라미터 모델이 일반적으로 사용됩니다.이 경우 hoe 및 hre 파라미터는 무시됩니다(즉, 각각 무한대와 0으로 설정됩니다).표시된 h-파라미터 모델은 저주파 소신호 분석에 적합합니다.고주파 분석의 경우 고주파에서 중요한 전극 간 캐패시턴스를 추가해야 합니다.

h의FE 어원

h는 하이브리드 등가회로 모델(위 참조)에서 원점으로부터 명명된 일련의 파라미터인 h-파라미터입니다.모든 h 파라미터와 마찬가지로 "h" 뒤에 오는 문자의 소문자 또는 대문자 선택은 중요합니다. 소문자는 "작은 신호" 파라미터, 즉 특정 관계의 기울기를 나타냅니다. 대문자는 "큰 신호" 또는 DC 값, 전압 또는 전류의 비율을 나타냅니다.매우 자주 사용되는FE h의 경우:

- F는 전류 게인이라고도 불리는 순방향 전류 증폭에서 나옵니다.

- E는, 공통의 이미터(CE) 구성으로 동작하는 트랜지스터를 가리킵니다.

따라서FE h(또는 hFE)는 (총, DC) 컬렉터 전류를 기본 전류로 나눈 것을 의미하며 치수가 없습니다.이 파라미터는 수집기 전류에 따라 다소 변화하지만 종종 상수로 근사됩니다.일반적으로 일반적인 수집기 전류 및 전압으로 지정되거나 수집기 전류의 함수로 그래프로 표시됩니다.

첨자에 대문자가 사용되지 않은 경우(즉, h라고 쓰여fe 있는 경우) 파라미터는 작은 신호(AC) 전류 게인을 나타냅니다. 즉, 특정 포인트의 수집기 전류 대 기준 전류 그래프의 기울기는 테스트 주파수가 높지 않은 한 종종 hFE 값에 가깝습니다.

산업 모델

이 섹션은 확장해야 합니다.추가하시면 됩니다. (2015년 1월) |

Gummel-Poon SPICE 모델이 자주 사용되지만 몇 가지 제한이 있습니다.예를 들어 베이스-이미터 다이오드의 역내역은 SGP(SPICE Gummel-Poon) 모델에서는 포착되지 않으며 열효과(자기 가열)나 준포화도 아닙니다.[32]이러한 문제는 특정 응용 사례(Mextram, HICUM, Modella)에 초점을 맞추거나 범용 용도(VBIC)[33][34][35][36]용으로 설계된 다양한 고급 모델에서 해결되었습니다.

적용들

BJT는 사용 가능한 BJT 유형이 매우 광범위하고 MOSFET에 비해 높은 트랜스컨덕턴스와 출력 저항으로 인해 이산 회로 설계와 같은 일부 애플리케이션에서 탁월한 성능을 발휘합니다.

BJT는 요구가 까다로운 아날로그 회로, 특히 무선 시스템용 무선 주파수 회로와 같은 매우 고주파 애플리케이션에 적합합니다.

고속 디지털 로직

Emitter-Coupled Logic(ECL; 이미터 결합 논리)에서는 BJT가 사용됩니다.

바이폴라 트랜지스터는 웨이퍼 제작의 BiCMOS 프로세스를 사용하여 집적회로에서 MOSFET와 결합할 수 있으며, 두 유형의 트랜지스터의 적용 강도를 이용하는 회로를 만들 수 있습니다.

앰프

트랜지스터 매개 변수 α 및 β는 BJT의 전류 게인을 특징짓습니다.BJT를 전자 증폭기의 구성 요소로 사용할 수 있게 된 것은 바로 이 이득입니다.세 가지 주요 BJT 앰프 토폴로지는 다음과 같습니다.

온도 센서

전방 바이어스 베이스-이미터 접합 전압의 알려진 온도 및 전류 의존성 때문에 BJT를 사용하여 알려진 비율로 [37]서로 다른 두 바이어스 전류에서 두 전압을 빼서 온도를 측정할 수 있습니다.

로그 변환기

베이스 이미터 전압은 베이스 이미터 전류와 콜렉터 이미터 전류의 대수에 따라 변화하기 때문에 BJT를 사용하여 로그 및 반로그를 계산할 수도 있습니다.다이오드는 이러한 비선형 기능을 수행할 수도 있지만 트랜지스터는 더 많은 회로 유연성을 제공합니다.

눈사태 펄스 발생기

트랜지스터는 콜렉터 대 베이스 파괴 전압보다 낮은 콜렉터 대 이미터 파괴 전압으로 의도적으로 만들 수 있다.이미터 베이스 접점이 역바이어스 되어 있는 경우, 콜렉터 이미터 전압은 고장 직전의 전압으로 유지될 수 있습니다.베이스전압이 상승하고 전류가 흐르면 눈사태가 일어나 컬렉터 베이스공핍영역의 충격이온화가 급속히 캐리어에 의해 베이스에 홍수를 일으켜 트랜지스터를 완전히 온으로 한다.펄스가 충분히 짧고 드물어서 장치가 손상되지 않는 한 이 효과를 사용하여 매우 날카로운 하강 에지를 만들 수 있습니다.

이 응용을 위해 특수 눈사태 트랜지스터 소자가 만들어집니다.

취약성

트랜지스터가 이온화 방사선에 노출되면 방사선 손상이 발생합니다.방사선은 재조합의 중심 역할을 하는 기저부위 '결함'의 축적을 일으킨다.그 결과 마이너 캐리어 수명이 감소하면 트랜지스터 이득이 점차 손실됩니다.

트랜지스터에는 전력 정격(본질적으로 자기 발열에 의해 제한됨), 최대 수집기 및 베이스 전류(연속/DC 정격 및 피크 모두) 및 고장 전압 정격을 포함한 "최대 정격"이 있으며, 이 정격을 초과하면 장치가 고장 나거나 최소한 성능이 저하될 수 있습니다.

전원 BJT는 디바이스의 통상적인 파괴정격과 더불어 2차 파괴라고 불리는 고장모드에 따릅니다.이 모드에서는 실리콘 다이 내의 과도한 전류 및 통상적인 결함이 디바이스 내의 실리콘 일부가 다른 것보다 불균형적으로 뜨거워집니다.도프된 실리콘의 전기 저항률은 다른 반도체와 마찬가지로 음의 온도 계수를 가지며, 이는 더 높은 온도에서 더 많은 전류를 전도한다는 것을 의미합니다.따라서 다이의 가장 뜨거운 부분이 가장 전류를 전도하여 전도율이 증가하게 되고, 이는 소자가 내부에서 고장날 때까지 다시 점진적으로 뜨거워지게 됩니다.2차 고장과 관련된 서멀 런웨이 프로세스는 한번 트리거되면 거의 즉시 발생하며 트랜지스터 패키지가 치명적인 손상을 입을 수 있습니다.

이미터 베이스 접점이 아발란치 또는 제너 모드로 역바이어스 되어 짧은 시간 동안 전하 흐름이 되면 이미터가 컬렉터보다 작고 상당한 전력을 소산할 수 없기 때문에 BJT의 전류 이득이 영구적으로 저하될 수 있습니다.이것은 저전압 디바이스에서 일반적인 ESD 장애 메커니즘입니다.

「 」를 참조해 주세요.

메모들

레퍼런스

- ^ Ashcroft and Mermin (1976). Solid State Physics (1st ed.). Holt, Rinehart, and Winston. pp. 299–302. ISBN 978-0030839931.

- ^ Chenming Calvin Hu (2010). Modern Semiconductor Devices for Integrated Circuits.

- ^ a b c Paul Horowitz and Winfield Hill (1989). The Art of Electronics (2nd ed.). Cambridge University Press. ISBN 978-0-521-37095-0.

- ^ Juin Jei Liou and Jiann S. Yuan (1998). Semiconductor Device Physics and Simulation. Springer. ISBN 978-0-306-45724-1.

- ^ General Electric (1962). Transistor Manual (6th ed.). p. 12. Bibcode:1964trma.book.....C. "트랜지스터 분석에 공간 전하 중립성의 원리를 사용하면 집전 전류가 베이스 영역의 양의 전하(홀 농도)에 의해 제어되는 것이 명백합니다."트랜지스터를 더 높은 주파수로 사용하는 경우, 기본적인 제한은 캐리어가 기본 영역 전체에 확산되는 데 걸리는 시간입니다..."(4번째 및 5번째 에디션과 동일).

- ^ Paolo Antognetti and Giuseppe Massobrio (1993). Semiconductor Device Modeling with Spice. McGraw–Hill Professional. ISBN 978-0-07-134955-0.

- ^ Morgan, D.V.; Williams, Robin H., eds. (1991). Physics and Technology of Heterojunction Devices. London: Institution of Electrical Engineers (Peter Peregrinus Ltd.). ISBN 978-0-86341-204-2.

- ^ Peter Ashburn (2003). SiGe Heterojunction Bipolar Transistors. New York: Wiley. Chapter 10. ISBN 978-0-470-84838-8.

- ^ Paul Horowitz and Winfield Hill (1989). The Art of Electronics (2nd ed.). Cambridge University Press. pp. 62–66. ISBN 978-0-521-37095-0.

- ^ "1947: Invention of the Point-Contact Transistor - The Silicon Engine - Computer History Museum". Retrieved August 10, 2016.

- ^ "1948: Conception of the Junction Transistor - The Silicon Engine - Computer History Museum". Retrieved August 10, 2016.

- ^ 세 번째 도입 사례– 솔리드 스테이트 어드밴스 2007년 9월 27일 Wayback Machine에서 아카이브(PDF)

- ^ "Transistor Museum, Historic Transistor Photo Gallery, Bell Labs Type M1752".

- ^ Morris, Peter Robin (1990). "4.2". A History of the World Semiconductor Industry. IEE History of Technology Series 12. London: Peter Peregrinus Ltd. p. 29. ISBN 978-0-86341-227-1.

- ^ "Transistor Museum Photo Gallery RCA TA153". Retrieved August 10, 2016.

- ^ High Speed Switching Transistor Handbook (2nd ed.). Motorola. 1963. p. 17.[1]

- ^ 트랜지스터 박물관, 트랜지스터 역사 사진 갤러리, 웨스턴 일렉트릭 3N22.

- ^ Maupin, J.T. (1957). "The tetrode power transistor". IRE Transactions on Electron Devices. 4 (1): 1–5. Bibcode:1957ITED....4....1M. doi:10.1109/T-ED.1957.14192. S2CID 51668235.

- ^ "Transistor Museum Photo Gallery Philco A01 Germanium Surface Barrier Transistor". Retrieved August 10, 2016.

- ^ "Transistor Museum Photo Gallery Germanium Surface Barrier Transistor". Retrieved August 10, 2016.

- ^ Brar, B.; Sullivan, G.J.; Asbeck, P.M. (2001). "Herb's bipolar transistors". IEEE Transactions on Electron Devices. 48 (11): 2473–2476. Bibcode:2001ITED...48.2473B. doi:10.1109/16.960370.

- ^ Bullis, W.M.; Runyan, W.R. (1967). "Influence of mobility and lifetime variations on drift-field effects in silicon-junction devices". IEEE Transactions on Electron Devices. 14 (2): 75–81. Bibcode:1967ITED...14...75B. doi:10.1109/T-ED.1967.15902.

- ^ "Transistor Museum Photo Gallery Bell Labs Prototype Diffused Base Germanium Silicon Transistor". Retrieved August 10, 2016.

- ^ "Transistor Museum Photo Gallery Fairchild 2N1613 Early Silicon Planar Transistor". Retrieved August 10, 2016.

- ^ "1960: Epitaxial Deposition Process Enhances Transistor Performance – The Silicon Engine – Computer History Museum". Retrieved August 10, 2016.

- ^ Ebers, J.; Moll, J. (1954). "Large-Signal Behavior of Junction Transistors". Proceedings of the IRE. 42 (12): 1761–1772. doi:10.1109/jrproc.1954.274797. S2CID 51672011.

- ^ Adel S. Sedra and Kenneth C. Smith (1987). Microelectronic Circuits, second ed. p. 903. ISBN 978-0-03-007328-1.

- ^ A.S. Sedra and K.C. Smith (2004). Microelectronic Circuits (5th ed.). New York: Oxford. Eqs. 4.103–4.110, p. 305. ISBN 978-0-19-514251-8.

- ^ Gummel, H. K.; Poon, H. C. (1970). "An Integral Charge Control Model of Bipolar Transistors". Bell System Technical Journal. 49 (5): 827–852. doi:10.1002/j.1538-7305.1970.tb01803.x.

- ^ "Bipolar Junction Transistors". Retrieved August 10, 2016.

- ^ A.S. Sedra and K.C. Smith (2004). Microelectronic Circuits (5th ed.). New York: Oxford. p. 509. ISBN 978-0-19-514251-8.

- ^ "VBIC Description and Derivation Details" (PDF). Designer’s Guide.

{{cite web}}: CS1 maint :url-status (링크) - ^ "Archived copy" (PDF). Archived from the original (PDF) on 2016-03-05. Retrieved 2015-01-15.

{{cite web}}: CS1 maint: 제목으로 아카이브된 복사(링크) - ^ Gennady Gildenblat, ed. (2010). Compact Modeling: Principles, Techniques and Applications. Springer Science & Business Media. Part II: Compact Models of Bipolar Junction Transistors, pp. 167–267 cover Mextram and HiCuM in-depth. ISBN 978-90-481-8614-3.

- ^ Michael Schröter (2010). Compact Hierarchical Bipolar Transistor Modeling with Hicum. World Scientific. ISBN 978-981-4273-21-3.

- ^ "Compact Models for Bipolar Transistors, Berkner (Archived copy)" (PDF). Archived from the original (PDF) on 2015-01-16. Retrieved 2015-01-16.

- ^ "IC Temperature Sensors Find the Hot Spots - Application Note - Maxim". maxim-ic.com. February 21, 2002. Retrieved August 10, 2016.

기본 전류를 곱합니다.일부 기본 회로는 베이스 이미터 전압이 대략 일정하고 컬렉터 전류가 베이스 전류의 β배라고 가정하여 설계할 수 있습니다.그러나 생산 BJT 회로를 정확하고 안정적으로 설계하려면 전압 제어(예

기본 전류를 곱합니다.일부 기본 회로는 베이스 이미터 전압이 대략 일정하고 컬렉터 전류가 베이스 전류의 β배라고 가정하여 설계할 수 있습니다.그러나 생산 BJT 회로를 정확하고 안정적으로 설계하려면 전압 제어(예

.

.

(는) 양수이며, 이미터-베이스 접합을 전진 바이어싱하고 콜렉터-베이스 접합을 역바이어싱합니다.이 모드에서 전자는 순방향 바이어스 n형 이미터 영역에서 p형 베이스로 주입되며, 여기서 소수 캐리어로서 역방향 바이어스 n형 컬렉터로 확산되어 역방향 바이어스 콜렉터-베이스 접합부의 전계에 의해 스위프된다.

(는) 양수이며, 이미터-베이스 접합을 전진 바이어싱하고 콜렉터-베이스 접합을 역바이어싱합니다.이 모드에서 전자는 순방향 바이어스 n형 이미터 영역에서 p형 베이스로 주입되며, 여기서 소수 캐리어로서 역방향 바이어스 n형 컬렉터로 확산되어 역방향 바이어스 콜렉터-베이스 접합부의 전계에 의해 스위프된다.

이미터 전류입니다.

이미터 전류입니다. (는) 수집기 전류입니다.

(는) 수집기 전류입니다. 공통 베이스 순방향 단락 전류 게인(0.98~0.998)입니다.

공통 베이스 순방향 단락 전류 게인(0.98~0.998)입니다. 베이스-이미터 다이오드의 역포화 전류(10~10암페어−15−12)입니다.

베이스-이미터 다이오드의 역포화 전류(10~10암페어−15−12)입니다. p형 베이스에 있는 전자의 확산 상수입니다.

p형 베이스에 있는 전자의 확산 상수입니다.

![{\displaystyle {\begin{aligned}i_{\text{C}}&=I_{\text{S}}\left[\left(e^{\frac {V_{\text{BE}}}{V_{\text{T}}}}-e^{\frac {V_{\text{BC}}}{V_{\text{T}}}}\right)-{\frac {1}{\beta _{\text{R}}}}\left(e^{\frac {V_{\text{BC}}}{V_{\text{T}}}}-1\right)\right]\\i_{\text{B}}&=I_{\text{S}}\left[{\frac {1}{\beta _{\text{F}}}}\left(e^{\frac {V_{\text{BE}}}{V_{\text{T}}}}-1\right)+{\frac {1}{\beta _{\text{R}}}}\left(e^{\frac {V_{\text{BC}}}{V_{\text{T}}}}-1\right)\right]\\i_{\text{E}}&=I_{\text{S}}\left[\left(e^{\frac {V_{\text{BE}}}{V_{\text{T}}}}-e^{\frac {V_{\text{BC}}}{V_{\text{T}}}}\right)+{\frac {1}{\beta _{\text{F}}}}\left(e^{\frac {V_{\text{BE}}}{V_{\text{T}}}}-1\right)\right]\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2b9ab64b3efec643711bf37b452cc3ba5fb725d5)

(는) 수집기 전류입니다.

(는) 수집기 전류입니다. (가) 기본 전류입니다.

(가) 기본 전류입니다. 이미터 전류입니다.

이미터 전류입니다. (는) 역공통 이미터 전류 게인(0~20)입니다.

(는) 역공통 이미터 전류 게인(0~20)입니다. 역포화−15 전류(10~10암페어−12)입니다.

역포화−15 전류(10~10암페어−12)입니다. 베이스-콜렉터 전압입니다.

베이스-콜렉터 전압입니다.