연산 증폭기

Operational amplifier 가장 성공적인 연산 증폭기 중 하나인 μA741 집적회로 | |

| 유형 | 이산 회로 집적회로 |

|---|---|

| 발명된 | 칼 D. 스와첼 주니어 |

| 제1회 생산 | 1967 |

| 핀 구성 | |

| 전자 기호 | |

Op Amp의 회로 다이어그램 기호.핀에는 위와 같은 라벨이 붙어 있습니다. | |

연산 증폭기(종종 opamp 또는 opamp)는 차동 입력과 일반적으로 싱글 엔드 [1]출력을 가진 DC 결합 고이득 전자 전압 증폭기입니다.이 구성에서 op amp는 일반적으로 입력 단자 간의 전위차보다 100,000배 큰 출력 전위를 생성합니다.연산 증폭기의 기원은 선형, 비선형 및 주파수 의존 회로에서 수학적 연산을 수행하는 데 사용된 아날로그 컴퓨터에서 비롯되었습니다.

op amp가 아날로그 회로의 구성 요소로 인기가 있는 것은 다용도 때문입니다.부귀환을 이용하여 op-amp 회로의 특성, 그 이득, 입출력 임피던스, 대역폭 등을 외부성분에 의해 결정하고 op-amp 자체의 온도계수 또는 공학적 허용오차에 거의 의존하지 않는다.

Op Amp는 오늘날 다양한 소비자, 산업 및 과학 장치를 포함한 전자 장치에 널리 사용되고 있습니다.많은 표준 IC op amp의 가격은 몇 센트에 불과하지만, 특별한 성능 사양을 가진 일부 통합 또는 하이브리드 연산 증폭기의 가격은 [2]소량으로 100달러를 넘을 수 있습니다.Op Amp는 컴포넌트로 패키지되거나 보다 복잡한 집적회로의 소자로 사용될 수 있습니다.

op amp는 차동 증폭기의 한 유형입니다.다른 유형의 차동 증폭기에는 완전 차동 증폭기(opamp와 유사하지만 2개의 출력이 있음), 계장 증폭기(일반적으로 3개의 opamp로 구성됨), 절연 증폭기(계장 증폭기와 유사하지만 일반 opamp를 파괴하는 공통 모드 전압에 대한 내성이 있음) 및 음이 포함됩니다.(통상 1개 이상의 op암페어 및 저항성 피드백 네트워크로 구축됨)

작동

그 증폭기의 차동 입력 전압 V+(+)과 비반전형 입력 및 전압 V−을 가진 반전 입력(−), 직원들의 op앰프 전압의 두인 차동 입력 전압이라고 불린다 격차뿐, 증폭시킬 수 있습니다.그 op앰프 Vout의 출력 전압은 다음 등식으로 주어진다.

는 증폭기(용어"개루프의"외부 피드백 루프의 출력에서 불참에 대한 입력을 말한다)어디 AOL은 개방 루프 이득이었다.

Open-loop형 증폭기

AOL의 크기는 일반적으로 매우 큰(10만 이상 집적 회로 옵 암페어에), 따라서 V+과 V− 간 꽤 작은 차이 클립이나 포화에 증폭기를 운전한다.AOL의 크기는 제조 과정에 의해서 그것은 독립형 차동 증폭기로 open-loop 증폭기를 사용하는 것은 비현실적이다. 통제되지 않는다.

음의 피드백과 재생에 대한 선택적 양의 피드백이 없으면 op amp가 비교기 역할을 합니다.반전 입력이 접지(0V)에 유지되고 비반전 입력에 인가되는 입력 전압in V가 양이면 출력이 최대 양이고, V가in 음이면 출력이 최대 음이 됩니다.어느 쪽의 입력에도 출력으로부터의 피드백이 없기 때문에, 이것은 컴퍼레이터로서 동작하는 오픈 루프 회로입니다.

폐루프 증폭기

예측 가능한 동작이 바람직할 경우 출력전압의 일부를 반전입력에 인가함으로써 부귀환을 이용한다.폐쇄 루프 피드백은 회로의 이득을 크게 감소시킵니다.네거티브 피드백을 사용하는 경우 회로의 전체적인 게인과 응답은 주로 op-amp 특성이 아닌 피드백 네트워크에 의해 결정됩니다.피드백 네트워크가 opamp의 입력 임피던스에 비해 값이 작은 컴포넌트로 구성되어 있는 경우 opamp의 개방 루프 응답OL A 값은 회로의 성능에 심각한 영향을 미치지 않습니다.이러한 맥락에서 입력 단자의 높은 입력 임피던스와 출력 단자의 낮은 출력 임피던스는 특히 op amp의 유용한 기능입니다.

입력, 출력 및 피드백 회로에 대한 op-amp 회로의 응답은 수학적으로 전송 함수에 의해 특징지어집니다.op-amp 회로를 설계하여 원하는 전송 함수를 갖도록 하는 것은 전기 공학 분야입니다.전송 기능은 아날로그 컴퓨터와 같은 대부분의 Op Amp 애플리케이션에서 중요합니다.

우측의 비전도 증폭기에서는 분압기f R, R을g 통한 음의 피드백이 있으면 폐쇄 루프 이득 ACL = Vout / V를in 결정합니다. V가 V와 동일한in 전압으로 반전 입력을 끌어당길 수 있을out 때 평형이 설정됩니다.따라서 전체 회로의 전압 이득은 1 + Rf/R입니다g. 간단한 예로 V = 1V 및 Rf = R이면ingout V는 정확히 1V로 유지되는− 데 필요한 2V가 됩니다. R, Rg 네트워크에서f 제공하는 피드백 때문에 이 회로는 폐쇄 루프 회로입니다.

이 회로를 분석하는 또 다른 방법은 다음과 같은([3]통상 유효한) 가정을 하는 것입니다.

- op amp가 선형(즉, 포화 상태가 아님) 모드에서 작동하는 경우, 비반전(+) 핀과 반전(-) 핀 사이의 전압 차이는 무시할 수 있을 정도로 작습니다.

- (+) 핀과 (-) 핀의 입력 임피던스는 회로의 다른 저항보다 훨씬 큽니다.

입력 신호in V는 가정 1당 (+) 및 (-) 핀에 모두 나타나며, 결과적으로 전류 i ~ R은g V / R과g 같습니다in.

Kirchhoff의 전류 법칙은 노드가 들어갈 때 동일한 전류가 노드를 떠나야 한다고 규정하고 있으며, 가정 2에 따라 (-) 핀으로의 임피던스가 무한대에 가깝기 때문에 실질적으로 모든 동일한 전류 i가 R을 통해f 흐르면서 출력 전압을 생성한다고 가정할 수 있습니다.

용어를 조합하여 폐루프 게인CL A를 결정합니다.

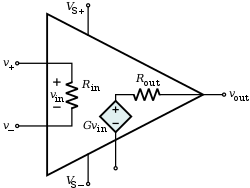

Op-amp 특성

이상적인 동작 암페어

이상적인 opamp는 일반적으로 다음과 같은 특성을 [4][5]가진 것으로 간주됩니다.

- 무한 개방 루프 이득 G = voutin / v

- 무한 입력 임피던스in R, 즉 제로 입력 전류

- 제로 입력 오프셋 전압

- 무한 출력 전압 범위

- 제로 위상 편이 및 무한 슬루 레이트를 갖춘 무한 대역폭

- 제로 출력 임피던스out R 등 무한 출력 전류 범위

- 제로 노이즈

- 무한 공통 모드 제거 비율(CMR)

- 무한 전원 장치 제거 비율.

이러한 이상은 두 가지 황금률로 요약할 수 있습니다.

- 폐쇄 루프에서 출력은 입력 간의 전압 차이를 0으로 만들기 위해 필요한 모든 작업을 시도합니다.

- 입력에 전류가 [6]: 177 흐르지 않습니다.

첫 번째 규칙은 폐쇄 루프 설계(부정 피드백, 출력에서 반전 입력으로 피드백되는 소트의 신호 경로가 있는 경우)에서 op amp를 사용하는 일반적인 경우에만 적용됩니다.이러한 규칙은 일반적으로 op-amp [6]: 177 회선을 분석하거나 설계하기 위한 첫 번째 근사치로 사용됩니다.

이 이상들 중 어느 것도 완벽하게 실현될 수 없다.실제 opamp는 op-amp 모델에서 등가 저항기와 캐패시터를 사용하여 무한하지 않거나 0이 아닌 파라미터로 모델링할 수 있습니다.설계자는 이러한 효과를 최종 회로의 전체 성능에 포함할 수 있습니다.일부 매개변수는 최종 설계에 무시해도 될 정도의 영향을 미칠 수 있는 반면, 다른 매개변수는 평가해야 하는 최종 성능의 실제 한계를 나타낼 수 있다.

실제 동작 전류

실제 연산 전류는 다양한 측면에서 이상적인 모델과 다릅니다.

- 유한 이득

- 개방 루프 이득은 이상적인 연산 증폭기에서는 무한하지만 실제 연산 증폭기에서는 유한합니다.일반적인 디바이스에서는 오픈루프 DC 게인이 100,000을 넘습니다.루프 게인 (즉, 개방 루프와 피드백 게인의 곱)이 매우 큰 한, 폐쇄 루프 게인은 전적으로 부정적인 피드백의 양에 의해 결정될 것입니다 (즉, 개방 루프 게인과는 무관할 것입니다).클로즈드 루프 게인이 매우 높아야 하는 어플리케이션에서는 피드백 게인이 매우 낮아지고 이러한 경우 루프 게인이 낮아지면 회로로부터의 이상적이지 않은 동작이 발생합니다.

- 0이 아닌 출력 임피던스

- 낮은 임피던스 부하에서는 낮은 출력 임피던스가 중요합니다.이러한 부하에서는 출력 임피던스에 걸친 전압 강하가 오픈 루프 게인을 효과적으로 줄입니다.전압 감지 음의 피드백이 있는 구성에서는 증폭기의 출력 임피던스가 효과적으로 낮아집니다. 따라서 선형 애플리케이션에서는 op-amp 회로가 일반적으로 매우 낮은 출력 임피던스를 나타냅니다.

- 저임피던스 출력은 일반적으로 출력 단계에서 높은 대기(예: 유휴) 전류를 필요로 하며 더 많은 전력을 소모하므로 저전력 설계로 인해 저출력 임피던스가 의도적으로 희생될 수 있습니다.

- 유한 입력 임피던스

- OP 앰프의 차동 입력 임피던스는 두 입력 사이의 임피던스로 정의됩니다. 공통 모드 입력 임피던스는 각 입력에서 접지까지의 임피던스입니다.MOSFET 입력 연산 증폭기에는 작은 임계값보다 큰 입력 차이를 효과적으로 단락시키는 보호 회로가 있는 경우가 많기 때문에 일부 테스트에서는 입력 임피던스가 매우 낮은 것처럼 보일 수 있습니다.단, 이러한 연산 증폭기가 일반적인 고이득 음성 피드백 애플리케이션에서 사용되는 한 이러한 보호 회로는 비활성화됩니다.아래에 설명된 입력 바이어스 및 누출 전류는 일반적인 Op 앰프 애플리케이션에서 더 중요한 설계 파라미터입니다.

- 입력 캐패시턴스

- 기생 캐패시턴스에 의한 추가 입력 임피던스는 입력 임피던스를 저하시켜 위상 편이를 일으킬 가능성이 있는 고주파 동작에서는 중대한 문제가 될 수 있습니다.

- 입력 전류

- 바이어스 요구 사항 또는 누출로 인해 소량의 전류가[nb 2] 입력으로 흐릅니다.회로에서 높은 저항 또는 높은 출력 임피던스를 가진 소스가 사용되는 경우 이러한 작은 전류로 인해 전압 강하가 발생할 수 있습니다.입력 전류가 일치하고 두 입력 중 임피던스가 일치하면 각 입력에서 생성되는 전압은 같아집니다.OP 앰프는 입력 간의 차이에 따라 작동하므로 이러한 일치 전압은 아무런 영향을 미치지 않습니다.입력 전류가 약간 일치하지 않는 경우가 더 많습니다.이 차이를 입력 오프셋 전류라고 하며, 일치하는 저항에도 작은 오프셋 전압(아래 입력 오프셋 전압과 구별됨)이 생성될 수 있습니다.이 오프셋 전압은 OP 앰프에서 오프셋 또는 드리프트를 생성할 수 있습니다.

- 입력 오프셋 전압

- 이 전압은 출력 전압을 [7][nb 3]0으로 구동하는 데 Op Amp의 입력 단자에서 필요한 전압입니다.완벽한 증폭기에서는 입력 오프셋 전압이 없습니다.단, op암페어의 차동증폭기 입력단계의 결함으로 인해 존재합니다.입력 오프셋 전압은 두 가지 문제를 일으킵니다.첫째, 앰프의 고전압 게인으로 인해 입력 단자가 함께 배선되어 있는 경우에도 음의 피드백 없이 작동하면 앰프 출력이 포화 상태가 되도록 사실상 보장합니다.둘째, 폐루프, 부귀환 구성에서는 입력 오프셋 전압이 신호와 함께 증폭되므로 고정밀 DC 증폭이 필요하거나 입력 신호가 매우 [nb 4]작을 경우 문제가 발생할 수 있습니다.

- 공통 모드 게인

- 완벽한 OP 앰프는 두 입력 사이의 전압 차이만 증폭하여 두 입력 모두에 공통적인 모든 전압을 완전히 제거합니다.그러나 연산증폭기의 차동입력단계가 결코 완벽하지 않기 때문에 이들 공통전압은 어느 정도 증폭된다.이 결함에 대한 표준 척도를 Common-Mode Reject Ratio(CMR; 공통 모드 제거 비율)라고 합니다.높은 게인으로 동작하는 비반전 증폭기에서는 공통 모드 게인의 최소화가 중요합니다.

- 전원 장치의 거부

- 완벽한 OP 앰프의 출력은 전원 공급 전압 변동과 무관합니다.모든 실제 연산 증폭기에는 공급 전압의 변화를 opamp가 얼마나 잘 제거할 수 있는지를 반영하는 유한한 전원 제거 비율(PSR)이 있습니다.

- 온도 효과

- 증폭기의 성능은 일반적으로 온도 변화에 따라 어느 정도 변화합니다.입력 오프셋 전압의 온도 드리프트는 특히 중요합니다.

- 드리프트

- 실제 op-amp 파라미터는 시간이 지남에 따라 온도, 입력조건 등의 변화에 따라 서서히 변화할 수 있습니다.

- 한정된 대역폭

- 모든 증폭기의 대역폭은 한정되어 있습니다.첫 번째 근사치에 대해 op amp는 게인이 있는 적분기의 주파수 응답을 가집니다.즉, 일반적인 opamp의 이득은 주파수에 반비례하며 이득 대역폭 곱(GBWP)에 의해 특징지어집니다.예를 들어 GBWP가 1MHz인 opamp는 200kHz에서 게인이 5, 1MHz에서 게인이 1이 됩니다.이 동적 응답은 opamp의 매우 높은 DC 게인과 결합되어 GBWP를 DC 게인으로 나눈 매우 높은 DC 게인과 낮은 컷오프 주파수를 갖는 1차 로우패스 필터의 특성을 제공합니다.op amp의 한정된 대역폭은 다음과 같은 몇 가지 문제의 원인이 될 수 있습니다.

- Stability

- 대역폭 제한과 관련된 것은 입력 신호와 증폭기 출력 사이의 위상차이며, 일부 피드백 회로에서 발진을 일으킬 수 있습니다.예를 들어 같은 주파수의 입력신호를 파괴적으로 간섭하는 정현파 출력신호는 180도 지연되면 건설적으로 간섭하여 양의 피드백을 형성한다.이 경우, 피드백 회로는 주파수 보상에 의해 안정화 될 수 있으며, 개방 루프 회로의 이득 또는 위상 마진을 증가시킬 수 있다.회로 설계자는 별도의 회로 컴포넌트를 사용하여 이 보상을 외부에 구현할 수 있습니다.또는 오퍼앰프의 고주파 게인을 충분히 감쇠시키는 지배극이 추가되어 오퍼앰프 내에서 보정을 실시할 수 있다.이 극의 위치는 제조업체가 내부적으로 고정하거나 회로 설계자가 Op Amp에 고유한 방법을 사용하여 구성할 수 있습니다.일반적으로 지배극 주파수 보정은 Opamp의 대역폭을 더욱 감소시킨다.원하는 폐쇄 루프 게인이 높을 경우 필요한 개방 루프 게인이 충분히 낮기 때문에 op-amp 주파수 보정이 필요하지 않은 경우가 많습니다.따라서 폐쇄 루프 게인이 높은 애플리케이션은 대역폭이 높은 opamp를 사용할 수 있습니다.

- Distortion, and other effects

- 대역폭이 한정되어 있으면 주파수가 높을수록 피드백량이 적어지고 왜곡이 커지며 주파수가 증가할수록 출력 임피던스가 커집니다.

- 노이즈

- 신호가 인가되지 않은 경우에도 앰프가 노이즈를 출력합니다.이 문제는 디바이스의 내부 온도 이상음 및 깜박임 소음 때문일 수 있습니다.고게인 또는 고대역폭 어플리케이션에서는 노이즈가 중요한 고려사항이 되며 성능 요건을 충족하기 위해 저노이즈 앰프가 필요할 수 있습니다.

- 전원 장치의 거부

- 주파수가 증가함에 따라 전원장치 제거는 일반적으로 더 심해집니다.따라서 예를 들어 바이패스 캐패시터를 사용하여 고주파 리플 및 신호의 공급을 청결하게 유지하는 것이 중요합니다.

비선형 결함

- 포화도

- 출력 전압은 전원 공급기 [nb 5]전압에 가까운 최소값과 최대값으로 제한됩니다.이전 Op Amp의 출력은 공급 레일의 1~2V 이내에 도달할 수 있습니다.낮은 출력 [8]전류를 제공할 때 이른바 레일 간 운영 암페어의 출력은 공급 레일의 밀리볼트 이내에 도달할 수 있습니다.

- 슬링

- 앰프의 출력 전압은 최대 변화율인 슬루 레이트에 도달하며, 일반적으로 마이크로초당 볼트(V/μs)로 지정됩니다.슬레잉이 발생하면 입력 신호의 추가 증가는 출력 변화율에 영향을 주지 않습니다.슬루잉은 일반적으로 입력 스테이지가 포화되어 발생하며, 그 결과 정전류 i가 증폭기의 정전용량 C(특히 주파수 보상을 구현하는 데 사용되는 정전용량)를 구동합니다. 슬루 레이트는 dv/dt = i/C로 제한됩니다.slewing은 op amp의 큰 신호 성능과 관련이 있습니다.예를 들어 게인 10에 대해 op amp가 설정되어 있다고 가정합니다.입력이 1V, 100kHz 톱니 파형이라고 가정합니다.즉, 진폭은 1V이고 주기는 10마이크로초입니다.따라서 입력의 변화율(즉 기울기)은 0.1V/마이크로초이다.10×증폭 후 출력은 10V, 100kHz 톱니가 되어야 하며 이에 상응하는 슬루 레이트는 마이크로초당 1V입니다.그러나 고전적인 741 op amp는 0.5V/마이크로초 슬루 레이트 사양이므로 톱니바퀴의 10마이크로초 주기에 출력이 5V 이하로 상승할 수 있습니다.따라서 출력을 측정할 경우 10V, 100kHz 톱니가 아닌 5V, 100kHz 톱니가 됩니다.다음에는 동일한 앰프와 100kHz 톱니를 고려하지만, 이제 입력 진폭은 1V가 아닌 100mV입니다. 10배 증폭 후 출력은 1V, 100kHz 톱니가 되며 마이크로초당 0.1V의 상응하는 슬루 레이트가 발생합니다.이 경우 마이크로초당 0.5V 슬루 레이트의 741은 입력을 적절히 증폭합니다.현대의 고속 연산 전류는 마이크로초당 5,000V 이상의 슬루 레이트를 가질 수 있습니다.단, 일반적으로 op암페어의 슬루 레이트는 마이크로초당 5~100V입니다.예를 들어 범용 TL081 op amp의 슬루 레이트는 마이크로초당 13V입니다.일반적으로 저전력 및 소대역폭의 op암페어는 슬루 레이트가 낮습니다.예를 들어 LT1494 마이크로파워 opamp는 1.5마이크로암페어를 소비하지만 2.7kHz 게인 대역폭 곱과 마이크로초당 0.001V 슬루 레이트를 갖추고 있습니다.

- 비선형 입출력 관계

- 그 출력 전압 정확하게 입력 전압 사이의 차이에 비례하지 않을 수 있다.입력 신호 파형을 일반적으로 왜곡이라고 불린다.이 영향은 매우 상당한 부정적인 피드백 사용되는 실용적인 회로에 줄어들 것이다.

- 위상 역전

- 때는 출간된 공통 모드 전압(하나를 입력한 사건 중 하나는 공급 전압을 갖는 것으로 예:)를 위반한 경우 일부 통합 opamp에서는, 출력인 것이 작업에 예상된다와 반대 극성에를 젤 수 있다.[9][10]이러한 조건들 하에서 부정적인 피드백은 회로 그 주의" 잠그다" 긍정적이 된다.

전력에 관한 고려 사항

- 제한된 출력 전류

- 그 출력 전류 유한해야 한다.실제로, 가장 옵 앰프 출력을 제한하도록 설계된다 그렇게 지정된 수준을 초과하지 않는 형식으로 741명의 ICop앰프 – 손상으로부터 옵 앰프와 관련된 회로를 보호하기 위해 약 25mA – 현재.현대 디자인 전자적으로 좀 더 일찍 구현보다 약간의 손상 없이 결과에 직접적인 회로를 단락을 유지할 수 있는 험준한 있다.

- 제한된 출력 전압

- 출력 전압의 전원 공급 장치 전압이 op앰프 공급을 초과할 수 없다.대부분의 옵 amp의 최대 출력은 어느 정도에 의해 출력 회로의 제한 때문에 감소된다.특별한 rail-to-rail 옵 amp최대 출력 수준을 위해 고안되었다.[8]

- 출력은 싱크 전류

- 출력 싱크 전류는 출력 스테이지에 싱크할 수 있는 최대 전류입니다.일부 제조업체는 다른 소스에서 출력 핀으로 전류를 싱크할 때 출력 전압을 알 수 있는 출력 전압 대 출력 싱크 전류도를 보여 줍니다.

- 제한된 소산 전력

- 출력 전류가 opamp의 내부 출력 임피던스를 통해 흐르면서 방산해야 하는 열을 생성합니다.op amp가 너무 많은 전력을 소산하면 온도가 어느 정도 안전 한계 이상으로 증가합니다.op amp가 서멀 셧다운 상태가 되거나 파괴될 수 있습니다.

입력 임피던스 및 입력 바이어스 전류에 관한 한 현대의 통합 FET 또는 MOSFET op amp는 바이폴라 IC보다 이상적인 op amp에 가깝습니다.바이폴라는 일반적으로 입력 전압 오프셋이 더 좋고 노이즈가 더 낮은 경우가 많습니다.일반적으로 상온에서 상당히 큰 신호와 제한된 대역폭으로 FET 및 MOSFET op amp가 더 나은 성능을 제공합니다.

741 타입의 opamp 내부 회로

많은 제조업체와 여러 유사한 제품에서 공급되는 바이폴라 트랜지스터 OP 앰프의 예로는 1968년 Fairchild Semiconductor의 David Fullagar가 Bob Widlar의 LM301 집적회로 [11]설계를 따라 설계한 741 집적회로가 있습니다.이 설명에서는 하이브리드 pi 모델의 파라미터를 사용하여 트랜지스터의 작은 신호 접지 이미터 특성을 특징짓습니다.이 모델에서 트랜지스터의 전류 이득은 h로 표시되며fe, [12]더 일반적으로 β라고 불립니다.

아키텍처

소규모 집적회로인 741 op amp는 [13]세 가지 게인 단계로 구성된 내부 구조를 대부분의 op amp와 공유합니다.

- 차동증폭기(진청색 아웃라인) - 커먼 모드 신호 거부, 저노이즈, 고입력 임피던스, 고차동증폭(게인)을 실현합니다.

- 전압증폭기(선상 자홍색) - 고전압 게인, 단극 주파수 롤오프, 나아가서 구동,

- 출력 앰프(시안 및 녹색 아웃라인) — 출력 전류 제한 및 출력 단락 보호와 함께 높은 전류 게인(낮은 출력 임피던스)을 제공합니다.

또한 전류 미러(빨간색 아웃라인) 바이어스 회로와 보정 캐패시터(30pF)를 포함합니다.

차동 증폭기

입력 단계는 캐스케이드된 차동 증폭기(파란색으로 표시됨)와 그에 이은 전류 미러 활성 부하로 구성됩니다.이는 Q1, Q2 베이스의 차압 신호를 Q15 베이스의 전류 신호로 변환하는 트랜스컨덕턴스 앰프를 구성합니다.

두 개의 캐스케이드 트랜지스터 쌍을 사용하여 상충되는 요구 사항을 충족합니다.첫 번째 단계는 높은 입력 임피던스를 제공하는 일치하는 NPN 이미터 팔로어 쌍 Q1, Q2로 구성됩니다.두 번째는 바람직하지 않은 밀러 효과를 제거하는 일치 PNP 공통 베이스 페어 Q3, Q4입니다.이는 액티브 부하 Q7과 일치 페어 Q5, Q6을 구동합니다.

이 활성 로드는 수정된 Wilson 전류 미러로 구현됩니다. 이 부하의 역할은 (차동) 입력 전류 신호를 어텐던트 50% 손실 없이 단일 엔드 신호로 변환하는 것입니다(op amp의 개방 루프 게인 [nb 6]3dB 증가).따라서 Q3 대 Q4의 작은 신호 차분 전류는 전압 게인 스테이지의 입력인 Q15의 베이스에서 합계(더블)된 것으로 보입니다.

전압 증폭기

(class-A) 전압 게인 스테이지(마젠타 표시)는 Darlington 구성으로 연결된 2개의 NPN 트랜지스터 Q15/Q19로 구성되며, 고전압 게인을 달성하기 위해 전류 미러 Q12/Q13의 출력 측을 컬렉터(동적) 부하로 사용합니다.출력 싱크 트랜지스터 Q20은 Q15 및 Q19의 공통 컬렉터로부터 베이스 드라이브를 수신합니다.레벨 시프트 Q16은 출력 소스 트랜지스터 Q14에 베이스 드라이브를 제공합니다.

트랜지스터 Q22는 이 단계가 Q20에 과도한 전류를 공급하는 것을 방지하여 출력 싱크 전류를 제한합니다.

출력 증폭기

출력 스테이지(Q14, Q20, 시안으로 아웃라인 표시)는 클래스 AB의 상보대칭 앰프입니다.임피던스가 최대 50Ω인 출력 드라이브를 제공합니다(기본적으로 전류 게인).트랜지스터 Q16(녹색으로 표시)은 출력 트랜지스터에 대기 전류를 제공하고 Q17은 출력 전류 제한을 제공합니다.

바이어스 회로

각 작동 전류 단계에 적절한 대기 전류를 공급하십시오.

(다이오드 연결) Q11과 Q12를 연결하는 저항(39kΩ)과 주어진 공급 전압(VS+ - VS−)이 전류 미러(일치 쌍) Q10/Q11과 Q12/Q13의 전류를 결정합니다.Q11, i11 × 39 kΩ = VS+ - VS− - 2BE V의 컬렉터 전류.일반적인S V = ±20 V의 경우, Q11/Q12(Q13뿐만 아니라 Q12)의 정지 전류는 약 1mA입니다.약 2mA의 일반적인 741의 공급전류는 이들 2개의 바이어스 전류가 대기전류를 지배한다는 개념과 일치한다.

트랜지스터 Q11 및 Q10은 ln(i11/i10) = i10 × 5kΩ / 28mV가 Q10의 이미터 저항을 나타내며 28mV는T 상온에서 열전압인 V인 대기전류를10 갖는 Widlar 전류미러를 형성한다.이 경우10 i ≤ 20 μA이다.

차동 증폭기

이 스테이지의 바이어스 회로는 Q10과 Q9의 컬렉터 전류를 (거의) 일치시키는 피드백루프에 의해 설정됩니다.이러한 전류의 작은 차이는 Q3/Q4의 공통 베이스에 대한 구동력을 제공합니다(입력 트랜지스터 Q1/Q2의 베이스 드라이브는 입력 바이어스 전류이므로 외부에서 소싱해야 함).Q1/Q3 + Q2/Q4의 합계 대기 전류는 Q8에서 Q9로 미러링되며, Q10의 콜렉터 전류와 합산되어 Q3/Q4의 베이스에 적용됩니다.

따라서 Q1/Q3(응답1, Q2/Q4) i의 대기 전류는 i의 절반10, 약 10μA가 됩니다.Q1의 베이스에 대한 입력 바이어스 전류(resp).Q2)는 i / β가 됩니다1.일반적으로 50nA까지 됩니다.이는 Q1(Q2)의fe 전류 이득 h ≤ 200을 의미합니다.

이 피드백 회로는 Q3/Q4의 공통 기본 노드를 전압 Vcom - 2V로BE 끌어당기는 경향이 있습니다. 여기서com V는 입력 공통 모드 전압입니다.동시에 대기전류의 크기는 온도 의존성 또는 부품 간 변화를 일으킬 수 있는 Q1~Q4 성분(예fe: h)의 특성에 상대적으로 민감하지 않습니다.

트랜지스터 Q7은 Q1/Q3 및 Q2/Q4의 콜렉터 전류가 일치할 때까지 Q5 및 Q6을 도통으로 구동합니다.Q7의 대기 전류는BE V / 50 kΩ, 약 35 μA이며, Q15의 대기 전류와 작동 지점이 일치합니다.따라서 대기 전류는 Q1/Q2, Q3/Q4, Q5/Q6, Q7/Q15에서 쌍으로 일치합니다.

전압 증폭기

Q16 및 Q19의 대기 전류는 약 1mA에서 작동하는 전류 미러 Q12/Q13에 의해 설정됩니다.일부 메커니즘을 통해[vague] Q19의 수집기 전류는 해당 정전류를 추적합니다.

출력 증폭기

Q16(다양한 이름의 고무 다이오드 또는BE V 멀티플라이어)을 사용하는 회로에서는 4.5kΩ 저항기가 약 100μA, Q16BE V는 약 700mV를 전도해야 합니다.그러면 V는CB 약 0.45V이고 V는CE 약 1.0V여야 합니다.Q16 컬렉터는 전류원에 의해 구동되며 Q16 이미터는 Q19 컬렉터 전류 싱크로 구동되므로 Q16 트랜지스터는 Q14/Q20 베이스의 커먼 모드 전압에 관계없이 Q14 베이스와 Q20 베이스 사이의 전압차를 1V 이하로 설정합니다.Q14/Q20의 정지 전류는 opamp의 클래스 A 부분의 1mA 대기 전류보다 작은 exp(100mV/VT) 36 36입니다.출력 트랜지스터의 이(작은) 정전기류는 클래스 AB 작동에서 출력 스테이지를 확립하고 이 스테이지의 크로스오버 왜곡을 줄입니다.

소신호 차동 모드

작은 차동 입력 전압 신호는 여러 단계의 전류 증폭을 통해 훨씬 더 큰 출력 전압 신호를 생성합니다.

입력 임피던스

Q1과 Q3의 입력 스테이지에서는 이미터-커플링 페어(롱테일 페어)와 비슷하며 Q2와 Q4에 약간의 저하 임피던스가 추가됩니다.Q1~Q4를 통과하는 전류가 적기 때문에 입력 임피던스가 상대적으로 높습니다.일반적인 741 op amp의 차동 입력 임피던스는 약 2MΩ입니다.공통 모드 입력 임피던스는 입력 스테이지가 기본적으로 일정한 전류로 작동하기 때문에 더욱 높습니다.

차동 증폭기

opamp 입력에서의 차동전압in V(각각 핀 3, 2)는 Q1 및 Q2in iθVin / (2hhiefe)의 베이스에서 소량의 차동전류를 발생시킨다.이 차동 기본 전류는 각 레그의 차동 수집기 전류를 ih만큼infe 변화시킵니다.Q1, gm = hfe/h의ie 트랜스컨덕턴스를 도입할 때 Q15의 베이스(전압 게인 스테이지의 입력)에서의 (소량) 전류는inm Vg/2입니다.

op amp의 이 부분은 op amp 입력 시 차분 신호를 Q15 베이스의 싱글 엔드 신호로 교묘하게 변경하여 어느 한쪽 레그에서 신호가 낭비되는 것을 방지합니다.그 방법을 확인하려면 반전 입력(Q2 베이스)에서 전압이 약간 음의 변화만 있으면 통전되지 않고, 이 증분 전류 감소가 Q4 컬렉터에서 이미터로 직접 전달되어 Q15용 베이스 드라이브가 감소합니다.한편, 비반전 입력(Q1 베이스)에서의 전압의 작은 양의 변화는 이 트랜지스터를 전도 상태로 구동하며, 이는 Q3 컬렉터의 전류 증가에 반영됩니다.이 전류는 Q7을 더욱 전도 상태로 유도하여 전류 미러 Q5/Q6을 켭니다.따라서 Q3 이미터 전류의 증가는 Q6 컬렉터 전류의 증가에 반영됩니다.증가된 컬렉터 전류는 컬렉터 노드에서 더 많이 분쇄되어 Q15의 베이스 드라이브 전류가 감소합니다.이 기술은 여기서 3dB의 이득 낭비를 방지할 뿐만 아니라 공통 모드 이득 및 전원 노이즈 피드 스루를 줄입니다.

전압 증폭기

Q15 베이스에서의 전류신호 i는 iβ차2(달링턴쌍으로 접속된 Q15, Q19의 h의fe 곱)의 Q19에서 전류를 발생시킨다.이 전류 신호는 출력 트랜지스터 Q14/Q20의 베이스에서 각 트랜지스터의 h에ie 비례하는 전압을 발생시킵니다.

출력 증폭기

출력 트랜지스터 Q14 및 Q20은 각각 이미터 팔로어로 구성되므로 전압 게인은 발생하지 않으며, 대신 이 단계는 Q14의 hfe(resp)와 동일한 전류 게인을 제공합니다.문제 20)

출력 임피던스는 이상적인 op암페어에서는 0이 아니지만 음의 피드백에서는 저주파에서는 0에 가깝습니다.

전체 개방 루프 전압 게인

Opamp의 순 개방 루프 소 신호 전압 이득에는 일부 4개의 트랜지스터의 전류 이득fe h의 곱이 포함됩니다.실제로 일반적인 741식 opamp의 전압 게인은 200,000개이며 전류 게인은 입력 임피던스(~2~6MΩ) 대 출력 임피던스(~50Ω)의 비율입니다.

기타 선형 특성

소신호 공통 모드 게인

이상적인 op amp는 무한 공통 모드 제거 비율 또는 0 공통 모드 게인을 가집니다.

현재 회로에서 입력 전압이 동일한 방향으로 변화하면 음의 피드백에 의해 Q3/Q4 기본 전압이 입력 전압 변동(2VBE 이하)을 따릅니다.이제 Q10-Q11 전류 미러의 출력부(Q10)는 전압이 변동하더라도 Q9/Q8을 통해 공통 전류를 일정하게 유지합니다.Q3/Q4 컬렉터 전류와 그에 따라 Q15의 베이스 출력 전류는 변경되지 않습니다.

일반적인 741 op암페어에서는 커먼 모드 제거비는 90dB로 오픈 루프 커먼 모드 전압 게인이 약 6임을 의미합니다.

주파수 보정

Fairchild μA741의 혁신은 온칩(모놀리식) 캐패시터를 통한 주파수 보정을 도입하여 이 기능을 위한 외부 구성요소의 필요성을 제거함으로써 op amp의 적용을 단순화한 것입니다.30pF 캐패시터는 밀러 보상을 통해 앰프를 안정화하며 op-amp 적분 회로와 유사한 방식으로 작동합니다.다른 극의 효과를 개방 루프 주파수 응답에 마스킹(지배)하는 극을 도입하여 '우세한 극 보상'이라고도 합니다. 741op A에서 이 극은 10Hz(열린 루프 전압 게인의 -3dB 손실을 유발함)까지 낮아질 수 있습니다.

이 내부 보상은 피드백 네트워크가 비반응적이고 폐쇄 루프 게인이 유니티 이상인 부귀환 구성에서 앰프의 무조건적인 안정성을 달성하기 위해 제공됩니다.반면 μA748과 같이 외부 보상을 필요로 하는 증폭기는 외부 보상 또는 단일성보다 훨씬 높은 폐쇄 루프 게인을 요구할 수 있습니다.

입력 오프셋 전압

"오프셋 null" 핀은 Q5/Q6 전류 미러의 밸런스를 조정하기 위해 외부 저항기(일반적으로 전위차계의 양단 형태, 슬라이더가 V에 연결된S– 상태)를 Q5 및 Q6의 이미터 저항기와 병렬로 배치하는 데 사용할 수 있습니다.전위차계는 입력이 함께 단락될 때 출력이 null(미드 레인지)이 되도록 조정됩니다.

비선형 특성

입력 파괴 전압

트랜지스터 Q3, Q4는 역VBE 정격 증가에 도움이 됩니다.NPN 트랜지스터 Q1 및 Q2의 베이스 이미터 접합은 약 7V에서 분해되지만 PNP 트랜지스터 Q3 및 Q4는 약 50V의 [14]V 파괴 전압을 가집니다BE.

출력단 전압 변동 및 전류 제한

온도에 따라 또는 동일한 유형의 부품 간에 대기 전류가 변동하는 것이 일반적이므로 교차 왜곡 및 대기 전류에 상당한 변동이 있을 수 있습니다.

앰프의 출력 범위는 출력 트랜지스터 Q14 및 Q20의 일부 V로BE 인해 공급 전압보다 약 1V 작습니다.

Q14 이미터의 25Ω 저항은 Q17과 함께 Q14 전류를 약 25mA로 제한합니다.그렇지 않으면 Q17은 전류를 통하지 않습니다.

Q20에 대한 전류 제한은 전압 게인 단계에서 수행됩니다.Q22는 Q19의 이미터 저항(50Ω)에서 전압을 감지합니다. 전원이 켜지면 구동 전류가 Q15 베이스로 감소합니다.

이 앰프 도식의 최신 버전에서는 출력 전류 제한 방법이 다소 다를 수 있습니다.

적용가능성 고려사항

741은 역사적으로 오디오 및 기타 민감한 장비에 사용되었지만, 더 현대적인 Op Amp의 향상된 소음 성능 때문에 이러한 사용은 현재 드물다.741 및 기타 오래된 동작암페어는 현저한 쉿음을 발생시키는 것 외에 커먼 모드 제거율이 낮을 수 있기 때문에 종종 케이블로 전달되는 주전원 험 및 스위치 '클릭'과 같은 기타 커먼 모드 간섭을 민감한 기기에 도입합니다.

「741」은, 범용의 op-amp IC(μA741, LM301, 558, LM324, TBA221 등)를 의미하는 경우가 많아지고 있습니다.741 출력 스테이지의 설명은 (입력 스테이지가 상당히 다를 수 있는) 다른 많은 설계에서도 질적으로 유사합니다.다만, 다음과 같습니다.

- 일부 장치(μA748, LM301, LM308)는 내부적으로 보정되지 않습니다(저폐 루프 게인 애플리케이션에서 사용되는 경우 출력에서 연산 증폭기 내의 특정 지점까지 외부 캐패시터가 필요합니다).

- 일부 최신 장치에는 레일 간 출력 기능이 있습니다. 즉, 출력 범위는 양의 공급 전압의 수 밀리볼트 이내에서 음의 공급 [8]전압의 수 밀리볼트 이내까지입니다.

분류

Op Amp는 구조에 따라 분류할 수 있습니다.

IC op amp는 다음과 같은 다양한 방법으로 분류할 수 있습니다.

- 군사용, 산업용 또는 상업용 등급.예를 들어 LM301은 LM101의 상업용 버전이고 LM201은 산업용 버전입니다.이것에 의해, 동작 온도 범위나 그 외의 환경적 또는 품질적 요인이 정의되는 경우가 있습니다.

- 패키지 타입에 의한 분류는 환경적인 견고성과 제조 옵션에 영향을 줄 수 있습니다.DIP 및 기타 스루홀 패키지는 표면 실장 장치로 대체되는 경향이 있습니다.

- 내부 보상에 의한 분류: 작은 보정 캐패시터가 위상 및 주파수 응답을 변경하지 않는 한 일부 음의 피드백 회로에서 op암페어가 고주파 불안정성을 겪을 수 있습니다.콘덴서가 내장된 Op Amp는 보상이라고 불리며, 지정된 폐쇄 루프 게인 이상의 회로를 외부 콘덴서 없이 안정적으로 동작시킬 수 있습니다.특히 닫힌 루프 게인 1에서도 안정된 op암페어는 유니티 게인 보정이라고 불립니다.

- 많은 상용 op-amp IC의 싱글, 듀얼 및 쿼드 버전을 사용할 수 있습니다. 즉, 1, 2 또는 4개의 운영 증폭기가 동일한 패키지에 포함되어 있습니다.

- 레일간 입력(및/또는 출력) 동작암페어는 전원장치 [8]레일에 매우 가까운 입력(및/또는 출력) 신호로 동작할 수 있습니다.

- CMOS op암페어(CA3140E 등)는 JFET 입력 op암페어(통상 바이폴라 입력 op암페어)보다 높은 매우 높은 입력 저항을 제공합니다.

- 다른 다양한 Op Amp에는 프로그래밍 가능한 Op Amp(대기 전류, 대역폭 등을 외부 저항기로 조정할 수 있음을 의미함)가 있습니다.

- 제조업체는 저소음 프리앰프, 광대역 앰프 등 목적에 따라 op암페어를 표로 작성하는 경우가 많습니다.

적용들

전자 시스템 설계에 사용

회로 블록으로 Op Amp를 사용하는 것은 사용되는 증폭기가 집적회로인지 이산회로인지에 관계없이 모든 개별 회로 소자(트랜지스터, 저항기 등)를 지정하는 것보다 훨씬 쉽고 명확합니다.첫 번째 근사에서는 이상적인 미분 이득 블록인 것처럼 op amp를 사용할 수 있으며, 이후 단계에서는 각 op amp에 대해 허용되는 파라미터 범위에 한계를 둘 수 있습니다.

회로 설계는 모든 전자 회로에 대해 동일한 라인을 따릅니다.회로에 필요한 작업을 규정하는 사양이 작성되어 있으며 허용 한도가 있습니다.예를 들어 특정 온도 범위에서 5%의 공차에서 1% 미만의 드리프트로 게인이 100배 요구될 수 있으며 입력 임피던스는 1메가움 이상일 수 있습니다.

기본 회로는 종종 (컴퓨터의) 회로 모델링의 도움을 받아 설계됩니다.그런 다음 상용화된 특정 Op Amp 및 기타 구성요소가 허용 가능한 비용으로 지정된 허용 오차 내에서 설계 기준을 충족하는 것으로 선택됩니다.모든 기준을 충족할 수 없는 경우 사양을 수정해야 할 수 있습니다.

그런 다음 프로토타입을 제작하고 테스트합니다. 사양을 충족하거나 개선하거나 기능을 변경하거나 비용을 절감하기 위한 변경이 이루어질 수 있습니다.

피드백을 사용하지 않는 응용 프로그램

즉, op amp가 전압 비교기로 사용되고 있습니다.예를 들어 속도가 중요하거나 광범위한 입력 전압이 발견될 수 있는 경우 주로 비교기로 설계된 장치가 더 나을 수 있습니다. 이러한 장치는 완전히 켜지거나 완전히 꺼진("포화") 상태에서 빠르게 복구할 수 있기 때문입니다.

Opamp의 입력 중 하나에 기준전압ref V를 인가하면 전압레벨 검출기를 얻을 수 있다.즉, op amp가 양전압을 검출하기 위한 비교기로 설정되어 있습니다.감지될 전압 E가i opamp의 (+) 입력에 적용되면 비반전 양 수준 검출기가 됩니다. 즉, E가 V보다ref 크면i V는O +V이고sat, E가 V보다ref 작으면i V는O -V입니다sat.반전 입력에 E가 적용되는 경우i 회로는 반전 양 레벨 검출기입니다.E가 V보다ref 크면i V는O -V와sat 같습니다.

제로 전압 레벨 검출기(Ei = 0)는 예를 들어 함수 발생기의 사인파 출력을 가변 주파수 사각파로 변환할 수 있습니다.E가 사인파, 삼각파 또는 0 주위에 대칭인 다른 모양의 파형인 경우i 제로 교차 검출기의 출력은 정사각형입니다.제로 교차 감지는 주 간섭 및 전류 스파이크를 줄이기 위해 최적의 시간에 TRIAC를 트리거하는 데도 유용할 수 있습니다.

포지티브 피드백 애플리케이션

op-amp의 또 다른 일반적인 구성은 양의 피드백으로 출력 신호의 일부를 비반전 입력으로 되돌리는 것입니다.이것의 중요한 응용 분야는 슈미트 트리거인 이력과의 비교기입니다.일부 회로는 동일한 증폭기 주변에서 양의 피드백과 음의 피드백을 사용할 수 있습니다(예: 삼각형 파형 오실레이터 및 활성 필터).

슬루 범위가 넓고 양의 피드백이 없기 때문에 위에서 설명한 모든 개방 루프 레벨 검출기의 응답은 비교적 느립니다.외부 전체 양성 피드백이 적용될 수 있지만 (목적 설계 대조군의 후반 단계에서 적용될 수 있는 내부 양성 피드백과 달리) 이는 제로 교차 검출 지점의 정확도에 현저하게 영향을 미친다.예를 들어 범용 op amp를 사용할 경우 사인파 대 사각파 변환기의 E 주파수는i 100Hz [citation needed]미만이어야 합니다.

네거티브 피드백 응용 프로그램

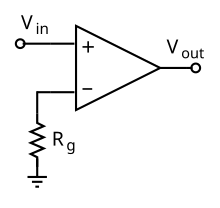

비반전 증폭기

비반전 증폭기에서는 출력전압이 입력전압과 같은 방향으로 변화합니다.

op amp의 게인 방정식은

그러나 이 회로에서는− R R 네트워크를12 통한 음의 피드백 때문에 V가 V의out 함수입니다.R과12 R은 분압기를 형성하고 V는 고임피던스 입력이므로− 부하가 현저하지 않다.결과적으로

어디에

이것을 게인 방정식에 대입하면, 우리는 다음을 얻는다.

out { V _ { \ { }} v 해결 중 :

의(\OL은(는) 매우 크므로 다음과 같이 됩니다.

OP 앰프의 비반전 입력에는 DC 접지 경로가 필요합니다.신호 소스가 DC 경로를 제공하지 않거나 해당 소스가 특정 로드 임피던스를 필요로 하는 경우 회로에는 비반전 입력에서 접지까지의 다른 저항이 필요합니다.OP의 입력 바이어스 전류가 상당할 경우 입력을 구동하는 DC 소스 저항이 균형을 [15]이루어야 합니다.피드백 저항의 이상적인 값(최소 오프셋 전압을 제공하기 위해)은 병렬로 배치된 두 저항이 비반전 입력 핀의 접지 저항과 거의 동일한 값이어야 합니다.이 이상적인 값은 바이어스 전류가 잘 일치한다고 가정하며, 이는 모든 Op Amp에 [16]해당되지 않을 수 있습니다.

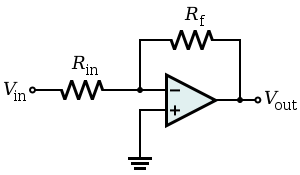

반전 증폭기

반전증폭기에서 출력전압이 입력전압과 반대방향으로 변화한다.

비반전 증폭기와 마찬가지로 op amp의 게인 방정식으로 시작합니다.

이때 V는− R과in R에 의해f 형성되는 분압기 때문에 V와in V의out 함수이다.다시 말하지만 op-amp 입력은 상당한 부하를 가하지 않습니다.

이를 게인 방정식에 대입하여 에 해결:

의(\OL은(는) 매우 크므로 다음과 같이 됩니다.

저항은 종종 비반전 입력과 접지 사이에 삽입됩니다(따라서 두 입력 모두 유사한 저항을 참조). 바이어스 전류에 의한 전압 강하에 따른 입력 오프셋 전압을 줄이고 일부 Op Amp에서 왜곡을 줄일 수 있습니다.

DC에 대한 주파수 응답이 필요하지 않고 입력에 DC 전압이 불필요한 경우 DC 차단 콘덴서를 입력 저항기와 직렬로 삽입할 수 있습니다.즉, 입력 임피던스의 용량성 성분이 DC 0과 저주파 극을 삽입하여 회로에 밴드패스 또는 하이패스 특성을 부여합니다.

OP 입력에서의 전위는 반전 구성에서 사실상 일정하게(접지 부근) 유지됩니다.통상, 일정한 동작 가능성으로 인해, 비반전 토폴로지로 달성할 수 있는 왜곡 레벨보다 낮은 왜곡 레벨이 발생합니다.

기타 응용 프로그램

- 오디오 주파수 및 비디오 주파수 사전 증폭기 및 버퍼

- 차동 증폭기

- 차별화 요소 및 통합업체

- 필터

- 정밀 정류기

- 정밀 피크 검출기

- 전압 및 전류 조절기

- 아날로그 계산기

- 아날로그-디지털 변환기

- 디지털-아날로그 변환기

- 전압 클램핑

- 발진기 및 파형 발생기

- 클리퍼

- clamper(DC 인서터 또는 restoreer)

- LOG 및 안티로그 증폭기

대부분의 싱글, 듀얼 및 쿼드 오퍼 암페어에는 표준화된 핀 배치가 있어 배선 변경 없이 어떤 타입을 다른 타입으로 대체할 수 있습니다.개방 루프 게인, 대역폭, 노이즈 퍼포먼스, 입력 임피던스, 전력 소비 또는 이들 요인 간의 타협을 위해 특정 op amp를 선택할 수 있습니다.

역사 연대 표

1941년: 진공관 op amp.범용 DC 결합 고이득 반전 피드백 증폭기로 정의되는 Op Amp는 Karl D가 제기한 미국 특허 2401,779 "Summing Amp"에서 처음 발견됩니다. 1941년 벨 연구소의 스와첼 주니어이 설계는 90dB의 게인을 달성하기 위해 3개의 진공 튜브를 사용했으며 ±350V의 전압 레일에서 작동했습니다.오늘날의 연산 전류에서 흔히 볼 수 있듯이, 미분 반전 및 비반전 입력이 아닌 단일 반전 입력이 있었다.제2차 세계대전 내내, 스와르첼의 디자인은 벨 연구소에서 디자인된 M9 포병 책임자에 폭넓게 사용됨으로써 그 가치를 입증했다.이 포병 소장은 SCR584 레이더 시스템과 함께 [17]일하면서 그렇지 않았다면 불가능했을 엄청난 명중률(90%에 육박)을 달성했습니다.

1947: 명시적인 비반전 입력이 있는 opamp.1947년, 연산 증폭기는 콜롬비아 대학의 존 R. 라가지니에 의해 공식적으로[18] 정의되고 명명되었다.이 논문에서 각주는 상당히 중요한 것으로 판명된 학생의 op-amp 설계를 언급했다.Loebe Julie가 디자인한 이 op amp는 여러 면에서 우수했습니다.두 가지 주요 혁신이 있었습니다.입력 단계에서는 출력의 드리프트를 줄이기 위해 부하가 일치하는 긴 꼬리의 3극 쌍이 사용되었으며, 훨씬 더 중요한 것은 두 개의 입력(하나는 반전, 다른 하나는 비반전)을 가진 최초의 op-amp 설계였다.차동 입력으로 인해 모든 범위의 새로운 기능이 가능했지만, 초퍼 안정화 [17]앰프의 상승으로 인해 오랫동안 사용되지 않았습니다.

1949년: 헬리콥터에 고정된 연산 증폭기.1949년 에드윈 A.골드버그는 헬리콥터에 고정된 연산 [19]증폭기를 설계했다.이 설정에서는 일반 opamp와 함께 opamp와 함께 추가 AC 앰프는 OP 앰프와 함께 사용됩니다.초퍼는 DC 전압과 접지 사이를 빠른 속도(60Hz 또는 400Hz)로 전환하여 DC로부터 AC 신호를 수신합니다.그런 다음 이 신호는 증폭, 정류, 필터링되고 Op Amp의 비반전 입력으로 공급됩니다.이를 통해 출력 드리프트 및 DC 오프셋을 크게 줄이면서 op amp의 이득을 크게 개선했습니다.안타깝게도 헬리콥터를 사용한 디자인은 다른 용도로는 비반전 입력을 사용할 수 없습니다.그럼에도 불구하고 초퍼 안정화 Op Amp의 특성이 크게 개선되었기 때문에 Op Amp를 사용하는 주요 방법이 되었습니다.비반전 입력을 정기적으로 사용하는 기법은 op-amp IC가 현장에 등장하기 시작한 1960년대까지는 그다지 인기가 없었다.

1953년: 시판되는 OP 앰프.1953년 조지 A가 K2-W 모델을 출시하면서 진공관 Op Amp가 상용화되었습니다. Philbrick Researches, 주식회사표시된 디바이스의 명칭인 GAP/R은 완전한 회사 이름의 약자입니다.두 개의 9핀 12AX7 진공 튜브는 8진수 패키지에 장착되었으며, 비반전 입력에 효과적으로 "사용"할 수 있는 모델 K2-P 초퍼 애드온을 사용할 수 있습니다.이 op amp는 1947년 Loebe Julie의 설계에 기초한 것으로, 그 후속 제품과 함께 업계에서 op amp의 광범위한 사용을 시작할 것입니다.

1961: 개별 IC Op Amp.1947년 트랜지스터와 1954년 실리콘 트랜지스터가 탄생하면서 IC의 개념이 실현되었다.1959년 평면 공정의 도입으로 트랜지스터와 IC는 상업적으로 유용하게 쓰일 만큼 안정적이었습니다.1961년에는 솔리드 스테이트의 이산 Op Amp가 생산되었습니다.이들 Op Amp는 엣지 커넥터 등의 패키지가 있는 소형 회로 기판입니다.그들은 보통 전압 오프셋과 드리프트와 같은 것들을 개선하기 위해 손으로 선택한 저항을 가지고 있었다.P45(1961)는 94dB의 이득이 있었으며 ±15V 레일로 주행했습니다.이것은 ±10V 범위의 신호를 처리하기 위한 것입니다.

1961년: 배랙터 브릿지 op 앰프.op-amp 설계에는 여러 가지 방향이 있습니다.Varactor bridge op amp는 1960년대 [20][21]초에 생산되기 시작했습니다.입력 전류가 매우 작도록 설계되었으며, 입력 시 수백 V를 올바르게 처리할 수 있어 공통 모드 제거 측면에서 여전히 사용 가능한 최고의 작동 전류에 속합니다.

1962년: 화분모듈의 연산암페어.1962년까지 여러 회사가 인쇄 회로 [citation needed]기판에 꽂을 수 있는 모듈러 화분 패키지를 생산했습니다.이러한 패키지는 연산 증폭기를 하나의 블랙박스로 만들어 더 큰 회로의 구성요소로 쉽게 취급할 수 있도록 했기 때문에 매우 중요했습니다.

1963년: 일체형 IC OP 앰프.1963년 Fairchild Semiconductor의 Bob Widlar가 설계한 최초의 모노리식 IC op amp인 μA702가 출시되었습니다.모노리식 IC는 칩과 이산 부품(분리형 IC)이 아닌 단일 칩 또는 회로 기판(하이브리드 IC)에 접합 및 접속된 여러 칩으로 구성됩니다.현대의 거의 모든 Op Amp는 모노리식 IC이지만, 이 첫 번째 IC는 큰 성공을 거두지 못했습니다.불균일한 전원 전압, 낮은 이득, 작은 다이내믹 레인지 등의 문제로 인해 1965년[22] μA709(Bob Widlar 설계)가 출시될 때까지 모노리식 Op Amp의 우위가 유지되었습니다.

1968년: μA741 출시.1967년 LM101이 출시되어 다양한 문제가 해결되었고 1968년 μA741이 출시되면서 모노리식 Op Amp의 인기는 더욱 향상되었다.μA741은 Fairchild의 설비로 외부 보상을 필요로 하지 않고 칩 내부에 30pF 보상 캐패시터를 장착할 수 있었다는 점을 제외하면 LM101과 매우 유사했습니다.이 단순한 차이로 인해 741은 표준 Op Amp가 되었고 많은 현대 전류는 741을 기반으로 합니다.μA741은 아직 생산 중이며 전자제품 분야에서 보편적으로 사용되고 있습니다.많은 제조업체가 741을 포함한 부품 번호로 인식 가능한 이 클래식 칩의 버전을 생산하고 있습니다.같은 부품을 여러 회사에서 제조하고 있습니다.

1970년: 최초의 고속, 저입력 전류 FET 설계.1970년대 고속에서는 FET를 사용하여 저입력 전류 설계가 이루어지기 시작했습니다.이것들은 1980년대에 MOSFET로 만들어진 op amp로 대체될 것이다.

1972년: 단측 전원 공급 op 암페어가 생산되고 있습니다.단측 전원 공급 op amp는 입력 및 출력 전압이 음의 전원 공급 전압만큼 낮을 수 있는 전류입니다.그 결과, Op Amp의 음극 전원 핀이 신호 접지에 연결된 상태에서 많은 애플리케이션에서 작동할 수 있으므로 별도의 음극 전원 공급 장치가 필요하지 않습니다.

LM324(1972년 출시)는 쿼드 패키지(1개의 패키지에 4개의 개별 Op Amp)로 제공되어 업계 표준이 되었습니다.1970년대에는 단일 패키지에 여러 개의 Op Amp를 패키징하는 것 외에도 하이브리드 패키지에 Op Amp가 등장했습니다.이들 연산암페어는 일반적으로 기존 일체형 연산암페어의 개량형입니다.모노리식 Op Amp의 특성이 개선됨에 따라, 보다 복잡한 하이브리드 IC는 매우 긴 서비스 수명을 필요로 하는 시스템이나 다른 특수 시스템으로 빠르게 밀려났습니다.

최근 트렌드최근 아날로그 회로의 공급 전압이 감소(디지털 로직과 마찬가지로)하고 있으며 이를 반영하여 저전압 op암페어가 도입되었습니다.일반적으로 5V와 3.3V(경우에 따라서는 1.8V까지 낮아짐)의 전원이 공급됩니다.신호 범위를 최대화하기 위해 현대의 운영 암페어에는 일반적으로 레일 간 출력(출력 신호의 범위는 최저 공급 전압에서 최고) 및 경우에 따라서는 레일 [8]간 입력이 있습니다.

「 」를 참조해 주세요.

메모들

- ^ a b 전원장치 핀S+(VS− 및 V)에는 다양한 방법으로 라벨을 붙일 수 있습니다(IC 전원장치 핀 참조).대부분의 경우 이들 핀은 명확성을 위해 그림에서 제외되며, 전원 구성은 회로에서 설명 또는 가정됩니다.

- ^ 일반적으로 바이폴라 op암페어의 경우 최대 10나노암페어, nA, JFET 입력 스테이지의 경우 수십 피코암페어, pA, MOSFET 입력 스테이지의 경우 소수 pA만 사용합니다.

- ^ 이 정의는 회로의 0 전압 지점에 대한 op-amp 매개 변수 측정 관례에 부합하며, 일반적으로 증폭기의 양 및 음 전원 레일 사이의 총 전압의 절반입니다.

- ^ 이전의 많은 연산 증폭기 설계에서는 오프셋을 수동으로 조정할 수 있도록 오프셋 null 입력이 있습니다.최신 정밀 연산 암페어에는 오프셋 전압을 주기적으로 측정하여 입력 전압에서 빼는 다른 회로나 초퍼를 사용하여 이 오프셋을 자동으로 취소하는 내부 회로가 있을 수 있습니다.

- ^ 출력이 전원 공급기 전압에 도달할 수 없는 것은 일반적으로 앰프의 출력 스테이지 트랜지스터의 한계 때문입니다.출력 단계를 참조하십시오.

- ^ Widlar는 μA702와 μA709에서 동일한 방법을 사용했습니다.

레퍼런스

- ^ "Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs". Maxim Application Note 1108. Archived from the original on 2007-06-26. Retrieved November 10, 2007.

- ^ "Apex OP PA98". Archived from the original on 1 January 2016. Retrieved 8 November 2015.

APEX PA98 Op Amp Modules, Selling Price: $207.51

- ^ Millman, Jacob (1979). Microelectronics: Digital and Analog Circuits and Systems. McGraw-Hill. pp. 523–527. ISBN 0-07-042327-X.

- ^ "Understanding Basic Analog – Ideal Op Amps" (PDF). Archived (PDF) from the original on 2016-12-27.

- ^ "Lecture 5: The ideal operational amplifier" (PDF). Archived (PDF) from the original on 2016-11-23.

- ^ a b Horowitz, Paul; Hill, Winfield (1989). The Art of Electronics. Cambridge, UK: Cambridge University Press. ISBN 0-521-37095-7.

- ^ Stout, D. F. (1976). Handbook of Operational Amplifier Circuit Design. McGraw-Hill. pp. 1–11. ISBN 0-07-061797-X.

- ^ a b c d e "Application of Rail-to-Rail Operational Amplifiers" (PDF). Texas Instruments. Retrieved 2021-06-08.

- ^ "Op Amp Output Phase-Reversal and Input Over-Voltage Protection" (PDF). Analog Devices. 2009. Retrieved 2012-12-27.

- ^ King, Grayson; Watkins, Tim (13 May 1999). "Bootstrapping your op amp yields wide voltage swings" (PDF). Electronic Design News. Retrieved 2012-12-27.[영구 데드링크]

- ^ Lee, Thomas H. (November 18, 2002). "IC Op-Amps Through the Ages" (PDF). Stanford University. Archived (PDF) from the original on October 24, 2012Handout #18: EE214 Fall 2002.

{{cite web}}: CS1 유지보수: 포스트스크립트(링크) - ^ Lu, Liang-Hung. "Electronics 2, Chapter 10" (PDF). National Taiwan University, Graduate Institute of Electronics Engineering. Archived from the original (PDF) on 2014-06-30. Retrieved 2014-02-22.

- ^ "Understanding silicon circuits: inside the ubiquitous 741 op amp". www.righto.com. Archived from the original on 9 October 2017. Retrieved 28 April 2018.

- ^ μA741 연산 증폭기[영구 데드링크]

- ^ 10kΩ의 DC 소스 저항을 통해 1μA의 입력 바이어스 전류가 10mV 오프셋 전압을 생성합니다.다른 입력 바이어스 전류가 동일하고 동일한 소스 저항이 확인되면 두 입력 오프셋 전압이 상쇄됩니다.입력 바이어스 전류와 소스 저항 곱이 작으면 DC 소스 저항의 균형을 맞출 필요가 없을 수 있습니다.

- ^ Analog Devices (2009). "Op Amp Input Bias Current" (PDF). Analog Devices. Tutorial MT-038.

- ^ a b Jung, Walter G. (2004). "Chapter 8: Op Amp History". Op Amp Applications Handbook. Newnes. p. 777. ISBN 978-0-7506-7844-5. Retrieved 2008-11-15.

- ^ Ragazzini, John R.; Randall, Robert H.; Russell, Frederick A. (May 1947). "Analysis of Problems in Dynamics by Electronic Circuits". Proceedings of the IRE. IEEE. 35 (5): 444–452. doi:10.1109/JRPROC.1947.232616. ISSN 0096-8390.

- ^ "Archived copy" (PDF). Archived from the original (PDF) on 2012-10-07. Retrieved 2012-12-27.

{{cite web}}: CS1 maint: 제목으로 아카이브된 복사(링크) - ^ "The Philbrick Archive". www.philbrickarchive.org. Archived from the original on 7 September 2012. Retrieved 28 April 2018.

- ^ 1961년 6월 Philbrick P2 광고,

- ^ Malvino, A. P. (1979). Electronic Principles (2nd ed.). p. 476. ISBN 0-07-039867-4.

추가 정보

- 책들

- 모두를 위한 Op Amps; 제5판; Bruce Carter, Ron Mancini; Newnes; 484페이지; 2017; ISBN 978-0128116487. (영어: PDF 형식 2MB - 초판)

- 오퍼레이션 앰프 - 이론과 설계; 제3판, 요한 휘싱; 스프링거; 423페이지; 2017; ISBN 978-3319281261.

- 연산 증폭기 및 선형 집적회로 - 이론 및 응용; 제3판; James Fiore; Creative Commons; 589페이지; 2016. (13MB PDF 텍스트) (2MB PDF Lab)

- 선형 회로의 분석과 설계; 제8판; 롤랜드 토마스, 앨버트 로사, 그레고리 투생; 와일리; 912페이지; 2016; ISBN 978-119235385.

- 연산 증폭기 및 아날로그 집적회로를 사용한 설계, 제4판, 세르지오 프랑코, 맥그로 힐, 672페이지, 2015년, ISBN 978-0078028168.

- 소형 신호 오디오 디자인, 제2판, Douglas Self, Focial Press, 780페이지, 2014년, ISBN 978-0415709736.

- 리니어 회로 설계 핸드북, 제1판, 행크 줌발렌, 뉴네스, 960페이지, 2008년, ISBN 978-0750687034 (PDF 형식 35 MB)

- OpAmp 응용 프로그램 핸드북; 제1판; Walt Jung; 아날로그 장치 & Newnes; 896 페이지; 2005; ISBN 978-0750678445. (영어: PDF 형식 17 MB)

- 연산 증폭기 및 선형 집적회로, 제6판, 로버트 코글린, 프레드릭 드리스콜, 프렌티스 홀, 529페이지, 2001년, ISBN 978-0130149916.

- 액티브 필터 요리책, 제2판, Don Lancaster, Sams, 240페이지, 1996년, ISBN 978-0750629867 (영어: PDF 형식 28 MB - 초판)

- IC Op-Amp 요리책, 제3판, 월트 융, 프렌티스 홀, 433페이지, 1986년, ISBN 978-0138896010. (영어: PDF 형식 18MB)

- 엔지니어용 미니노트북– OpAmp IC 회선, 제1판, Forrest Mims III, Radio Shack, 49페이지, 1985년, ASIN B000DZG196 (영어: PDF 형식 4MB)

- 직관적인 IC Op Amp - 기본에서 유용한 애플리케이션까지; 제1판, 토마스 프레데릭센; 내셔널 세미컨덕터; 299 페이지; 1984; ISBN 978-997796677.

- Operational Amplifers를 사용한 설계 - 어플리케이션 대체, 제1판, 제랄드 그라임, 버 브라운 & 맥그로 힐, 269페이지, 1976년, ISBN 978-0070238916.

- operational amplifier - 제3세대 테크닉, 제1판, 제랄드 그라임, 버브라운 & 맥그로 힐, 233페이지, 1973년, ISBN 978-0070238909. (PDF 형식 37MB)

- IC 연산 증폭기의 이해; 제1판, Roger Melen 및 Harry Garland; Sams 출판; 128 페이지; 1971; ISBN 978-0672208553. (아카이브)

- operational amplifers - 설계 및 응용, 제1판, 제랄드 그라메, 진 토비, 로렌스 휴엘스먼, 버 브라운 & 맥그로 힐, 473페이지, 1971년, ISBN 978-0070649170.

- opamp 챕터가 있는 책

- 일렉트로닉스 기술 학습 - 실습 랩 코스; 제1판; Thomas Hayes, Paul Horowitz; Cambridge; 1150 페이지; 2016; ISBN 978-0521177238 (제3부는 268 페이지)

- The Art of Electronics; 제3판; Paul Horowitz, Winfield Hill; Cambridge; 1220페이지; 2015; ISBN 978-0521809269. (4장은 69페이지)

- 전기회로의 레슨 - 제3권 - 반도체; 제5판; 토니 쿠팔트; 오픈북 프로젝트; 528페이지; 2009년. (8장은 59페이지) (영어: PDF 형식 4MB)

- 아날로그 회선의 트러블 슈팅: 제1 Ed; 밥 피스; 뉴네스; 217 페이지; 1991; ISBN 978-0750694995 (8장은 19 페이지)

- 아날로그 애플리케이션 매뉴얼, 제1판, 신호학, 418페이지, 1979년. (3장은 32페이지) (PDF 형식 32MB)

외부 링크

- OpAmp 회로 컬렉션 - National Semiconductor Corporation

- Operational Amplifier - 회로에 관한 모든 장

- 루프 게인과 아날로그 회로 성능에 미치는 영향 - 루프 게인, 게인 및 위상 여유, 루프 안정성 소개

- 간단한 OpAmp 측정 오프셋 전압, 오프셋 및 바이어스 전류, 게인, CMRR 및 PSRR을 측정하는 방법

- 오퍼레이션 앰프E. J. Mastascusa(Bucknell University)의 온라인 소개 텍스트.

- 증폭기 회로 단계, 두번째 주문 필터, 하나의 증폭기 bandpass 필터, 간단한 인터폰에 대한 입문서.

- MOS옵 앰프 설계:A튜토리얼 개요

- 작전 폭기 소음 예측(모든 OpAmps)을 사용하여 스폿 잡음.

- 작전 폭기 기본기

- 그 Op-amp의 진공 튜브에 대해부터 2002년까지 역사,.

- 밥 Pease에 의해 Loebe 줄리는 역사적 OpAmp 인터뷰.

- 재료의 자유 보고 – 조지 APhilbrick/방안-작전 폭기 파이오니어에서Www.PhilbrickArchive.org.

- 뭐 운전 Amplifiers 그리고 계측 Amplifiers 사이에 그 차이점은?입니다.전자 디자인 매거진

- 데이터시트/데이터북

- LM301, 싱글 BJT OpAmp, 텍사스 인스트루먼트[영구 데드링크]

- LM324, Quad BJT OpAmp, 텍사스 인스트루먼트

- LM741, 싱글 BJT OpAmp, 텍사스 인스트루먼트

- NE5532, Dual BJT OpAmp, Texas Instruments(NE5534는 유사한 싱글)

- TL072, 듀얼 JFET OpAmp, 텍사스 인스트루먼트(TL074는 쿼드)

(는) 매우 크므로 다음과 같이

(는) 매우 크므로 다음과 같이