PCI 익스프레스

PCI Express| 주변장치 인터커넥트 익스프레스 | |

PCI Express 로고 | |

| 작성년도 | |

|---|---|

| 작성자: | |

| 대체자 | |

| 비트 단위의 너비 | 레인당 1개(최대 16개 레인) |

| No. 장치의 | 각 [a]연결의 각 끝점에 1개씩 있습니다. |

| 스피드 | 이중 단순화(dual simplex); 방향당 단일 레인(x1) 및 16 레인(x16)의 예: |

| 스타일. | 직렬 |

| 핫플러깅인터페이스 | 예(ExpressCard, OCuLink, CFexpress 또는 U.2 포함) |

| 외부 인터페이스 | 예(OCuLink 또는 PCI Express 외부 케이블 사용) |

| 웹사이트 | pcisig |

- PCI 익스프레스 x4

- PCI 익스프레스 x16

- PCI 익스프레스 x1

- PCI 익스프레스 x16

- 기존 PCI(32비트, 5V)

PCI 익스프레스(Peripheral Component Interconnect Express), 공식적으로 PCIe 또는 PCI-e로 [1]약칭되는 PCI 익스프레스(Peripheral Component Interconnect Express)는 고속 직렬 컴퓨터 확장 버스 표준으로, 이전의 PCI, PCI-X 및 AGP 버스 표준을 대체하도록 설계되었습니다.개인용 컴퓨터의 그래픽 카드, 사운드 카드, 하드 디스크 드라이브 호스트 어댑터, SSD, Wi-Fi 및 이더넷 하드웨어 연결을 위한 [2]공통 마더보드 인터페이스입니다.PCIe는 이전 표준보다 더 높은 최대 시스템 버스 처리량, 더 적은 I/O 핀 수 및 더 적은 물리적 설치 공간, 버스 장치에 대한 더 나은 성능 확장, 더 상세한 오류 감지 및 보고 메커니즘(Advanced Error Reporting,[3] AER), 기본 핫 스왑 기능 등 많은 개선점을 가지고 있습니다.PCIe 표준의 최신 개정판에서는 I/O 가상화에 대한 하드웨어 지원을 제공합니다.

PCI Express 전기 인터페이스는 동시 [4]레인 개수로 측정됩니다. (레인은 단일 데이터 송수신 라인입니다.그 비유는 양방향으로 교통량이 많은 고속도로입니다.)이 인터페이스는 다양한 다른 표준에도 사용됩니다. 특히 ExpressCard라고 불리는 노트북 확장 카드 인터페이스가 대표적입니다.SATA Express, U.2(SFF-8639) 및 M.2의 스토리지 인터페이스에서도 사용됩니다.

포맷 사양은 PCI-SIG(PCI Special Interest Group)에 의해 유지 및 개발됩니다. 이 그룹은 기존 PCI 사양도 유지하는 900개 이상의 회사로 구성되어 있습니다.

건축학

흰색 "접합 상자"는 PCI Express 장치 다운스트림 포트를 나타내며 회색은 업스트림 [5]: 7 포트를 나타냅니다.

개념적으로 PCI 익스프레스 버스는 이전 PCI/PCI-X [7]버스를 고속 직렬로 대체한 것입니다.PCI Express 버스와 이전 PCI 간의 주요 차이점 중 하나는 버스 토폴로지입니다. PCI는 공유 병렬 버스 아키텍처를 사용하여 PCI 호스트와 모든 디바이스가 공통 주소, 데이터 및 제어 라인 집합을 공유합니다.이와 달리 PCI Express는 점대점 토폴로지를 기반으로 하며, 별도의 직렬 링크가 모든 장치를 루트 콤플렉스(호스트)에 연결합니다.이전 PCI 버스에 대한 액세스는 공유 버스 토폴로지 때문에 (여러 마스터의 경우) 중재되고 한 번에 하나의 마스터로 단일 방향으로 제한됩니다.또한, 오래된 PCI 클록킹 방식은 버스 트랜잭션과 관련된 장치에 관계없이 버스 클럭을 버스에서 가장 느린 주변 장치로 제한합니다.반면 PCI Express 버스 링크는 여러 엔드포인트 간의 동시 액세스에 고유한 제한이 없이 모든 두 엔드포인트 간의 전이중 통신을 지원합니다.

버스 프로토콜 측면에서 PCI 익스프레스 통신은 패킷 단위로 캡슐화되어 있습니다.데이터 및 상태 메시지 트래픽을 패킷화 및 탈패킷화하는 작업은 PCI Express 포트의 트랜잭션 계층(후술)에서 처리합니다.전기 신호와 버스 프로토콜의 급격한 차이로 인해 다른 기계적 폼 팩터와 확장 커넥터(따라서 새로운 마더보드와 새로운 어댑터 보드)를 사용해야 합니다. PCI 슬롯과 PCI Express 슬롯은 상호 교환할 수 없습니다.소프트웨어 수준에서 PCI Express는 PCI와의 하위 호환성을 유지합니다. 기존 PCI 시스템 소프트웨어는 PCI Express 표준을 명시적으로 지원하지 않아도 새로운 PCI Express 장치를 감지하고 구성할 수 있습니다.

두 장치 사이의 PCI Express 링크의 크기는 1레인에서 16레인까지 다양합니다.다중 레인 링크에서 패킷 데이터는 레인에 걸쳐 스트라이프되고, 피크 데이터 처리량은 전체 링크 폭과 함께 확장됩니다.차선 수는 장치 초기화 중에 자동으로 협상되며 두 끝점 중 하나에 의해 제한될 수 있습니다.예를 들어, 단일 레인 PCI Express(x1) 카드를 멀티 레인 슬롯(x4, x8 등)에 삽입할 수 있으며, 초기화 주기는 상호 지원되는 가장 높은 레인 카운트를 자동으로 조정합니다.링크는 차선을 적게 사용하도록 동적으로 다운 구성할 수 있어 차선이 잘못되거나 신뢰할 수 없는 경우 장애 허용 오차를 제공합니다.PCI Express 표준은 x1, x2, x4, x8, x16의 링크 폭을 정의합니다.PCIe 5.0, x12 및 x32 링크까지 정의되었지만 사용된 [8]적은 없습니다.따라서 PCI Express 버스는 높은 처리량이 필요하지 않은 비용에 민감한 애플리케이션과 3D 그래픽, 네트워킹(10기가비트 이더넷 또는 멀티포트 기가비트 이더넷), 엔터프라이즈 스토리지(SAS 또는 파이버 채널)와 같은 성능에 중요한 애플리케이션을 모두 지원할 수 있습니다.슬롯과 커넥터는 다음으로 큰 물리적 슬롯 크기를 사용하여 링크 너비를 사이에 두고 이러한 너비의 하위 집합에 대해서만 정의됩니다.

참고로, 4개의 레인(x4)을 사용하는 PCI-X(133 MHz 64비트) 장치와 PCI Express 1.0 장치는 대략 1064 MB/s의 동일한 피크 단방향 전송 속도를 갖습니다.PCI Express 버스는 여러 장치가 동시에 데이터를 전송하는 경우 또는 PCI Express 주변 장치와의 통신이 양방향인 경우 PCI-X 버스보다 성능이 뛰어날 가능성이 있습니다.

인터커넥트

PCI Express 장치는 인터커넥터[9] 링크(interconnector link)라는 논리적 연결을 통해 통신합니다.링크는 두 PCI Express 포트 간의 점대점 통신 채널로, 두 포트 모두 일반적인 PCI 요청(구성, I/O 또는 메모리 읽기/쓰기)과 인터럽트(INTX, MSI 또는 MSI-X)를 주고받을 수 있습니다.물리적 수준에서 링크는 하나 이상의 [9]차선으로 구성됩니다.저속 주변 장치(802.11 Wi-Fi 카드 등)는 단일 레인(x1) 링크를 사용하는 반면, 그래픽 어댑터는 일반적으로 훨씬 더 넓고 따라서 더 빠른 16 레인(x16) 링크를 사용합니다.

레인

레인은 두 개의 차동 신호 쌍으로 구성되며, 하나의 쌍은 데이터를 수신하기 위한 것이고 다른 하나는 전송하기 위한 것입니다.따라서 각 차선은 4개의 와이어 또는 신호 트레이스로 구성됩니다.개념적으로, 각 레인은 전이중 바이트 스트림으로 사용되며,[10] 링크의 엔드포인트 간에 양방향으로 동시에 8비트 "바이트" 형식으로 데이터 패킷을 전송합니다.물리적 PCI Express 링크는 1,[11][5]: 4, 5 [9] 4, 8 또는 16 레인을 포함할 수 있습니다.차선 수는 "x" 접두사로 작성되며(예: "x8"은 8차선 카드 또는 슬롯을 나타냄), x16은 일반적으로 [12]사용되는 가장 큰 크기입니다.차선 크기는 "너비" 또는 "별"이라는 용어를 통해서도 언급됩니다. 예를 들어, 8차선 슬롯은 "별 8차선" 또는 "별 8차선"으로 언급될 수 있습니다.

기계식 카드 크기는 아래를 참조하십시오.

직렬버스

본딩된 직렬 버스 아키텍처는 반이중 동작, 초과 신호 수, 그리고 본질적으로 타이밍 스큐(timing skew)로 인한 대역폭 감소를 포함하는 후자의 고유한 한계 때문에 기존의 병렬 버스보다 선택되었습니다.타이밍 스큐는 서로 다른 길이의 도체, 잠재적으로 서로 다른 인쇄 회로 기판(PCB) 층을 통과하며 서로 다른 신호 속도로 이동하는 병렬 인터페이스 내에서 별도의 전기 신호로 인해 발생합니다.병렬 인터페이스의 신호는 하나의 단어로 동시에 전송되지만 이동 시간이 다르며 목적지에 도착하는 시간도 다릅니다.인터페이스 클럭 주기가 신호 도착 사이의 가장 큰 시간 차이보다 짧으면 전송된 워드의 복구가 더 이상 불가능합니다.병렬 버스를 통한 시간 왜곡은 수 나노초에 달할 수 있기 때문에, 결과적인 대역폭 제한은 수백 메가헤르츠 범위에 있습니다.

직렬 인터페이스는 각 레인 내에서 각 방향에 하나의 차동 신호만 존재하기 때문에 타이밍 스큐가 나타나지 않으며, 직렬 신호 자체 내에 클록킹 정보가 내장되어 있기 때문에 외부 클록 신호가 없습니다.이와 같이 직렬 신호에 대한 일반적인 대역폭 제한은 멀티 기가헤르츠 범위에 있습니다.PCI Express는 병렬 버스를 직렬 인터커넥트로 대체하는 일반적인 추세의 한 예이며, 다른 예로는 직렬 ATA(SATA), USB, 직렬 연결 SCSI(SAS), FireWire(IEEE 1394), Rapid 등이 있습니다.IO. 디지털 비디오에서 일반적으로 사용되는 예로는 DVI, HDMI, DisplayPort 등이 있습니다.

다채널 직렬 설계는 속도가 느린 장치를 위해 더 적은 레인을 할당할 수 있는 기능으로 유연성을 높입니다.

폼팩터

PCI Express(표준)

PCI Express 카드는 물리적 크기 이상의 슬롯(x16을 가장 크게 사용)에는 적합하지만 작은 PCI Express 슬롯에는 적합하지 않을 수 있습니다. 예를 들어 x16 카드는 x4 또는 x8 슬롯에는 적합하지 않을 수 있습니다.일부 슬롯은 개방형 소켓을 사용하여 물리적으로 더 긴 카드를 허용하고 최상의 전기적 및 논리적 연결을 협상합니다.

슬롯에 실제로 연결된 레인 수는 실제 슬롯 크기에서 지원하는 레인 수보다 적을 수도 있습니다.예를 들어 x4에서 실행되는 x16 슬롯은 x1, x2, x4, x8 또는 x16 카드를 모두 사용할 수 있지만 4개의 레인만 제공합니다.사양은 "x16(x4 모드)"로 읽을 수 있지만, "기계 @전기" 표기법(예: "x16 @ x4")도 [citation needed]일반적입니다.이러한 슬롯은 전체 전송 속도를 지원하는 마더보드 하드웨어 없이도 더 많은 범위의 PCI Express 카드를 수용할 수 있다는 장점이 있습니다.표준 기계적 크기는 x1, x4, x8, x16입니다.표준 기계적 크기 이외의 여러 레인을 사용하는 카드는 다음으로 큰 기계적 크기에 물리적으로 맞춰야 합니다(예: x2 카드는 x4 크기를 사용하거나 x12 카드는 x16 크기를 사용).

카드 자체는 다양한 크기로 디자인되고 제작됩니다.예를 들어 PCI Express 카드 형태로 제공되는 솔리드 스테이트 드라이브(SSD)는 [14][15]카드의 물리적 치수를 설명하기 위해 HHHL(하프 높이, 하프 길이)과 FHHHL(풀 높이, 하프 길이)을 사용하는 경우가 많습니다.

| PCI 카드 종류 | 치수 높이 × 길이 × 너비, 최대 | |

|---|---|---|

| (mm) | (인) | |

| 전체 길이 | 111.15 × 312.00 × 20.32 | 4.376 × 12.283 × 0.8 |

| 하프-길이 | 111.15 × 167.65 × 20.32 | 4.376 × 6.600 × 0.8 |

| 낮은 프로파일/낮음 | 068.90 x 167.65 x 20.32 | 2.731 × 6.600 × 0.8 |

비표준 비디오 카드 폼 팩터

게임 비디오 카드가 수백 와트의 [17]열을 방출하는 경우가 종종 있기 때문에, 더 유능하고 더 조용한 냉각 팬이 필요하기 때문에 (2012년[16] 경 이후) 현대의 게임 비디오 카드는 대개 PCI Express 표준에 명시된 높이와 두께를 초과합니다.현대의 컴퓨터 케이스는 종종 이러한 큰 카드를 수용하기 위해 더 넓지만, 항상 그렇지는 않습니다.풀 길이 카드(312mm)는 흔하지 않기 때문에 현대적인 경우에는 해당 카드에 맞지 않는 경우가 있습니다.이러한 카드의 두께는 일반적으로 2개의 PCIe 슬롯의 공간을 차지합니다.실제로 카드를 측정하는 방법도 공급업체마다 다르며, 금속 브래킷 크기를 치수로 포함하는 업체도 있고 그렇지 않은 업체도 있습니다.

예를 들어, 2020년에 출시된 세 개의 고급 비디오 카드를 비교하면 사파이어 Radeon RX 5700 XT 카드의 높이는 135mm(금속 브래킷 제외)로 PCIe 표준 높이를 28mm 초과합니다.[18] XFX의 또 다른 Radeon RX 5700 XT 카드의 두께는 55mm(20.32mm의 2.7 PCI 슬롯)로 3개의 PCIe [19]슬롯을 차지하는 반면 Asus GeForce RT는X 3080 비디오 카드는 2개의 슬롯을 차지하며 크기는 318.5mm x 140.1mm x 57.8mm로 PCI 익스프레스의 최대 길이, 높이 및 두께를 [20]각각 초과합니다.

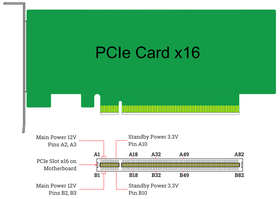

핀아웃

다음 표는 PCI Express 카드에서 에지 커넥터의 각 면에 있는 도체를 나타냅니다.인쇄회로기판(PCB)의 솔더측은 A측이며, 부품측은 [21]B측입니다.PRSNT1# 및 PRSNT2# 핀은 핫 플러그가 장착된 카드를 완전히 삽입하려면 나머지 핀보다 약간 짧아야 합니다.WAKE# 핀은 컴퓨터를 웨이크업 시키기 위해 최대 전압을 사용하지만, 대기 전력에서 높게 당겨야 카드가 웨이크업 [22]할 수 있음을 나타냅니다.

| 핀 | 사이드 B | 사이드 A | 묘사 | 핀 | 사이드 B | 사이드 A | 묘사 | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12V | PRSNT1# | 가장 먼 PRSNT2# 핀에 연결해야 함 | 50 | HSOP(8) | 예약된 | 8번 레인에서 데이터를 전송합니다. + 그리고 - | |

| 2 | +12V | +12V | 주 전원핀 | 51 | HSON(8) | 땅 | ||

| 3 | +12V | +12V | 52 | 땅 | HSIP(8) | 8번 레인에서 데이터 수신, + 및 - | ||

| 4 | 땅 | 땅 | 53 | 땅 | HSin(8) | |||

| 5 | SMCLK | TCK | SMBus 및 JTAG 포트 핀 | 54 | HSOP(9) | 땅 | 9번 레인에서 데이터를 전송합니다. + 그리고 - | |

| 6 | SMDAT | TDI | 55 | HSON(9) | 땅 | |||

| 7 | 땅 | TDO | 56 | 땅 | HSIP(9) | 9번 레인은 데이터를 수신하고 +와 - | ||

| 8 | +3.3V | TMS | 57 | 땅 | HSin(9) | |||

| 9 | TRST# | +3.3V | 58 | HSOP(10) | 땅 | 10번 레인에서 데이터를 전송합니다. + 그리고 - | ||

| 10 | +3.3 Vaux | +3.3V | 보조전원 및 대기전원 | 59 | HSON(10) | 땅 | ||

| 11 | WAKE# | PERST# | 링크 재활성화, 기본 재설정 | 60 | 땅 | HSIP(10) | 10번 레인은 +와 - 데이터를 수신합니다. | |

| 키노치 | 61 | 땅 | HSin(10) | |||||

| 12 | CLKREQ#[24] | 땅 | 시계 요청 신호 | 62 | HSOP(11) | 땅 | 11번 레인에서 데이터를 전송합니다. +와 - | |

| 13 | 땅 | REFCLK+ | 기준 시계 차동 쌍 | 63 | HSON(11) | 땅 | ||

| 14 | HSOP(0) | REFCLK− | 0번 레인은 데이터를 전송하며 +와 - | 64 | 땅 | HSIP(11) | 11번 레인은 +와 - 데이터를 수신합니다. | |

| 15 | HSON(0) | 땅 | 65 | 땅 | HSin(11) | |||

| 16 | 땅 | HSIP(0) | 차선 0은 데이터를 수신하며 + 및 - | 66 | HSOP(12) | 땅 | 12번 레인에서 데이터를 전송합니다. + 그리고 - | |

| 17 | PRSNT2# | HSin(0) | 67 | HSON(12) | 땅 | |||

| 18 | 땅 | 땅 | 68 | 땅 | HSIP(12) | 12번 레인은 데이터를 수신하고 +와 - | ||

| PCI Express x1 카드는 핀 18에서 끝납니다. | 69 | 땅 | HSin(12) | |||||

| 19 | HSOP(1) | 예약된 | 1번 레인에서 데이터를 전송합니다. + 및 - | 70 | HSOP(13) | 땅 | 13번 레인에서 데이터를 전송합니다. + 그리고 - | |

| 20 | HSON(1) | 땅 | 71 | HSON(13) | 땅 | |||

| 21 | 땅 | HSIP(1) | 1번 레인은 + 및 - 데이터를 수신합니다. | 72 | 땅 | HSIP(13) | 13번 레인은 데이터를 수신하고 +와 - | |

| 22 | 땅 | HSin(1) | 73 | 땅 | HSin(13) | |||

| 23 | HSOP(2) | 땅 | 2번 레인에서 데이터를 전송합니다. + 및 - | 74 | HSOP(14) | 땅 | 14번 레인에서 데이터를 전송합니다. +와 - | |

| 24 | HSON(2) | 땅 | 75 | HSON(14) | 땅 | |||

| 25 | 땅 | HSIP(2) | 2번 레인은 + 및 - 데이터를 수신합니다. | 76 | 땅 | HSIP(14) | 14번 레인은 데이터를 수신하고 +와 - | |

| 26 | 땅 | HSin(2) | 77 | 땅 | HSin(14) | |||

| 27 | HSOP(3) | 땅 | 3번 레인에서 데이터를 전송합니다. + 및 - | 78 | HSOP(15) | 땅 | 15번 레인에서 데이터를 전송합니다. + 그리고 - | |

| 28 | HSON(3) | 땅 | 79 | HSON(15) | 땅 | |||

| 29 | 땅 | HSIP(3) | 3번 레인은 + 및 - 데이터를 수신합니다. "파워 브레이크", 장치 전력을 줄이기 위해 액티브-로우 | 80 | 땅 | HSIP(15) | 15번 레인은 +와 - 데이터를 수신합니다. | |

| 30 | PWRBRK#[25] | HSin(3) | 81 | PRSNT2# | HSin(15) | |||

| 31 | PRSNT2# | 땅 | 82 | 예약된 | 땅 | |||

| 32 | 땅 | 예약된 | ||||||

| PCI Express x4 카드는 핀 32에서 끝납니다. | ||||||||

| 33 | HSOP(4) | 예약된 | 4번 레인은 데이터를 전송합니다. +와 - | |||||

| 34 | HSON(4) | 땅 | ||||||

| 35 | 땅 | HSIP(4) | 4번 레인은 +와 - 데이터를 수신합니다. | |||||

| 36 | 땅 | HSin(4) | ||||||

| 37 | HSOP(5) | 땅 | 5번 레인에서 데이터를 전송합니다. + 그리고 - | |||||

| 38 | HSON(5) | 땅 | ||||||

| 39 | 땅 | HSIP(5) | 5번 레인에서 데이터를 수신합니다. + 및 - | |||||

| 40 | 땅 | HSin(5) | ||||||

| 41 | HSOP(6) | 땅 | 6번 레인은 데이터를 전송합니다. +와 - | |||||

| 42 | HSON(6) | 땅 | ||||||

| 43 | 땅 | HSIP(6) | 6번 레인은 데이터를 수신합니다. + 및 - | 전설 | ||||

| 44 | 땅 | HSin(6) | 접지핀 | 영전압 기준 | ||||

| 45 | HSOP(7) | 땅 | 7번 레인은 데이터를 전송합니다. +와 - | 전원핀 | PCIe 카드에 전원을 공급합니다. | |||

| 46 | HSON(7) | 땅 | 카드 대 호스트 핀 | 카드에서 마더보드로 보내는 신호 | ||||

| 47 | 땅 | HSIP(7) | 7번 레인은 +와 - 데이터를 수신합니다. | 호스트-카드 핀 | 마더보드에서 카드로 보내는 신호 | |||

| 48 | PRSNT2# | HSin(7) | 배수구 개방 | 낮게 당겨지거나 여러 카드에 의해 감지될 수 있음 | ||||

| 49 | 땅 | 땅 | 센스핀 | 카드에서 함께 묶임 | ||||

| PCI Express x8 카드는 핀 49에서 끝납니다. | 예약된 | 현재사용하지않음,연결하지않음 | ||||||

힘

모든 PCI 익스프레스 카드는 +3.3V(9.9W)에서 최대 3A를 소비할 수 있습니다.폼 팩터와 [26]: 35–36 [27][28]카드의 역할에 따라 +12V와 총 전력 소모량이 달라집니다.

- x1 카드는 +12V(6W)와 10W를 합하면 0.5A로 제한됩니다.

- x4 이상의 카드는 +12V(25W)와 25W를 합하면 2.1A로 제한됩니다.

- 초기화 및 고출력 장치로 소프트웨어를 구성한 후 풀사이즈 x1 카드는 최대 25W 제한을 적용할 수 있습니다.

- 초기화 및 고출력 [22]: 38–39 장치로 소프트웨어를 구성한 후 풀사이즈 x16 그래픽 카드는 +12V(66W) 및 75W 결합 시 최대 5.5A를 그릴 수 있습니다.

옵션 커넥터는 75W(6핀) 또는 150W(8핀)의 +12V 전력을 추가하여 총 300W(2 × 75W + 1 × 150W)까지 사용할 수 있습니다.

- Sense0 핀은 케이블 또는 전원 공급 장치를 통해 접지에 연결되거나 케이블이 연결되지 않은 경우 보드에 플로팅됩니다.

- Sense1 핀은 케이블 또는 전원 공급 장치를 통해 접지에 연결되거나 케이블이 연결되지 않은 경우에는 보드에 플로팅됩니다.

일부 카드는 두 개의 8핀 커넥터를 사용하지만 2018년 현재[update] 표준화되지 않았기 때문에 공식 PCI Express 로고를 부착하지 않아야 합니다.이 구성은 총 375W(1 × 75W + 2 × 150W)를 허용하며 PCI Express 4.0 [needs update]표준과 함께 PCI-SIG로 표준화될 가능성이 높습니다.8핀 PCI Express 커넥터는 주로 SMP 및 멀티 코어 시스템에 전원을 공급하는 데 사용되는 EPS12V 커넥터와 혼동될 수 있습니다.전원 커넥터는 Mollex Mini-Fit Jr. 시리즈 [30]커넥터의 변형 모델입니다.

| 핀 | 암/수용체 PS 케이블로 | 남/직각 PCB의 헤더 |

|---|---|---|

| 6핀 | 45559-0002 | 45558-0003 |

| 8핀 | 45587-0004 | 45586-0005, 45586-0006 |

| 6핀 전원 커넥터(75W)[31] | 8핀 전원 커넥터(150W)[32][33][34] | ||||

|---|---|---|---|---|---|

| 핀 | 묘사 | 핀 | 묘사 | ||

| 1 | +12V | 1 | +12V | ||

| 2 | 연결되지 않음(보통 +12V도 있음) | 2 | +12V | ||

| 3 | +12V | 3 | +12V | ||

| 4 | 센스1(8핀[A] 연결) | ||||

| 4 | 땅 | 5 | 땅 | ||

| 5 | 감각 | 6 | Sense0(6핀 또는 8핀 연결) | ||

| 6 | 땅 | 7 | 땅 | ||

| 8 | 땅 | ||||

- ^ 6핀 커넥터를 8핀 리셉터클에 연결하면 분실된 Sense1에서 카드가 최대 75W만 사용할 수 있음을 알립니다.

PCI Express 미니 카드

PCI Express를 기반으로 하는 PCI Express Mini Card(Mini PCI Express, Mini PCIe, Mini PCI-E, mPCIe 및 PEM이라고도 함)는 Mini PCI 폼 팩터를 대체하는 제품입니다.PCI-SIG에 의해 개발되었습니다.호스트 디바이스는 PCI Express 및 USB 2.0 연결을 모두 지원하며 각 카드는 표준 중 하나를 사용할 수 있습니다.2005년 이후에 만들어진 대부분의 노트북 컴퓨터들은 확장 카드에 PCI Express를 사용하지만, 2015년 현재 많은[update] 공급업체들이 이 목적을 위해 더 새로운 M.2 폼 팩터를 사용하고 있습니다.

PCI Express Mini Card는 치수가 다르기 때문에 표준 풀 사이즈 PCI Express 슬롯과 물리적으로 호환되지 않지만 풀 사이즈 [35]슬롯에서 사용할 수 있는 패시브 어댑터가 존재합니다.

물리적 치수

PCI Express 미니 카드의 치수는 풀 미니 카드의 경우 30mm x 50.95mm(가로×세로)입니다.52핀 에지 커넥터가 있으며, 0.8mm 피치에 2개의 엇갈린 행으로 구성되어 있습니다.각 행에는 8개의 연락처가 있고, 4개의 연락처에 해당하는 간격이 있으며, 그 다음에는 추가로 18개의 연락처가 있습니다.보드의 두께는 구성품을 제외하고 1.0mm입니다.또한 "하프 미니 카드"(Half Mini Card)(HMC라고도 약칭됨)가 지정되어 있으며, 물리적 길이의 약 절반인 26.8mm입니다.

전기적 인터페이스

PCI Express Mini Card 에지 커넥터는 여러 개의 연결과 버스를 제공합니다.

- PCI Express x1(SMus 포함)

- USB 2.0

- 컴퓨터 섀시의 무선 네트워크(예: Wi-Fi) 상태를 진단하기 위한 와이어 투 진단 LED

- GSM 및 WCDMA 응용 프로그램을 위한 SIM 카드(스펙 상 UIM 신호)

- 다른 PCIe 레인에 대한 향후 확장

- 1.5V 및 3.3V 전원

Mini-SATA(mSATA) 변종

Mini PCI Express 폼 팩터를 공유하지만 mSATA 슬롯이 반드시 Mini PCI Express와 전기적으로 호환되는 것은 아닙니다.이러한 이유로 특정 노트북만 mSATA 드라이브와 호환됩니다.대부분의 호환되는 시스템은 휴런 리버 플랫폼을 사용하는 인텔의 샌디 브릿지 프로세서 아키텍처를 기반으로 합니다.2011년 3~4월에 출시된 Lenovo의 ThinkPad T, W 및 X 시리즈와 같은 노트북은 WWAN 카드 슬롯에 mSATA SSD 카드를 지원합니다.씽크패드 엣지 E220s/E420s, 레노버 아이디어패드 Y460/Y560/Y570/Y580 등도 mSATA를 [36]지원합니다.반대로 L 시리즈는 WWAN 슬롯의 PCIe 표준을 사용하여 M.2 카드만 지원할 수 있습니다.

일부 노트북(특히 Asus Eee PC, Apple MacBook Air, Dell mini9 및 mini10)은 SSD로 PCI Express Mini Card의 변형을 사용합니다.이 변형 모델은 예약 핀과 예약 핀을 사용하여 SATA 및 IDE 인터페이스 패스스루를 구현하고 USB, 접지 라인 및 때로는 코어 PCIe x1 버스만 [37]그대로 유지합니다.따라서 넷북용으로 판매되는 "miniPCIe" 플래시 및 솔리드 스테이트 드라이브는 진정한 PCI Express Mini 구현과 거의 호환되지 않습니다.

또한 일반적인 Asus miniPCIe SSD의 길이는 71mm이므로 Dell 51mm 모델이 종종 (잘못) 하프 길이로 언급되기도 합니다.실제 51 mm Mini PCIe SSD는 2009년에 발표되었으며, 두 개의 적층된 PCB 레이어가 있어 더 높은 스토리지 용량을 제공합니다.발표된 디자인은 PCIe 인터페이스를 보존하여 표준 미니 PCIe 슬롯과 호환됩니다.작동하는 제품은 아직 개발되지 않았습니다.

Intel은 일반적으로 mSATA SSD를 지원하지 않는 PCIe x1 Mini-Card 슬롯이 있는 수많은 데스크톱 보드를 보유하고 있습니다.PCIe x1 미니 카드 슬롯(일반적으로 SATA 포트로 다중화됨)에서 mSATA를 기본적으로 지원하는 데스크톱 보드 목록은 Intel Support [38]사이트에 제공됩니다.

PCI 익스프레스 M.2

M.2는 mSATA 표준과 Mini PCIe를 [39]대체합니다.M.2 커넥터를 통해 제공되는 컴퓨터 버스 인터페이스는 PCI Express 3.0(최대 4개 레인), 직렬 ATA 3.0 및 USB 3.0(후단 두 개 각각에 대해 단일 논리 포트)입니다.원하는 호스트 지원 수준과 디바이스 유형에 따라 지원할 인터페이스를 선택하는 것은 M.2 호스트 또는 디바이스 제조업체의 몫입니다.

PCI Express 외부 케이블

PCI 익스프레스 외부 케이블 (외부 PCI 익스프레스, 케이블 PCI 익스프레스, 또는 ePCIe라고도 함) 사양은 2007년 [40][41]2월에 PCI-SIG에 의해 출시되었습니다.

x1, x4, x8 및 x16 링크 폭에 대해 표준 케이블 및 커넥터가 정의되었으며, 전송 속도는 레인당 250MB/s입니다.PCI-SIG는 또한 PCI Express 2.0에서와 같이 표준이 500MB/s에 이를 수 있도록 진화할 것으로 예상하고 있습니다.Cabled PCI Express의 사용 예로는 다수의 PCIe 슬롯과 PCIe-to-ePCIe 어댑터 회로가 포함된 금속 인클로저가 있습니다.ePCIe 사양이 없었다면 이 장치는 사용할 수 없었을 것입니다.

PCI Express OCuLink

OCuLink(구리의 화학 기호는 Cu이므로 "광동 링크"의 약자)는 썬더볼트 3와 경쟁하기 위해 설계된 PCI 익스프레스의 케이블 버전의 확장입니다.2015년 10월에 출시된 OCuLink 버전 1.0은 구리 케이블을 통해 최대 4개의 PCIe 3.0 레인(8GT/s(초당 기가 전송), 3.9GB/s)을 지원합니다. 향후 광섬유 버전이 등장할 수도 있습니다.

OCuLink-2의 가장 최신 버전인 OCuLink-2는 최대 16GB/s(PCIe 4.0 x8)[42]를 지원하며 최대 속도 Thunderbolt 4 케이블의 최대 대역폭은 5GB/s입니다.일부 공급업체는 차선당 32GT/s로 작동하는 차세대 PCI Express 5.0을 지원하도록 커넥터 제품을 설계하여 향후 몇 [42]년간 개발 비용을 최소화할 수 있습니다.

OCuLink는 처음에는 강력한 외부 GPU 박스를 연결하기 위해 노트북에 사용하려고 했지만, 주로 서버의 PCIe 상호 연결에 사용되는 [43]것이 인기입니다.

파생형

수많은 다른 폼 팩터들이 PCIe를 사용하거나 사용할 수 있습니다.여기에는 다음이 포함됩니다.

- 낮은 높이의 카드

- Express Card: PC Card 폼 팩터의 후속 제품(x1 PCIe 및 USB 2.0 포함, 핫 플러그 지원)

- PCI Express Express 모듈:서버 및 워크스테이션용으로 정의된 핫플러그형 모듈러 폼 팩터

- XQD 카드: CompactFlash Association에서 x2 PCIe를 지원하는 PCI Express 기반 플래시 카드 표준

- CFExpress 카드: CompactFlash Association에서 제공하는 PCIe 레인 1~4개를 지원하는 폼 팩터 3개로 구성된 PCI Express 기반 플래시 카드

- SD 카드:SD 사양 버전 7.0에 도입된 SD Express 버스는 x1 PCIe 링크를 사용합니다.

- XMC: CMC/PMC 폼 팩터와 유사(VITA 42.3)

- 고급TCA: 컴팩트를 보완하는 제품대규모 애플리케이션용 PCI, 직렬 기반 백플레인 토폴로지 지원

- AMC: 어드밴스드의 보완물TCA 사양. ATCA 보드(x1, x2, x4 또는 x8 PCIe)에서 프로세서 및 I/O 모듈을 지원합니다.

- 피쳐Pak:내장형 및 소형 폼팩터 애플리케이션을 위한 소형 확장 카드 포맷(43mm x 65mm). 고밀도 커넥터에 두 개의 x1 PCIe 링크와 USB, I2C, 최대 100포인트의 I/O를 구현합니다.

- 유니버설 IO: 슈퍼 마이크로 컴퓨터 주식회사에서 변형된 제품으로, 로우 프로파일 랙 장착 [44]섀시에 사용할 수 있도록 설계되었습니다.커넥터 브래킷이 반대로 되어 있어 일반 PCI Express 소켓에는 들어갈 수 없지만 핀 호환이 가능하며 브래킷을 제거하면 삽입할 수 있습니다.

- M.2 (이전 명칭: NGFF)

- M-PCIE는 M-PHY 물리 [45][46]계층을 통해 PCIe 3.0을 태블릿 및 스마트폰과 같은 모바일 장치에 제공합니다.

- U.2 (이전 이름은 SFF-8639)

PCIe 슬롯 커넥터는 PCIe 이외의 프로토콜도 운반할 수 있습니다.일부 9xx 시리즈 Intel 칩셋은 지원되는 추가 기능을 사용하여 슬롯을 사용하여 PCIe 대신 호스트 CPU의 통합 그래픽에서 비디오 신호를 전송하는 독점 기술인 Serial Digital Video Out을 지원합니다.

PCIe 트랜잭션 계층 프로토콜은 전기적으로 PCIe가 아닌 다른 인터커넥트를 통해서도 사용할 수 있습니다.

- Thunderbolt: Mini DisplayPort와 호환되는 폼 팩터에 DisplayPort와 PCIe 프로토콜을 결합한 Intel의 로열티 없는 인터커넥트 표준입니다.Thunderbolt 3.0 또한 USB 3.1을 결합하고 Mini DisplayPort가 아닌 USB-C 폼 팩터를 사용합니다.

- USB4

이력 및 수정사항

개발 초기에 PCIe는 처음에는 HSI(High Speed Interconnect용)로 불렸고 3GIO(3세대 I/O용)로 이름을 바꾼 뒤 PCI-SIG 명칭인 PCI Express에 정착했습니다.아라파호 작업 그룹(AWG)이라는 이름의 기술 작업 그룹이 이 표준을 만들었습니다.초기 초안의 경우, AWG는 인텔 엔지니어들로만 구성되었고, 이후 AWG는 산업 파트너들로 확장되었습니다.

그 이후로 PCIe는 몇 번의 크고 작은 수정을 거쳤고, 성능과 다른 기능들을 개선했습니다.

비교표

| 버전 | 도입부- 연역의 | 라인코드 | 갈아타다 평가하다 | 처리량[i][iii] | |||||

|---|---|---|---|---|---|---|---|---|---|

| x1 | x2 | x4 | x8 | x16 | |||||

| 1.0 | 2003 | NRZ | 8b/10b | 2.5GT/s | 0.250GB/s | 0.500GB/s | 1.000 GB/s | 2.000 GB/s | 4.000 GB/s |

| 2.0 | 2007 | 5.0 GT/s | 0.500GB/s | 1.000 GB/s | 2.000 GB/s | 4.000 GB/s | 8.000 GB/s | ||

| 3.0 | 2010 | 128b/130b | 8.0 GT/s | 0.985 GB/s | 1.969 GB/s | 3.938GB/s | 7.877 GB/s | 15.754 GB/s | |

| 4.0 | 2017 | 16.0 GT/s | 1.969 GB/s | 3.938GB/s | 7.877 GB/s | 15.754 GB/s | 031.508GB/s | ||

| 5.0 | 2019 | 32.0 GT/s | 3.938GB/s | 7.877 GB/s | 15.754 GB/s | 31.508GB/s | 63.015 GB/s | ||

| 6.0 | 2022 | PAM-4 FEC | 1b/1b 242B/256B FLIT | 64.0 GT/s 32.0 GBd | 7.563GB/s | 15.125GB/s | 30.250GB/s | 60.500GB/s | 121.000 GB/s |

| 7.0 | 2025 (예정) | 128.0 GT/s 64.0 GBd | 15.125GB/s | 30.250GB/s | 60.500GB/s | 121.000 GB/s | 242.000 GB/s | ||

- 메모들

PCI Express 1.0a

PCI-SIG는 2003년에 250 MB/s의 레인당 데이터 전송 속도와 2.5 GT/s의 전송 속도를 가진 PCIe 1.0a를 발표했습니다.

전송 횟수에 추가 처리량을 제공하지 않는 오버헤드 비트가 포함되어 있기 때문에 전송 속도는 초당 비트 수가 아닌 초당 전송 수로 표현됩니다. PCIe 1.x는 8b/10b 인코딩 방식을 사용하므로 원시 채널 대역폭에서 20%(= 2/10) 오버헤드가 발생합니다.따라서 PCIe 용어에서 전송 속도는 인코딩된 비트 전송 속도를 나타냅니다. 인코딩된 시리얼 링크에서 2.5 GT/s는 2.5 Gbps입니다.이는 2.0Gbps의 사전 코딩된 데이터 또는 250MB/s에 해당하며, 이를 PCIe에서는 처리량이라고 합니다.

PCI 익스프레스 1.1

2005년 PCI-SIG는 PCIe 1.1을 선보였습니다.이 업데이트된 사양에는 설명과 몇 가지 개선 사항이 포함되어 있지만 PCI Express 1.0a와 완벽하게 호환됩니다.데이터 속도에 변경된 내용이 없습니다.

PCI 익스프레스 2.0

PCI-SIG는 2007년 [52]1월 15일 PCI Express Base 2.0 사양의 가용성을 발표했습니다.PCIe 2.0 표준은 PCIe 1.0~5GT/s에 비해 전송 속도를 두 배로 높였으며 레인당 처리량은 250MB/s에서 500MB/s로 증가했습니다.따라서 16레인 PCIe 커넥터(x16)는 최대 8GB/s의 총 처리량을 지원할 수 있습니다.

PCIe 2.0 마더보드 슬롯은 PCIe v1.x 카드와 완전히 이전 버전으로 호환됩니다.PCIe 2.0 카드는 PCIe 1.x 마더보드와 역호환이 가능하며, PCI Express 1.1의 대역폭을 사용합니다.전반적으로 v2.0용으로 설계된 그래픽 카드 또는 마더보드가 작동하며 나머지 하나는 v1.1 또는 v1.0a입니다.

PCI-SIG는 또한 PCIe 2.0이 점대점 데이터 전송 프로토콜과 소프트웨어 [53]아키텍처를 개선했다고 밝혔습니다.

인텔의 최초의 PCIe 2.0 지원 칩셋은 X38이었고 보드는 2007년 [54]10월 21일부터 다양한 벤더(Abit, Asus, Gigabyte)로부터 출하되기 시작했습니다.AMD는 AMD 700 칩셋 시리즈로 PCIe 2.0을 지원하기 시작했고 nVidia는 MCP72로 [55]시작했습니다.인텔 P35 칩셋을 포함한 인텔의 모든 이전 칩셋은 PCIe 1.1 또는 1.[56]0a를 지원했습니다.

1.x와 마찬가지로 PCIe 2.0도 8b/10b 인코딩 방식을 사용하므로 5GT/s 원시 데이터 전송 속도에서 최대 레인당 4기가비트/s의 전송 속도를 제공합니다.

PCI 익스프레스 2.1

PCI Express 2.1(사양은 2009년 3월 4일)은 PCI Express 3.0에서 완전한 구현을 위해 계획된 관리, 지원 및 문제 해결 시스템의 대부분을 지원합니다.그러나 속도는 PCI Express 2.0과 동일합니다.슬롯의 전력 증가로 인해 PCI Express 2.1 카드와 1.0/1.0a를 사용하는 일부 구형 마더보드 간의 하위 호환성이 손상되지만 PCI Express 1.1 커넥터를 사용하는 대부분의 마더보드는 PCIe 2.1을 사용하는 카드의 하위 호환성을 지원하기 위해 유틸리티를 통해 제조업체에서 BIOS 업데이트를 제공합니다.

PCI 익스프레스 3.0

PCI Express 3.0 Base 사양 리비전 3.0은 여러 번의 지연 끝에 2010년 11월에 출시되었습니다.2007년 8월, PCI-SIG는 PCI Express 3.0이 초당 8기가 전송(GT/s)의 비트 전송 속도를 전달할 것이며, 기존 PCI Express 구현과 하위 호환성을 가질 것이라고 발표했습니다.그 때 PCI Express 3.0의 최종 사양이 [57]2010년 2분기로 미뤄질 것이라고 발표되기도 했습니다.PCI Express 3.0 사양의 새로운 기능에는 송신기와 수신기의 균등화, PLL 향상, 클록 데이터 복구, 현재 지원되는 [58]토폴로지의 채널 향상 등 시그널링 및 데이터 무결성 향상을 위한 여러 가지 최적화 기능이 포함되었습니다.

PCI Express 인터커넥트 대역폭 확장 가능성에 대한 6개월간의 기술적 분석 결과, PCI-SIG의 분석 결과, 메인스트림 실리콘 공정 기술에서 초당 8기가바이트의 전송을 제조할 수 있었으며, 기존의 저가 재료 및 인프라스트럭처와 함께 구축할 수 있었습니다.PCI Express 프로토콜 스택과 완벽한 호환성(영향은 무시)을 유지하는 동시에

PCI Express 3.0은 이전 8b/10b 인코딩에서 128b/130b로 인코딩 방식을 업그레이드하여 대역폭 오버헤드를 PCI Express 2.0의 20%에서 약 1.54%(= 2/130)로 줄였습니다.PCI Express 3.0의 8GT/s 비트 전송률은 차선당 985MB/s를 효과적으로 제공하여 PCI Express 2.[48]0에 비해 차선 대역폭을 거의 두 배로 늘렸습니다.

2010년 11월 18일, PCI 특별 관심 그룹은 이 [59]새로운 버전의 PCI 익스프레스를 기반으로 디바이스를 구축하기 위해 최종 PCI 익스프레스 3.0 규격을 회원들에게 공식적으로 발표했습니다.

PCI 익스프레스 3.1

2013년 9월, PCI Express 3.1 사양은 2013년 말 또는 2014년 초에 출시될 것으로 발표되었으며, 발표된 PCI Express 3.0 사양에 대한 다양한 개선 사항을 전력 관리, 성능 및 [46][60]기능의 세 가지 영역에서 통합했습니다.2014년 [61]11월에 개봉했습니다.

PCI Express 4.0

2011년 11월 29일, PCI-SIG는 PCI 익스프레스 4.[62]0을 발표하였는데, 16레인 구성을 위해 각 방향에서 PCI 익스프레스 3.0에서 31.5 GB/s로 제공되는 대역폭을 두 배로 증가시키는 동시에 소프트웨어 지원과 사용된 기계적 인터페이스 [63]모두에서 역방향 및 순방향 호환성을 유지하는 16 GT/s 비트 전송률을 제공합니다.PCI Express 4.0 사양은 Thunderbolt의 대안인 OCuLink-2를 제공합니다.OCuLink 버전 2는 최대 16GT/s(x8 [42]레인의 경우 총 16GB/s)이며 Thunderbolt 3 링크의 최대 대역폭은 5GB/s입니다.

2016년 6월, PLDA와 Synopsys는 PCIe 4.0 물리 계층, 컨트롤러, 스위치 및 기타 IP 블록을 PCI SIG [64]연례 개발자 회의에서 시연했습니다.

Mellanox Technologies는 2016년 [65]6월 15일 PCIe 4.0을 탑재한 최초의 100 Gbit/s 네트워크 어댑터를 발표하였고,[66] 2016년 11월 10일 PCIe 4.0을 탑재한 최초의 200 Gbit/s 네트워크 어댑터를 발표하였습니다.

2016년 8월, 시놉시스는 인텔 개발자 포럼에서 PCIe 4.0 속도의 차선을 기록하는 FPGA의 테스트 설정을 발표했습니다.그들의 IP는 2016년 [67]말에 그들의 칩과 제품을 발표할 계획인 몇몇 회사들에게 허가를 받았습니다.

2016년 8월 IEEE Hot Chips Symposium에서 IBM은 PCIe 4.0을 지원하는 최초의 CPU POWER9을 [68][69]발표했습니다.

PCI-SIG는 2017년 [70]6월 8일 최종 PCI 익스프레스 4.0 사양의 출시를 공식 발표했습니다.사양에는 유연성, 확장성 및 저전력의 향상이 포함됩니다.

2017년 12월 5일, IBM은 최초의 PCIe 4.0 슬롯 시스템인 Power AC922를 [71][72]발표했습니다.

NETINT Technologies는 Flash Memory[73] Summit 2018에 앞서 2018년 7월 17일 PCIe 4.0을 기반으로 한 최초의 NVMe SSD를 선보였습니다.

AMD는 2019년 1월 9일에 출시 예정인 젠 2 기반 프로세서와 X570 칩셋이 PCIe 4.[74]0을 지원할 것이라고 발표했습니다. AMD는 구형 칩셋에 대한 부분적인 지원을 가능하게 하기를 희망했지만 메인보드 트레이스가 PCIe 4.0 사양을 준수하지 않음으로 인한 불안정성이 [75][76]불가능하게 만들었습니다.

인텔은 2020년 중반 Tiger [77]Lake 마이크로아키텍처의 일환으로 PCI Express 4.0을 지원하는 첫 모바일 CPU를 출시했습니다.

PCI Express 5.0

2017년 6월, PCI-SIG는 PCI Express 5.0 예비 [70]사양을 발표했습니다.대역폭은 32GT/s로 증가하여 16레인 구성에서 각 방향으로 63GB/s를 산출할 것으로 예상되었습니다.규격 초안은 [citation needed]2019년에 표준화될 것으로 예상되었습니다.처음에는 25.0 GT/s도 기술적 실현 가능성을 고려했습니다.

2017년 6월 7일 PCI-SIG DevCon에서 시놉시스는 32 GT/[78]s에서 PCI 익스프레스 5.0의 첫 시연을 녹화했습니다.

2018년 5월 31일, PLDA는 Xpress의 이용 가능성을 발표했습니다.당일 PCIe 5.0 규격 초안 0.7을 기반으로 [79][80]한 RICH5 PCIe 5.0 컨트롤러 IP.

2018년 12월 10일, PCI SIG는 PCIe 5.0 규격의 버전 0.9를 [81]회원들에게 공개했고, 2019년 1월 17일, PCI SIG는 버전 0.9가 비준되었으며 2019년 [82]1분기에 버전 1.0이 출시될 예정이라고 발표했습니다.

2019년 5월 29일, PCI-SIG는 최종 PCI 익스프레스 5.0 [83]사양의 출시를 공식 발표했습니다.

2019년 11월 20일, 장쑤 화쿤은 최초의 PCIe 5.0 컨트롤러 HC9001을 12nm 제조 공정으로 [84]선보였습니다.생산은 2020년에 시작되었습니다.

2020년 8월 17일, IBM은 PCIe 5.0과 싱글칩 모듈(SCM)당 최대 32레인, 더블칩 모듈(DCM)[85]당 최대 64레인을 갖춘 파워10 프로세서를 발표했습니다.

2021년 9월 9일, IBM은 Power E1080 Enterprise 서버를 출시 [86]예정일을 9월 17일로 발표했습니다.최대 16개의 Power10 SCM과 시스템당 최대 32개의 슬롯을 가질 수 있으며, 이는 PCIe 5.0 x8 또는 PCIe 4.0 x16 [87]역할을 할 수 있습니다.또는 외부 PCIe 확장 드로어에 연결하는 옵션 광 CXP 컨버터 어댑터용 PCIe 5.0 x16 슬롯으로 사용할 수도 있습니다.

2021년 10월 27일, 인텔은 12세대 인텔 코어 CPU 제품군을 발표하였는데, 이는 PCIe 5.0([88]최대 16레인) 연결을 갖춘 세계 최초의 소비자용 x86-64 프로세서입니다.

2022년 3월 22일 엔비디아는 세계 최초의 PCIe 5.0 [89]GPU인 엔비디아 호퍼 GH100 GPU를 발표했습니다.

2022년 5월 23일, AMD는 소비자 플랫폼에서 최대 24 레인의 PCIe 5.0 연결을 지원하는 Zen 4 아키텍처를 발표했습니다.[90][91]

PCI Express 6.0

2019년 6월 18일, PCI-SIG는 PCI 익스프레스 6.0 사양 개발을 발표했습니다.대역폭은 64GT/s로 증가하여 16레인 구성에서 각 방향으로 128GB/s를 산출할 것으로 예상되며,[92] 목표 출시일은 2021년입니다.새 표준은 NRZ([93]Non-Return-to-Zero) 변조 대신 저지연 순방향 오류 수정(FEC)이 있는 4단계 펄스 진폭 변조(PAM-4)를 사용합니다.이전 PCI Express 버전과 달리 순방향 에러 정정 기능을 사용하여 데이터 무결성을 높이고 PAM-4를 라인 코드로 사용하여 전송당 2비트씩 전송합니다.64 GT/s의 데이터 전송 속도(raw bit rate)로 x16 [92]구성에서는 각 방향으로 최대 121 GB/s까지 가능합니다.

2020년 2월 24일, PCI 익스프레스 6.0 버전 0.5 사양([94]모든 아키텍처 측면과 요구 사항이 정의된 "최초 초안")이 공개되었습니다.

2020년 11월 5일, PCI 익스프레스 6.0 버전 0.7 사양([95]테스트 칩을 통해 검증된 전기 사양을 포함한 "완전한 초안")이 공개되었습니다.

2021년 10월 6일, PCI 익스프레스 6.0 버전 0.9 사양([96]최종안)이 공개되었습니다.

2022년 1월 11일, PCI-SIG는 최종 PCI 익스프레스 6.0 [97]사양의 출시를 공식 발표했습니다.

PAM-4 부호화는 10(이전의 10에−12 비해)의−6 매우 높은 비트 오류율(BER)을 초래하므로 128b/130b 부호화 대신 주기적 중복성 검사(CRC)에 3-way 인터레이스 포워드 에러 정정(FEC)을 사용합니다.고정된 256바이트 FLIT(Flow Control Unit) 블록은 가변 크기 트랜잭션 레벨 패킷(TLP) 및 데이터 링크 계층 페이로드(DLLP)를 포함한 242바이트의 데이터를 전달하며, 나머지 14바이트는 8바이트 CRC 및 6바이트 FEC를 위해 예약됩니다.[98][99] 3-way 그레이 코드는 오류율을 줄이기 위해 PAM-4/FLIT 모드에서 사용되며, 인터페이스는 데이터율을 [100][101]낮추기 위해 재교육할 때에도 NRZ 및 128/130b 인코딩으로 전환되지 않습니다.

PCI Express 7.0

2022년 6월 21일, PCI-SIG는 PCI 익스프레스 7.0 [102]사양 개발을 발표했습니다.버전 6.0과 동일한 PAM4 시그널링을 사용하여 128 GT/s의 원시 비트 전송률과 방향당 최대 242 GB/s를 x16 구성으로 제공합니다.신호 손실을 줄이고 전력 효율을 향상시키기 위해 채널 파라미터를 미세 조정함으로써 데이터 전송률을 두 배로 증가시킬 것이지만, 신호 무결성은 어려운 과제가 될 것으로 예상됩니다.규격은 2025년에 확정될 것으로 예상됩니다.

확장 및 향후 방향

일부 공급업체는 PCIe 확장 [106][87]드로어에서 거리를 늘린 PCIe 스위칭을 위한 액티브 광케이블(AOC)과 함께 파이버 [103][104][105]제품을 통해 PCIe를 제공하거나, 투명 PCIe 브리징이 이를 지원하기 위해 추가 소프트웨어가 필요할 수 있는 더 메인스트림 표준(예: InfiniBand 또는 Ethernet)을 사용하는 것보다 더 나은 경우에 제공합니다.

Thunderbolt는 Intel과 Apple이 DisplayPort와 논리적 PCIe 링크를 결합한 범용 고속 인터페이스로 공동 개발했으며 원래는 모든 파이버 인터페이스로 의도되었지만 소비자 친화적인 파이버 인터커넥트를 만드는 초기의 어려움 때문에 거의 모든 구현이 구리 시스템입니다.눈에 띄는 예외인 Sony VAIOZ VPC-Z2는 광학 부품이 내장된 비표준 USB 포트를 사용하여 선외기 PCIe 디스플레이 어댑터에 연결합니다.Apple은 2011년까지 Thunderbolt를 채택한 주요 동인이었지만 다른 여러[107] 공급업체는 Thunderbolt를 포함한 새로운 제품 및 시스템을 발표했습니다.Thunderbolt 3은 USB4 표준의 기본을 이룹니다.

모바일 PCIe 사양(약칭: M-PCIe)을 통해 PCI Express 아키텍처는 MIPI Alliance의 M-PHY 물리 계층 기술을 통해 작동할 수 있습니다.M-PHY를 이미 광범위하게 채택하고 저전력 설계를 기반으로 하는 Mobile PCIe는 모바일 장치가 PCI Express를 [108]사용할 수 있도록 합니다.

초안공정

PCI-SIG [109]규격에는 5가지 기본 릴리스/체크포인트가 있습니다.

- 초안 0.3 (개념): 이번 릴리스는 세부 사항이 거의 없을 수 있지만 일반적인 접근 방식과 목표를 요약합니다.

- 초안 0.5(초안): 이번 릴리스에는 아키텍처 요구사항이 완벽하게 포함되어 있으며 0.3 초안에 명시된 목표를 완전히 해결해야 합니다.

- 초안 0.7 (완전한 초안): 이 릴리스에는 일련의 기능적 요구 사항과 방법이 정의되어 있어야 하며, 이 릴리스 이후에는 사양에 새로운 기능이 추가될 수 없습니다.이 초안을 공개하기 전에 테스트 실리콘을 통해 전기 사양을 확인해야 합니다.

- 초안 0.9(최종안): 이 릴리스를 통해 PCI-SIG 회원사는 지적 재산권에 대한 내부 검토를 수행할 수 있으며, 이 초안 이후에는 기능 변경이 허용되지 않습니다.

- 1.0 (최종 릴리스): 최종 및 최종 사양이며, 변경 또는 개선 사항은 각각 Errata 문서 및 ECN(Engineering Change Notice)을 통해 이루어집니다.

역사적으로, 새로운 PCIe 규격의 최초 채택자들은 일반적으로 새로운 대역폭 정의를 중심으로 자신의 애플리케이션 로직을 자신 있게 구축할 수 있고, 때로는 모든 새로운 프로토콜 기능에 대한 개발을 시작할 수 있기 때문에 Draft 0.5로 설계를 시작합니다.그러나 초안 0.5 단계에서는 실제 PCIe 프로토콜 계층 구현이 변경될 가능성이 여전히 크기 때문에 내부적으로 이러한 블록을 개발하는 책임이 있는 설계자는 외부 소스의 인터페이스 IP를 사용하는 설계자보다 작업을 시작하는 것이 더 망설여질 수 있습니다.

하드웨어 프로토콜 요약

PCIe 링크는 레인이라고 알려진 직렬(1비트) 점대점 연결의 전용 단방향 커플을 기반으로 구축됩니다.이는 모든 장치가 동일한 양방향, 32비트 또는 64비트 병렬 버스를 공유하는 버스 기반 시스템인 이전의 PCI 연결과는 극명한 대조를 이룹니다.

PCI Express는 트랜잭션 계층, 데이터 링크 계층 및 물리 계층으로 구성된 계층화된 프로토콜입니다.데이터 링크 계층은 MAC(Media Access Control) 하위 계층을 포함하도록 세분화됩니다.물리 계층은 논리 계층과 전기 계층으로 세분화됩니다.물리 논리-하위 계층에는 물리적 코딩 하위 계층(PCS)이 포함되어 있습니다.이 용어들은 IEEE 802 네트워킹 프로토콜 모델에서 차용한 것입니다.

물리층

| 레인즈 | 핀 | 길이 | ||

|---|---|---|---|---|

| 총 | 변수 | 총 | 변수 | |

| x1 | 2x18 = 036 | = 014 | 25mm | .65mm |

| x4 | 2x32 = 064 | 2x21 = 042 | 39mm | 21.65mm |

| x8 | 2x49 = 098 | 2x38 = 076 | 56mm | 38.65mm |

| x16 | 2×82 = 164 | 2×71 = 142 | 89mm | 71.65mm |

PCIe 물리 계층(PHY, PCIEPHY, PCI Express PHY 또는 PCIe PHY) 사양은 전기적 및 논리적 사양에 대응하여 두 개의 하위 계층으로 구분됩니다.논리 서브레이어는 때때로 MAC 서브레이어와 PCS로 더 나뉘기도 하지만, 이 분할은 공식적으로 PCIe 규격의 일부가 아닙니다.PCI Express용 PHY 인터페이스(PIPE)[111]인 Intel이 발표한 규격은 MAC/PCS 기능 분할과 이 두 하위 계층 간의 인터페이스를 정의합니다.PIPE 규격은 직렬화기/병렬화기(SerDes) 및 기타 아날로그 회로를 포함하는 물리적 미디어 부착(PMA) 계층도 식별합니다. 그러나 SerDes 구현은 ASIC 공급업체마다 크게 다르기 때문에 PIPE는 PCS와 PMA 간의 인터페이스를 지정하지 않습니다.

전기 수준에서 각 차선은 협상된 능력에 따라 2.5, 5, 8, 16 또는 32 Gbit/s로 작동하는 두 개의 단방향 차동 쌍으로 구성됩니다.전송과 수신은 별개의 차동 쌍으로, 레인당 총 4개의 데이터 와이어에 대해 수행됩니다.

임의의 두 PCIe 장치 사이의 연결을 링크(link)라고 하며, 하나 이상의 레인으로 구성됩니다.모든 장치는 단일 레인(x1) 링크를 최소한으로 지원해야 합니다.장치는 [112][113]최대 32개의 레인으로 구성된 더 넓은 링크를 선택적으로 지원할 수 있습니다.이를 통해 두 가지 측면에서 매우 우수한 호환성을 확보할 수 있습니다.

- PCIe 카드는 적어도 크기만큼 큰 슬롯에 물리적으로 들어맞고 올바르게 작동합니다(예: x1 크기의 카드는 어떤 크기의 슬롯에서도 작동합니다).

- 물리적 크기가 큰 슬롯(예: x16)은 더 큰 물리적 슬롯 크기에 필요한 접지 연결만 제공하면 더 적은 레인(예: x1, x4, x8 또는 x12)으로 전기적으로 배선할 수 있습니다.

두 경우 모두 PCIe는 상호 지원되는 가장 높은 수의 레인을 협상합니다.많은 그래픽 카드, 마더보드 및 BIOS 버전이 동일한 연결에서 x1, x4, x8 및 x16 연결을 지원하는 것으로 확인되었습니다.

PCIe 커넥터의 너비는 8.8mm이고 높이는 11.25mm이며 길이는 가변적입니다.커넥터의 고정구간은 길이가 11.65mm이며 각각 11핀씩 2열씩(총 22핀) 포함되어 있으며, 나머지 구간의 길이는 차선 수에 따라 가변적입니다.핀은 1mm 간격으로 배치되어 있으며, 커넥터에 들어가는 카드의 두께는 1.[114][115]6mm입니다.

데이터전송

PCIe는 인터럽트를 포함한 모든 제어 메시지를 데이터에 사용되는 동일한 링크를 통해 전송합니다.직렬 프로토콜은 절대로 차단할 수 없기 때문에 지연 시간은 전용 인터럽트 라인이 있는 기존 PCI와 비교해도 손색이 없습니다.핀 기반 인터럽트의 IRQ 공유 문제와 MSI(Message Signaled Interrupt)가 I/O APIC를 우회하여 CPU에 직접 전달될 수 있다는 점을 고려하면 MSI 성능이 크게 향상됩니다.

다중 레인 링크를 통해 전송되는 데이터는 인터리빙되며, 이는 연속되는 각 바이트가 연속 레인 아래로 전송됨을 의미합니다.PCIe 규격에서는 이 인터리빙을 데이터 스트라이핑이라고 합니다.수신 스트라이프 데이터를 동기화(또는 디스큐)하려면 하드웨어 복잡성이 크게 필요하지만 스트라이프를 사용하면 링크에서 n바이트의th 지연 시간을 크게 줄일 수 있습니다.차선이 긴밀하게 동기화되지는 않지만 2.5/5/8 GT/s에 대해 차선 대 차선 스큐가 20/8/6ns로 제한되어 있어 하드웨어 버퍼가 줄무늬 [117]데이터를 다시 정렬할 수 있습니다.패딩(padding) 요구 사항으로 인해, 스트라이핑이 반드시 링크 상의 작은 데이터 패킷의 지연 시간을 줄이지는 않을 수도 있습니다.

다른 높은 데이터 전송 속도의 직렬 전송 프로토콜과 마찬가지로, 클럭은 신호에 내장됩니다.물리적 수준에서 PCI Express 2.0은 8b/10b 인코딩[48] 방식(라인 코드)을 사용하여 연속적으로 동일한 숫자(0 또는 1)의 문자열이 길이로 제한되도록 합니다.이 코딩은 수신기가 비트 에지가 어디에 있는지에 대한 트랙을 잃는 것을 방지하기 위해 사용되었습니다.이 코딩 방식에서는 8개의 (코딩되지 않은) 페이로드 비트마다 10개의 (인코딩된) 전송 데이터로 대체되어 전기 대역폭에 20%의 오버헤드가 발생합니다.사용 가능한 대역폭을 개선하기 위해 PCI Express 버전 3.0은 128b/130b 인코딩(오버헤드 1.54%)을 대신 사용합니다.라인 인코딩은 데이터 스트림에서 동일한 자릿수 문자열의 실행 길이를 제한하고 수신기가 클럭 복구를 통해 송신기에 동기화된 상태를 유지하도록 보장합니다.

데이터 스트림에서 0과 1비트의 바람직한 균형(따라서 스펙트럼 밀도)은 피드백 토폴로지에서 데이터 스트림에 대해 "스크램블러"로서 알려진 이진 다항식을 XOR함으로써 달성됩니다.스크램블링 다항식이 알려져 있기 때문에 XOR을 두 번째로 적용하여 데이터를 복구할 수 있습니다.스크램블링 및 디스크램블링 단계는 모두 하드웨어로 수행됩니다.

데이터 링크 계층

데이터 링크 계층은 PCIe 링크에 대해 다음과 같은 세 가지 중요한 서비스를 수행합니다.

- 트랜잭션 계층에 의해 생성된 트랜잭션 계층 패킷(TLP)의 순서를 정합니다.

- 승인되지 않은/불량 TLP의 재생을 명시적으로 요구하는 승인 프로토콜(ACK 및 NAK 시그널링)을 통해 두 엔드포인트 간에 TLP의 신뢰성 있는 전달을 보장합니다.

- 플로우 제어 크레딧 초기화 및 관리

송신측에서, 데이터 링크 계층은 각각의 송신 TLP에 대한 증분 시퀀스 번호를 생성합니다.전송되는 각 TLP에 대한 고유한 식별 태그 역할을 하며, 송신 TLP의 헤더에 삽입됩니다.각각의 송신 TLP의 끝에는 (본 문맥에서는 Link CRC 또는 LCRC로 알려진) 32 비트의 순환 중복 체크 코드도 부가됩니다.

수신측에서, 수신된 TLP의 LCRC 및 시퀀스 번호는 모두 링크 계층에서 확인됩니다.LCRC 검사에 실패하거나(데이터 오류를 나타냄), 시퀀스 번호가 범위를 벗어나는 경우(마지막으로 수신한 유효한 TLP와 연속적이지 않음), 불량 TLP는 물론 불량 TLP 이후에 수신한 모든 TLP는 무효로 간주되어 폐기됩니다.수신기는 잘못된 TLP의 시퀀스 번호가 포함된 부정적 확인 메시지(NAK)를 전송하여 해당 시퀀스 번호로 전달된 모든 TLP의 재전송을 요청합니다.수신된 TLP가 LCRC 검사를 통과하고 정확한 시퀀스 번호를 가진 경우 유효한 것으로 처리됩니다.링크 수신기는 시퀀스 번호(마지막으로 수신된 양호한 TLP를 추적함)를 증가시키고 유효한 TLP를 수신기의 트랜잭션 계층에 전달합니다.원격 송신기로 ACK 메시지가 전송되어 TLP가 성공적으로 수신되었음을 알립니다(확장하면 과거 시퀀스 번호를 가진 모든 TLP).

송신기가 NAK 메시지를 수신하거나 타임아웃 기간이 만료될 때까지 승인(NAK 또는 ACK)이 수신되지 않으면, 송신기는 긍정적인 승인(ACK)이 없는 모든 TLP를 재전송해야 합니다.전송 프로토콜이 신뢰할 수 없는 매체를 통해 TLP의 전달을 보장하기 때문에, 장치 또는 전송 매체의 지속적인 오작동을 막으면, 링크 계층은 트랜잭션 계층에 신뢰할 수 있는 연결을 제공합니다.

데이터 링크 계층은 트랜잭션 계층에서 생성된 TLP를 송수신할 뿐만 아니라 데이터 링크 계층 패킷(DLLP)을 생성 및 소비합니다.ACK 및 NAK 신호는 DLLP를 통해 전달되며, 일부 전력 관리 메시지 및 흐름 제어 크레딧 정보도 트랜잭션 계층을 대신하여 전달됩니다.

실제로, 링크에서 승인되지 않은 기내 TLP의 수는 두 가지 요소로 제한됩니다. 송신기의 재생 버퍼의 크기(원격 수신기가 ACK를 수신할 때까지 전송된 모든 TLP의 복사본을 저장해야 함)와 수신기가 송신기에 발급하는 흐름 제어 크레딧.PCI Express는 모든 수신기가 최소 크레딧 수를 발행하도록 요구하며, 링크를 통해 PCIconfig TLP와 메시지 TLP를 전송할 수 있도록 보장합니다.

트랜잭션 계층

PCI Express는 분할 트랜잭션(요청과 응답이 시간별로 구분된 트랜잭션)을 구현하여 대상 디바이스가 응답에 대한 데이터를 수집하는 동안 링크가 다른 트래픽을 전달할 수 있도록 합니다.

PCI Express는 크레딧 기반 플로우 제어를 사용합니다.이 방식에서, 디바이스는 트랜잭션 계층에서 수신된 각 버퍼에 대한 초기 크레딧 양을 광고합니다.링크의 반대쪽 끝에 있는 장치는 이 장치로 트랜잭션을 전송할 때 각 TLP가 계정에서 소비하는 크레딧 수를 계산합니다.송신 장치는 소비된 신용 횟수가 신용 한도를 초과하지 않는 경우에만 TLP를 송신할 수 있습니다.수신 장치는 버퍼로부터 TLP의 처리를 완료하면, 송신 장치에 크레딧의 반환을 시그널링하고, 이는 복원된 양만큼 크레딧 한도를 증가시킵니다.크레딧 카운터는 모듈식 카운터이며 소비된 크레딧과 크레딧 한도를 비교하려면 모듈식 산술이 필요합니다.(대기 상태 또는 핸드셰이크 기반 전송 프로토콜과 같은 다른 방법과 비교할 때) 이 방식의 장점은 신용 한도가 충족되지 않는 한 신용 수익의 지연 시간이 성능에 영향을 미치지 않는다는 것입니다.각 장치가 적절한 버퍼 크기로 설계된 경우 이 가정은 일반적으로 충족됩니다.

PCIe 1.x는 종종 각 방향에서 레인당 250MB/s의 데이터 전송 속도를 지원하는 것으로 인용됩니다.이 수치는 물리적 신호 전송 속도(2.5기가바이트)를 인코딩 오버헤드(바이트당 10비트)로 나눈 값입니다.즉, 이론적으로 16 레인(x16) PCIe 카드는 각 방향으로 16x250 MB/s = 4 GB/s가 가능합니다.이것은 데이터 바이트 측면에서는 옳지만, 보다 의미 있는 계산은 사용 가능한 데이터 페이로드 속도를 기반으로 하며, 이는 상위 레벨(소프트웨어) 애플리케이션 및 중간 프로토콜 레벨의 기능인 트래픽의 프로파일에 따라 달라집니다.

다른 높은 데이터 전송 속도 직렬 인터커넥트 시스템과 마찬가지로, PCIe는 추가적인 전송 강건성(CRC 및 승인)으로 인해 프로토콜 및 처리 오버헤드를 가집니다.고성능 스토리지 컨트롤러에서 일반적으로 전송되는 것과 같은 긴 연속 단방향 전송은 PCIe의 원시(레인) 데이터 전송률의 95%에 육박할 수 있습니다.또한 이러한 환승은 차선 수 증가(x2, x4 등)로 인해 가장 큰 이점을 얻을 수 있습니다.그러나 보다 일반적인 애플리케이션(예: USB 또는 이더넷 컨트롤러)에서 트래픽 프로파일은 강제 [118]승인이 자주 발생하는 짧은 데이터 패킷으로 특징지어집니다.이러한 트래픽 유형은 패킷 구문 분석 및 강제 인터럽트(장치의 호스트 인터페이스 또는 PC의 CPU)로 인한 오버헤드로 인해 링크의 효율성을 저하시킵니다.동일한 인쇄 회로 기판에 연결된 장치를 위한 프로토콜이므로 장거리 통신을 위한 프로토콜과 동일한 전송 오류에 대한 허용 오차를 요구하지 않으므로 이러한 효율성 손실은 PCIe에만 해당되지 않습니다.

링크의 효율성

"네트워크와 같은" 통신 링크의 경우, "원시" 대역폭의 일부는 프로토콜 [119]오버헤드에 의해 소비됩니다.

예를 들어 PCIe 1.x 레인은 250MB/s(simplex)의 물리 계층 위에서 데이터 전송 속도를 제공합니다.이것은 페이로드 대역폭이 아니라 물리 계층 대역폭입니다. PCIe 레인은 완전한 [119]기능을 위해 추가 정보를 운반해야 합니다.

| 층 | PHY | 데이터 링크 계층 | 거래. | 데이터 링크 계층 | PHY | ||

|---|---|---|---|---|---|---|---|

| 데이터. | 시작 | 순서 | 머리글 | 페이로드 | ECRC | CCRC | 끝. |

| 크기(바이트) | 1 | 2 | 12 또는 16 | 0 ~ 4096 | 4 (옵션) | 4 | 1 |

그러면 [clarification needed][citation needed]Gen2 오버헤드는 트랜잭션당 20, 24 또는 28바이트가 됩니다.

| 층 | G3 PHY | 데이터 링크 계층 | 트랜잭션 계층 | 데이터 링크 계층 | ||

|---|---|---|---|---|---|---|

| 데이터. | 시작 | 순서 | 머리글 | 페이로드 | ECRC | CCRC |

| 크기(바이트) | 4 | 2 | 12 또는 16 | 0 ~ 4096 | 4 (옵션) | 4 |

그러면 [clarification needed][citation needed]Gen3 오버헤드는 트랜잭션당 22, 26, 30바이트가 됩니다.

128 바이트 페이로드의 패킷 = + Efficiency}}={\{\는 86%이며 1024 바이트 페이로드의 경우 98%입니다.레지스터 설정(4바이트)과 같은 작은 액세스의 경우 효율성이 16%[citation needed]까지 떨어집니다.

MPS(Maximum Payload Size)는 체인의 모든 장치에서 가장 작은 최대값을 기준으로 모든 장치에서 설정됩니다.장치 하나에 128바이트의 MPS가 있는 경우 트리의 모든 장치는 MPS를 128바이트로 설정해야 합니다.이 경우 버스는 [119]: 3 쓰기 효율이 86%에 달합니다.

적용들

PCI Express는 소비자, 서버 및 산업용 애플리케이션에서 마더보드 수준의 인터커넥트(마더보드 장착 주변 장치를 연결하는 데 사용), 패시브 백플레인 인터커넥트 및 애드인 보드용 확장 카드 인터페이스로 작동합니다.

소비자 노트북과 데스크톱에서 엔터프라이즈 데이터 서버에 이르기까지 사실상[update] 모든 최신 PC에서 PCIe 버스는 기본 마더보드 수준의 인터커넥트 역할을 하며, 호스트 시스템 프로세서를 통합 주변기기(표면 장착 IC)와 애드온 주변기기(확장 카드) 모두에 연결합니다.대부분의 시스템에서 PCIe 버스는 하나 이상의 레거시 PCI 버스와 함께 존재하며, 기존 PCI 주변기기의 대규모 본체와의 하위 호환성을 위해 사용됩니다.

2013년부터[update] PCI 익스프레스는 AGP를 새로운 시스템의 그래픽 카드의 기본 인터페이스로 대체했습니다.AMD(ATI)와 엔비디아가 2010년 이후 출시한 그래픽 카드의 거의 모든 모델은 PCI 익스프레스를 사용합니다.Nvidia는 PCIe의 고대역폭 데이터 전송을 SLI(Scalable Link Interface) 기술에 사용하여 칩셋과 모델 번호가 동일한 여러 그래픽 카드를 함께 실행하여 성능을 [citation needed]향상시킵니다.AMD는 크로스파이어([citation needed]CrossFire)라는 PCIe 기반의 멀티 GPU 시스템도 개발했습니다.AMD, 엔비디아 및 인텔은 4개의 PCIe x16 슬롯을 지원하는 마더보드 칩셋을 출시하여 트라이 GPU 및 쿼드 GPU 카드 구성이 가능합니다.

외장 GPU

이론적으로, 외부 PCIe는 노트북에 PCIe 데스크톱 비디오 카드를 연결함으로써 데스크톱의 그래픽 성능을 제공할 수 있습니다(외부 하우징에 내장되어 전원 공급 및 냉각 기능이 있음). ExpressCard 또는 Thunderbolt 인터페이스를 사용하면 가능합니다.ExpressCard 인터페이스는 5Gbit/s(0.5GB/s 처리량)의 비트 전송률을 제공하는 반면 Thunderbolt 인터페이스는 최대 40Gbit/s(5GB/s 처리량)의 비트 전송률을 제공합니다.

2006년 엔비디아는 전문 시장을 위한 [120]고급 그래픽 애플리케이션에 사용할 수 있는 쿼드로 플렉스 외부 PCIe GPU 제품군을 개발했습니다.이러한 비디오 카드에는 호스트측 카드에 PCI Express x8 또는 x16 슬롯이 필요하며, 이 슬롯은 8개의 PCIe [121]레인을 포함하는 VHDCI를 통해 Plex에 연결됩니다.

2008년 AMD는 PCIe x8 신호 [122]전송과 호환되는 독점 케이블링 시스템을 기반으로 하는 ATI XGP 기술을 발표했습니다.이 커넥터는 Fujitsu Amilo와 Acer Ferrari One 노트북에서 사용할 수 있습니다.Fujitsu는 [123]XGP용 AMILO Graphic Booster 인클로저를 곧 출시했습니다.2010년 경, 에이서는 [124]XGP용 Dynavivid 그래픽스 독을 출시했습니다.

2010년에는 PCI ExpressCard 슬롯을 통해 노트북이나 데스크톱에 연결할 수 있는 외부 카드 허브가 도입되었습니다.이러한 허브는 풀 사이즈 그래픽 카드를 사용할 수 있습니다.MSI GUS,[125] 빌리지 인스트루먼트의 ViDock,[126] Asus XG Station, Bplus PE4H V3.2 [127]어댑터 등이 대표적인 예입니다.[128]그러나 이러한 솔루션은 노트북에서 사용 가능한 PCIe 슬롯의 크기(종종 x1)와 버전에 따라 제한됩니다.

Intel Thunderbolt 인터페이스는 외부에서 PCIe 카드와 연결할 수 있는 새로운 옵션을 제공했습니다.Magma는 최대 3개의 PCIe 카드(x8에 2개, [129]x4에 1개)를 담을 수 있는 ExpressBox 3T를 출시했습니다.MSI는 비디오 [130]카드 전용 PCIe 섀시인 썬더볼트 GUS II도 출시했습니다.Sonnet의 Echo[131] Express와 mLogic의 mLink와 같은 다른 제품들은 더 작은 폼 [132]팩터의 Thunderbolt PCIe 섀시입니다.

2017년에는 전체 길이의 PCIe x16 [133]인터페이스를 갖춘 레이저 코어(Razer Core)와 같은 더 완전한 기능을 갖춘 외부 카드 허브가 소개되었습니다.

저장장치

PCI Express 프로토콜은 메모리 카드 및 SSD(Solid State Drive)와 같은 플래시 메모리 장치에 대한 데이터 인터페이스로 사용할 수 있습니다.

XQD 카드는 CompactFlash Association이 개발한 PCI Express를 활용한 메모리 카드 형식으로 최대 1GB/[134]s의 전송 속도를 자랑합니다.

많은 고성능 엔터프라이즈급 SSD는 PCI Express RAID 컨트롤러 [citation needed]카드로 설계되어 있습니다.NVMe가 표준화되기 전에는 대부분의 카드가 운영 체제와 통신하기 위해 전용 인터페이스와 사용자 지정 드라이버를 사용했습니다. 직렬 ATA나 [quantify][135][136]SAS 드라이브에 비해 전송률(1GB/s 이상)과 IOPS(초당 100만 I/O 작업)가 훨씬 높았습니다.예를 들어, 2011년 OCZ와 Marvell은 최대 용량 12TB, 최대 7.2GB/s 순차 전송 및 최대 252만 IOPS의 랜덤 전송 [137][relevant?]성능을 갖춘 PCI Express 3.0 x16 슬롯용 네이티브 PCI Express 솔리드 스테이트 드라이브 컨트롤러를 공동 개발했습니다.

SATA Express는 SATA 호환 포트를 통해 SSD를 연결하기 위한 인터페이스로, 선택적으로 여러 PCI Express 레인을 연결된 스토리지 [138]장치에 대한 순수 PCI Express 연결로 제공합니다.M.2는 내부에 장착된 컴퓨터 확장 카드 및 관련 커넥터에 대한 사양으로, 여러 PCI Express [139]레인도 사용합니다.

PCI Express 스토리지 장치는 하위 호환성을 위해 AHCI 논리 인터페이스를 구현할 수 있으며, NVM Express 논리 인터페이스는 이러한 장치가 제공하는 내부 병렬을 활용하여 훨씬 더 빠른 I/O 작업을 수행할 수 있습니다.엔터프라이즈급 SSD는 PCI [140]Express를 통해 SCSI를 구현할 수도 있습니다.

클러스터 인터커넥트

특정 데이터 센터 애플리케이션(예: 대형 컴퓨터 클러스터)은 구리 케이블에 내재된 거리 제한으로 인해 광섬유 인터커넥트를 사용해야 합니다.일반적으로 이더넷이나 파이버 채널과 같은 네트워크 지향 표준은 이러한 애플리케이션에 충분하지만, 라우팅 가능한 프로토콜에 의해 도입되는 오버헤드는 바람직하지 않으며 InfiniBand, Rapid와 같은 하위 레벨의 인터커넥트가 있는 경우도 있습니다.IO 또는 NUMA 링크가 필요합니다.이를 [141]위해 PCIe, 하이퍼트랜스포트와 같은 시내버스 표준이 원칙적으로 사용될 수 있지만 2015년 현재[update] Dolphin ICS, TTech Auto와 같은 틈새 판매업체에서만 솔루션을 사용할 수 있습니다.

경쟁 프로토콜

고대역폭 직렬 아키텍처를 기반으로 하는 다른 통신 표준으로는 InfiniBand, Rapid 등이 있습니다.IO, HyperTransport, Intel QuickPath Interconnect 및 MIPI(Mobile Industry Processor Interface).이러한 차이는 유연성과 확장성 대 지연 시간 및 오버헤드 간의 균형을 기반으로 합니다.예를 들어 Infiniband와 같이 시스템을 핫플러그형으로 설정하되 PCI Express는 설정하지 않으려면 소프트웨어가 네트워크 토폴로지의 [citation needed]변경을 추적해야 합니다.

또 다른 예는 지연 시간을 줄이기 위해 패킷을 더 짧게 하는 것입니다(버스가 메모리 인터페이스로 작동해야 하는 경우에 필요함).패킷이 작을수록 패킷 헤더가 패킷을 더 많이 소비하므로 유효 대역폭이 줄어듭니다.이러한 목적으로 설계된 버스 프로토콜의 예로는 Rapid가 있습니다.IO와 하이퍼트랜스포트.[citation needed]

PCI Express는 장치 인터커넥트 또는 라우팅된 네트워크 프로토콜이 아닌 시스템 인터커넥트(로컬 버스)로 설계되어 중간에 해당합니다.또한 소프트웨어 투명성이라는 설계 목표는 프로토콜을 제한하고 지연 시간을 [citation needed]다소 증가시킵니다.

PCIe 4.0 구현의 지연으로 인해 Gen-Z 컨소시엄, CCIX 노력, 개방형 CAPI(Coherent Accelerator Processor Interface)가 2016년 [142]말까지 발표되었습니다.

2019년 3월 11일, 인텔은 PCI Express 5.0 물리 계층 인프라를 기반으로 하는 새로운 인터커넥트 버스인 컴퓨팅 익스프레스 링크(CXL)를 선보였습니다.CXL 사양의 최초 제안자는 다음과 같습니다.알리바바, 시스코, 델 EMC, 페이스북, 구글, HPE, 화웨이, 인텔 및 마이크로소프트.[143]

적분기 목록

PCI-SIG Integrators List는 컴플라이언스 테스트를 통과한 PCI-SIG 회원사에서 만든 제품을 나열합니다.이 목록에는 스위치, 브리지, NIC, SSD [144]등이 포함됩니다.

참고 항목

- ASPM(Active State Power Management)

- 주변 부품 인터커넥트

- PCI 구성 공간

- PCI-X

- PCI/104-익스프레스

- PCIe/104

- 근복합체

- SDVO(직렬 디지털 비디오 출력)

- 장치 비트 전송률 목록 § 주 버스

- UCIe

- 계산 익스프레스 링크(CXL)

메모들

- ^ 스위치는 여러 장치와 공유할 수 있도록 하나의 엔드포인트를 여러 개 생성할 수 있습니다.

- ^ USB 3.0 포트가 PCI Express 버스가 공급할 수 있는 것보다 더 많은 전력을 필요로 하기 때문에 카드의 직렬 ATA 전원 커넥터가 있습니다.4핀 Mollex 전원 커넥터를 사용하는 경우가 많습니다.

참고문헌

- ^ Mayhew, D.; Krishnan, V. (August 2003). "PCI express and advanced switching: Evolutionary path to building next generation interconnects". 11th Symposium on High Performance Interconnects, 2003. Proceedings. pp. 21–29. doi:10.1109/CONECT.2003.1231473. ISBN 0-7695-2012-X. S2CID 7456382.

- ^ "Definition of PCI Express". PCMag.

- ^ Zhang, Yanmin; Nguyen, T Long (June 2007). "Enable PCI Express Advanced Error Reporting in the Kernel" (PDF). Proceedings of the Linux Symposium. Fedora project. Archived from the original (PDF) on 10 March 2016. Retrieved 8 May 2012.

- ^ https://www.hyperstone.com 플래시 메모리 폼 팩터 – 신뢰할 수 있는 플래시 스토리지의 기본, 2018년 4월 19일 검색

- ^ a b c Ravi Budruk (21 August 2007). "PCI Express Basics". PCI-SIG. Archived from the original (PDF) on 15 July 2014. Retrieved 15 July 2014.

- ^ "What are PCIe Slots and Their Uses". PC Guide 101. 18 May 2021. Retrieved 21 June 2021.

- ^ "How PCI Express Works". How Stuff Works. 17 August 2005. Archived from the original on 3 December 2009. Retrieved 7 December 2009.

- ^ "4.2.4.9. Link Width and Lane Sequence Negotiation", PCI Express Base Specification, Revision 2.1., 4 March 2009

- ^ a b c "PCI Express Architecture Frequently Asked Questions". PCI-SIG. Archived from the original on 13 November 2008. Retrieved 23 November 2008.

- ^ "PCI Express Bus". Interface bus. Archived from the original on 8 December 2007. Retrieved 12 June 2010.

- ^ PCIe 5.0까지 PCIe 기본 사양에 의해 32개의 레인이 정의되지만 PCIe 카드 전자기계 사양에는 카드 표준이 없으며 해당 레인 번호는 구현되지 않았습니다.

- ^ "PCI Express – An Overview of the PCI Express Standard". Developer Zone. National Instruments. 13 August 2009. Archived from the original on 5 January 2010. Retrieved 7 December 2009.

- ^ Qazi, Atif. "What are PCIe Slots?". PC Gear Lab. Retrieved 8 April 2020.

- ^ "New PCIe Form Factor Enables Greater PCIe SSD Adoption". NVM Express. 12 June 2012. Archived from the original on 6 September 2015.

- ^ "Memblaze PBlaze4 AIC NVMe SSD Review". StorageReview. 21 December 2015.

- ^ July 2015, Kane Fulton 20 (20 July 2015). "19 graphics cards that shaped the future of gaming". TechRadar.

- ^ Leadbetter, Richard (16 September 2020). "Nvidia GeForce RTX 3080 review: welcome to the next level". Eurogamer.

- ^ "Sapphire Radeon RX 5700 XT Pulse Review bit-tech.net". bit-tech.net. Retrieved 26 August 2019.

- ^ "AMD Radeon™ RX 5700 XT 8GB GDDR6 THICC II – RX-57XT8DFD6". xfxforce.com. Retrieved 25 August 2019.

- ^ "ROG Strix GeForce RTX 3080 OC Edition 10GB GDDR6X Graphics Cards". rog.asus.com.

- ^ "What is the A side, B side configuration of PCI cards". Frequently Asked Questions. Adex Electronics. 1998. Archived from the original on 2 November 2011. Retrieved 24 October 2011.

- ^ a b PCI Express Card Electromechanical Specification Revision 2.0

- ^ "PCI Express Card Electromechanical Specification Revision 4.0, Version 1.0 (Clean)".

- ^ "L1 PM Substates with CLKREQ, Revision 1.0a" (PDF). PCI-SIG. Archived from the original (PDF) on 4 December 2018. Retrieved 8 November 2018.

- ^ "Emergency Power Reduction Mechanism with PWRBRK Signal ECN" (PDF). PCI-SIG. Archived from the original (PDF) on 9 November 2018. Retrieved 8 November 2018.

- ^ PCI Express 카드 전자기계 사양 리비전 1.1

- ^ Schoenborn, Zale (2004), Board Design Guidelines for PCI Express Architecture (PDF), PCI-SIG, pp. 19–21, archived (PDF) from the original on 27 March 2016

- ^ IMT2000 3GPP - PCI Express 베이스 규격, 개정판 1.1 332페이지

- ^ "Where Does PCIe Cable Go?". 16 January 2022. Retrieved 10 June 2022.

- ^ a b "Mini-Fit® PCI Express®* Wire to Board Connector System" (PDF). Retrieved 4 December 2020.

- ^ PCI Express x16 그래픽 150W-ATX 사양 리비전 1.0

- ^ PCI Express 225 W/300 W 고출력 카드 전기기계 사양 리비전 1.0

- ^ PCI Express 카드 전자기계 사양 개정판 3.0

- ^ Yun Ling (16 May 2008). "PCIe Electromechanical Updates". Archived from the original on 5 November 2015. Retrieved 7 November 2015.

- ^ "MP1: Mini PCI Express / PCI Express Adapter". hwtools.net. 18 July 2014. Archived from the original on 3 October 2014. Retrieved 28 September 2014.

- ^ "mSATA FAQ: A Basic Primer". Notebook review. Archived from the original on 12 February 2012.

- ^ "Eee PC Research". ivc (wiki). Archived from the original on 30 March 2010. Retrieved 26 October 2009.

- ^ "Desktop Board Solid-state drive (SSD) compatibility". Intel. Archived from the original on 2 January 2016.

- ^ "How to distinguish the differences between M.2 cards Dell US". www.dell.com. Retrieved 24 March 2020.

- ^ "PCI Express External Cabling 1.0 Specification". Archived from the original on 10 February 2007. Retrieved 9 February 2007.

- ^ "PCI Express External Cabling Specification Completed by PCI-SIG". PCI SIG. 7 February 2007. Archived from the original on 26 November 2013. Retrieved 7 December 2012.

- ^ a b c "OCuLink connectors and cables support new PCIe standard". www.connectortips.com. Archived from the original on 13 March 2017.

- ^ Mokosiy, Vitaliy (9 October 2020). "Untangling terms: M.2, NVMe, USB-C, SAS, PCIe, U.2, OCuLink". Medium. Retrieved 26 March 2021.

- ^ "Supermicro Universal I/O (UIO) Solutions". Supermicro.com. Archived from the original on 24 March 2014. Retrieved 24 March 2014.

- ^ "Get ready for M-PCIe testing", PC board design, EDN

- ^ a b "PCI SIG discusses M‐PCIe oculink & 4th gen PCIe", The Register, UK, 13 September 2013, archived from the original on 29 June 2017

- ^ "PCI Express 4.0 Frequently Asked Questions". pcisig.com. PCI-SIG. Archived from the original on 18 May 2014. Retrieved 18 May 2014.

- ^ a b c "PCI Express 3.0 Frequently Asked Questions". pcisig.com. PCI-SIG. Archived from the original on 1 February 2014. Retrieved 1 May 2014.

- ^ "What does GT/s mean, anyway?". TM World. Archived from the original on 14 August 2012. Retrieved 7 December 2012.

- ^ "Deliverable 12.2". SE: Eiscat. Archived from the original on 17 August 2010. Retrieved 7 December 2012.

- ^ PCI SIG, archived from the original on 6 July 2008

- ^ — "PCI Express Base 2.0 specification announced" (PDF) (Press release). PCI-SIG. 15 January 2007. Archived from the original (PDF) on 4 March 2007. Retrieved 9 February 2007. 이 보도 자료에서 집계 대역폭이라는 용어는 들어오는 대역폭과 나가는 대역폭의 합을 나타냅니다. 이 용어를 사용하면 전이중 100BASE-TX의 집계 대역폭은 200 Mbit/s입니다.

- ^ Smith, Tony (11 October 2006). "PCI Express 2.0 final draft spec published". The Register. Archived from the original on 29 January 2007. Retrieved 9 February 2007.

- ^ Key, Gary; Fink, Wesley (21 May 2007). "Intel P35: Intel's Mainstream Chipset Grows Up". AnandTech. Archived from the original on 23 May 2007. Retrieved 21 May 2007.

- ^ Huynh, Anh (8 February 2007). "NVIDIA "MCP72" Details Unveiled". AnandTech. Archived from the original on 10 February 2007. Retrieved 9 February 2007.

- ^ "Intel P35 Express Chipset Product Brief" (PDF). Intel. Archived (PDF) from the original on 26 September 2007. Retrieved 5 September 2007.

- ^ Hachman, Mark (5 August 2009). "PCI Express 3.0 Spec Pushed Out to 2010". PC Mag. Archived from the original on 7 January 2014. Retrieved 7 December 2012.

- ^ "PCI Express 3.0 Bandwidth: 8.0 Gigatransfers/s". ExtremeTech. 9 August 2007. Archived from the original on 24 October 2007. Retrieved 5 September 2007.

- ^ "PCI Special Interest Group Publishes PCI Express 3.0 Standard". X bit labs. 18 November 2010. Archived from the original on 21 November 2010. Retrieved 18 November 2010.

- ^ "PCIe 3.1 and 4.0 Specifications Revealed". eteknix.com. July 2013. Archived from the original on 1 February 2016.

- ^ "Trick or Treat… PCI Express 3.1 Released!". synopsys.com. Archived from the original on 23 March 2015.

- ^ "PCI Express 4.0 evolution to 16 GT/s, twice the throughput of PCI Express 3.0 technology" (press release). PCI-SIG. 29 November 2011. Archived from the original on 23 December 2012. Retrieved 7 December 2012.

- ^ "Frequently Asked Questions PCI-SIG". pcisig.com. Archived from the original on 20 October 2016.

- ^ "PCIe 4.0 Heads to Fab, 5.0 to Lab". EE Times. 26 June 2016. Archived from the original on 28 August 2016. Retrieved 27 August 2016.

- ^ "Mellanox Announces ConnectX-5, the Next Generation of 100G InfiniBand and Ethernet Smart Interconnect Adapter NVIDIA". www.mellanox.com.

- ^ "Mellanox Announces 200Gb/s HDR InfiniBand Solutions Enabling Record Levels of Performance and Scalability NVIDIA". www.mellanox.com.

- ^ "IDF: PCIe 4.0 läuft, PCIe 5.0 in Arbeit". Heise Online (in German). 18 August 2016. Archived from the original on 19 August 2016. Retrieved 18 August 2016.

- ^ Brian Thompto, 인지 시대를 위한 POWER9 프로세서

- ^ 2016 IEEE Hot Chips 28 심포지엄(HCS), 2016년 8월 21일-23일

- ^ a b Born, Eric (8 June 2017). "PCIe 4.0 specification finally out with 16 GT/s on tap". Tech Report. Archived from the original on 8 June 2017. Retrieved 8 June 2017.

- ^ "IBM Unveils Most Advanced Server for AI". www-03.ibm.com. 5 December 2017.

- ^ IBM Power System AC922(8335-GTG) 서버는 혁신적인 가속 AI, HPDA 및 HPC 성능을 활용하여 통찰력을 더 빠르게 확보할 수 있도록 지원합니다. IBM Europe Hardware Announcement ZG17-0147

- ^ "NETINT Introduces Codensity with Support for PCIe 4.0 – NETINT Technologies". NETINT Technologies. 17 July 2018. Retrieved 28 September 2018.

- ^ Mujtaba, Hassan (9 January 2019). "AMD Ryzen 3000 Series CPUs Based on Zen 2 Launching in Mid of 2019".

- ^ Alcorn, Paul (3 June 2019). "AMD Nixes PCIe 4.0 Support on Older Socket AM4 Motherboards, Here's Why". Tom's Hardware. Archived from the original on 10 June 2019. Retrieved 10 June 2019.

- ^ Alcorn, Paul (10 January 2019). "PCIe 4.0 May Come to all AMD Socket AM4 Motherboards (Updated)". Tom's Hardware. Archived from the original on 10 June 2019. Retrieved 10 June 2019.

- ^ Cutress, Dr. Ian (13 August 2020). "Tiger Lake IO and Power". Anandtech.

- ^ "1,2,3,4,5... It's Official, PCIe 5.0 is Announced synopsys.com". www.synopsys.com. Retrieved 7 June 2017.

{{cite web}}: CS1 유지 : url-status (링크) - ^ "PLDA Announces Availability of XpressRICH5™ PCIe 5.0 Controller IP PLDA.com". www.plda.com. Retrieved 28 June 2018.

- ^ "XpressRICH5 for ASIC PLDA.com". www.plda.com. Retrieved 28 June 2018.

- ^ "Doubling Bandwidth in Under Two Years: PCI Express® Base Specification Revision 5.0, Version 0.9 is Now Available to Members". pcisig.com. Retrieved 12 December 2018.

- ^ "PCIe 5.0 Is Ready For Prime Time". tomshardware.com. 17 January 2019. Retrieved 18 January 2019.

- ^ "PCI-SIG® Achieves 32GT/s with New PCI Express® 5.0 Specification". www.businesswire.com. 29 May 2019.

- ^ "PCI-Express 5.0: China stellt ersten Controller vor". PC Games Hardware. 18 November 2019.

- ^ IBM의 POWER10 프로세서, 핫 칩스 32, 2020년 8월 16일 ~ 18일

- ^ Power E1080 Enterprise 서버는 하이브리드 클라우드에서 핵심 운영 및 AI 애플리케이션을 안전하고 효율적으로 확장할 수 있도록 지원하는 고유한 아키텍처의 플랫폼인 IBM Europe Hardware Announcement ZG21-0059를 제공합니다.

- ^ a b IBM Power E1080 기술 개요 및 소개

- ^ "Intel Unveils 12th Gen Intel Core, Launches World's Best Gaming". Intel.com. Retrieved 16 February 2022.

- ^ "NVIDIA Announces Hopper Architecture, the Next Generation of Accelerated Computing".

- ^ "AMD Showcases Industry-Leading Gaming, Commercial, and Mainstream PC Technologies at COMPUTEX 2022". AMD.com. Retrieved 23 May 2022.

- ^ "4th Gen AMD EPYC™ Processor Architecture". AMD.com. Retrieved 12 November 2022.

- ^ a b "PCI-SIG® Announces Upcoming PCI Express® 6.0 Specification to Reach 64 GT/s". www.businesswire.com. 18 June 2019.

- ^ Smith, Ryan. "PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021". www.anandtech.com.

- ^ "PCI Express 6.0 Reaches Version 0.5 Ahead Of Finalization Next Year – Phoronix". www.phoronix.com.

- ^ Shilov, Anton (4 November 2020). "PCIe 6.0 Specification Hits Milestone: Complete Draft Is Ready". Tom's Hardware.

- ^ Yanes, Al. "PCIe® 6.0 Specification, Version 0.9: One Step Closer to Final Release PCI-SIG". pcisig.com. Retrieved 6 October 2021.

- ^ "PCI-SIG® Releases PCIe® 6.0 Specification Delivering Record Performance to Power Big Data Applications". Business Wire. 11 January 2022. Retrieved 16 February 2022.

- ^ "The Evolution of the PCI Express Specification: On its Sixth Generation, Third Decade and Still Going Strong". Pci-Sig. 11 January 2022. Retrieved 16 February 2022.

- ^ Debendra Das Sharma. "PCIe 6.0 Specification: The Interconnect for I/O Needs of the Future". PCI-SIG. p. 8. Archived from the original on 30 October 2021.

- ^ "Pushing the Envelope with PCIe 6.0: Bringing PAM4 to PCIe" (PDF). Retrieved 16 February 2022.

- ^ "PowerPoint Presentation" (PDF). Retrieved 16 February 2022.

- ^ "PCI-SIG® Announces PCI Express® 7.0 Specification to Reach 128 GT/s". Business Wire. 21 June 2022. Retrieved 25 June 2022.

- ^ "PLX demo shows PCIe over fiber as data center clustering interconnect". Cabling install. Penn Well. Retrieved 29 August 2012.

- ^ "Introduced second generation PCI Express Gen 2 over fiber optic systems". Adnaco. 22 April 2011. Archived from the original on 4 October 2012. Retrieved 29 August 2012.

- ^ "PCIe Active Optical Cable System". Archived from the original on 30 December 2014. Retrieved 23 October 2015.

- ^ IBM Power Systems E870 및 E880 기술 개요 및 소개

- ^ "Acer, Asus to Bring Intel's Thunderbolt Speed Technology to Windows PCs". PC World. 14 September 2011. Archived from the original on 18 January 2012. Retrieved 7 December 2012.

- ^ Kevin Parrish (28 June 2013). "PCIe for Mobile Launched; PCIe 3.1, 4.0 Specs Revealed". Tom's Hardware. Retrieved 10 July 2014.

- ^ "PCI Express 4.0 Draft 0.7 & PIPE 4.4 Specifications – What Do They Mean to Designers? — Synopsys Technical Article ChipEstimate.com". www.chipestimate.com. Retrieved 28 June 2018.

- ^ "PCI Express 1x, 4x, 8x, 16x bus pinout and wiring @". RU: Pinouts. Archived from the original on 25 November 2009. Retrieved 7 December 2009.

- ^ "PHY Interface for the PCI Express Architecture" (PDF) (version 2.00 ed.). Intel. Archived from the original (PDF) on 17 March 2008. Retrieved 21 May 2008.

- ^ PCI 익스프레스 시스템 아키텍처

- ^ PCI Express 아키텍처, intel.com

- ^ "Mechanical Drawing for PCI Express Connector". Interface bus. Retrieved 7 December 2007.

- ^ "FCi schematic for PCIe connectors" (PDF). FCI connect. Retrieved 7 December 2007.

- ^ 메시지 신호 인터럽트 사용을 통한 인터럽트 지연 감소

- ^ IMT2000 3GPP - PCI Express Base 규격, 개정판 3.0 표 4-24

- ^ Computer Peripherals And Interfaces. Technical Publications Pune. 2008. ISBN 9788184313086. Archived from the original on 25 February 2014. Retrieved 23 July 2009.

- ^ a b c d e Lawley, Jason (28 October 2014). "Understanding Performance of PCI Express Systems" (PDF). 1.2. Xilinx.

{{cite web}}: CS1 유지 : url-status (링크) - ^ "NVIDIA Introduces NVIDIA Quadro® Plex – A Quantum Leap in Visual Computing". Nvidia. 1 August 2006. Archived from the original on 24 August 2006. Retrieved 14 July 2018.

- ^ "Quadro Plex VCS – Advanced visualization and remote graphics". nVidia. Archived from the original on 28 April 2011. Retrieved 11 September 2010.

- ^ "XGP". ATI. AMD. Archived from the original on 29 January 2010. Retrieved 11 September 2010.

- ^ Fujitsu-Siemens Amilo GraphicBooster External Laptop GPU Released, 3 December 2008, archived from the original on 16 October 2015, retrieved 9 August 2015

- ^ DynaVivid Graphics Dock from Acer arrives in France, what about the US?, 11 August 2010, archived from the original on 16 October 2015, retrieved 9 August 2015

- ^ Dougherty, Steve (22 May 2010), "MSI to showcase 'GUS' external graphics solution for laptops at Computex", TweakTown

- ^ Hellstrom, Jerry (9 August 2011), "ExpressCard trying to pull a (not so) fast one?", PC Perspective (editorial), archived from the original on 1 February 2016

- ^ "PE4H V3.2 (PCIe x16 Adapter)". Hwtools.net. Archived from the original on 14 February 2014. Retrieved 5 February 2014.

- ^ O'Brien, Kevin (8 September 2010), "How to Upgrade Your Notebook Graphics Card Using DIY ViDOCK", Notebook review, archived from the original on 13 December 2013

- ^ Lal Shimpi, Anand (7 September 2011), "The Thunderbolt Devices Trickle In: Magma's ExpressBox 3T", AnandTech, archived from the original on 4 March 2016

- ^ "MSI GUS II external GPU enclosure with Thunderbolt". The Verge (hands-on). 10 January 2012. Archived from the original on 13 February 2012. Retrieved 12 February 2012.

- ^ "PCI express graphics, Thunderbolt", Tom’s hardware, 17 September 2012

- ^ "M logics M link Thunderbold chassis no shipping", Engadget, 13 December 2012, archived from the original on 25 June 2017

- ^ Burns, Chris (17 October 2017), "2017 Razer Blade Stealth and Core V2 detailed", SlashGear, archived from the original on 17 October 2017

- ^ "CompactFlash Association readies next-gen XQD format, promises write speeds of 125 MB/s and up". Engadget. 8 December 2011. Archived from the original on 19 May 2014. Retrieved 18 May 2014.

- ^ Zsolt Kerekes (December 2011). "What's so very different about the design of Fusion-io's ioDrives / PCIe SSDs?". storagesearch.com. Archived from the original on 23 September 2013. Retrieved 2 October 2013.

- ^ "Fusion-io ioDrive Duo Enterprise PCIe Review". storagereview.com. 16 July 2012. Archived from the original on 4 October 2013. Retrieved 2 October 2013.

- ^ "OCZ Demos 4 TiB, 16 TiB Solid-State Drives for Enterprise". X-bit labs. Archived from the original on 25 March 2013. Retrieved 7 December 2012.

- ^ "Enabling Higher Speed Storage Applications with SATA Express". SATA-IO. Archived from the original on 27 November 2012. Retrieved 7 December 2012.

- ^ "SATA M.2 Card". SATA-IO. Archived from the original on 3 October 2013. Retrieved 14 September 2013.

- ^ "SCSI Express". SCSI Trade Association. Archived from the original on 27 January 2013. Retrieved 27 December 2012.

- ^ Meduri, Vijay (24 January 2011). "A Case for PCI Express as a High-Performance Cluster Interconnect". HPCwire. Archived from the original on 14 January 2013. Retrieved 7 December 2012.

- ^ Evan Koblentz (3 February 2017). "New PCI Express 4.0 delay may empower next-gen alternatives". Tech Republic. Archived from the original on 1 April 2017. Retrieved 31 March 2017.

- ^ Cutress, Ian. "CXL Specification 1.0 Released: New Industry High-Speed Interconnect From Intel". www.anandtech.com. Retrieved 9 August 2019.

- ^ "Integrators List PCI-SIG". pcisig.com. Retrieved 27 March 2019.

추가열람

- Budruk, Ravi; Anderson, Don; Shanley, Tom (2003), Winkles, Joseph ‘Joe’ (ed.), PCI Express System Architecture, Mind share PC system architecture, Addison-Wesley, ISBN 978-0-321-15630-3Budruk, Ravi; Anderson, Don; Shanley, Tom (2003), Winkles, Joseph ‘Joe’ (ed.), PCI Express System Architecture, Mind share PC system architecture, Addison-Wesley, ISBN 978-0-321-15630-31120pp.

- Solari, Edward; Congdon, Brad (2003), Complete PCI Express Reference: Design Implications for Hardware and Software Developers, Intel, ISBN 978-0-9717861-9-6Solari, Edward; Congdon, Brad (2003), Complete PCI Express Reference: Design Implications for Hardware and Software Developers, Intel, ISBN 978-0-9717861-9-61056pp.

- Wilen, Adam; Schade, Justin P; Thornburg, Ron (April 2003), Introduction to PCI Express: A Hardware and Software Developer's Guide, Intel, ISBN 978-0-9702846-9-3Wilen, Adam; Schade, Justin P; Thornburg, Ron (April 2003), Introduction to PCI Express: A Hardware and Software Developer's Guide, Intel, ISBN 978-0-9702846-9-3325pp.

외부 링크

Wikimedia Commons의 PCIe 관련 미디어

Wikimedia Commons의 PCIe 관련 미디어- PCI-SIG 규격