x86-64

x86-64

x86-64([note 1]x64, x86_64, AMD64, 인텔 64라고도 함)는 x86 명령어 세트의 64비트 버전으로 1999년에 처음 발표되었습니다. 새로운 4단계 페이징 모드와 함께 64비트 모드와 호환 모드라는 두 가지 새로운 동작 모드를 도입했습니다.

64비트 모드와 새로운 페이징 모드를 통해 이전 32비트에서 가능했던 것보다 훨씬 더 많은 양의 가상 메모리와 물리적 메모리를 지원하므로 프로그램이 더 많은 양의 데이터를 메모리에 저장할 수 있습니다. x86-64는 또한 64비트로 범용 레지스터를 확장하고, 8비트에서 16비트(예를 들어 스택 관리의 경우 일부 기능이 제한적이거나 고정되어 있음)로 확장하며, 기타 수많은 향상된 기능을 제공합니다. 부동 소수점 산술은 SSE2와 같은 필수 명령어를 통해 지원되며, x87/MMX 스타일 레지스터는 일반적으로 사용되지 않습니다(그러나 64비트 모드에서도 여전히 사용 가능). 대신에, 각각 128비트씩 16개의 벡터 레지스터 세트가 사용됩니다. (각 레지스터는 1~2개의 이중 정밀도 숫자 또는 1~4개의 단일 정밀도 숫자를 저장할 수 있습니다.) 또는 다양한 정수 형식.) 64비트 모드에서는 64비트 피연산자와 64비트 주소 지정 모드를 지원하도록 명령이 수정됩니다.

아키텍처에 정의된 호환성 모드를 사용하면 16비트 및 32비트 사용자 애플리케이션을 수정하지 않고 실행할 수 있으며 64비트 운영 체제에서 지원하는 경우 64비트 애플리케이션과 공존합니다.[11][note 2] 전체 x86 16비트 및 32비트 명령어 세트가 에뮬레이션 없이 하드웨어로 구현된 상태로 유지되기 때문에, 이러한 오래된 실행 파일은 성능 페널티를 거의 또는 전혀 받지 않고 실행할 수 있는 반면,[13] 더 새로운 애플리케이션이나 수정된 애플리케이션은 프로세서 설계의 새로운 기능을 활용하여 성능 향상을 달성할 수 있습니다. 또한 x86-64를 지원하는 프로세서는 보호 모드를 지원하는 x86 프로세서가 80286 이후에 그랬던 것처럼 8086과의 완전한 하위 호환성을 위해 실제 모드에서 계속 켜져 있습니다.

AMD가 만들고 2000년에 출시된 원래 사양은 AMD, 인텔, VIA에 의해 구현되었습니다. AMD K8 마이크로아키텍처는 Opteron과 Athlon 64 프로세서에서 처음으로 구현되었습니다. 이것은 인텔 이외의 회사가 설계한 x86 아키텍처에 처음으로 중요한 추가 사항이었습니다. 인텔은 어쩔 수 없이 이를 따를 수밖에 없었고, AMD의 사양과 소프트웨어 호환되는 수정된 NetBurst 제품군을 선보였습니다. VIA Technologies는 VIA Nano와 함께 VIA 이사야 아키텍처에 x86-64를 도입했습니다.

x86-64 아키텍처는 일반적으로 16GB 이상의 메모리를 위해 구성된 데스크톱 및 랩톱 개인용 컴퓨터와 서버에 빠르게 채택되었습니다. 원래 x86 아키텍처를 대체하기 위해 의도되었던 단종된 Intel Itanium 아키텍처(이전의 IA-64)를 사실상 대체했습니다. x86-64와 Itanium은 기본 명령어 세트 수준에서 호환되지 않으며, 하나의 아키텍처에 대해 컴파일된 운영 체제 및 애플리케이션은 다른 기본 아키텍처에서 실행할 수 없습니다.

AMD64

역사

AMD64는 인텔과 휴렛패커드가 설계한 근본적으로 다른 IA-64 아키텍처의 대안으로 개발되었으며, 32비트 버전의 x86 아키텍처인 IA-32와 역호환이 되지 않습니다. AMD는 원래 2000년 8월에 전체 사양을 사용할 수 있는 AMD64를 1999년에[14] 발표했습니다.[15] AMD가 IA-64 아키텍처에 대한 기여 파티에 초대된 적이 없고 어떤 종류의 라이선스도 가능성이 없어 보였기 때문에 AMD는 처음부터 기존 x86 아키텍처에 64비트 컴퓨팅 기능을 추가하는 동시에 레거시 32비트 x86 코드를 지원하는 진화적 방법으로 자리 잡았습니다. IA-64와 완전히 새로운 x86 호환되지 않는 64비트 아키텍처를 만드는 인텔의 접근 방식과는 대조적입니다.

최초의 AMD64 기반 프로세서인 옵테론은 2003년 4월에 출시되었습니다.

구현

AMD64 아키텍처를 구현하는 AMD의 프로세서는 옵테론, 애슬론 64, 애슬론 64 X2, 애슬론 64 FX, 애슬론 II(코어 수를 나타내는 X2, X3 또는 X4), 튜리온 64, 튜리온 64 X2, 셈프론(팔레르모 E6 스테핑 및 모든 "마닐라" 모델), 페놈(코어 수를 나타내는 X3 또는 X4), 페놈 II(코어 수를 나타내는 X2, X3, X4 또는 X6), FX, 퓨전/APU 및 라이젠/Epyc.

건축적 특징

AMD64의 주요한 정의 특징은 64비트 범용 프로세서 레지스터를 사용할 수 있다는 것입니다. rax), 64비트 정수 산술 및 논리 연산 및 64비트 가상 주소.[citation needed] 디자이너들은 다른 개선도 할 수 있는 기회를 가졌습니다.

64비트 확장에서 주목할 만한 변경 사항은 다음과 같습니다.

- 64비트 정수 기능

- 모든 범용 레지스터(GPR)는 32비트에서 64비트로 확장되며, 모든 산술 및 논리 연산, 메모리 대 레지스터 및 레지스터 대 메모리 연산 등은 64비트 정수에서 직접 작동할 수 있습니다. 스택에서 밀어서 터뜨리면 기본적으로 8바이트 보폭이 되며 포인터의 너비는 8바이트입니다.

- 추가 레지스터

- 범용 레지스터의 크기를 증가시키는 것 외에도, 명명된 범용 레지스터의 수는 x86의 8개(즉, eax, ecx, edx, ebx, esi, edi)에서 16개(즉, rax, rcx, rdx, rbx, rsp, rbp, rsi, rdi, rd8, r10, r11, r12, r13, r14, r15)로 증가됩니다. 따라서 스택보다는 레지스터에 더 많은 로컬 변수를 유지할 수 있고, 레지스터에 자주 액세스되는 상수를 유지할 수 있습니다. 작고 빠른 서브루틴에 대한 인수도 레지스터에 더 많이 전달될 수 있습니다.

- AMD64는 여전히 많은 RISC 명령어 세트(예: PA-RISC, Power ISA 및 MIPS에는 32개의 GPR이 있고, 알파, 64비트 ARM 및 SPARC에는 31개의 레지스터가 있음) 또는 IA-64와 같은 VLIW 유사 기계(128개의 레지스터가 있음)보다 적은 수의 레지스터가 있습니다. 그러나 AMD64 구현은 명령어 세트에 의해 노출되는 아키텍처 레지스터의 수보다 훨씬 더 많은 내부 레지스터를 가질 수 있습니다(레지스터 이름 변경 참조). (예를 들어 AMD Zen 코어에는 168개의 64비트 정수와 160개의 128비트 벡터 부동 소수점 물리적 내부 레지스터가 있습니다.)

- 추가 XMM(SSE) 레지스터

- 마찬가지로 128비트 XMM 레지스터(Streaming SIMD 명령에 사용됨)도 8개에서 16개로 증가합니다.

- 기존 x87 FPU 레지스터 스택은 SSE2에서 사용하는 XMM 레지스터와 비교하여 64비트 모드의 레지스터 파일 크기 확장에 포함되지 않습니다. x87 레지스터 스택은 단순한 레지스터 파일이 아니지만 저비용 교환 작업을 통해 개별 레지스터에 직접 액세스할 수 있습니다.

- 더 큰 가상 주소 공간

- AMD64 아키텍처는 64비트 가상 주소 형식을 정의하며, 이 중 하위 48비트는 현재 구현에서 사용됩니다.[11]: 120 이를 통해 최대 256TB(2바이트48)의 가상 주소 공간을 사용할 수 있습니다. 아키텍처 정의를 통해 향후 구현 시 이 제한을 전체 64비트로 높일 수 있으며,[11]: 2 : 3 : 13 : 117 : 120 가상 주소 공간을 16EB(2바이트64)로 확장할 수 있습니다.[16] 이는 x86의 경우 4GB(2바이트32)에 불과합니다.[17]

- 즉, 파일의 영역을 주소 공간에 매핑할 필요 없이 전체 파일을 프로세스의 주소 공간에 매핑하여 매우 큰 파일을 작업할 수 있습니다(이는 종종 파일 읽기/쓰기 호출로 작업하는 것보다 훨씬 빠릅니다).

- 더 큰 물리적 주소 공간

- AMD64 아키텍처의 원래 구현은 40비트 물리적 주소를 구현하여 최대 1TB(2바이트40)의 RAM을 처리할 수 있었습니다.[11]: 24 AMD64 아키텍처의 현재 구현(AMD 10h 마이크로아키텍처부터 시작)은 이를 48비트 물리적[18] 주소로 확장하므로 최대 256TB(2바이트48)의 RAM을 처리할 수 있습니다. 이 아키텍처는 향후[11]: 24 [19] 52비트까지 확장할 수 있습니다(페이지 테이블 엔트리 형식에 따라 제한됨).[11]: 131 이를 통해 최대 4PB의 RAM 주소 지정이 가능합니다. 비교를 위해 32비트 x86 프로세서는 PAE(Physical Address Extension) 모드에서 64GB의 RAM [20]또는 PAE 모드가 없는 4GB의 RAM으로 제한됩니다.[11]: 4

- 레거시 모드에서 더 큰 물리적 주소 공간

- 레거시 모드에서 작동할 때 AMD64 아키텍처는 대부분의 현재 x86 프로세서와 마찬가지로 물리적 주소 확장(PAE) 모드를 지원하지만 AMD64는 PAE를 36비트에서 52비트의 아키텍처 제한으로 확장합니다. 따라서 모든 구현은 롱 모드에서와 동일한 물리적 주소 제한을 허용합니다.[11]: 24

- 명령 포인터 상대 데이터 액세스

- 이제 명령어는 명령어 포인터(RIP 레지스터)와 관련된 데이터를 참조할 수 있습니다. 이를 통해 공유 라이브러리 및 실행 시 로드되는 코드에서 자주 사용되는 것처럼 위치 독립적인 코드를 보다 효율적으로 만들 수 있습니다.

- SSE 지침

- 원래 AMD64 아키텍처는 인텔의 SSE와 SSE2를 핵심 명령어로 채택했습니다. 이러한 명령어 세트는 단일 정밀도 및 이중 정밀도 데이터 유형에 대한 스칼라 x87 FPU에 대한 벡터 보충 기능을 제공합니다. SSE2는 또한 8비트에서 64비트 정밀도에 이르는 데이터 유형에 대해 정수 벡터 연산을 제공합니다. 따라서 이 아키텍처의 벡터 기능은 당대 가장 진보된 x86 프로세서의 벡터 기능과 동등합니다. 이러한 지침은 32비트 모드에서도 사용할 수 있습니다. 64비트 프로세서의 확산으로 이러한 벡터 기능이 가정용 컴퓨터에서 보편화되어 32비트 애플리케이션의 표준을 개선할 수 있게 되었습니다. 예를 들어 32비트 버전의 Windows 8에는 SSE2 명령이 있어야 합니다.[21] SSE3 명령 및 이후의 스트리밍 SIMD 확장 명령 세트는 아키텍처의 표준 기능이 아닙니다.

- 실행 안 함 비트

- No-Execute 비트 또는 NX 비트(페이지 테이블 항목의 비트 63)를 사용하면 운영 체제에서 실행 가능한 코드를 포함할 수 있는 가상 주소 공간의 페이지와 포함할 수 없는 페이지를 지정할 수 있습니다. "실행 금지" 태그가 붙은 페이지에서 코드를 실행하려고 하면 읽기 전용 페이지에 쓰기를 시도하는 것과 마찬가지로 메모리 액세스 위반이 발생합니다. 이렇게 하면 악성 코드가 "버퍼 오버런" 또는 "확인되지 않은 버퍼" 공격을 통해 시스템을 제어하기가 더 어려워집니다. 80286 이후로 x86 프로세서에서도 세그먼트 설명자의 속성으로 비슷한 기능을 사용할 수 있었지만 한 번에 전체 세그먼트에서만 작동합니다.

- 세그먼트 주소 지정은 오래 전부터 구식으로 여겨져 왔으며, 현재 사용되는 모든 PC 운영 체제는 이를 우회하여 모든 세그먼트를 기본 주소 0과 (32비트 구현에서는) 4GB 크기로 설정합니다. AMD는 x86 계열 벤더 중 최초로 선형 어드레싱 모드에서 실행되지 않는 기능을 구현했습니다. 이 기능은 AMD64 프로세서와 최신 Intel x86 프로세서의 레거시 모드에서도 사용할 수 있습니다(PAE가 사용되는 경우).

- 오래된 기능 제거

- x86 아키텍처의 일부 "시스템 프로그래밍" 기능은 현대 운영 체제에서 사용되지 않았거나 덜 사용되었으며 AMD64에서 롱(64비트 및 호환성) 모드로 사용할 수 없거나 제한된 형태로만 존재합니다. 여기에는 분할된 주소 지정(FS 및 GS 세그먼트는 운영 체제 구조에 대한 추가 기본 포인터로 사용하기 위해 기본 형태로 유지되지만),[11]: 70 작업 상태 전환 메커니즘 및 가상 8086 모드가 포함됩니다. 이러한 기능은 "레거시 모드"에서 완벽하게 구현되어 이러한 프로세서는 수정 없이 32비트 및 16비트 운영 체제를 실행할 수 있습니다. 스택의 세그먼트 레지스터 저장/복원, 모든 레지스터(PUSHA/POPA) 저장/복원, 십진수 산술, BUND 및 INT 명령, 즉각적인 피연산자를 사용한 "멀리" 점프 및 호출을 포함하여 거의 유용하지 않은 것으로 입증된 일부 명령어는 64비트 모드에서 지원되지 않습니다.

가상 주소 공간 세부 정보

표준 양식 주소

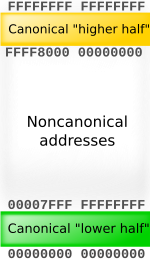

64비트 모드에서는 가상 주소의 너비가 64비트이지만 현재 구현(및 계획 단계에 있는 것으로 알려진 모든 칩)에서는 2바이트64(16EB)의 전체 가상 주소 공간을 사용할 수 없습니다. 이는 32비트 시스템의 가상 주소 공간 크기의 약 40억 배입니다. 대부분의 운영 체제 및 애플리케이션은 가까운 미래에 이러한 넓은 주소 공간을 필요로 하지 않을 것이므로 이러한 넓은 가상 주소를 구현하면 실질적인 이점 없이 주소 변환의 복잡성과 비용이 증가할 뿐입니다. 따라서 AMD는 아키텍처의 첫 번째 구현에서 가장 중요하지 않은 48비트의 가상 주소만 실제로 주소 변환에 사용하기로 결정했습니다(페이지 테이블 조회).[11]: 120

또한 AMD 사양에서는 모든 가상 주소의 가장 중요한 16비트인 비트 48~63이 비트 47의 복사본이어야 합니다(사인 확장과 유사한 방식). 이 요구 사항이 충족되지 않으면 프로세서는 예외를 제기합니다.[11]: 131 이 규칙을 준수하는 주소를 "정규 형식"이라고 합니다.[11]: 130 표준 양식 주소는 0 ~ 00007입니다.총 256TB의 사용 가능한 가상 주소 공간을 위해 FFF'FFF'FFF'FFF8000'0000000000을 통해 사용할 수 있습니다. 이는 여전히 32비트 시스템의 가상 4GB 주소 공간보다 65,536배 더 큽니다.

이 기능은 나중에 진정한 64비트 주소 지정으로 확장성을 용이하게 합니다. 많은 운영 체제(윈도우 NT 계열 포함, 이에 국한되지는 않음)는 주소 공간의 상위 주소 절반(이름이 커널 공간)을 스스로 차지하고 애플리케이션 코드, 사용자 모드 스택, 힙 및 기타 데이터 영역에 대해 하위 주소 절반(사용자 공간)을 남깁니다.[22] "정규 주소" 설계는 모든 AMD64 호환 구현에 사실상 두 개의 메모리 절반을 갖도록 보장합니다. 하위 절반은 00000000000000000000에서 시작하여 더 많은 가상 주소 비트를 사용할 수 있게 됨에 따라 "상향으로 증가"하는 반면, 상위 절반은 주소 공간의 맨 위에 "도킹"되어 아래로 증가합니다. 또한 사용되지 않는 주소 비트를 확인하여 주소의 "정규 형식"을 적용하면 운영 체제에서 플래그, 권한 마커 등으로 태그 지정된 포인터를 사용할 수 없기 때문에 이러한 사용은 더 많은 가상 주소 비트를 구현하기 위해 아키텍처를 확장할 때 문제가 될 수 있습니다.

Windows for x64의 첫 번째 버전은 256TB 전체를 사용하지도 않았습니다. 사용자 공간은 8TB, 커널 공간은 8TB로 제한되었습니다.[22] Windows는 2013년 10월에 출시된 Windows 8.1까지 48비트 주소 공간 전체를 지원하지 않았습니다.[22]

페이지 테이블 구조

64비트 주소 지정 모드("long mode")는 물리 주소 확장(PAE)의 슈퍼셋입니다. 이 때문에 페이지 크기는 4KB(2바이트12) 또는 2MB(2바이트21)가 될 수 있습니다.[11]: 120 롱 모드는 1GB(2바이트30)의 페이지 크기도 지원합니다.[11]: 120 PAE 모드의 시스템에서 사용하는 3단계 페이지 테이블 시스템이 아닌, 롱 모드로 실행되는 시스템은 4단계의 페이지 테이블을 사용합니다. PAE의 페이지-디렉토리 포인터 테이블은 4개의 항목에서 512개로 확장되고, 48비트 구현의 512개의 항목을 포함하는 PML4(Page-Map Level 4) 테이블이 추가됩니다.[11]: 131 전체 48비트 공간에 대한 4KB 페이지의 전체 매핑 계층 구조는 512GB(256TB 가상 공간의 약 0.195%)보다 약간 더 많은 메모리를 필요로 합니다.

64비트 페이지 테이블 항목 비트: 63 62 … 52 51 … 32 내용: NX 유보적인 기본 주소의 비트 51…32 비트: 31 … 12 11 … 9 8 7 6 5 4 3 2 1 0 내용: 기본 주소의 비트 31…12 ign. G 쓰다듬다 D A PCD PWT U/S R/W P

인텔은 인텔 64 프로세서가 57비트 가상 주소 공간을 지원하는 5단계 페이지 테이블을 갖춘 방식을 구현했습니다.[23] 추가 확장을 통해 페이지 테이블 입력 크기를 128비트로 확장하여 전체 64비트 가상 주소 공간과 물리적 메모리를 사용할 수 있으며, 하위 호환성을 위해 여전히 4KB 페이지 작업을 지원하는 더 큰 64KB 페이지 할당 크기를 사용하여 5단계 계층 구조에서 페이지 워크를 줄일 수 있습니다.[24]

운영체제 한계

운영 체제는 또한 가상 주소 공간을 제한할 수 있습니다. 해당되는 경우 자세한 내용은 "운영 체제 호환성 및 특성" 섹션에 나와 있습니다.

물리적 주소 공간 세부 정보

현재 AMD64 프로세서는 최대 2바이트의48 RAM, 즉 256TB의 물리적 주소 공간을 지원합니다.[18] 하지만 2020년[update] 현재 256TB의 RAM을 지원하는 x86-64 마더보드는 알려져 있지 않습니다.[25][26][27][28][failed verification] 운영 체제는 사용 가능하거나 지원되는 RAM의 양에 추가적인 제한을 둘 수 있습니다. 이 점에 대한 자세한 내용은 본 문서의 "운영 체제 호환성 및 특성" 섹션에 나와 있습니다.

작동 모드

아키텍처에는 롱 모드와 레거시 모드의 두 가지 주요 작동 모드가 있습니다.

| 운영하는 | 필요한 운영체제 | 실행 중인 코드 유형 | 크기(비트 단위) | 범용대장 제1호 | ||

|---|---|---|---|---|---|---|

| 모드 | 서브 모드 | 주소 | 피연산자(이탤릭체로 기본값) | |||

| 롱 모드 | 64비트 모드 | 64비트 OS, 64비트 UEFI 펌웨어 또는 64비트 펌웨어의 UEFI 인터페이스를 통해 상호 작용하는 이전 두 가지 | 64비트 | 64 | 8, 16, 32, 64 | 16 |

| 호환 모드 | 부트로더 또는 64비트 OS | 32비트 | 32 | 8, 16, 32 | 8 | |

| 16비트 보호 모드 | 16 | 8, 16, 32 | 8 | |||

| 레거시 모드 | 보호 모드 | 부트로더, 32비트 OS, 32비트 UEFI 펌웨어 또는 펌웨어의 UEFI 인터페이스를 통해 상호 작용하는 후자의 두 가지 | 32비트 | 32 | 8, 16, 32 | 8 |

| 16비트 보호 모드 OS | 16비트 보호 모드 | 16 | 8, 16, 32[m 1] | 8 | ||

| 가상 8086 모드 | 16비트 보호 모드 또는 32비트 OS | 실제 모드의 부분 집합 | 16 | 8, 16, 32[m 1] | 8 | |

| 언리얼 모드 | 부트로더 또는 실제 모드 OS | 리얼 모드 | 16, 20, 32 | 8, 16, 32[m 1] | 8 | |

| 리얼모드 | 부트로더, 실제 모드 OS 또는 펌웨어의 BIOS 인터페이스와[29] 인터페이스하는 모든 OS | 리얼 모드 | 16, 20, 21 | 8, 16, 32[m 1] | 8 | |

롱 모드

롱 모드(Long mode)는 아키텍처에서 의도하는 기본 동작 모드입니다. 프로세서의 기본 64비트 모드와 32비트 및 16비트 호환 모드를 결합한 것입니다. 64비트 운영 체제에서 사용됩니다. 64비트 운영 체제에서는 64비트 프로그램이 64비트 모드에서 실행되고, 32비트 및 16비트 보호 모드 응용 프로그램(언제든지 실행하기 위해 실제 모드 또는 가상 8086 모드를 사용할 필요가 없음)이 호환 모드에서 실행됩니다. 언제든지 가상 8086 모드를 사용하는 실제 모드 프로그램 및 프로그램은 소프트웨어로 에뮬레이트되지 않으면 롱 모드로 실행할 수 없습니다.[11]: 11 그러나 이러한 프로그램은 원하는 모드로 실행되는 가상 프로세서를 생성하여 VT-x 또는 AMD-V를 지원하는 프로세서에서 긴 모드로 실행되는 운영 체제에서 시작될 수 있습니다.

기본 명령어 세트가 동일하기 때문에 보호 모드 x86 코드를 실행할 때 성능 패널티가 거의 없습니다. 이것은 인텔의 IA-64와 달리 32비트 코드를 실행하는 것은 x86의 에뮬레이션(프로세스 속도를 느리게 만드는) 또는 전용 x86 보조 프로세서를 사용하여 실행해야 한다는 것을 의미합니다. 그러나 x86-64 플랫폼에서는 64비트 코드에 추가 레지스터가 있고 SSE2 기반 FPU 지원이 보장되어 컴파일러가 최적화에 사용할 수 있기 때문에 많은 x86 응용 프로그램이 64비트 재컴파일의 혜택을 받을 수 있습니다. 그러나 암호 알고리즘과 같이 32비트보다 넓은 정수를 정기적으로 처리하는 응용 프로그램은 64비트 레지스터를 활용하기 위해 거대한 정수를 처리하는 코드를 다시 작성해야 합니다.

레거시 모드

레거시 모드는 프로세서가 긴 모드가 아닐 때 사용하는 모드입니다.[11]: 14 이 모드에서는 프로세서가 이전 x86 프로세서처럼 작동하며 16비트 및 32비트 코드만 실행할 수 있습니다. 레거시 모드에서는 최대 32비트 가상 주소 지정을 허용하므로 가상 주소 공간이 4GB로 제한됩니다.[11]: 14 : 24 : 118 레거시 모드에서는 64비트 프로그램을 실행할 수 없습니다.

보호 모드

보호 모드는 레거시 모드의 하위 모드로 만들어집니다.[11]: 14 32비트 운영 체제와 16비트 보호 모드 운영 체제가 x86-64 CPU에서 실행될 때 작동하는 하위 모드입니다.[11]: 14

리얼모드

Real mode는 프로세서가 초기화될 때의 초기 동작 모드이며, 레거시 모드의 하위 모드입니다. 오리지널 인텔 8086 및 인텔 8088 프로세서와 역호환이 가능합니다. 실제 모드는 오늘날 운영 체제 부트로더에서 주로 사용되며, 이는 아키텍처에서 상위 모드로 전환하기 전에 가상 메모리 세부 정보를 구성하는 데 필요합니다. 이 모드는 기존의 BIOS 스타일 인터페이스를 사용하여 시스템 펌웨어와 통신해야 하는 모든 운영 체제에서도 사용됩니다.[29]

인텔 64

인텔 64는 인텔이 x86-64를 구현한 것으로, 인텔이 만든 다양한 프로세서에 사용되고 구현됩니다.

역사

역사적으로 AMD는 인텔의 원래 디자인을 본뜬 명령어 세트를 가진 프로세서를 개발하고 생산해 왔지만, x86-64와 함께 역할이 뒤바뀌었습니다. 인텔은 AMD가 인텔의 자체 x86 프로세서 라인의 확장으로 만든 ISA를 채택하는 입장에 서게 되었습니다.

인텔의 프로젝트는 원래 Yamhill[30](오레곤의 Willamette Valley에 있는 Yamhill River의 이름을 따서)이라는 암호명을 가지고 있었습니다. 몇 년 동안 존재를 부인해 온 인텔은 2004년 2월 IDF에서 프로젝트가 실제로 진행 중이라고 발표했습니다. 당시 인텔의 회장이었던 크레이그 바렛은 이것이 그들의 최악의 비밀 중 하나라고 인정했습니다.[31][32]

이 명령어 세트에 대한 인텔의 이름은 여러 번 변경되었습니다. IDF에서 사용된 이름은 CT[33](아마[original research?] 오리건 강의 또 다른 코드명인 Clackamas Technology의 경우)였습니다. 몇 주 안에 그들은 그것을 IA-32e(IA-32 확장용)로 언급하기 시작했고 2004년 3월에 "공식" 이름 EM64T(Extended Memory 64 Technology)를 공개했습니다. 2006년 말, 인텔은 AMD가 AMD64라는 이름을 사용하는 것과 병행하여 인텔 64라는 이름을 구현에 사용하기 시작했습니다.[34]

인텔 64를 구현한 최초의 프로세서는 2004년 6월 노코나(Nocona)라는 코드명을 가진 멀티 소켓 프로세서 Xeon이었습니다. 이와 대조적으로 초기 프레스콧 칩(2004년 2월)에서는 이 기능이 활성화되지 않았습니다. 인텔은 이후 프레스콧 코어의 E0 개정판을 사용하여 인텔 64 지원 펜티엄 4를 판매하기 시작했으며, 이는 OEM 시장에서 펜티엄 4, 모델 F로 판매되었습니다. E0 개정판은 또한 인텔 64에 eXCute Disable(XD)(NX 비트에 대한 인텔의 이름)을 추가하였으며, 현재의 제온 코드명 Irwindale에 포함되어 있습니다. 인텔이 주류 데스크톱 프로세서에서 인텔 64(당시 EM64T라는 이름으로)를 공식 출시한 것은 N0 스테핑 프레스콧-2M이었습니다.

인텔 64를 구현하는 최초의 인텔 모바일 프로세서는 2006년 7월 27일에 출시된 코어 2 프로세서의 메롬 버전입니다. 인텔의 이전 노트북 CPU(코어 듀오, 펜티엄 M, 셀러론 M, 모바일 펜티엄 4) 중 어느 것도 인텔 64를 구현하지 않습니다.

구현

인텔 64 아키텍처를 구현하는 인텔의 프로세서로는 Pentium 4 F-Series/5x1 시리즈, 506 및 516, Celeron D 모델 3x1, 3x6, 355, 347, 352, 360 및 365와 이후의 모든 Celeron, "Nocona" 이후의 Xeon 모델, Atom 230, 330, D410, D425, D510, N450, N470, N475, N550, N570, N2600 및 N2800, 모든 버전의 Pentium D, Pentium Extreme Edition, Core 2, Core i9, Core i7, Core i5 및 Core i3 프로세서 및 Xeon Phi 7200 시리즈 프로세서.

X86S

X86S는 인텔이 2023년 5월 "인텔 64" 제품을 위해 제안한 X86-64를 단순화한 것입니다.[35] 새로운 아키텍처는 16비트 및 32비트 운영 체제에 대한 지원을 제거하는 반면, 32비트 프로그램은 64비트 OS에서 계속 실행됩니다. CPU는 더 이상 레거시 모드가 없고 직접 64비트 긴 모드에서 시작합니다. 비페이지 모드를 거치지 않고 5단계 페이징으로 전환하는 방법이 있을 것입니다. 구체적으로 제거된 기능은 다음과 같습니다.[36]

인텔은 2008년 A20 게이트가 제거되고 2020년 인텔 펌웨어에서 16비트 및 32비트 OS 지원이 중단된 후 이러한 변화가 논리적으로 뒤따른다고 생각합니다. 레거시 운영 체제에 대한 지원은 하드웨어 가속 가상화 및/또는 링 0 에뮬레이션을 통해 수행됩니다.[36]

VIA의 x86-64 구현

VIA Technologies는 CPU 부문인 Centaur Technology에서 5년 동안 개발한 후 2008년에 x86-64 아키텍처를 처음으로 구현했습니다.[37] 코드명은 "Isiah"로, 64비트 아키텍처는 2008년 1월 24일에 공개되었고,[38] 5월 29일에 VIA Nano 브랜드 이름으로 출시되었습니다.[39]

프로세서는 저전력 가전 제품의 효율성을 높이기 위해 설계된 여러 VIA 전용 x86 확장을 지원합니다. 이사야 아키텍처는 동급 클럭 속도로 이전 세대 VIA 에스더보다 정수 성능은 2배, 부동 소수점 성능은 4배 빨라질 것으로 예상됩니다. 전력 소비 또한 5W에서 25W 범위의 열 설계 전력으로 이전 세대의 VIA CPU와 동등할 것으로 예상됩니다.[40] 완전히 새로운 디자인인 이사야 아키텍처는 이전 제품인 VIA C7 라인에서는 사용할 수 없었던 x86-64 명령어 세트 및 x86 가상화와 같은 기능을 지원하여 구축되었습니다. 암호화 확장을 유지하는 동안.

마이크로아키텍처 수준

2020년에는 AMD, Intel, Red Hat 및 SUSE 간의 공동 작업을 통해 x86-64 기준선 위에 x86-64 아키텍처 레벨(또는 기능 레벨) 3개가 정의되었습니다: x86-64-v2, x86-64-v3 및 x86-64-v4.[41][42] 이러한 수준은 컴파일 시간 최적화를 제공하기 위해 프로그래머가 목표로 삼을 수 있는 특정 기능을 정의합니다. 각 레벨별로 노출되는 기능은 다음과 같습니다.[43]

| 레벨 | CPU 기능 | 예시적인 지시사항 | 지원되는 프로세서 |

|---|---|---|---|

| x86-64 (x86-64-v1) | CMOV | cmov | all x86-64 CPUs |

| CX8 | cmpxchg8b | ||

| FPU | 밭을 일구다 | ||

| FXSR | fx세이브 | ||

| MMX | emms | ||

| OSFXSR | fx세이브 | ||

| SCE | syscall | ||

| SSE | cvtss2si | ||

| SSE2 | cvtpi2pd | ||

| x86-64-v2 | CMPXCHG16B | cmpxchg16b | Intel Nehalem 및 최신 Intel "빅" 코어 |

| LAHF-SAHF | 라후프 | ||

| POPCNT | popcnt | ||

| SSE3 | 서브pd 추가 | ||

| SSE4_1 | 블렌드 pd | ||

| SSE4_2 | pcmpestri | ||

| SSSE3 | 파드드드드 | ||

| x86-64-v3 | AVX | vzeroall | Intel Haswell 및 최신 Intel "빅" 코어(AVX2 지원 모델만 해당) |

| AVX2 | vpermd | ||

| BMI1 | 그리고 | ||

| BMI2 | bzhi | ||

| F16C | vvtph2ps | ||

| FMA | vfmadd132pd | ||

| LZCNT | lzcnt | ||

| 모브 | 움직이다 | ||

| OSXSAVE | xgetbv | ||

| x86-64-v4 | AVX512F | kmovw | Intel Skyrake 및 최신 Intel "빅" 코어(AVX512 지원 모델만 해당) |

| AVX512BW | vdbpsadbw | ||

| AVX512CD | vplzcntd | ||

| AVX512DQ | vpmullq | ||

| AVX512VL | — |

모든 레벨에는 이전 레벨에서 볼 수 있는 기능이 포함됩니다. AES-NI 및 RDRAND를 포함한 범용 계산과 관련이 없는 명령어 세트 확장은 수준 요구 사항에서 제외됩니다.

AMD64와 인텔64의 차이점

거의 동일하지만, 주로 시스템 프로그래밍에 사용되는 몇 가지 자주 사용되지 않는 기계 명령어(또는 상황)의 의미에서 두 명령어 세트 사이에는 약간의 차이가 있습니다.[46] 컴파일러는 일반적으로 적어도 일반 응용 프로그램의 경우 차이를 방지하는 실행 파일(즉, 머신 코드)을 생성합니다. 따라서 이것은 주로 컴파일러, 운영 체제 등의 개발자에게 관심이 있으며, 이들은 개별적이고 특수한 시스템 지침을 다루어야 합니다.

최근 구현 내용

- 인텔 64와 명령어는 소스가 0이고 피연산자 크기가 32비트일 때 AMD64와 다르게 작용합니다. 프로세서는 제로 플래그를 설정하고 대상의 상위 32비트를 정의되지 않은 상태로 유지합니다.[citation needed] 인텔은 이 경우 대상 레지스터에 정의되지 않은 값이 있다고 문서화하지만 실제로는 실리콘에서 AMD와 동일한 동작을 구현합니다(수정되지 않은 대상). 상위 32개의 비트를 보존하지 않는다는 별도의 주장은 검증되지 않았지만 64비트 펜티엄 4나 저전력 아톰과 같은 모든 인텔 마이크로아키텍처가 [47]아닌 코어 2와 스카이레이크에 대해서만 배제되었습니다.

- AMD64는 다른 마이크로코드 업데이트 형식과 제어 MSR(모델별 레지스터)을 필요로 하는 반면, 인텔 64는 32비트 전용 프로세서에서 변경되지 않은 마이크로코드 업데이트를 구현합니다.

- Intel 64에는 AMD64에서 아키텍처로 간주되는 일부 MSR이 부족합니다. 여기에는 다음이 포함됩니다.

SYSCFG,TOP_MEM,그리고.TOP_MEM2. - 인텔 64는 다음을 허용합니다.

SYSCALL/SYSRET64비트 모드(호환 모드 아님)에서만 가능하며,[48]SYSENTER/SYSEXIT두 가지 모드로.[49] AMD64는 부족합니다.SYSENTER/SYSEXIT롱 모드의 두 하위 modes에서. - 64비트 모드에서는 66H(연산자 및 크기 재정의) 접두사가 있는 가까운 분기가 다르게 동작합니다. 인텔 64는 이 접두사를 무시합니다. 명령어에 32비트 부호 확장 오프셋이 있고 명령어 포인터가 잘리지 않습니다. AMD64는 명령어에 16비트 오프셋 필드를 사용하며, 상위 48비트의 명령어 포인터를 지웁니다.

- AMD64가 아닌 Intel 64에서

REX.Wprefix는 먼 pointer 지침과 함께 사용할 수 있습니다.LFS,LGS,LSS, far pointer 인수의 크기를 80비트(64비트 오프셋 + 16비트 세그먼트)로 늘립니다.CALL FAR - Intel 64는 축소된(따라서 더 빠른) 버전의 부동 소수점 상태를 저장하고 복원하는 기능이 부족합니다.

FXSAVE그리고.FXRSTOR설명서)[clarification needed] - Opteron Rev. E와 Athlon 64 Rev. D 이후로 AMD 프로세서는 64비트 게스트의 가상화를 용이하게 하기 위해 LMSLE(Long Mode Segment Limit Enable) 비트를 통해 제한된 세분화 지원을 다시 도입했습니다.[50][51] Zen 3 프로세서에서 LMLSE 지원이 제거되었습니다.

- 다음을 사용하여 비정규 주소로 복귀하는 경우

SYSRET, AMD64 프로세서는 권한 수준 3에서 일반 보호 장애 처리기를 실행하는 [53]반면 Intel 64 프로세서에서는 권한 수준 0에서 실행됩니다.[54] - 다음과 같은 일부 메모리 주문 명령에서 제공하는 주문 보증

LFENCE그리고.MFENCE인텔 64와 AMD64의 차이점:

오래된 구현

이 섹션을 업데이트해야 합니다. 이유는 다음과 같습니다. 몇 년 동안 사용되지 않은 프로세서와 관련된 미래의 시제, 날짜 및 날짜는 일 년이지만 연도는 없습니다. (2023년 1월) |

- 2006년[56] 버전 F 이전의 AMD64 프로세서(DDR에서 DDR2 메모리로의 스위치와 새로운 소켓 AM2, F 및 S1으로 구분됨)에는 다음과 같은 기능이 없었습니다.

CMPXCHG16B의 확장인 명령어.CMPXCHG8B대부분의 80486 이후 프로세서에 존재하는 지침. 와 비슷합니다.CMPXCHG8B,CMPXCHG16B옥타 워드(128비트 값)에 대한 원자 연산을 허용합니다. 이는 잠금 및 대기 시간이 없는 알고리즘에서 일반적으로 포인터 크기보다 큰 데이터를 비교하고 스왑하는 병렬 알고리즘에 유용합니다. 없이.CMPXCHG16B중요 섹션이나 다른 잠금 없는 접근 방식과 같은 해결 방법을 사용해야 합니다.[57] 또한 Windows 8.1 이전 버전의 64비트 Windows에는 8TB보다 큰 사용자 모드 주소 공간이 없습니다.[58] 64비트 버전의 Windows 8.1에는 이 지침이 필요합니다.[59] - 초기 AMD64 및 Intel 64 CPU 부족

LAHF그리고.SAHF64비트 모드의 명령어입니다. AMD는 2004년 10월 Athlon 64를 시작으로 90nm(Revision D) 프로세서를 탑재하여 이러한 지침을 도입했습니다.[60][61] 인텔은 2005년 10월에 NetBurst의 0F47h 이상의 개정판과 함께 이 지침을 도입했습니다.[67] 64비트 버전의 Windows 8.1에는 이 기능이 필요합니다.[59] - 인텔 64를 탑재한 초기 인텔 CPU에는 AMD64 아키텍처의 NX 비트도 부족합니다. 2004년 10월에 스텝핑 E0(0F41h) 펜티엄 4에 추가되었습니다.[68] 이 기능은 모든 버전의 Windows 8에서 필요합니다.

- 초기 인텔 64 구현은 메모리의 36비트(64GB) 물리적 주소 지정이었고, 기존 AMD64 구현은 40비트(1TB) 물리적 주소 지정이었습니다. 인텔은 2005년 3월 29일에 출시된 Xeon MP(포토맥)에서 40비트 물리적 주소 지정을 처음 사용했습니다.[69] 그 차이는 사용자가 볼 수 있는 ISA의 차이가 아닙니다. 2007년 AMD 10h 기반 Opteron은 최초로 48비트(256TB)의 물리적 주소 공간을 제공했습니다.[70][71] 인텔 64의 물리적 주소 지정은 2010년[72] Nehalem-EX에서 44비트(16TB)로, 2011년 Sandy Bridge E에서 46비트(64TB)로 확장되었습니다.[73][74] 인텔은 Ice Lake 3세대 Xeon Scalable 프로세서를 통해 2021년에 가상 주소 지정을 57비트(128PB)로, 물리적 주소 지정을 52비트(4PB)로 늘렸고, 5단계 페이징이 필요했습니다.[75] 이듬해 AMD64는 4세대 EPYC(Genoa)에도 동일한 기능을 추가했습니다.[76] 비서버 CPU는 더 작은 주소 공간을 더 오래 유지합니다.

입양

TOP500이 추적한 슈퍼컴퓨터에서 x86 아키텍처에 대한 64비트 확장 기능이 등장함에 따라 AMD와 인텔은 32비트 x86뿐만 아니라 이전에 그러한 시스템에서 사용되었던 대부분의 RISC 프로세서 아키텍처(PA-RISC, SPARC, Alpha 등)를 대체할 수 있었습니다. 인텔은 처음에 x86을 Itanium 프로세서의 새로운 호환되지 않는 64비트 아키텍처로 대체하려고 시도했지만 실패했습니다.

2020년[update] 현재 후지쯔 A64FX 기반 슈퍼컴퓨터 후가쿠가 1위입니다. 2018년[78] 최초의 ARM 기반 슈퍼컴퓨터가 이 목록에 등장했고, 최근에는 비 CPU 아키텍처 공동 프로세서(GPGPU)도 성능에 큰 역할을 했습니다. 인텔의 Xeon Phi "Knights Corner" 코프로세서는 x86-64 프로세서와 함께 x86-64 프로세서의 일부 벡터 확장을 구현합니다.[79][80]

운영체제 호환성 및 특성

다음 운영 체제 및 릴리스는 x86-64 아키텍처를 롱 모드로 지원합니다.

BSD

드래곤플라이 BSD

x86-64 포트에 대한 예비 인프라 작업은 2004년 2월에 시작되었습니다.[81] 이 개발은 나중에 중단되었습니다. 개발은 2007년[82] 7월에 다시 시작되어 Google Summer of Code 2008 및 SoC 2009 동안 계속되었습니다.[83][84] x86-64 지원을 포함한 최초의 공식 릴리스는 버전 2.4였습니다.[85]

FreeBSD

FreeBSD는 2003년 6월 5.1-RELEASE에서 "amd64"라는 이름으로 x86-64 지원을 처음 추가했습니다. 2004년 1월 5.2-RELEASE를 기준으로 표준 배포 아키텍처로 포함되었습니다. 그 이후로 프리비.SD는 Tier 1 플랫폼으로 지정했습니다. 6.0-RELEASE 버전은 amd64에서 x86 실행 파일을 실행함으로써 몇 가지 단점을 제거했으며 대부분의 드라이버는 x86 아키텍처에서 작동합니다. 리눅스 32비트 ABI 호환성이 현재 작동하는 것과 동일하게 x86 애플리케이션 바이너리 인터페이스(ABI)를 보다 완벽하게 통합하기 위한 작업이 현재 진행 중입니다.

NetBSD

x86-64 아키텍처 지원은 2001년 6월 19일 NetBSD 소스 트리에 처음으로 커밋되었습니다. 2004년 12월 9일에 출시된 NetBSD 2.0을 기준으로 NetBSD/amd64는 완전히 통합되어 지원되는 포트입니다. 32비트 코드는 여전히 64비트 모드에서 지원되며 32비트 syscall을 위한 netbsd-32 커널 호환 계층이 있습니다. NX 비트는 페이지별 세분성(32비트 x86에서 사용 중인 세그먼트 세분성)을 가진 실행 불가능한 스택 및 힙을 제공하는 데 사용됩니다.

오픈BSD

OpenBSD는 2004년 5월 1일 OpenBSD 3.5부터 AMD64를 지원하고 있습니다. AMD64 지원의 완전한 트리 내 구현은 하드웨어가 처음 출시되기 전에 이루어졌는데, 이는 AMD가 그 해 프로젝트의 해커톤을 위해 여러 대의 머신을 대여했기 때문입니다. OpenBSD 개발자들은 NX 비트를 지원하기 때문에 W^X 기능을 쉽게 구현할 수 있었습니다.

오픈BSD의 AMD64 포트 코드는 AMD64 확장을 복제한 인텔 64 프로세서에서도 실행되지만 초기 인텔 64 프로세서에서는 페이지 테이블 NX 비트를 제외했기 때문에 해당 인텔 CPU에는 W^X 기능이 없습니다. 이후 인텔 64 프로세서에서는 NX 비트를 "XD 비트"라는 이름으로 추가했습니다. 대칭 다중 처리(SMP)는 OpenB에서 작동합니다.SD의 AMD64 포트, 2004년 11월 1일 릴리스 3.6부터 시작.

도스

도스 익스텐더 없이 도스에서 롱 모드로 진입할 수 있지만,[86] BIOS나 도스 인터럽트를 호출하기 위해서는 사용자가 리얼 모드로 돌아가야 합니다.

DOS/4GW와 유사한 DOS 확장기로 긴 모드로 진입하는 것도 가능하지만, x86-64에는 가상 8086 모드가 없기 때문에 더 복잡합니다. DOS 자체는 이러한 사실을 알지 못하며, 대용량 스토리지 인터페이스와 같은 적절한 가상화 드라이버 백엔드를 사용하여 DOS를 에뮬레이션으로 실행하지 않는 한 어떠한 이점도 기대할 수 없습니다.

리눅스

리눅스는 2001년 2.4 버전을 시작으로 x86-64 아키텍처를 롱 모드로 실행한 최초의 운영 체제 커널입니다.[87][88] 리눅스는 또한 32비트 실행 파일을 실행하기 위한 하위 호환성을 제공합니다. 이를 통해 32비트 프로그램의 사용을 유지하면서 프로그램을 긴 모드로 재컴파일할 수 있습니다. 현재 리눅스 배포판은 x86-64 네이티브 커널 및 사용자 영역과 함께 제공됩니다. Arch Linux,[89] SUSE, Mandriva 및 Debian과 같은 일부는 사용자가 64비트 배포 매체를 설치할 때 32비트 구성 요소 및 라이브러리 세트를 설치할 수 있으므로 대부분의 기존 32비트 응용 프로그램이 64비트 OS와 함께 실행될 수 있습니다.

리눅스 3.4에 도입된 x32 ABI(Application Binary Interface)는 x32 ABI를 위해 컴파일된 프로그램을 x86-64의 64비트 모드로 실행하면서 32비트 포인터와 데이터 필드만 사용할 수 있도록 해줍니다.[90][91][92] 이렇게 하면 프로그램의 가상 주소 공간이 4GB로 제한되지만, 프로그램의 메모리 사용량이 줄어들기도 하며, 경우에 따라 프로그램을 더 빠르게 실행할 수도 있습니다.[90][91][92]

64비트 Linux에서는 개별 프로세스에 대해 최대 128TB의 가상 주소 공간을 사용할 수 있으며 프로세서 및 시스템 제한에[93] 따라 약 64TB의 물리적 메모리를 처리하거나 5단계 페이징을 사용하면 최대 128PB(가상) 및 4PB(물리적)를 처리할 수 있습니다.[94]

macOS

맥 OS X 10.4.7 이상 버전의 맥 OS X 10.4 및 10.5 버전이 64비트 PowerPC 시스템에서 실행되는 것과 마찬가지로 맥 OS X 10.4 및 10.5 버전도 64비트 인텔 기반 시스템에서 POSIX 및 수학 라이브러리를 사용하여 64비트 명령줄 도구를 실행합니다. Mac OS X 10.4의 64비트 응용 프로그램에서는 다른 라이브러리나 프레임워크가 작동하지 않습니다.[95] 커널과 모든 커널 확장은 32비트입니다.

Mac OS X 10.5는 64비트 PowerPC 시스템뿐만 아니라 64비트 Intel 기반 시스템에서 코코아, Quartz, OpenGL 및 X11을 사용하는 64비트 GUI 애플리케이션을 지원합니다.[96] 모든 비 GUI 라이브러리 및 프레임워크는 이러한 플랫폼에서 64비트 애플리케이션도 지원합니다. 커널과 모든 커널 확장은 32비트입니다.

Mac OS X 10.6은 64비트 커널을 지원하는 MacOS의 첫 번째 버전입니다. 그러나 모든 64비트 시스템에서 64비트 커널을 실행할 수 있는 것은 아니며 기본적으로 64비트 커널을 실행할 수 있는 모든 64비트 시스템에서 실행되지 않습니다.[97] 64비트 커널은 32비트 커널과 마찬가지로 32비트 응용 프로그램을 지원하며, 두 커널 모두 64비트 응용 프로그램을 지원합니다. 32비트 응용 프로그램은 두 커널 모두에서 가상 주소 공간 제한이 4GB입니다.[98][99] 64비트 커널은 32비트 커널 확장을 지원하지 않으며 32비트 커널은 64비트 커널 확장을 지원하지 않습니다.

OS X 10.8은 64비트 커널만 포함하지만 32비트 애플리케이션은 계속 지원하지만 32비트 커널 확장은 지원하지 않습니다.

macOS 10.15는 64비트 커널만 포함하며 더 이상 32비트 애플리케이션을 지원하지 않습니다. 이 지원 제거로 와인에 문제가 발생했습니다.HQ(및 상용 버전인 CrossOver)는 32비트 Windows 애플리케이션을 계속 실행할 수 있어야 합니다. wine32on64로 명명된 이 솔루션은 일반적으로 64비트 애플리케이션에서 CPU를 32비트 호환 모드로 전환하는 스컹크를 추가하는 것이었습니다.[100][101]

macOS는 범용 바이너리 형식을 사용하여 32비트 및 64비트 버전의 응용 프로그램 및 라이브러리 코드를 단일 파일로 패키징합니다. 로드 시 가장 적절한 버전이 자동으로 선택됩니다. Mac OS X 10.6에서는 커널과 32비트 및 64비트 커널을 모두 지원하는 커널 확장에도 범용 이진 형식이 사용됩니다.

솔라리스

Solaris 10 이상의 릴리스는 x86-64 아키텍처를 지원합니다.

Solaris 10의 경우 SPARC 아키텍처와 마찬가지로 운영 체제 이미지가 하나뿐이며 32비트 커널과 64비트 커널을 포함합니다. 이를 "x64/x86" DVD-ROM 이미지라고 합니다. 기본 동작은 64비트 커널을 부팅하여 64비트와 기존 또는 새로운 32비트 실행 파일을 모두 실행할 수 있도록 하는 것입니다. 32비트 커널도 수동으로 선택할 수 있으며, 이 경우 32비트 실행 파일만 실행됩니다. 그 isainfo 명령어를 사용하여 시스템이 64비트 커널을 실행하고 있는지 확인할 수 있습니다.

Solaris 11의 경우 64비트 커널만 제공됩니다. 그러나 64비트 커널은 32비트 및 64비트 실행 파일, 라이브러리 및 시스템 호출을 모두 지원합니다.

창문들

마이크로소프트 윈도우 클라이언트 및 서버의 x64 에디션(윈도우 XP Professional x64 Edition 및 윈도우 서버 2003 x64 Edition)은 2005년 3월에 출시되었습니다.[102] 내부적으로는 동일한 소스 기반과 운영 체제 바이너리를 공유하기 때문에 실제로는 동일한 빌드(5.2.3790.1830 SP1)[103][104]이므로 시스템 업데이트조차도 통합 패키지로 출시되며, 이는 x86용 Windows 2000 Professional 및 Server 에디션과 매우 유사합니다. 또한 다양한 에디션이 있는 윈도우 비스타는 2007년 1월에 출시되었습니다. 윈도우 7은 2009년 7월에 출시되었습니다. 윈도우 서버 2008 R2는 x64 및 Itanium 에디션으로만 판매되었으며, 이후 버전의 윈도우 서버는 x64 에디션만 제공합니다.

Windows 8.1 및 Windows Server 2012 R2 이전 버전의 Windows for x64는 다음과 같은 기능을 제공합니다.

- 프로세스당 8TB의 가상 주소 공간, 사용자 모드와 커널 모드에서 모두 액세스할 수 있으며, 이를 사용자 모드 주소 공간이라고 합니다. x64 프로그램은 시스템의 백업 저장소 제한에 따라 이 모든 것을 사용할 수 있으며 기본적으로 존재하는 "큰 주소 인식" 옵션과 연결되어 있습니다.[105] 이는 32비트 Windows에서 제공하는 기본 2GB 사용자 모드 가상 주소 공간보다 4096배 증가한 것입니다.[106][107]

- 운영 체제의 커널 모드 가상 주소 공간 8TB.[106] 사용자 모드 주소 공간과 마찬가지로 32비트 Windows 버전에 비해 4096배 증가한 것입니다. 늘어난 공간은 주로 파일 시스템 캐시와 커널 모드 "heaps"(페이징되지 않은 풀과 페이징 풀)에 도움이 됩니다. Windows는 초기 AMD64 프로세서가 부족했기 때문에 프로세서가 구현한 256TB 중 총 16TB만 사용합니다.

CMPXCHG16B훈시[108]

윈도우즈 8.1 및 윈도우즈 서버 2012 R2에서는 사용자 모드와 커널 모드 가상 주소 공간이 모두 128TB로 확장되었습니다.[22] 이 버전의 Windows(윈도우)는 다음 버전이 없는 프로세서에 설치되지 않습니다. CMPXCHG16B 설명.

다음과 같은 추가적인 특징은 모든 x64 버전의 Windows에 적용됩니다.

- 기존 32비트 애플리케이션 실행 기능(

.exe프로그램) 및 동적 링크 라이브러리(.dlls) WoW64가 해당 버전에서 지원되는 경우 WoW64를 사용합니다. 또한 32비트 프로그램이 "큰 주소 인식" 옵션과 연결된 경우 기본 2GB 대신 64비트 Windows에서 최대 4GB의 가상 주소 공간을 사용할 수 있습니다([105]옵션 3GB 포함)./3GB32비트 Windows에서 제공하는 부팅 옵션 및 "큰 주소 인식" 링크 옵션).[109] 의 사용과 달리/3GBx86의 부팅 옵션을 사용해도 운영 체제에서 사용할 수 있는 커널 모드 가상 주소 공간이 줄어들지 않습니다. 따라서 32비트 응용 프로그램은 x86-64용으로 재컴파일되지 않더라도 x64 Windows에서 실행되는 이점을 얻을 수 있습니다. - 32비트 및 64비트 애플리케이션 모두 "큰 주소 인식"과 연결되지 않은 경우 가상 주소 공간이 2GB로 제한됩니다.

- 최대 128GB(윈도우 XP/Vista), 192GB(윈도우 7), 512GB(윈도우 8), 1TB(윈도우 서버 2003), 2TB(윈도우 서버 2008/윈도우 10), 4TB(윈도우 서버 2012) 또는 24TB(윈도우 서버 2016/2019)의 물리적 랜덤 액세스 메모리(RAM)[110]를 사용할 수 있는 기능

- LLP64 데이터 모델: C/C++에서 "int" 및 "long" 유형은 너비 32비트, "long long"은 64비트, 포인터에서 파생된 포인터 및 유형은 너비 64비트입니다.

- 커널 모드 장치 드라이버는 64비트 버전이어야 합니다. 64비트 운영 체제 내에서 32비트 커널 모드 실행 파일을 실행할 수 있는 방법이 없습니다. 사용자 모드 장치 드라이버는 32비트 또는 64비트 중 하나일 수 있습니다.

- 16비트 Windows(Win16) 및 DOS 응용 프로그램은 가상 8086 모드를 사용할 수 있는 가상 DOS 머신 서브시스템(NTVDM)이 제거되어 x86-64 버전의 Windows에서 실행되지 않습니다. 가상 8086 모드는 긴 모드로 실행 중에는 입력할 수 없습니다.

- NX(No Execute) 페이지 보호 기능의 전체 구현. 이는 최근 32비트 버전의 Windows(윈도우)에서도 PAE 모드로 시작할 때 구현됩니다.

- 윈도우 NT 계열의 x86 버전에서 FS 세그먼트 디스크립터 대신 GS 세그먼트 디스크립터는 두 가지 운영 체제 정의 구조를 가리키는 데 사용됩니다. 사용자 모드에서는 스레드 정보 블록(NT_TIB), 커널 모드에서는 프로세서 제어 영역(KPCR). 따라서 예를 들어 사용자 모드에서

GS:0는 스레드 정보 블록의 첫 번째 멤버의 주소입니다. 이 규칙을 유지함으로써 x86-64 포트는 더 쉬워졌지만, AMD는 분할된 주소 지정 자체가 현대 운영 체제에서 실제로 사용되지 않더라도 FS 및 GS 세그먼트의 기능을 롱 모드로 유지해야 했습니다.[106] - 초기 보고서에서는 운영 체제 스케줄러가 스레드 컨텍스트 스위치 간에 x87 FPU 시스템 상태를 저장하고 복원하지 않는다고 주장했습니다. 관찰된 동작은 그렇지 않다는 것을 보여줍니다. 커널 모드 전용 스레드(32비트 버전에도 존재하는 제한 사항)를 제외하고 x87 상태가 저장되고 복원됩니다. 마이크로소프트에서 제공하는 가장 최근의 문서에는 x87/MMX/3DNow! 명령이 긴 모드에서 사용될 수 있지만 권장되지 않으며 향후 호환성 문제를 일으킬 수 있다고 나와 있습니다.[109] (3DNow!는 AMD 프로세서에서 더 이상 사용할 수 없습니다. 단,

PREFETCH그리고.PREFETCHW(Broadwell 기준 인텔 프로세서에서도 지원되는 지침)[111] - Jet Database Engine 및 Data Access Objects와 같은 일부 구성 요소는 x86-64 및 IA-64와 같은 64비트 아키텍처로 포팅되지 않습니다.[112][113][114]

- Microsoft Visual Studio는 64비트 Microsoft Windows에서만 실행할 수 있는 x86-64 아키텍처 또는 32비트 Microsoft Windows 또는 WoW64 에뮬레이션 모드에서 32비트 애플리케이션으로 실행할 수 있는 IA-32 아키텍처를 대상으로 네이티브 애플리케이션을 컴파일할 수 있습니다. 관리되는 애플리케이션은 IA-32, x86-64 또는 AnyCPU 모드로 컴파일할 수 있습니다. 처음 두 모드에서 생성된 소프트웨어는 각각 IA-32 또는 x86-64 네이티브 코드 대응물처럼 동작합니다. 그러나 AnyCPU 모드를 사용하는 경우 마이크로소프트 윈도우의 32비트 버전의 응용 프로그램은 32비트 응용 프로그램으로 실행되는 반면 마이크로소프트 윈도우의 64비트 버전에서는 64비트 응용 프로그램으로 실행됩니다.

비디오 게임기

PlayStation 4와 Xbox One, 그리고 그러한 콘솔의 모든 변형은 재규어 마이크로아키텍처를 기반으로 하는 AMD x86-64 프로세서를 통합합니다.[115][116] 펌웨어 및 게임은 x86-64 코드로 작성되며 레거시 x86 코드는 포함되지 않습니다.

현재 세대인 플레이스테이션 5와 엑스박스 시리즈 X와 시리즈 S도 젠 2 마이크로아키텍처를 기반으로 AMD x86-64 프로세서를 통합했습니다.[117][118]

PC로 여겨지지만, 스팀 덱은 Zen 2 마이크로아키텍처를 기반으로 한 맞춤형 AMD x86-64 가속 처리 장치(APU)를 사용합니다.[119]

산업별 명명 규칙

AMD64와 Intel 64는 상당히 유사하기 때문에 많은 소프트웨어 및 하드웨어 제품이 두 가지 구현과의 호환성을 나타내기 위해 하나의 벤더 중립 용어를 사용합니다. 이 프로세서 아키텍처에 대한 AMD의 원래 명칭인 "x86-64"는 변형 "x86_64"[2]와 마찬가지로 여전히 이 목적을 위해 사용됩니다.[3][4] Microsoft[6] 및 Sun Microsystems/Oracle Corporation과 같은 다른 회사에서는 마케팅 자료에 "x64"라는 축약을 사용합니다.[5]

IA-64라는 용어는 Itanium 프로세서를 의미하며, 완전히 다른 명령어 세트이므로 x86-64와 혼동해서는 안 됩니다.

많은 운영 체제와 제품들, 특히 인텔의 시장 진출 이전에 x86-64 지원을 도입한 제품들은 AMD64와 인텔 64를 모두 지칭하기 위해 "AMD64" 또는 "amd64"라는 용어를 사용합니다.

- amd64

- FreeBSD, MidnightBSD, NetBSD 및 OpenBSD와 같은 대부분의 BSD 시스템은 "amd64"라는 아키텍처 이름으로 AMD64와 Intel64를 모두 나타냅니다.

- 데비안, 우분투, 젠투 리눅스와 같은 일부 리눅스 배포판은 AMD64와 인텔 64를 모두 "amd64"라는 아키텍처 이름으로 나타냅니다.

- 마이크로소프트 윈도우의 x64 버전은 내부적으로 AMD64 별명을 사용하여 이 아키텍처를 사용하거나 호환되는 다양한 구성 요소를 지정합니다. 예를 들어, 환경 변수 PROCER_ARCHITURE는 32비트 버전의 "x86"이 아닌 "AMD64" 값을 할당받고, 윈도우 x64 Edition 설치 CD-ROM의 시스템 디렉토리는 32비트 버전의 "i386"과 달리 "AMD64"로 명명됩니다.[120]

- Sun의 Solaris islist 명령은 AMD64 기반 시스템과 Intel 64 기반 시스템을 모두 "amd64"로 식별합니다.

- 자바 개발 키트(JDK): "amd64"라는 이름은 x86-64 파일을 포함하는 디렉터리 이름에 사용됩니다.

- x86_64

- 리눅스 커널과[121] GNU 컴파일러 모음은 64비트 아키텍처를 "x86_64"라고 부릅니다.

- 페도라, openSUSE, 아치 리눅스, 젠투 리눅스와 같은 일부 리눅스 배포판은 이 64비트 아키텍처를 "x86_64"라고 부릅니다.

- Apple macOS는 터미널 명령에서 볼 수 있듯이 64비트 아키텍처를 "x86-64" 또는 "x86_64"로 나타냅니다.

arch[3] 그리고 개발자 문서에 있습니다.[2][4] - 대부분의 다른 BSD 시스템과 달리 DragonFly BSD는 64비트 아키텍처를 "x86_64"라고 부릅니다.

- 하이쿠는 64비트 아키텍처를 "x86_64"라고 부릅니다.

라이센싱

x86-64/AMD64는 AMD에 의해 독점적으로 개발되었습니다. AMD는 AMD64에서 사용되는 기술에 대한 특허를 보유하고 있습니다.[122][123][124] AMD64를 구현하기 위해 해당 특허는 AMD로부터 라이센스를 받아야 합니다. Intel은 AMD와 교차 라이선스 계약을 체결하여 기존 x86 기술에 대한 특허를 AMD에 라이선스하고 x86-64에 사용된 기술에 대한 특허를 AMD로부터 라이선스했습니다.[125] 2009년 AMD와 Intel은 여러 소송과 교차 라이선스 분쟁을 해결하여 교차 라이선스 계약을 연장했습니다.[126][127][128]

참고 항목

메모들

- ^ 명령어 세트에는 다양한 이름이 사용됩니다. 출시 전에는 x86-64와 x86_64가 사용되었고, 출시 당시 AMD는 AMD64라고 이름을 붙였습니다.[1] 인텔은 처음에 IA-32e와 EM64T라는 이름을 사용한 후 구현을 위해 인텔 64에 최종 합의했습니다. Apple을 포함한 업계의 일부는 [2][3][4]x86-64 및 x86_64를 사용하고 다른 일부는 Sun Microsystems[5](현재 Oracle Corporation) 및 Microsoft를 사용합니다.[6] BSD 계열의 OS와 여러 리눅스 배포판은[7][8] 내부적으로 마이크로소프트 윈도우와 마찬가지로 AMD64를 사용합니다.[9][10]

- ^ 실제로 64비트 운영 체제는 일반적으로 16비트 응용 프로그램을 지원하지 않지만, 최신 버전의 마이크로소프트 윈도우에는 32비트 코드로 자동으로 대체하여 16비트 InstallShield 및 마이크로소프트 ACME 설치 프로그램을 효과적으로 지원하는 제한된 해결 방법이 포함되어 있습니다.[12]

참고문헌

- ^ "Debian AMD64 FAQ". Debian Wiki. Archived from the original on September 26, 2019. Retrieved May 3, 2012.

- ^ a b c "x86-64 Code Model". Apple. Archived from the original on June 2, 2012. Retrieved November 23, 2012.

- ^ a b c – Darwin 및 macOS 일반 명령 매뉴얼

- ^ a b c Kevin Van Vechten (August 9, 2006). "re: Intel XNU bug report". Darwin-dev mailing list. Apple Computer. Archived from the original on February 1, 2020. Retrieved October 5, 2006.

The kernel and developer tools have standardized on "x86_64" for the name of the Mach-O architecture

- ^ a b "Solaris 10 on AMD Opteron". Oracle. Archived from the original on July 25, 2017. Retrieved December 9, 2010.

- ^ a b "Microsoft 64-Bit Computing". Microsoft. Archived from the original on December 12, 2010. Retrieved December 9, 2010.

- ^ "AMD64 Port". Debian. Archived from the original on September 26, 2019. Retrieved November 23, 2012.

- ^ "Gentoo/AMD64 Project". Gentoo Project. Archived from the original on June 3, 2013. Retrieved May 27, 2013.

- ^ "WOW64 Implementation Details". Archived from the original on April 13, 2018. Retrieved January 24, 2016.

- ^ "ProcessorArchitecture Class". Archived from the original on June 3, 2017. Retrieved January 24, 2016.

- ^ a b c d e f g h i j k l m n o p q r s t u AMD Corporation (December 2016). "Volume 2: System Programming" (PDF). AMD64 Architecture Programmer's Manual. AMD Corporation. Archived (PDF) from the original on July 13, 2018. Retrieved March 25, 2017.

- ^ Raymond Chen (October 31, 2013). "If there is no 16-bit emulation layer in 64-bit Windows, how come certain 16-bit installers are allowed to run?". Archived from the original on July 14, 2021. Retrieved July 14, 2021.

- ^ "IBM WebSphere Application Server 64-bit Performance Demystified" (PDF). IBM Corporation. September 6, 2007. p. 14. Archived (PDF) from the original on January 25, 2022. Retrieved April 9, 2010.

Figures 5, 6 and 7 also show the 32-bit version of WAS runs applications at full native hardware performance on the POWER and x86-64 platforms. Unlike some 64-bit processor architectures, the POWER and x86-64 hardware does not emulate 32-bit mode. Therefore applications that do not benefit from 64-bit features can run with full performance on the 32-bit version of WebSphere running on the above mentioned 64-bit platforms.

- ^ "AMD Discloses New Technologies At Microporcessor Forum" (Press release). AMD. October 5, 1999. Archived from the original on March 8, 2012. Retrieved November 9, 2010.

- ^ "AMD Releases x86-64 Architectural Specification; Enables Market Driven Migration to 64-Bit Computing" (Press release). AMD. August 10, 2000. Archived from the original on March 8, 2012. Retrieved November 9, 2010.

- ^ 마우러, W. (2010). 전문가용 리눅스 커널 아키텍처. 존 와일리 & 선즈.

- ^ "Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1" (PDF). pp. 4–7. Archived (PDF) from the original on May 16, 2011. Retrieved July 10, 2019.

- ^ a b "BIOS and Kernel Developer's Guide (BKDG) For AMD Family 10h Processors" (PDF). p. 24. Archived (PDF) from the original on April 18, 2016. Retrieved February 27, 2016.

Physical address space increased to 48 bits.

- ^ "Myth and facts about 64-bit Linux" (PDF). March 2, 2008. p. 7. Archived from the original (PDF) on October 10, 2010. Retrieved May 30, 2010.

Physical address space increased to 48 bits

- ^ Shanley, Tom (1998). Pentium Pro and Pentium II System Architecture. PC System Architecture Series (Second ed.). Addison-Wesley. p. 445. ISBN 0-201-30973-4.

- ^ Microsoft Corporation. "What is PAE, NX, and SSE2 and why does my PC need to support them to run Windows 8 ?". Archived from the original on April 11, 2013. Retrieved March 19, 2013.

- ^ a b c d "Memory Limits for Windows Releases". MSDN. Microsoft. November 16, 2013. Archived from the original on January 6, 2014. Retrieved January 20, 2014.

- ^ "5-Level Paging and 5-Level EPT" (PDF). Intel. May 2017. Archived (PDF) from the original on December 5, 2018. Retrieved June 17, 2017.

- ^ 미국 특허 9858198, Larry Siler "4KB 페이지 운영을 지원하는 64KB 페이지 시스템" 2016-12-29, 2018-01-02 발행, Intel Corp.

- ^ "Opteron 6100 Series Motherboards". Supermicro Corporation. Archived from the original on June 3, 2010. Retrieved June 22, 2010.

- ^ "Supermicro XeonSolutions". Supermicro Corporation. Archived from the original on May 27, 2010. Retrieved June 20, 2010.

- ^ "Opteron 8000 Series Motherboards". Supermicro Corporation. Archived from the original on May 27, 2010. Retrieved June 20, 2010.

- ^ "Tyan Product Matrix". MiTEC International Corporation. Archived from the original on June 6, 2010. Retrieved June 21, 2010.

- ^ a b "From the AMI Archives: AMIBIOS 8 and the Transition to EFI". American Megatrends. September 8, 2017. Archived from the original on October 25, 2021. Retrieved October 25, 2021.

- ^ "Intel is Continuing the Yamhill Project?". Neowin. Archived from the original on June 5, 2022. Retrieved June 5, 2022.

- ^ "Craig Barrett confirms 64 bit address extensions for Xeon. And Prescott". The Inquirer. February 17, 2004. Archived from the original on January 12, 2013. Retrieved August 20, 2017.

- ^ ""A Roundup of 64-Bit Computing", from internetnews.com". Archived from the original on September 25, 2012. Retrieved September 18, 2006.

- ^ Lapedus, Mark. "Intel to demo 'CT' 64-bit processor line at IDF". EDN. AspenCore Media. Archived from the original on May 25, 2021. Retrieved May 25, 2021.

- ^ "Intel 64 Architecture". Intel. Archived from the original on June 29, 2011. Retrieved June 29, 2007.

- ^ "Intel Publishes "X86-S" Specification For 64-bit Only Architecture". www.phoronix.com.

- ^ a b "Envisioning a Simplified Intel Architecture for the Future". Intel.

- ^ "VIA to launch new processor architecture in 1Q08" (subscription required). DigiTimes. Archived from the original on December 3, 2008. Retrieved July 25, 2007.

- ^ Stokes, Jon (January 23, 2008). "Isaiah revealed: VIA's new low-power architecture". Ars Technica. Archived from the original on January 27, 2008. Retrieved January 24, 2008.

- ^ "VIA Launches VIA Nano Processor Family" (Press release). VIA. May 29, 2008. Archived from the original on February 3, 2019. Retrieved May 25, 2017.

- ^ "VIA Isaiah Architecture Introduction" (PDF). VIA. January 23, 2008. Archived from the original (PDF) on September 7, 2008. Retrieved July 31, 2013.

- ^ Weimer, Florian (July 10, 2020). "New x86-64 micro-architecture levels". llvm-dev (Mailing list). Archived from the original on April 14, 2021. Retrieved March 11, 2021.

- ^ Weimer, Florian (January 5, 2021). "Building Red Hat Enterprise Linux 9 for the x86-64-v2 microarchitecture level". Red Hat developer blog. Archived from the original on February 20, 2022. Retrieved March 22, 2022.

- ^ "System V Application Binary Interface Low Level System Information". x86-64 psABI repo. January 29, 2021. Archived from the original on February 2, 2021. Retrieved March 11, 2021 – via GitLab.

- ^ "QEMU version 7.2.0 released - QEMU". www.qemu.org. Archived from the original on December 21, 2022. Retrieved January 9, 2023.

- ^ "ChangeLog/7.2 - QEMU". wiki.qemu.org. Archived from the original on January 9, 2023. Retrieved January 9, 2023.

- ^ Wasson, Scott (March 23, 2005). "64-bit computing in theory and practice". The Tech Report. Archived from the original on March 12, 2011. Retrieved March 22, 2011.

- ^ "Discussion on Stack Overflow". March 2021. Archived from the original on January 11, 2023. Retrieved March 2, 2021.

- ^ "Intel 64 and IA-32 Architectures Software Developer's Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A–Z" (PDF). Intel. September 2013. pp. 4–397. Archived (PDF) from the original on October 20, 2013. Retrieved January 21, 2014.

- ^ "Intel 64 and IA-32 Architectures Software Developer's Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z" (PDF). Intel. September 2013. pp. 4–400. Archived (PDF) from the original on October 20, 2013. Retrieved January 21, 2014.

- ^ "How retiring segmentation in AMD64 long mode broke VMware". Pagetable.com. November 9, 2006. Archived from the original on July 18, 2011. Retrieved May 2, 2010.

- ^ "VMware and CPU Virtualization Technology" (PDF). VMware. Archived (PDF) from the original on July 17, 2011. Retrieved September 8, 2010.

- ^ "Linux-Kernel Archive: [PATCH 2/5] KVM: svm: Disallow EFER.LMSLE on hardware that doesn't support it". lkml.indiana.edu. Retrieved November 3, 2023.

- ^ "AMD64 Architecture Programmer's Manual Volume 3: General-Purpose and System Instructions" (PDF). AMD. May 2018. p. 419. Archived (PDF) from the original on August 20, 2018. Retrieved August 2, 2018.

- ^ "Intel 64 and IA-32 Architectures Software Developer's Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z" (PDF). Intel. September 2014. pp. 4–412. Archived (PDF) from the original on January 13, 2015. Retrieved December 28, 2014.

- ^ Hadi Brais, x86 LFENCE Instruction의 의의, 2018년 5월 14일. 2023년 6월 10일 보관.

- ^ "Live Migration with AMD-V™ Extended Migration Technology" (PDF). developer.amd.com. Archived (PDF) from the original on December 6, 2022. Retrieved June 30, 2022.

- ^ Maged M. Michael. "Practical Lock-Free and Wait-Free LL/SC/VL Implementations Using 64-Bit CAS" (PDF). IBM. Archived (PDF) from the original on May 2, 2013. Retrieved January 21, 2014.

- ^ darwou (August 20, 2004). "Why is the virtual address space 4GB anyway?". The Old New Thing. Microsoft. Archived from the original on March 26, 2017. Retrieved March 25, 2017.

- ^ a b "System Requirements—Windows 8.1". Archived from the original on April 28, 2014. Retrieved April 27, 2014.

To install a 64-bit OS on a 64-bit PC, your processor needs to support CMPXCHG16b, PrefetchW, and LAHF/SAHF.

- ^ Petkov, Borislav (August 10, 2009). "Re: [PATCH v2] x86: clear incorrectly forced X86_FEATURE_LAHF_LM flag". Linux kernel mailing list. Archived from the original on January 11, 2023. Retrieved June 30, 2022.

- ^ "Revision Guide for AMD Athlon 64 and AMD Opteron Processors" (PDF). AMD. Archived (PDF) from the original on August 24, 2009. Retrieved July 18, 2009.

- ^ "Product Change Notification 105224 - 01" (PDF). Intel. Archived from the original (PDF) on November 17, 2005.

- ^ "Intel® Pentium® D Processor 800 Sequence and Intel® Pentium® Processor Extreme Edition 840 Specification Update" (PDF). Archived (PDF) from the original on May 18, 2021. Retrieved June 30, 2022.

- ^ "Intel Xeon 2.8 GHz - NE80551KG0724MM / BX80551KG2800HA". CPU-World. Archived from the original on June 28, 2020. Retrieved June 30, 2022.

- ^ Smith, Tony (August 23, 2005). "Intel tweaks EM64T for full AMD64 compatibility". The Register. Archived from the original on June 30, 2022. Retrieved June 30, 2022.

- ^ "Product Change Notification 105271 – 00" (PDF). Intel. Archived from the original (PDF) on November 17, 2005.

- ^ 0F47h는 10월 21일 Pentium D의 B0 스텝에서 첫 선을 보였으나,[62][63] 0F48h는 10월 10일 듀얼 코어 Xeon에서 출시된 LAHF/SAHF도 지원합니다.[64][a]

- ^ "Product Change Notification 104101 – 00" (PDF). Intel. Archived from the original (PDF) on July 16, 2004.

- ^ "64-bit Intel® Xeon™ Processor MP with up to 8MB L3 Cache Datasheet" (PDF). Archived (PDF) from the original on November 17, 2022. Retrieved November 17, 2022.

- ^ "Justin Boggs's at Microsoft PDC 2008". p. 5. Archived from the original on November 17, 2022. Retrieved November 17, 2022.

- ^ Waldecker, Brian. "AMD Opteron Multicore Processors" (PDF). p. 13. Archived (PDF) from the original on December 13, 2022. Retrieved November 17, 2022.

- ^ "Intel® Xeon® Processor 7500 Series Datasheet, Volume 2" (PDF). Archived (PDF) from the original on November 17, 2022. Retrieved November 17, 2022.

- ^ "Intel 64 and IA-32 Architectures Software Developer's Manual". September 2014. p. 2-21. Archived from the original on May 14, 2019.

Intel 64 architecture increases the linear address space for software to 64 bits and supports physical address space up to 46 bits.

- ^ Logan, Tom (November 14, 2011). "Intel Core i7-3960X Review". Archived from the original on March 28, 2016. Retrieved July 1, 2022.

- ^ Ye, Huaisheng. "Introduction to 5-Level Paging in 3rd Gen Intel Xeon Scalable Processors with Linux" (PDF). Lenovo. Archived (PDF) from the original on May 26, 2022. Retrieved July 1, 2022.

- ^ Kennedy, Patrick (November 10, 2022). "AMD EPYC Genoa Gaps Intel Xeon in Stunning Fashion". ServeTheHome. p. 2. Archived from the original on November 17, 2022. Retrieved November 17, 2022.

- ^ "Statistics TOP500 Supercomputer Sites". Top500.org. Archived from the original on March 19, 2014. Retrieved March 22, 2014.

- ^ "Sublist Generator TOP500 Supercomputer Sites". www.top500.org. Archived from the original on December 7, 2018. Retrieved December 6, 2018.

- ^ "Intel® Xeon PhiTM Coprocessor Instruction Set Architecture Reference Manual" (PDF). Intel. September 7, 2012. section B.2 Intel Xeon Phi coprocessor 64 bit Mode Limitations. Archived (PDF) from the original on May 21, 2014. Retrieved May 21, 2014.

- ^ "Intel Powers the World's Fastest Supercomputer, Reveals New and Future High Performance Computing Technologies". Archived from the original on June 22, 2013. Retrieved June 21, 2013.

- ^ "cvs commit: src/sys/amd64/amd64 genassym.c src/sys/amd64/include asm.h atomic.h bootinfo.h coredump.h cpufunc.h elf.h endian.h exec.h float.h fpu.h frame.h globaldata.h ieeefp.h limits.h lock.h md_var.h param.h pcb.h pcb_ext.h pmap.h proc.h profile.h psl.h ..." Archived from the original on December 4, 2008. Retrieved May 3, 2009.

- ^ "AMD64 port". Archived from the original on May 18, 2010. Retrieved May 3, 2009.

- ^ "DragonFlyBSD: GoogleSoC2008". Archived from the original on April 27, 2009. Retrieved May 3, 2009.

- ^ "Summer of Code accepted students". Archived from the original on September 4, 2010. Retrieved May 3, 2009.

- ^ "DragonFlyBSD: release24". Archived from the original on September 23, 2009. Retrieved May 3, 2009.

- ^ "Tutorial for entering protected and long mode from DOS". Archived from the original on February 22, 2017. Retrieved July 6, 2008.

- ^ Andi Kleen (June 26, 2001). "Porting Linux to x86-64". Archived from the original on September 10, 2010.

Status: The kernel, compiler, tool chain work. The kernel boots and work on simulator and is used for porting of userland and running programs

- ^ Andi Kleen. "Andi Kleen's Page". Archived from the original on December 7, 2009. Retrieved August 21, 2009.

This was the original paper describing the Linux x86-64 kernel port back when x86-64 was only available on simulators.

- ^ "Arch64 FAQ". April 23, 2012. Archived from the original on May 14, 2012. Retrieved May 11, 2012.

You can either use the multilib packages or a i686 chroot.

- ^ a b Thorsten Leemhuis (September 13, 2011). "Kernel Log: x32 ABI gets around 64-bit drawbacks". www.h-online.com. Archived from the original on October 28, 2011. Retrieved November 1, 2011.

- ^ a b "x32 - a native 32-bit ABI for x86-64". linuxplumbersconf.org. Archived from the original on May 5, 2012. Retrieved November 1, 2011.

- ^ a b "x32-abi". Google Sites. Archived from the original on October 30, 2011. Retrieved November 1, 2011.

- ^ "AMD64 Port". debian.org. Archived from the original on September 26, 2019. Retrieved October 29, 2011.

- ^ "5-level paging". kernel.org. Retrieved February 7, 2024.

- ^ "Apple – Mac OS X Xcode 2.4 Release Notes: Compiler Tools". Apple Inc. April 11, 2007. Archived from the original on April 22, 2009. Retrieved November 19, 2012.

- ^ "Apple – Mac OS X Leopard – Technology - 64-bit". Apple Inc. Archived from the original on January 12, 2009. Retrieved November 19, 2012.

- ^ "Mac OS X v10.6: Macs that use the 64-bit kernel". Apple Inc. Archived from the original on August 31, 2009. Retrieved November 29, 2012.

- ^ John Siracusa. "Mac OS X 10.6 Snow Leopard: the Ars Technica review". Ars Technica LLC. Archived from the original on October 9, 2009. Retrieved June 20, 2010.

- ^ "Mac OS X Technology". Apple Inc. Archived from the original on March 28, 2011. Retrieved November 19, 2012.

- ^ Schmid, J; Thomases, K; Ramey, J; Czekalla, U; Mathieu, B; Abhiram, R (September 10, 2019). "So We Don't Have a Solution for Catalina...Yet". CodeWeavers Blog. Archived from the original on September 29, 2021. Retrieved September 29, 2021.

- ^ Thomases, Ken (December 11, 2019). "win32 on macOS". WineHQ. Archived from the original on November 11, 2020. Retrieved September 29, 2021.

- ^ "Microsoft Raises the Speed Limit with the Availability of 64-Bit Editions of Windows Server 2003 and Windows XP Professional". Microsoft News Center (Press release). April 25, 2005. Retrieved January 29, 2024.

- ^ "A description of the x64-based versions of Windows Server 2003 and of Windows XP Professional x64 Edition". Microsoft Support. Archived from the original on April 20, 2016. Retrieved August 14, 2016.

- ^ "Windows Server 2003 SP1 Administration Tools Pack". Microsoft Download Center. Archived from the original on August 27, 2016. Retrieved August 14, 2016.

- ^ a b "/LARGEADDRESSAWARE (Handle Large Addresses)". Visual Studio 2022 Documentation – MSVC Linker Reference – MSVC Linker Options. Microsoft. Archived from the original on December 21, 2022. Retrieved December 21, 2022.

The /LARGEADDRESSAWARE option tells the linker that the application can handle addresses larger than 2 gigabytes.

- ^ a b c Matt Pietrek (May 2006). "Everything You Need To Know To Start Programming 64-Bit Windows Systems". Microsoft. Retrieved April 18, 2023.

- ^ Chris St. Amand (January 2006). "Making the Move to x64". Microsoft. Retrieved April 18, 2023.

- ^ "Behind Windows x86-64's 44-bit Virtual Memory Addressing Limit". Archived from the original on December 23, 2008. Retrieved July 2, 2009.

- ^ a b "64-bit programming for Game Developers". Retrieved April 18, 2023.

- ^ "Memory Limits for Windows and Windows Server Releases". Microsoft. Retrieved April 18, 2023.

- ^ Kingsley-Hughes, Adrian (August 23, 2010). "AMD says goodbye to 3DNow! instruction set". ZDNet. Archived from the original on January 8, 2023. Retrieved January 8, 2023.

- ^ "General Porting Guidelines". Programming Guide for 64-bit Windows. Microsoft Docs. Retrieved April 18, 2023.

- ^ "Driver history for Microsoft SQL Server". Microsoft Docs. Retrieved April 18, 2023.

- ^ "Microsoft OLE DB Provider for Jet and Jet ODBC driver are available in 32-bit versions only". Office Access. Microsoft Docs. KB957570. Retrieved April 18, 2023.

- ^ Anand Lal Shimpi (May 21, 2013). "The Xbox One: Hardware Analysis & Comparison to PlayStation 4". Anandtech. Archived from the original on June 7, 2013. Retrieved May 22, 2013.

- ^ "The Tech Spec Test: Xbox One Vs. PlayStation 4". Game Informer. May 21, 2013. Archived from the original on June 7, 2013. Retrieved May 22, 2013.

- ^ "What to expect from Sony 'PlayStation 5' launch in November". The Indian Express. August 31, 2020. Archived from the original on September 19, 2020. Retrieved September 14, 2020.

- ^ Cutress, Dr Ian. "Hot Chips 2020 Live Blog: Microsoft Xbox Series X System Architecture (6:00pm PT)". www.anandtech.com. Archived from the original on September 17, 2020. Retrieved September 14, 2020.

- ^ Hollister, Sean (November 12, 2021). "Steam Deck: Five big things we learned from Valve's developer summit". The Verge. Archived from the original on February 7, 2022. Retrieved November 12, 2021.

- ^ "ProcessorArchitecture Fields". Archived from the original on April 28, 2015. Retrieved September 4, 2013.

- ^ "An example file from Linux 3.7.8 kernel source tree displaying the usage of the term x86_64". Archived from the original on September 23, 2005. Retrieved February 17, 2013.

- ^ US 6877084

- ^ US 6889312

- ^ US 6732258

- ^ "Patent Cross License Agreement Between AMD and Intel". January 1, 2001. Archived from the original on June 21, 2007. Retrieved August 23, 2009.

- ^ "AMD Intel Settlement Agreement". Archived from the original on July 7, 2017. Retrieved September 18, 2017.

- ^ Stephen Shankland and Jonathan E. Skillings (November 12, 2009). "Intel to pay AMD $1.25 billion in antitrust settlement". CNET. Archived from the original on November 8, 2012. Retrieved April 24, 2012.

- ^ Smith, Ryan (November 12, 2009). "AMD and Intel Settle Their Differences: AMD Gets To Go Fabless". AnandTech. Archived from the original on May 13, 2010.

외부 링크

- AMD 개발자 가이드, 설명서 및 ISA 문서

- x86-64: x86 아키텍처를 64비트로 확장 – AMD64 설계자의 기술 강연(비디오 아카이브)과 동일한 스피커의 두 번째 강연(비디오 아카이브)

- AMD의 "강화된 바이러스 보호"

- Intel, 완전한 AMD64 호환을 위해 EM64T 조정

- 분석가: 인텔 역공학 AMD64

- Intel IA32e와 AMD64의 차이점에 대한 초기 보고서

- GCC Summit 2003의 Andreas Jeger가 64비트 GNU/Linux Systems로 포팅합니다. 32비트에서 64비트로의 전환을 위한 거의 모든 실용적인 측면을 설명하는 훌륭한 논문입니다.

- 인텔 64 아키텍처

- 인텔 소프트웨어 네트워크: "64비트"

- 터보IRC.DOS에서 원시 모드로 보호 모드와 긴 모드로 전환하는 방법의 예를 포함한 COM 튜토리얼

- 64비트 시스템으로의 프로그램 마이그레이션 7단계

- Windows 릴리스의 메모리 제한