인텔 8259

Intel 8259인텔 8259는 인텔 8085 및 인텔 8086 마이크로프로세서용으로 설계된 프로그래머블 인터럽트 컨트롤러(PIC)입니다.초기 부품은 8259로, 이후 A 서픽스 버전은 8086 또는 8088 프로세서와 호환성이 있어 사용할 수 있습니다.8259는 여러 인터럽트 입력 소스를 호스트 마이크로프로세서에 대한 단일 인터럽트 출력에 결합하여 시스템에서 사용 가능한 인터럽트 수준을 프로세서 칩에서 볼 수 있는 1~2가지 수준을 넘어 확장합니다.8259A는 원래 IBM PC 및 IBM PC AT에서 ISA 버스를 위한 인터럽트 컨트롤러였습니다.

8259는 1976년에 인텔의 MCS 85 패밀리의 일부로서 도입되었습니다.8259A는 1981년에 처음 도입된 PC에 포함되어 1983년에 도입된 PC/XT에 의해 유지보수되었습니다.두 번째 8259A는 PC/AT의 도입과 함께 추가되었습니다.8259는 Symmetric Multi-Processor PC에 도입된 이후 인텔 APIC 아키텍처와 공존해 왔습니다.최신 PC는 인텔 APIC 아키텍처를 채택하여8259A를 단계적으로 폐지하기 시작했습니다.단, 8259A 인터페이스는 더 이상 별도의 칩이 아니지만 최신 x86 [1]메인보드의 Platform Controller Hub 또는 Southbridge 칩셋에 의해 제공됩니다.

기능 설명

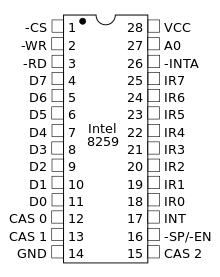

8259의 주요 신호 핀은 다음과 같습니다.IRQ0 ~ IRQ7이라는 이름의 8개의 인터럽트 입력 요구 라인, INTA, D0 ~ D7이라는 인터럽트 확인 응답 라인, 인터럽트 레벨 또는 벡터오프셋을 통신합니다.기타 접속에는 8259간의 캐스케이드 접속용 CAS0~CAS2가 있습니다.

최대 8개의 슬레이브 8259를 마스터 8259에 캐스케이드하여 최대 64개의 IRQ를 제공할 수 있습니다.한 개의 슬레이브 8259의 INT 회선을 마스터 8259의 IRQ 회선에 접속함으로써 8259를 캐스케이드할 수 있습니다.

End Of Interrupt(EOI; 엔드 오브 인터럽트) 조작은 특정 EOI, 비특정 EOI 및 자동 EOI를 지원합니다.특정 EOI는 ISR에서 인식되는 IRQ 레벨을 지정합니다.비특정 EOI는 ISR의 IRQ 레벨을 리셋합니다.자동 EOI는 인터럽트가 확인 응답된 직후 ISR의 IRQ 레벨을 리셋합니다.

에지 및 레벨 인터럽트 트리거 모드는 8259A에서 지원됩니다.고정 우선 모드와 회전 우선 모드가 지원됩니다.

8259 는, 8080/8085 또는 8086/8088 로 동작하도록 설정할 수 있습니다.8086/8088에서는 인터럽트가 발생하면 인터럽트 컨트롤러가 데이터 버스에 인터럽트 번호를 제공합니다.8080/8085의 인터럽트 사이클은 데이터 버스에서 3바이트를 발행합니다(8080/8085 명령 세트의 CALL 명령에 대응).

8259A는 8259(특히 버퍼링 모드 및 레벨 트리거 모드)와 비교하여 추가 기능을 제공하며 상위 호환성이 있습니다.

프로그래밍에 관한 고려 사항

DOS 및 Windows

8259를 DOS 및 Microsoft Windows와 함께 프로그래밍하면 하위 호환성을 위해 많은 혼란스러운 문제가 발생했는데, 이는 1981년에 처음 도입된 PC까지 거슬러 올라갑니다.

첫 번째 문제는 거의 두 번째 문제의 근원이다.DOS 디바이스 드라이버는, 디바이스의 수리가 종료하면, 비특정 EOI 를 8259 에 송신합니다.이는 DOS에서 8259의 다른 EOI 모드를 사용하는 것을 방지하고 마스터 8259에서 슬레이브 8259로 재루팅된 디바이스 인터럽트 간의 차이를 배제합니다.

두 번째 호에서는 PC/AT에 슬레이브 8259가 도입된 이후의 IRQ2 및 IRQ9 사용에 대해 설명합니다.슬레이브 8259의 INT 출력은 마스터의 IR2에 연결됩니다.ISA 버스의 IRQ2 회선은 원래 이 IR2에 연결되어 슬레이브의 IR1에 재루팅되었습니다.따라서 오래된 IRQ2 라인은 CPU에 IRQ9를 생성합니다.IRQ2용으로 설정된 DOS 디바이스 드라이버와의 하위 호환성을 확보하기 위해 IRQ9용 BIOS에 의해 인터럽트가 원래 IRQ2 핸들러로 리다이렉트 되는 핸들러가 설치됩니다.

PC에서 BIOS(및 DOS)는 전통적으로 마스터 8259 인터럽트 요구(IRQ0-IRQ7)를 인터럽트 벡터 오프셋 8(INT08-INT0F)에 매핑하고 슬레이브 8259(PC/AT 이후) 인터럽트 요구(IRQ8-IRQ15157INT70)를 인터럽트 벡터 오프셋에 매핑한다.이것은 최초의 32(INT00-INT1F) 인터럽트 벡터가 프로세서에 의해 내부 예외를 위해 예약되어 있는데도 수행되었습니다(이것은 PC 설계상 어떠한 이유로 무시되었습니다).예외용으로 예약된 벡터 때문에 대부분의 다른 운영체제는 (최소한 마스터) 8259 IRQ(플랫폼에서 사용되는 경우)를 다른 인터럽트 벡터 베이스 오프셋에 매핑합니다.

기타 운영 체제

대부분의 다른 운영체제는 디바이스 드라이버의 기대치를 변경할 수 있으므로 Auto-EOI와 같은 다른 8259 모드도 사용할 수 있습니다.이는 특히 8259s와 통신할 때 I/O 주소 공간 지연에 상당한 시간이 소요될 수 있는 최신 x86 하드웨어에서 중요합니다.또한 8259s를 탑재한 멀티프로세서x86 시스템에서 중요한 섹션 등 동기화된 다수의 최적화가 가능합니다.

에지 및 레벨 트리거 모드

ISA 버스는 레벨 트리거 인터럽트를 지원하지 않기 때문에 레벨 트리거 모드는 ISA 장치에 연결된 인터럽트에는 사용되지 않을 수 있습니다.즉, PC/XT, PC/AT 및 호환 시스템에서는 8259를 에지 트리거 모드로 프로그래밍해야 합니다.MCA 시스템에서 장치는 레벨 트리거 인터럽트를 사용하며 인터럽트 컨트롤러는 항상 레벨 트리거 모드로 작동하도록 유선 연결되어 있습니다.새로운 EISA, PCI 및 그 이후의 시스템에서는 Edge/Level Control Register(ELCR; 엣지/레벨 제어 레지스터)가 IRQ 회선 단위로 모드를 제어하기 때문에 ISA 버스를 사용하는 시스템에서는 8259의 모드가 사실상 무관합니다.ELCR은 시스템 부팅 시 BIOS에 의해 올바르게 동작하도록 프로그램되어 있습니다.

ELCR은 x86 I/O주소 공간에 0x4d0 및 0x4d1이 있습니다.각 비트는 8비트 폭이며 8259s의 IRQ에 대응합니다.비트가 설정되면 IRQ가 레벨 트리거 모드에 있고, 그렇지 않으면 IRQ가 에지 트리거 모드에 있습니다.

스플리어스 인터럽트

8259는 다수의 조건에 응답하여 스플리어스 인터럽트를 생성합니다.

첫 번째는 IRQ 회선이 확인 응답되기 전에 어사트 해제되는 것입니다.이 문제는 IRQ 회선의 노이즈로 인해 발생할 수 있습니다.에지 트리거 모드에서는 노이즈가 라인을 100ns 동안 낮은 상태로 유지해야 합니다.노이즈가 감소하면 풀업 저항기가 IRQ 라인을 하이로 되돌려 잘못된 인터럽트를 생성합니다.레벨 트리거 모드에서는 노이즈로 인해 시스템 INTR 라인에서 신호 레벨이 높아질 수 있습니다.시스템이 확인 응답 요구를 송신하면, 8259 는 해결할 필요가 없기 때문에, 응답으로 IRQ7 를 송신합니다.이 첫 번째 케이스는 가짜 IRQ7을 생성합니다.

8259 의 마스크 해제와 IRQ 입력 어사션이 올바르게 동기화되지 않은 경우에도 같은 현상이 발생할 수 있습니다.많은 시스템에서 IRQ 입력은 I/O 쓰기에 의해 할당 해제되고 프로세서는 쓰기가 I/O 디바이스에 도달할 때까지 기다리지 않습니다.IRQ 입력이 강조 해제되기 전에 프로세서가 계속 8259 IRQ의 마스크를 해제하면 8259는 다시 INTR을 강조합니다.프로세서가 이 INTR을 인식하고 8259로부터 IRQ를 읽기 위한 확인 응답을 발행할 때까지 IRQ 입력은 어사트 해제되어 8259는 스플리어스 IRQ7을 반환한다.

두 번째는 슬레이브 8259의 IRQ 회선이 인터럽트 확인 응답의 하강 에지에서 비활성화되어 있을 때 마스터 8259의 IRQ2가 하이인 것입니다.이 두 번째 케이스에서는 스플리어스 IRQ15가 생성되지만 드문 경우입니다.

PC/XT 및 PC/AT

PC/XT ISA 시스템에는 8259 컨트롤러가 1개, PC/AT 이후의 시스템에는 마스터 및 슬레이브 컨트롤러가 2개 있습니다.IRQ0 ~ IRQ7은 마스터 8259의 인터럽트 회선이며, IRQ8 ~ IRQ15는 슬레이브 8259의 인터럽트 회선입니다.8259의 핀 라벨은 IR0 ~ IR7 입니다.IRQ0 ~ IRQ15는 8259가 접속되어 있는ISA 버스 회선의 이름입니다.

변종

| 모델 번호 | 테크놀로지 | 온도 범위 | 패키지 | 발매일 | 가격 (USD)[list 1] |

|---|---|---|---|---|---|

| ID8259 | -40 ~ +85 °C[2] | 1979년 3월/4월[3] | $23.15 | ||

| M8259 | 군사의 | 1979년 3월/4월[4] | $95.00 | ||

| 82C59A[5] | CMOS | 1984년 7월/8월 | |||

| 8259 | 28핀 PLCC[list 2][6] |

「 」를 참조해 주세요.

- Advanced Programmable Interrupt Controller(APIC)

- IF(x86 플래그)

- 인터럽트 핸들러

- 인터럽트 레이텐시

- Non-Maskable Interrupt(NMI; 마스크 불가능 인터럽트)

- 프로그래머블 인터럽트 컨트롤러(PIC)

레퍼런스

- ^ http://pdf.datasheetcatalog.com/datasheet/Intel/mXvqwzr.pdf[베어 URL PDF]

- ^ Intel Corporation, "8086 산업환경에서 이용 가능", 인텔 프리뷰 스페셜호: 16비트 솔루션, 1980년 5월/6월, 29페이지

- ^ Intel Corporation, "마이크로컴퓨터 컴포넌트:새로운 산업용 제품 라인은 산업용 어플리케이션에서 동작하는 신뢰성 높은 컴포넌트에 대한 수요에 부응합니다." 인텔 프리뷰, 1979년 3월/4월, 11페이지

- ^ Intel Corporation, "군사 제품:인텔 행진 계속!)" 인텔 프리뷰, 1979년 3월/4월, 19페이지

- ^ Intel Corporation, "NewsBit:인텔·라이센스 Oki의 CMOS 버전의 몇 가지 제품」, 솔루션, 1984년 7월/8월, 페이지 1.

- ^ Ashborn, Jim; "Advanced Packaging: A Little Goes A Long Way", Intel Corporation, Solutions, 1986년 1월 / 2월, 페이지 2

- 길루위, 프랭크 밴문서화되어 있지 않은 PC.A-W Developers Press, 1997. ISBN0-201-47950-8

- 맥기번, 조셉인터럽트 주도의 PC 시스템 설계.안나북스, 1998년ISBN 0-929392-50-7

- IBM Personal System/2 하드웨어 인터페이스 기술 참조 - 아키텍처.IBM, 1990년IBM 출판 84F8933