페이지 테이블

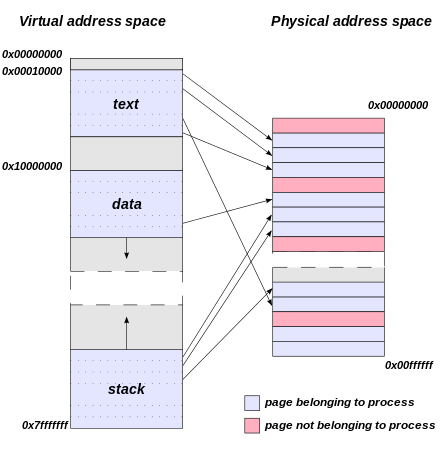

Page table페이지 테이블은 컴퓨터 운영 체제에서 가상 메모리 시스템이 가상 주소와 물리적 주소 간의 매핑을 저장하기 위해 사용하는 데이터 구조다.가상 주소는 액세스 프로세스에 의해 실행되는 프로그램에 의해 사용되는 반면 물리적 주소는 하드웨어에 의해, 또는 더 구체적으로는 RAM(Random-Access Memory) 하위 시스템에 의해 사용된다.페이지 테이블은 메모리의 데이터에 액세스하는 데 필요한 가상 주소 변환의 핵심 구성요소다.

페이지 테이블의 역할

가상 메모리를 사용하는 운영 체제에서는 모든 프로세스에서 메모리의 크고 연속적인 섹션으로 작동하고 있다는 인상을 준다.물리적으로 각 프로세스의 메모리는 물리적 메모리의 서로 다른 영역으로 분산되거나, 일반적으로 하드 디스크 드라이브(HDD) 또는 솔리드 스테이트 드라이브(SSD)로 2차 스토리지로 이동(정지)되었을 수 있다.

프로세스가 메모리에 있는 데이터에 대한 액세스를 요청할 때 프로세스에서 제공하는 가상 주소를 해당 데이터가 저장된 실제 메모리의 물리적 주소에 매핑하는 것은 운영 체제의 책임이다.페이지 테이블은 운영 체제가 가상 주소의 매핑을 물리적 주소에 저장하는 곳으로, 각 매핑을 페이지 테이블 항목(PTE)이라고도 한다.[1][2]

번역 과정

CPU 내부의 MMU(메모리 관리 장치)는 운영 체제의 페이지 테이블에서 최근에 사용한 매핑의 캐시를 저장한다.이를 TLB(translation lookaside buffer, translation lookaside buffer, tLB)라고 하는데, 이것은 연관 캐시다.

가상 주소를 물리적 주소로 변환해야 할 경우 TLB를 먼저 검색한다.TLB 적중이라고 알려진 일치 항목이 발견되면 물리적 주소가 반환되고 메모리 액세스가 계속될 수 있다.그러나 TLB 미스라고 하는 일치 항목이 없는 경우, MMU나 운영 체제의 TLB 미스 핸들러는 일반적으로 페이지 테이블에서 주소 매핑을 조회하여 매핑이 존재하는지, 이것을 페이지워크라고 한다.존재하는 경우 TLB에 다시 기록되는데, 이는 가상 메모리 시스템에서 하드웨어가 TLB를 통해 메모리에 접근하고 장애 명령이 다시 시작되기 때문에 수행되어야 하며, 이는 병렬로 발생할 수도 있다.후속 번역을 통해 TLB 적중 현상이 발생하고, 메모리 액세스가 계속된다.

번역 실패

페이지 테이블 조회가 실패하고 다음 두 가지 이유로 페이지 오류가 발생할 수 있다.

- 가상 주소에 사용할 수 있는 변환이 없는 경우 조회가 실패할 수 있으며, 이는 가상 주소가 유효하지 않음을 의미한다.이는 일반적으로 프로그래밍 오류로 인해 발생하며 운영 체제는 문제를 처리하기 위해 어떤 조치를 취해야 한다.현대적인 운영체제에서는 분할 결함 신호가 위반 프로그램으로 전송되는 원인이 될 것이다.

- 페이지가 현재 물리적 메모리에 상주하지 않는 경우에도 조회가 실패할 수 있다.다른 페이지를 위한 공간을 확보하기 위해 요청한 페이지를 물리적 메모리에서 벗어난 경우 이 문제가 발생할 수 있다.이 경우 페이지는 하드 디스크 드라이브와 같은 매체에 위치한 2차 저장소(이 2차 저장소 또는 "백킹 저장소")로 호출되며, 디스크 파티션인 경우에는 스왑 파티션, 스왑 파일 또는 페이지 파일인 경우에는 스왑 파일 또는 페이지 파일이라고 불린다.이 경우 디스크에서 페이지를 가져와 실제 메모리에 다시 넣어야 한다.가상 메모리에 매핑되고 요청 시 물리적 메모리에 로드되는 메모리 매핑 파일에도 유사한 메커니즘이 사용된다.

물리적 메모리가 가득 차지 않은 경우 이것은 간단한 작업이며, 페이지는 물리적 메모리에 다시 기록되고, 페이지 테이블과 TLB는 업데이트되고, 명령은 다시 시작된다.그러나 물리적 메모리가 가득 차면 요청된 페이지를 위한 공간을 확보하기 위해 물리적 메모리에 있는 하나 이상의 페이지를 호출해야 한다.이전에 물리적 메모리에 있던 페이지가 더 이상 존재하지 않음을 표시하고, 디스크에 있던 페이지가 이제 물리적 메모리에 있음을 표시하기 위해 페이지 테이블을 업데이트할 필요가 있다.TLB 또한 페이지 아웃 페이지를 제거하는 등 업데이트해야 하며 명령이 다시 시작되었다.어느 페이지를 페이지 아웃시킬 것인가는 페이지 교체 알고리즘의 주제다.

일부 MMU는 페이지가 현재 물리적 메모리에 저장되어 있고 프로세스의 가상 주소 공간에 매핑되어 있는지 여부에 관계없이 다른 이유로 페이지 장애를 트리거한다.

- 페이지 테이블에 읽기 전용 비트가 설정되어 있을 때 쓰기를 시도하면 페이지 오류가 발생한다.이것은 많은 운영체제의 쓰기 복사 구현의 일반적인 부분이다. 이것은 또한 프로세스가 읽을 수는 있지만 쓰기가 허용되지 않는 위치에 쓰기가 수행될 때 발생할 수 있으며, 이 경우 프로세스에 신호가 전달된다.

- 페이지 테이블에 NX 비트(비실행 비트)가 설정되어 있을 때 코드를 실행하려고 하면 페이지 오류가 발생한다.이것은 읽기 전용 비트와 함께 운영 체제에서 사용할 수 있으며, 일부 종류의 착취를 중지하는 쓰기 XOR 실행 기능을 제공한다.[3]

프레임 테이블 데이터

가장 간단한 페이지 테이블 시스템은 종종 프레임 테이블과 페이지 테이블을 유지한다.프레임 테이블에는 매핑된 프레임에 대한 정보가 들어 있다.보다 고급화된 시스템에서 프레임 테이블은 페이지가 속한 주소 공간, 통계 정보 또는 기타 배경 정보에 대한 정보도 포함할 수 있다.

페이지 테이블 데이터

페이지 테이블은 페이지 테이블 항목의 배열이다.

페이지 테이블 항목

각 페이지 테이블 항목(PTE)은 페이지의 가상 주소와 실제 프레임의 주소 간의 매핑을 보관한다.또한 현재 비트, 지저분하거나 수정된 비트, 주소 공간 또는 프로세스 ID 정보와 같은 페이지에 대한 보조 정보도 있다.

하드 디스크 드라이브와 같은 보조 저장소를 사용하여 물리적 메모리를 늘릴 수 있다.페이지는 물리적 메모리와 디스크로 호출할 수 있다.현재 비트는 물리적 메모리에 현재 존재하는 페이지나 디스크에 있는 페이지를 나타낼 수 있으며, 이러한 다른 페이지, 즉 디스크에서 페이지를 로드하여 물리적 메모리에서 다른 페이지를 페이지화할지 여부를 나타내는 방법을 나타낼 수 있다.

더티 비트는 성능 최적화를 가능하게 한다.실제 메모리에 페이징된 다음 에서 읽고 나서 다시 페이징된 디스크의 페이지는 페이지가 변경되지 않았으므로 디스크에 다시 쓸 필요가 없다.그러나 페이지를 페이징한 후 페이지에 쓴 경우 페이지의 더티 비트가 설정되므로 페이지를 백업 저장소에 다시 기록해야 함을 알 수 있다.이 전략에 따르면 백업 저장소는 페이지 복사본을 메모리에 저장한 후 보존해야 한다.지저분한 비트를 사용하지 않을 경우, 백업 저장소는 어느 순간에 모든 페이징된 페이지의 순간 총 크기만큼만 커지면 된다.더러운 비트를 사용하면 항상 일부 페이지가 물리적 메모리와 백업 저장소에 모두 존재하게 된다.

단일 주소 공간 운영 체제가 아닌 운영 체제에서는 가상 메모리 관리 시스템이 어떤 페이지를 어떤 프로세스에 연결할지 알 수 있도록 주소 공간이나 프로세스 ID 정보가 필요하다.두 프로세스는 서로 다른 목적으로 동일한 가상 주소 두 개를 사용할 수 있다.페이지 테이블은 두 프로세스에 대해 서로 다른 가상 메모리 매핑을 제공해야 한다.이는 두 개의 프로세스에 구별되는 주소 맵 식별자를 할당하거나 프로세스 ID를 사용하여 수행할 수 있다.프로세스 ID를 가상 메모리 페이지와 연결하면 비활성 프로세스와 관련된 페이지, 특히 코드 페이지가 페이징된 프로세스는 활성 프로세스에 속하는 페이지보다 즉시 필요하지 않을 가능성이 높기 때문에 페이지 선택을 도울 수 있다.

페이지 테이블 항목에 프로세스 고유 식별자를 태그하는 대신 페이지 테이블 자체가 프로세스 컨텍스트의 일부가 되도록 각 프로세스에 대해 다른 가상 메모리 페이지를 점유할 수 있다.이러한 구현에서는 프로세스가 더 이상 메모리에 상주하지 않을 때마다 프로세스의 페이지 테이블을 호출할 수 있다.

페이지 테이블 유형

페이지 테이블에는 여러 가지 유형이 있는데, 이는 서로 다른 요구사항에 최적화되어 있다.기본적으로 맨 뼈의 페이지 테이블은 가상 주소, 이 가상 주소 아래에 있는 물리적 주소 및 일부 주소 공간 정보를 저장해야 한다.

반전된 페이지 테이블

뒤집힌 페이지 테이블(IPT)은 일반 시스템 RAM을 사용하는 TLB의 오프칩 확장이라고 가장 잘 생각되고 있다.실제 페이지 테이블과 달리 모든 현재 매핑을 포함할 수 있는 것은 아니다.운영 체제는 MIPS 형식의 소프트웨어로 채워진 TLB와 마찬가지로 누락 처리를 위한 준비를 해야 한다.

통합 생산팀은 페이지 테이블과 프레임 테이블을 하나의 데이터 구조로 결합한다.그 중심에는 행의 수가 메모리의 프레임 수와 동일한 고정 크기 테이블이 있다.프레임이 4,000개일 경우, 반전된 페이지 테이블은 4,000개의 행을 가진다.각 행에는 가상 페이지 번호(VPN), 물리적 페이지 번호(물리적 주소가 아님), 일부 다른 데이터 및 충돌 체인을 생성하기 위한 수단이 있다.

코어 IPT 구조의 모든 항목을 검색하는 것은 비효율적이며, 해시 테이블을 사용하여 가상 주소(그리고 필요한 경우 주소 공간/PID 정보)를 IPT의 인덱스에 매핑할 수 있다. - 여기서 충돌 체인이 사용된다.이 해시 테이블을 해시 앵커 테이블이라고 한다.해싱 기능은 일반적으로 커버리지에 최적화되어 있지 않으므로 원시 속도가 더 바람직하다.물론 해시 테이블은 충돌을 겪는다.이 선택된 해싱 기능으로 인해 사용 중 충돌이 많이 발생할 수 있으므로 테이블의 각 항목에 대해 VPN을 제공하여 검색된 항목인지 또는 충돌인지를 확인한다.

매핑을 검색할 때 해시 앵커 테이블을 사용한다.항목이 없는 경우 페이지 오류가 발생한다.그렇지 않으면 항목이 발견된다.아키텍처에 따라, 입력은 다시 TLB에 배치되고 메모리 참조는 재시작되거나, 또는 충돌 체인이 소진되어 페이지 결함이 발생할 때까지 추적될 수 있다.

이 스키마의 가상 주소는 둘로 분할될 수 있으며, 전반부는 가상 페이지 번호, 후반부는 해당 페이지의 오프셋이 될 수 있다.

이 설계의 주요 문제점은 해시함수에 의해 야기되는 캐시 위치 불량이다.트리 기반 설계는 인접 페이지에 대한 페이지 테이블 항목을 인접 위치에 배치하여 이를 피하지만, 반전된 페이지 테이블은 모든 곳에 항목을 분산시킴으로써 공간적 참조 인접성을 파괴한다.운영 체제는 이 문제를 줄이기 위해 해시 테이블의 크기를 최소화할 수 있으며, 트레이드오프가 미스 레이트 증가가 될 수 있다.

일반적으로 물리적 메모리에 연속적으로 모든 프로세스가 공유하는 해시 테이블이 하나 있다.프로세스별 식별자는 서로 다른 프로세스의 페이지를 구분하는 데 사용된다.주어진 프로세스의 페이지 테이블 항목을 제거하는 것은 다소 느리다. OS는 이를 지연시키기 위해 프로세스별 식별자 값을 재사용하는 것을 피할 수 있다.또는 프로세스별 해시 테이블을 사용할 수 있지만, 메모리 조각화 때문에 테이블을 미리 할당해야 하기 때문에 실용적이지 못하다.

반전된 페이지 테이블은 예를 들어 PowerPC, UltraSPARC 및 IA-64 아키텍처에서 사용된다.[4]

다단계 페이지 테이블

반전된 페이지 테이블은 물리적 메모리의 모든 프레임에 대해 설치된 매핑 목록을 유지한다.하지만, 이것은 꽤 낭비일 수 있다.대신 가상 페이지에 대한 매핑을 포함하는 페이지 테이블 구조를 만들 수 있다.가상 메모리의 특정 블록을 커버하는 페이지 테이블을 여러 개 보관함으로써 이루어진다.예를 들어, 4MB의 가상 메모리를 포함하는 1024 입력 4KB 페이지를 더 작게 만들 수 있다.

이는 가상 메모리의 최상위 부분과 최하위 부분이 프로세스 실행에 사용되는 경우가 많기 때문에 유용하다. 상단은 텍스트와 데이터 세그먼트에, 하단은 스택에 사용되며 중간에는 여유 메모리가 있다.다층 페이지 테이블은 메모리의 위쪽과 아래쪽 부분만을 커버하기 위해 몇 개의 작은 페이지 테이블을 보관할 수 있으며 엄격히 필요한 경우에만 새로운 페이지를 작성할 수 있다.

이제 이 작은 페이지 테이블은 각각 마스터 페이지 테이블로 연결되어 트리 데이터 구조를 효과적으로 만든다.두 단계만이 아니라 여러 단계가 필요할 수 있다.예를 들어, 이 스키마의 가상 주소는 루트 페이지 테이블의 인덱스, 하위 페이지 테이블의 인덱스, 그리고 해당 페이지의 오프셋의 세 부분으로 분할될 수 있다.

다단계 페이지 테이블은 "계층적인 페이지 테이블"이라고도 한다.

가상화된 페이지 테이블

가상 주소 공간의 모든 가상 페이지에 대한 매핑을 포함하는 페이지 테이블 구조를 만드는 것은 결국 낭비가 될 수 있다고 언급되었다.그러나 페이지 테이블을 가상 메모리에 넣고 가상 메모리 시스템이 페이지 테이블의 메모리를 관리하도록 함으로써 과도한 공간 문제를 해결할 수 있다.

그러나, 이 선형 페이지 테이블 구조의 일부는 순환 페이지 오류를 방지하고 페이지 테이블에는 없는 페이지 테이블의 핵심 부분을 찾기 위해 항상 물리적 메모리에 상주해야 한다.

중첩된 페이지 테이블

중첩된 페이지 테이블을 구현하여 하드웨어 가상화의 성능을 높일 수 있다.페이지 테이블 가상화를 위한 하드웨어 지원을 제공함으로써 에뮬레이트할 필요성이 크게 감소한다.x86 가상화의 경우 현재 Intel의 확장 페이지 테이블 기능과 AMD의 신속한 가상화 인덱싱 기능을 선택할 수 있다.

참고 항목

참조

- ^ "Virtual Memory". umd.edu. Retrieved 28 September 2015.

- ^ "Page Table Management". kernel.org. Retrieved 28 September 2015.

- ^ "W^X - 기계"

- ^ 운영 체제 내부 및 설계 원리, 윌리엄 스털링스 페이지 353.

추가 읽기

- 앤드루 S. Tanenbaum, 최신 운영 체제, ISBN 0-13-031358-0

- A. 실버스챗츠, P. B. 갈빈, G. 개그네, 운영체제 개념, ISBN 0-471-69466-5

- 운영 체제: 렘지 H. 아르파시 두소, 안드레아 C의 이지피스 3점.아르파키두소아르파키-두소 북스, 2014.관련 장:페이징 TLB 고급 페이지 테이블에 대한 주소 공간 주소 변환 소개

- CNE 가상 메모리 튜토리얼, 신규 엔지니어 조지 메이슨 대학 센터, 페이지 표

- "Art of Assembler, 6.6 Virtual Memory, Protection, and Paging". Archived from the original on February 18, 2012.

- "Intel 64 and IA-32 Architectures Software Developer's Manuals". Intel. January 18, 2018.

- "AMD64 Architecture Software Developer's Manual". AMD. Archived from the original on 2010-03-13.