신호 무결성

Signal integrity

신호 무결성(SI)은 전기 신호의 품질에 대한 일련의 척도입니다.디지털 전자제품에서 이진수 값의 스트림은 전압(또는 전류) 파형으로 표시됩니다.단, 디지털 신호는 기본적으로 아날로그이며 모든 신호는 노이즈, 왜곡, 손실 등의 영향을 받습니다.단거리와 낮은 비트환율에서는 단순한 도체가 충분한 충실도로 이를 전송할 수 있습니다.높은 비트 전송률 및 장거리 또는 다양한 매체를 통해 다양한 효과가 전기 신호를 저하시켜 오류가 발생하고 시스템 또는 장치가 고장날 수 있습니다.신호 무결성 엔지니어링은 이러한 영향을 분석하고 경감하는 작업입니다.집적회로(IC)[1]의 내부접속부터 패키지, 프린트회로기판(PCB), 백플레인,[2] 시스템간접속까지 모든 수준의 전자제품 패키징 및 조립에서 중요한 활동입니다.이러한 다양한 수준에는 몇 가지 공통적인 주제가 있지만, 특히 온칩 접속과 칩 투 칩 접속의 신호 무결성에 대한 접근법에 상당한 차이를 일으키는 실질적인 고려 사항도 있습니다.

신호 무결성에 관한 주요 우려 사항으로는 호출음, 크로스 토크, 접지 바운스, 왜곡, 신호 손실 및 전원 노이즈 등이 있습니다.

역사

신호 무결성에는 주로 전자 제품 내에서 신호를 이동하기 위해 사용되는 와이어 및 기타 패키징 구조의 전기적 성능이 포함됩니다.이러한 성능은 기초 물리학의 문제이며, 따라서 전자 신호가 시작된 이후 상대적으로 변경되지 않았다.최초의 대서양 횡단 전신 케이블은 심각한 신호 무결성 문제로 어려움을 겪었으며, 문제의 분석 결과 텔레그래퍼 방정식과 같은 신호 무결성 문제를 분석하기 위해 오늘날에도 여전히 사용되는 많은 수학적 도구가 산출되었습니다.와이어 스프링 릴레이를 기반으로 한 Western Electric 크로스바 전화 교환기(cir 1940)와 같은 오래된 제품은 오늘날 볼 수 있는 거의 모든 효과, 즉 현대의 디지털 제품을 괴롭히는 벨소리, 크로스 토크, 접지 바운스 및 전원 공급 소음에 시달렸습니다.

프린트 회로 기판에서는 신호의 천이(상승 및 하강) 시간이 기판 전반의 전파 시간과 비슷해지기 시작하면서 신호 무결성이 심각한 문제가 되었습니다.대략적으로 말하면, 이것은 일반적으로 시스템 속도가 수십 MHz를 초과할 때 발생합니다.처음에는 가장 중요하거나 가장 빠른 소수의 신호만 상세한 분석이나 설계가 필요했습니다.속도가 증가함에 따라 신호의 더 큰 부분이 SI 분석과 설계 관행을 필요로 했습니다.최신(> 100MHz) 회로 설계에서는 기본적으로 모든 신호는 SI를 염두에 두고 설계되어야 합니다.

IC의 경우, SI 분석이 설계 규칙 감소의 영향으로 필요하게 되었다.현대 VLSI 시대 초기에 디지털 칩 회로 설계와 레이아웃은 수동 프로세스였습니다.추상화와 자동 합성 기술의 적용으로 설계자는 높은 수준의 언어를 사용하여 설계를 표현하고 기본 회로의 전기적 특성을 크게 무시한 채 매우 복잡한 설계를 만들기 위해 자동화된 설계 프로세스를 적용할 수 있게 되었다.그러나 확장 추세(Moore의 법칙 참조)는 최근의 기술 노드에서 전기 효과를 다시 부각시켰습니다.0.25µm 미만의 기술 스케일링으로 와이어 지연은 게이트 지연과 동등하거나 더 커졌습니다.그 결과 타이밍 클로징을 달성하기 위해 와이어 지연을 고려할 필요가 있었습니다.0.13µm 이하의 나노미터 기술에서는 신호 간의 의도하지 않은 상호작용(예: 크로스톡)이 디지털 설계에서 중요한 고려 사항이 되었습니다.이러한 기술 노드에서는 소음 영향을 고려하지 않고 설계의 성능과 정확성을 보장할 수 없다.

이 기사의 대부분은 현대 전자 기술과 관련된 SI에 관한 것입니다. 특히 집적회로와 프린트 기판 기술을 사용하는 것이 중요합니다.그럼에도 불구하고 SI의 원리는 사용되는 신호 전달 기술에 독점적인 것은 아니다.SI는 두 기술이 등장하기 훨씬 전에 존재했으며, 전자 통신이 지속되는 한 그렇게 할 것입니다.

온칩 신호 무결성

현대 집적회로(IC)의 신호 무결성 문제는 디지털 설계에 다음과 같은 중대한 결과를 초래할 수 있습니다.

- 제품이 전혀 작동하지 않거나 현장에서 신뢰성이 떨어질 수 있습니다.

- 설계는 동작할 수 있지만, 계획보다 느린 속도에서만 동작합니다.

- 수율이 대폭 저하될 수 있습니다.

이러한 실패의 비용은 매우 높으며, 제품 도입 지연으로 인한 포토마스크 비용, 엔지니어링 비용 및 기회 비용이 포함된다.따라서 전자설계자동화(EDA) 도구는 이러한 [1]문제를 분석, 방지 및 수정하기 위해 개발되었습니다.집적회로(IC)에서 신호 무결성 문제의 주요 원인은 크로스톡입니다.CMOS 테크놀로지에서는 이는 주로 커플링 캐패시턴스에 의한 것이지만 일반적으로 상호 인덕턴스, 기판 커플링, 이상적이지 않은 게이트 동작 및 기타 소스에 의한 것일 수 있습니다.이 수정에는, 통상, 드라이버의 사이즈나 와이어의 간격의 변경이 포함됩니다.

아날로그 회로에서는 설계자는 열 노이즈, 플리커 노이즈 및 샷 노이즈와 같은 물리적 소스에서 발생하는 노이즈도 고려합니다.이러한 노이즈 소스는 한편으로 증폭할 수 있는 최소 신호에 대한 하한치를 나타내며, 다른 한편으로 유용한 증폭에 대한 상한을 정의합니다.

디지털 IC에서 관심 신호의 노이즈는 주로 다른 신호의 전환으로 인한 결합 효과에서 발생합니다.상호접속 밀도가 높아짐에 따라 각 와이어가 물리적으로 서로 가까운 네이버를 갖게 되어 네이버네트간의 크로스톡이 증가하고 있습니다.무어의 법칙에 따라 회로가 계속 축소됨에 따라 다음과 같은 여러 가지 효과가 결합되어 소음 문제를 악화시켰습니다.

- 폭 감소에도 불구하고 저항을 견딜 수 있도록 하기 위해 최신 와이어 형상은 간격에 비례하여 더 두껍습니다.이로 인해 측벽 캐패시턴스가 접지되는 대신 증가하므로 유도 노이즈 전압(공급 전압의 비율로 표시됨)이 증가합니다.

- 테크놀로지 스케일링에 의해 MOS 트랜지스터의 임계값 전압이 낮아지고 임계값 전압과 공급 전압의 차이가 감소하여 노이즈 마진이 감소합니다.

- 로직 속도, 특히 클럭 속도가 크게 증가하여 이행(상승 및 하강) 시간이 빨라졌습니다.이러한 빠른 전환 시간은 더 높은 용량성 크로스톡과 밀접하게 관련되어 있습니다.또한 이러한 고속에서는 와이어의 유도 특성, 특히 상호 인덕턴스가 작용합니다.

이러한 효과는 신호 간의 상호작용을 증가시키고 디지털 CMOS 회로의 노이즈 내성을 감소시켰습니다.이로 인해 노이즈는 모든 디지털 칩 설계자가 테이프 아웃 전에 고려해야 하는 디지털 IC에 중대한 문제가 되고 있습니다.다음과 같은 몇 가지 우려 사항을 완화해야 합니다.

- 노이즈가 발생하면 신호가 잘못된 값을 가정할 수 있습니다.이는 특히 신호가 래치(또는 샘플링)되려고 할 때 중요합니다. 잘못된 값이 저장 요소에 로드되어 로직 오류가 발생할 수 있기 때문입니다.

- 노이즈가 발생하면 신호가 올바른 값으로 안착하는 것이 지연될 수 있습니다.이것은, 통상, 지연시의 노이즈라고 불립니다.

- 노이즈(예: 링잉)로 인해 게이트의 입력 전압이 접지 레벨 아래로 떨어지거나 공급 전압을 초과할 수 있습니다.이로 인해 컴포넌트에 부하를 가하거나 래치업을 유도하거나 특정 기간에 한 번만 사이클해야 하는 신호를 여러 번 사이클하여 장치의 수명을 단축할 수 있습니다.

IC 신호 무결성 문제 찾기

일반적으로 IC 설계자는 SI 검증을 위해 다음 단계를 수행합니다.

- 레이아웃 추출을 수행하여 레이아웃과 연결된 기생충을 가져옵니다.보통 최악의 경우 기생충과 최고의 경우 기생충을 추출하여 시뮬레이션에 사용합니다.IC의 경우 PCB와 달리 외부 장비로는 현장 측정이 매우 어렵기 때문에 기생충의 물리적 측정은 거의 이루어지지 않습니다.또한 칩이 생성된 후 측정이 이루어지기 때문에 관찰된 문제를 수정하기에는 너무 늦습니다.

- 커플링 및 전하 공유와 같은 다양한 유형의 노이즈를 포함하여 예상되는 노이즈 이벤트 목록을 만듭니다.

- 각 소음 사건에 대한 모델을 만듭니다.모델은 주어진 소음 사건을 모델링하는 데 필요한 만큼 정확해야 한다.

- 각 신호 이벤트에 대해 노이즈 이벤트가 발생하도록 회로를 활성화하는 방법을 결정합니다.

- 필요한 여진을 나타내는 SPICE(또는 다른 회선 시뮬레이터) 넷리스트를 작성하고, 필요에 따라서 많은 효과(기생 인덕턴스나 캐패시턴스, 다양한 왜곡 효과 등)를 포함합니다.

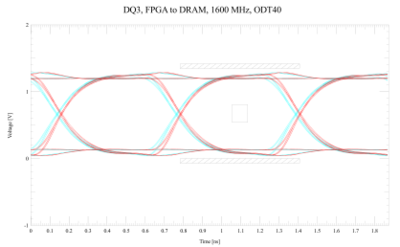

- SPICE 시뮬레이션을 실행합니다.시뮬레이션 결과를 분석하여 재설계가 필요한지 여부를 판단합니다.눈 패턴과 타이밍 버젯을 [3]계산하여 결과를 분석하는 것이 일반적입니다.

최신 IC 설계용 신호 무결성 도구는 이러한 모든 단계를 자동으로 수행하여 설계에 완전한 건강 증명서 또는 수정해야 할 문제의 목록을 제공하는 보고서를 생성합니다.그러나, 그러한 도구는 일반적으로 IC 전체에 적용되는 것이 아니라, 선택된 관심 신호에만 적용됩니다.

IC 신호 무결성 문제 해결

문제가 발견되면 수정해야 합니다.IC 온칩 문제의 일반적인 해결 방법에는 다음과 같은 것이 있습니다.

- 임피던스 불연속성을 제거하는 중입니다.임피던스의 현저한 변화가 존재하는 장소를 찾아, 패스의 지오메트리를 조정해, 임피던스를 다른 패스와 보다 잘 일치시킵니다.

- 드라이버 최적화드라이브가 너무 많아도 충분치 않을 수 있습니다.

- 버퍼 삽입이 어프로치에서는, 피해자 드라이버를 업 하는 대신에, 피해자 넷의 적절한 지점에 버퍼를 삽입한다.

- 어그레시브 다운사이징.이는 드라이버의 강도를 줄여 공격 네트의 전환 시간을 증가시키는 방식으로 작용한다.

- 차폐를 추가합니다.크로스톡의 영향을 줄이기 위해 GND 및 VDD 실드를 사용하여 크리티컬넷 또는 클럭넷의 차폐를 추가합니다(이 기술은 라우팅 오버헤드로 이어질 수 있습니다).

- 라우팅 변경경로 변경은 주로 분리를 통해 가장 문제가 많은 결합 효과를 감소시킴으로써 노이즈 문제를 해결하는 데 매우 효과적입니다.

이러한 수정으로 인해 다른 문제가 발생할 수 있습니다.이러한 유형의 문제는 설계 흐름 및 설계 폐쇄의 일부로 다루어져야 합니다.설계 변경 후의 재분석은 신중한 조치입니다.

온다이 터미네이션

On-Die Termination(ODT; 다이 종단) 또는 Digital Controlled Impinance(DCI[4]; 디지털 제어 임피던스)는 회로 기판에 탑재된 개별 디바이스 대신 전송선에서의 임피던스 매칭을 위한 종단 저항을 반도체 칩 내에 배치하는 기술입니다.리시버로부터의 터미네이션의 근접에 의해, 2개의 사이의 스탭이 단축되어 전체적인 신호 정합성이 향상됩니다.

칩 투 칩 신호 무결성

유선 접속의 경우 인터커넥트 비행시간을 비트 주기와 비교하여 임피던스가 일치하는지 일치하지 않는지를 판단하는 것이 중요합니다.

인터커넥트의 채널 비행 시간(지연)은 FR-4 스트라이플라인의 15cm(6인치)당 약 1ns입니다(전파 속도는 유전체와 [5]형상에 따라 다릅니다).임피던스 미스매치에서의 이전 펄스의 반사는 (즉, 비행 시간 순서대로) 몇 번 라인을 오르내린 후 사라집니다.낮은 비트환율에서는 에코가 저절로 소멸하고 중간 펄스에서는 문제가 되지 않습니다.임피던스 매칭은 필요하지도 않고 바람직하지도 않습니다.FR-4 이외에도 많은 회로 기판이 있지만, 일반적으로 제조 비용이 더 많이 듭니다.

2004년에는 인텔이 PCI-Express 표준을 도입하면서 비트 전송률이 높아지는 경향이 비약적으로 가속화되었습니다.이에 따라 대부분의 칩 투 칩 접속 표준은 병렬 버스로부터 "랜"이라고 불리는 시리얼라이저/디시리얼라이저(SERDES) 링크로 아키텍처 전환을 거쳤습니다.이러한 시리얼 링크는 병렬 버스 클럭스큐를 배제하고 트레이스 수와 그에 따른 커플링 효과를 감소시키지만 이러한 장점은 레인에서의 비트환율이 크게 상승하고 비트주기가 짧아지는 단점이 있습니다.

멀티기가비트/초 데이터 레이트에서 링크 설계자는 임피던스 변화 시 반사(예를 들어 트레이스가 vias에서 레벨을 변경하는 경우, 전송선 참조), 밀집된 인접 접속에 의해 발생하는 노이즈(크로스톡), 금속 트레이스 및 유전 손실 접선의 피부 효과에 의해 발생하는 고주파 감쇠 등을 고려해야 합니다.이러한 장애의 경감 기술의 예로는 [6][7]각각 임피던스 일치, 차분 시그널링의 사용 및 프리엠퍼시스 필터링을 보증하기 위한 via 지오메트리의 재설계 등이 있습니다.

이러한 새로운 멀티기가비트/초 비트환율에서는 비트주기가 비행시간보다 짧습니다.이전 펄스의 에코가 수신기에 도달하여 메인펄스 위에 있는 수신기가 파손될 수 있습니다.통신 공학에서는 이것을 심볼간 간섭(ISI)이라고 부릅니다.신호 무결성 공학에서는 일반적으로 아이 클로저(아이 다이어그램이라고 하는 오실로스코프 트레이스 유형의 중심에 있는 클러터를 참조)라고 합니다.비트 주기가 비행 시간보다 짧을 경우, 송신기의 전기적 임피던스를 상호 연결, 상호 연결 구간 및 수신기에 대한 상호 연결과 같은 고전적인 마이크로파 기술을 사용하여 반사를 제거하는 것이 중요합니다.소스 또는 로드와의 종료는 양 끝에서 일치하는 것과 동의어입니다.선택할 수 있는 상호접속 임피던스는 기하학적 폼 팩터인 자유 공간의 임피던스(~377Ω)와 스트립 라인 필러의 상대 유전율의 제곱근(일반적으로 FR-4, 상대 유전율은 ~4)에 의해 제한됩니다.이러한 특성은 함께 배선의 특성 임피던스를 결정합니다.싱글 엔드 [8]라인에서는 50Ω, 차동에서는 100Ω을 선택하는 것이 편리합니다.

매칭에 필요한 낮은 임피던스 때문에 PCB 신호 트레이스는 온칩 신호 트레이스보다 훨씬 많은 전류를 전달합니다.이 큰 전류는 주로 정전 모드가 아닌 자기 또는 유도 모드에서 크로스톡을 유도합니다.이 크로스톡을 방지하기 위해 디지털 PCB 설계자는 모든 신호의 의도된 신호 경로뿐만 아니라 모든 신호에 대해 신호 전류를 반환하는 경로도 잘 알고 있어야 합니다.신호 자체와 그 리턴 신호 전류 경로는 유도 크로스토크를 생성할 수 있습니다.차동 트레이스 쌍은 이러한 영향을 줄이는 데 도움이 됩니다.

온칩 접속과 칩 투 칩 접속의 세 번째 차이점은 신호 도체의 단면적 크기, 즉 PCB 도체가 훨씬 더 큰 크기(일반적으로 폭이 100µm 이상)입니다.따라서 PCB 트레이스는 DC에서 작은 직렬 저항(일반적으로 0.1Ω/cm)을 가집니다.그러나 펄스의 고주파 성분은 피부 효과 및 PCB 재료와 관련된 유전 손실 접선으로 인한 추가적인 저항에 의해 감쇠됩니다.

주요 과제는 종종 프로젝트가 비용 중심 소비자 애플리케이션인지 아니면 성능 중심 인프라 [9]애플리케이션인지에 따라 달라집니다.이들은 각각 광범위한 배치 후 검증(EM 시뮬레이터 사용)과 배치 전 설계 최적화(SPICE 및 채널 시뮬레이터 사용)가 필요한 경향이 있습니다.

라우팅 토폴로지

트레이스/네트워크상의 노이즈 레벨은, 선택한 라우팅 토폴로지에 의해서 크게 좌우됩니다.포인트 투 포인트토폴로지에서는 신호가 송신기에서 수신기로 직접 라우팅됩니다(이는 PCIe, Rapid로 적용됩니다).IO, GbE, DDR2/DDR3/DDR4 DQ/DQS 등).포인트 투 포인트토폴로지는 라인 T(트레이스의 쌍방향 분할)에 의해 도입되는 큰 임피던스 일치가 없기 때문에 SI 문제가 가장 적습니다.

복수의 패키지가 같은 회선으로부터 수신되고 있는 인터페이스(백플레인 설정등)의 경우, 모든 리시버에 서비스를 제공하기 위해서, 어느 시점에서 회선을 분할할 필요가 있습니다.일부 스터브와 임피던스 미스매치는 발생하는 것으로 간주됩니다.멀티패키지 인터페이스에는 BLVDS, DDR2/DDR3/DDR4 C/A 뱅크, RS485 및 CAN 버스가 포함됩니다.멀티패키지 토폴로지는 주로 다음 두 가지가 있습니다.나무와 플라이바이.

신호 무결성 문제 발견

- 레이아웃 추출을 수행하여 레이아웃과 연결된 기생충을 가져옵니다.보통 최악의 경우 기생충과 최고의 경우 기생충을 추출하여 시뮬레이션에 사용합니다.많은 장애의 분포 특성 때문에 전자기 시뮬레이션이[10] 추출에 사용됩니다.

- PCB 또는 패키지가 이미 존재하는 경우 설계자는 벡터 네트워크아나라이저 등의 고속 계측을 사용하여 접속에 의해 발생하는 장애를 측정할 수도 있습니다.예를 들어 IEEE P802.3ap 태스크포스에서는 측정된S 파라미터를 백플레인 상의 10기가비트/초 이더넷 문제에 대한 제안 솔루션의 테스트 케이스로[11] 사용합니다.

- 정확한 소음 모델링이 필수적입니다.커플링 및 전하 공유와 같은 다양한 유형의 노이즈를 포함하여 예상되는 노이즈 이벤트 목록을 만듭니다.Input Output Buffer Information Specification(IBIS; 입력 출력 버퍼 정보 사양) 또는 회로 모델을 사용하여 드라이버 및 수신기를 나타낼 수 있습니다.

- 노이즈 이벤트가 발생할 수 있도록 각 노이즈 이벤트에 대해 회로를 활성화하는 방법을 결정합니다.

- 목적의 들뜸을 나타내는 SPICE(또는 다른 회선 시뮬레이터) 넷 리스트를 작성합니다.

- SPICE를 실행하여 결과를 기록합니다.

- 시뮬레이션 결과를 분석하여 재설계가 필요한지 여부를 판단합니다.결과를 분석하기 위해 데이터 아이(Data Eye)를 생성하고 타이밍 예산을 계산합니다.YouTube에서 데이터 아이 생성용 비디오 예를 볼 수 있습니다.'눈'은 탄생했다.

엔지니어가 설계 내의 각 신호에 대해 이러한 모든 단계를 수행하여 문제를 지적하거나 설계가 제조 가능한 상태임을 확인하는 데 도움이 되는 특수 목적의 EDA[12] 도구가 있습니다.특정 작업에 가장 적합한 도구를 선택할 때 용량(노드 또는 요소의 수), 성능(시뮬레이션 속도), 정확도(모델이 얼마나 좋은지), 수렴(솔버) 기능(비선형 대 선형, 주파수 의존 대 주파수 독립 등) 및 e와 같은 각각의 특성을 고려해야 한다.무용지물

신호 무결성 문제 해결

IC 패키지 또는 PCB 설계자는 다음 기술을 사용하여 신호 무결성 문제를 제거합니다.

- 신호 트레이스 옆에 솔리드 기준 평면을 배치하여 크로스톡 제어

- 기준 평면에 대한 트레이스 폭 간격을 제어하여 일관된 트레이스 임피던스 생성

- 종단을 사용한 호출음 제어

- 인접 레이어에 수직으로 배선하여 크로스톡을 줄입니다.

- 크로스톡을 줄이기 위해 트레이스 간 간격을 늘리기

- 접지 바운스를 제한하기 위한 충분한 접지(및 전원) 접속을 제공한다(신호 무결성 서브섹션은 전원 무결성이라고 따로 부르기도 한다).

- 솔리드 플레인 층을 사용한 배전으로 전원 장치의 노이즈를 억제

- 송신기 구동[13] 셀에 사전 강조 필터 추가

- 수신[13] 셀에 이퀄라이저 추가

- 클럭 앤 데이터 리커버리(CDR) 회로가 개선되어 지터/위상[14] 노이즈가 적습니다.

이러한 수정으로 인해 다른 문제가 발생할 수 있습니다.이러한 유형의 문제는 설계 흐름 및 설계 폐쇄의 일부로 다루어져야 합니다.

「 」를 참조해 주세요.

메모들

- ^ a b : 일반 이름(도움말)이 있습니다Louis Kossuth Scheffer; Luciano Lavagno; Grant Martin (eds) (2006). Electronic design automation for integrated circuits handbook. Boca Raton, Florida: CRC/Taylor & Francis. ISBN 0-8493-3096-3.

{{cite book}}.CS1 maint: multiple name: authors 목록(링크) 전자설계 자동화 분야에 대한 조사.이 기사의 IC 섹션의 일부는 Vinod Kariat가 Vol II, 21장 "디지털 IC에서의 소음 고려사항"에서 (허가를 받아) 인용한 것입니다. - ^ Howard W. Johnson; Martin Graham (1993). High speed digital design a handbook of black magic. Englewood Cliffs, New Jersey: Prentice Hall PTR. ISBN 0-13-395724-1. 디지털 PCB 설계자를 위한 책으로, 고속 디지털 설계와 관련된 아날로그 회로 원리를 강조하고 설명합니다.

- ^ Ruckerbauer, Hermann. "An Eye is Born". 눈 패턴의 구성 예 비디오를 제공합니다.

- ^ Banas, David. "Using Digitally Controlled Impedance: Signal Integrity vs. Power Dissipation Considerations, XAPP863 (v1.0)" (PDF).

- ^ "Rule of Thumb #3 Signal speed on an interconnect". EDN. Retrieved 2018-03-17.

- ^ "Signal Integrity: 문제와 해결책" Eric Bogatin, Bogatin Enterprise

- ^ "고속 버스 디버깅 및 검증을 위한 8가지 힌트", 애플리케이션 노트 1382-10, Agilent Technologies

- ^ "Why 50 Ohms?". Microwaves101. Retrieved 2008-06-02.

- ^ Rako, Paul (April 23, 2009). "Voices: Signal-integrity experts speak out: Two experts discuss signal-integrity challenges and their expectations for signal integrity". EDN.

For cost-driven consumer applications ... [i]t's tempting to compact [the parallel buses], but the risk is postlayout failure ... For performance-driven applications, the pinch points [is] prelayout design-space exploration ...

- ^ "메가비트/초의 장벽을 허무는 것"

- ^ IEEE P802.3ap 태스크포스 채널모델

- ^ Breed, Gary (August 2008). "High Speed Digital Design Benefits from Recent EDA Tools Development" (PDF). High Frequency Electronics. p. 52. Retrieved May 1, 2009.

...with continued increase in clock rates of digital circuits, the realms of RF and digital circuits are now more closely tied than ever before.

- ^ a b "Using Pre-Emphasis and Equalization with Stratix GX" (PDF). Altera.

- ^ "직렬 데이터 응용 프로그램에서 클럭 지터 분석을 사용하여 BER 감소", 애플리케이션 노트, 문헌 번호 5989-5718EN, Agilent Technologies

레퍼런스

- Howard Johnson; Martin Graham. (2002). High-speed signal propagation : advanced black magic. Upper Saddle River, New Jersey: Prentice Hall PTR. ISBN 0-13-084408-X. 속도와 거리의 상한까지 디자인을 강요하고 싶은 경험이 풍부한 디지털 디자이너를 위한 고급 레퍼런스 텍스트.

- Eric Bogatin. (2009). Signal and Power Integrity - Simplified, Second Edition. Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-234979-6. Archived from the original on 2011-09-10. 뒷표지: 저자의 산업 경험과 5,000명 이상의 엔지니어를 가르치는 그의 작품에서 따온 것입니다.

- Stephen H. Hall; Garrett W. Hall; James A. McCall. (2000). High speed digital system design : a handbook of interconnect theory and design practices. New York: Wiley. ISBN 0-471-36090-2.

- William J. Dally; John W. Poulton. (1999). Digital systems engineering. Cambridge: Cambridge Univ. Press. ISBN 0-521-59292-5. 신호 무결성을 포함한 디지털 시스템 구축의 문제에 대한 교과서.

- Douglas Brooks. (2003). Signal integrity issues and printed circuit board design. Upper Saddle River, New Jersey: Prentice Hall PTR. ISBN 0-13-141884-X. 이 책에서는 전기공학 및 신호 무결성 원리에 대해 사전 지식이 거의 없다고 가정하고 기본 수준에서 접근합니다.

- Geoff Lawday; David Ireland & Greg Edlund. (2008). A signal integrity engineer's companion : real-time test and measurement and design simulation. Upper Saddle River, New Jersey: Prentice Hall. ISBN 0-13-186006-2.

- 라지, 에이 Ege Engin.(2008년).반도체와 시스템에 전원 무결성 모델과 설계이다.어퍼 새들 강, 뉴저지:PrenticeHall이다.아이 에스비엔 978-0-13-615206-4.현실적인 사례 및 다운로드 할 수 있는 소프트웨어 예를 사용하여 선두의 두 전문가들과 모형화하고 효율적으로 소음을 최소화 배전에 디자인으로 현재의 최적 기법을 보여 준다.저자들은 배전 설계의 핵심 개념을 주의 깊게 소개하고, 소음 모델링에 대한 선도적 기법을 체계적으로 제시 및 비교하며, 이러한 기법을 특정 애플리케이션에 연결한다.이러한 예는 가장 단순한 (분석 방정식을 사용하여 전원 노이즈를 계산하는) 것에서부터 복잡한 시스템 수준 애플리케이션에 이르기까지 다양합니다.

- PCB 설계자의 신호 무결성

- 알테라 신호 무결성 센터

- 신호 무결성의 기본 원리

- 애질런트 EESof EDA - 신호 무결성 분석 리소스

- "설계 팁: 신호 무결성 시뮬레이션을 개선하기 위한 기기 모델", EETimes, John Olah, 2007년 10월 25일

- 신호의 무결성에 관한 토픽은 2008년 2월 4일부터 2008년 2월 7일까지 DesignCon 2008에서 논의되었습니다.

- Eric Bogatin, GigaTest Labs, Agilent Application Note 5988-5978EN, 2002년 4월, 8페이지, PDF, 0.9의 "신호 무결성 이해 - 클럭 주파수가 증가함에 따라 신호 무결성 문제가 더욱 심각해지고 있습니다"MB

- "Signal Integrity Analysis Series Part 1: 싱글 포트 TDR, TDR/TDT, 및 2 포트 TDR"(애질런트응용 프로그램노트 5989-5763EN, 2007년 2월, 72 페이지, PDF, 5.2)MB)

- "Signal Integrity Analysis Series Part 2: 4-Port TDR/VNA/PLTS"(애질런트 애플리케이션 노트 5989-5764EN, 2007년 2월, 56 페이지, PDF, 3.6)MB)

- "Signal Integrity Analysis Series Part 3: 디임베딩의 ABC" (애질런트 애플리케이션 노트 5989-5765EN, 2007년 7월, 48페이지, PDF, 2.5)MB)