전원 MOSFET

Power MOSFET | |

| 작동 원리 | 반도체 |

|---|---|

전력 MOSFET는 상당한 전력 레벨을 처리하기 위해 설계된 특정 유형의 금속 산화물 반도체 전계효과 트랜지스터(MOSFET)입니다.절연 게이트 바이폴라 트랜지스터(IGBT)나 사이리스터 등 다른 전력 반도체 소자에 비해 스위칭 속도가 빠르고 전압이 낮을 때 효율이 좋다는 것이 주요 장점입니다.IGBT와 격리된 게이트를 공유하여 운전이 용이합니다.게이트 전압이 제어 전압보다 높아야 할 정도로 낮은 게인이 발생할 수 있습니다.

전력 MOSFET의 설계는 1960년대 이후 집적회로 제조에 사용된 MOSFET와 CMOS 기술의 진화에 의해 가능해졌다.동력 MOSFET는 저전력 대응 장치인 횡방향 MOSFET와 작동 원리를 공유합니다.전력 전자제품에 일반적으로 사용되는 전력 MOSFET는 표준 MOSFET에서 개조되어 1970년대에 [2]상업적으로 도입되었습니다.

전력 MOSFET는 낮은 게이트 드라이브 전력, 빠른 스위칭 속도,[3] 쉬운 고급 병렬 처리 기능,[3][4] 넓은 대역폭, 견고성, 쉬운 드라이브, 단순한 바이어스, 적용 용이성 및 손쉬운 [4]수리로 인해 세계에서 가장 일반적인 전력 반도체 장치입니다.특히 가장 널리 사용되는 저전압(200V 미만) 스위치입니다.대부분의 전원 장치, DC-DC 변환기, 저전압 모터 컨트롤러 및 기타 많은 응용 프로그램 등 다양한 응용 프로그램에서 찾을 수 있습니다.

역사

MOSFET는 1959년 벨 연구소에서 모하메드 아탈라와 다원 칸에 의해 발명되었다.그것은 전력 전자제품의 비약적인 발전이었다.여러 세대의 MOSFET를 통해 전력 설계자는 바이폴라 [5]트랜지스터에서는 불가능한 성능과 밀도 수준을 달성할 수 있었습니다.

1969년, 히타치는 최초의 수직 전력 MOSFET를 [6]도입했습니다.이 MOSFET는 나중에 VMOS(V-groove MOSFET)[7]로 알려지게 되었습니다.같은 해, 자기 정렬 게이트가 있는 DMOS(이중 확산 MOSFET)가 Y에 의해서 최초로 보고되었습니다.타루이, Y전기기술연구소(ETL)[8][9]의 하야시씨와 세키가와 토시히로씨.1974년, 도호쿠 대학의 니시자와 준이치는 오디오용 파워 MOSFET를 발명해, 곧 야마하 주식회사에 의해서 고품질 오디오 앰프용으로 제조되었다.JVC, 파이오니어, 소니, 도시바 등도 [10]1974년부터 파워 모스펫을 탑재한 앰프를 생산하기 시작했다.Siliconix는 1975년에 [7]VMOS를 상업적으로 도입했습니다.

VMOS와 DMOS는 VDMOS(Vertical DMOS)[10]로 발전했습니다.HP Labs의 John Moll의 연구팀은 1977년에 DMOS 프로토타입을 제작하여 VMOS보다 낮은 저항 및 높은 고장 전압 [7]등의 이점을 입증했습니다.같은 해, 히타치는 DMOS의 평면 타입인 LDMOS(Lateral DMOS)를 발표했습니다.히타치는 1977년부터 1983년 사이에 LDMOS 제조사 중 유일하게 LDMOS를 HH Electronics(V 시리즈)등의 제조사의 오디오 파워 앰프에 사용했으며, Ashly Audio는 음악용으로 사용되었습니다.1995년 2G 디지털 모바일 네트워크가 도입되면서 LDMOS는 2G, 3G,[11][12] 4G와 같은 모바일 네트워크에서 가장 널리 사용되는 RF 파워 앰프가 되었습니다.

Alex Lidow는 [13]1977년 Tom [14]Herman과 함께 스탠포드 대학에서 육각형 형태의 Power MOSFET인 HexFET를 공동 발명했습니다.HexFET는 1978년 [7][14]국제 정류기(International Refrectifier)에 의해 상용화되었습니다.전력 MOSFET와 바이폴라 접합 트랜지스터(BJT)의 요소를 결합한 절연 게이트 바이폴라 트랜지스터(IGBT)는 1977~[15]1979년 제너럴 일렉트릭(General Electric)의 Jayant Baliga에 의해 개발되었습니다.

초접합 MOSFET는 N- 에피택셜 층을 관통하는 P+ 컬럼을 사용하는 전력 MOSFET의 한 종류입니다.P층과 N층을 쌓는 아이디어는 1978년 [16]오사카 대학의 시로타 쇼조 씨와 가네다 시게오 씨에 의해 처음 제안되었습니다.필립스의 데이비드 코는 1988년 미국 [17]특허를 출원해 p형과 n형이 번갈아 가며 초접합 MOSFET를 발명했다.

적용들

전력 MOSFET는 세계에서 [3]가장 널리 사용되는 전력 반도체 장치입니다.2010년 현재[update] 전력 MOSFET는 전력 트랜지스터 시장의 53%를 차지하며 절연 게이트 바이폴라 트랜지스터(27%), RF 파워앰프(11%), 바이폴라 정션 트랜지스터(9%)[18]를 앞섭니다.2018년 기준으로[update] 연간 [19]500억 개 이상의 전력 MOSFET가 출하되고 있습니다.2017년 [20]2월까지 1000억대 이상 팔린 트렌치파워 MOSFET와 2019년 [16]기준[update] 50억대 판매를 기록한 ST마이크로일렉트로닉스의 MDmesh(초접속형 MOSFET) 등이 이에 해당한다.

전원 MOSFET는 일반적으로 다양한 [21][22]가전제품에 사용됩니다.

RF DMOS는 RF 전력 MOSFET라고도 불리며, Radio-Frequency(RF; 무선 주파수) 애플리케이션용으로 설계된 DMOS 전력 트랜지스터의 일종입니다.다양한 무선 [23][24]및 RF 어플리케이션에서 사용됩니다.

동력 MOSFET는 다양한 차량을 포함하는 운송 [25][26][27]기술에 널리 사용됩니다.

자동차 산업에서 [28][29][30]동력 MOSFET는 자동차 [31][32][21]전자제품에 널리 사용되고 있습니다.

전원 MOSFET(DMOS, LDMOS 및 VMOS 포함)는 일반적으로 광범위한 다른 애플리케이션에서 사용됩니다.

기본구조

1970년대에 상업용 전력 MOSFET가 처음 도입되었을 때 몇 가지 구조물이 탐색되었다.단, 이들 대부분은 VDMOS(Vertical Diffused MOS) 구조(Double-Diffused MOS 또는 단순히 DMOS라고도 함) 및 LDMOS(가로로 확산되는 MOS) 구조를 위해 포기되었습니다.

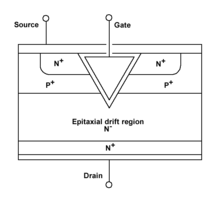

VDMOS의 단면(그림 1 참조)은 장치의 "수직성"을 나타냅니다. 소스 전극이 드레인 위에 배치되어 트랜지스터가 온 상태일 때 전류가 주로 수직인 것을 알 수 있습니다.VDMOS에서 "확산"은 제조 공정을 말합니다. P 웰(그림 1 참조)은 확산 공정을 통해 얻습니다(실제로 P+ 및 N 영역을 얻기 위한 이중 확산 공정이므로 이름이 이중 확산됩니다).

전원 MOSFET는 가로형 MOSFET와 구조가 다릅니다.대부분의 전원 디바이스와 마찬가지로 구조는 수직이며 평면형이 아닙니다.평면구조에서 전류와 파괴전압정격은 모두 채널치수(각각 채널의 폭과 길이)의 함수이므로 "실리콘 부동산"의 비효율적인 사용이 발생한다.수직 구조의 경우 트랜지스터의 전압 정격은 N 에피택셜 층의 도핑 및 두께(단면 참조)의 함수이며, 전류 정격은 채널 폭의 함수입니다.이를 통해 트랜지스터는 소형 실리콘 조각 내에서 높은 차단 전압과 고전류를 모두 유지할 수 있습니다.

LDMOS는 횡구조의 전력 MOSFET입니다.주로 2G, [10]3G,[11] 4G [12]등의 무선 셀룰러 네트워크의 하이엔드 오디오 파워앰프와 RF 파워앰프에 사용됩니다.이들의 장점은 수직 MOSFET보다 포화 영역(바이폴라 접합 트랜지스터의 선형 영역에 해당)에서 더 나은 거동입니다.수직 MOSFET는 스위칭 어플리케이션용으로 설계되어 있기 때문에 On 또는 Off 상태에서만 사용됩니다.

온스테이트 저항

전원 MOSFET가 ON 상태일 경우(동작 모드에 대한 설명은 MOSFET 참조), 드레인 단자와 소스 단자 사이에 저항 거동이 나타납니다.그림 2에서 이 저항('온상태에서 배출원 저항'에 대해 R이라고 함DSon)이 많은 기본 기여의 합이라는 것을 알 수 있다.

- R은S 소스 저항입니다.패키지의 소스 단자부터 MOSFET 채널까지의 모든 저항(와이어 본드, 소스 메탈라이제이션 및 N웰의 저항+)을 나타냅니다.

- Rch. 이것은 채널 저항입니다.채널 폭에 반비례하고 주어진 다이 사이즈에 대해 채널 밀도에 반비례합니다.채널 저항은 저전압 MOSFET의 R의DSon 주요 요인 중 하나이며 채널 밀도를 높이기 위해 셀 크기를 줄이는 집중적인 작업이 수행되었습니다.

- R은a 액세스 저항입니다.게이트 전극 바로 아래의 에피택셜 영역의 저항을 나타내며, 여기서 전류 방향이 수평(채널 내)에서 수직(배수 접점 측)으로 변화한다.

- R은JFET 위에서 언급한 셀 크기 감소의 해로운 영향입니다. P 삽입(그림 1 참조)은 전류 흐름의 폭을 감소시키는 경향이 있는 기생 JFET 트랜지스터의 게이트를 형성합니다.

- R은n 에피택셜층의 저항이다.이 층의 역할은 차단전압을 유지하는 것이므로 R은n 디바이스의 전압정격과 직접 관련된다.고전압 MOSFET는 두껍고 낮은 도프층(예: 높은 저항성)을 필요로 하는 반면, 저전압 트랜지스터는 더 높은 도핑 레벨(예: 낮은 저항성)의 얇은 층만 필요로 합니다.그 결과 R은n 고전압 MOSFET의 저항을 담당하는 주요 요인이다.

- R은D 배수구에 대한 R과S 동일합니다.이는 트랜지스터 기판의 저항(그림 1의 단면은 스케일이 아니며, 하단+ N층이 실제로 가장 두껍다) 및 패키지 연결부의 저항을 나타냅니다.

고장 전압/온 상태 저항 트레이드오프

OFF 상태일 때 전력 MOSFET는 PIN 다이오드(P+ 확산−, N 에피택셜 층+ 및 N 기판으로 구성됨)와 동일합니다.이 매우 비대칭적인 구조가 역바이어스일 때 공간 전하 영역은 주로 N개 층에 걸쳐− 광도프된 쪽에서 확장된다.즉, 이 레이어는 MOSFET의 OFF 상태 드레인 투 소스 전압을 대부분 견뎌야 합니다.

단, MOSFET가 ON 상태일 경우 이− N층은 기능을 하지 않습니다.또한 가볍게 도핑된 영역이기 때문에 고유 저항률이 지워지지 않고 MOSFET의 ON 상태 Drain-to-Source 저항(RDSon)에 추가됩니다(그림2의 R 저항n).

도핑 레벨과 N− 에피택셜층의 두께라는 두 가지 주요 파라미터가 트랜지스터의 파괴전압과 R을DSon 모두 제어합니다.층이 두껍고 도핑 레벨이 낮을수록 파괴전압은 높아집니다.반대로 층이 얇고 도핑 레벨이 높을수록 R은DSon 낮아진다(따라서 MOSFET의 전도 손실은 낮아진다).따라서 MOSFET 설계에서는 전압 정격과 ON 상태 [citation needed]저항 사이에 트레이드오프가 있음을 알 수 있습니다.이것은 그림 3의 그림에 나타나 있습니다.

바디 다이오드

그림 1에서 소스 메탈라이제이션이 N과+ P 삽입을+ 모두 연결하는 것을 알 수 있지만, MOSFET의 작동 원리에서는 소스만 N 존에+ 연결하면 됩니다.단, 이 경우 N 도프된 소스와 드레인 사이에 플로팅P 존이 생겨 베이스가 접속되어 있지 않은 NPN 트랜지스터에 해당합니다.특정 조건(높은 드레인 전류에서 온 상태 드레인 대 소스 전압이 일부 볼트인 경우)에서는 이 기생 NPN 트랜지스터가 트리거되어 MOSFET를 제어할 수 없게 됩니다.소스 메탈라이제이션에 대한 P 삽입의 접속은 기생 트랜지스터의 베이스를 이미터(MOSFET의 소스)에 단락시켜 스플리어스 래치를 방지합니다.그러나 이 솔루션은 MOSFET의 드레인(음극)과 소스(양극) 사이에 다이오드를 생성하여 한 방향으로만 전류를 차단할 수 있습니다.

바디 다이오드는 H 브리지 또는 하프 브리지와 같은 구성에서 유도 부하를 위한 자유분사 다이오드로 사용할 수 있습니다.이러한 다이오드는 일반적으로 순방향 전압 강하가 높지만 큰 전류를 처리할 수 있고 많은 애플리케이션에서 충분하므로 부품 수가 줄어들기 때문에 디바이스 비용과 보드 공간이 감소합니다.효율을 높이기 위해 동기식 정류를 사용하여 차체 다이오드가 전류를 전달하는 시간을 최소화합니다.

스위칭 조작

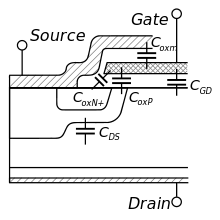

단극성으로 인해 전력 MOSFET는 매우 빠른 속도로 전환할 수 있습니다.실제로 양극성 장치처럼 소수 통신사를 제거할 필요는 없다.변환 속도의 유일한 본질적인 제한은 MOSFET의 내부 용량에 기인합니다(그림 4 참조).이러한 캐패시턴스는 트랜지스터가 전환될 때 충전 또는 방전되어야 합니다.게이트 캐패시턴스를 통과하는 전류는 외부 드라이버 회로에 의해 제한되므로 이 프로세스는 비교적 느린 프로세스일 수 있습니다.이 회로는 실제로 트랜지스터의 전류 속도를 지시합니다(전원 회로의 인덕턴스가 충분히 낮다고 가정).

용량

MOSFET 데이터 시트에서 캐패시턴스는 종종 C(입력 캐패시턴스, 드레인 및 소스 단자 단락), Coss(출력 캐패시턴스, 게이트 및 소스 단락) 및 Crss(역전송 캐패시턴스, 접지에 연결된 소스)로iss 명명됩니다.이러한 용량과 아래에 설명된 용량 사이의 관계는 다음과 같습니다.

여기서GS C, CGD 및DS C는 각각 게이트 대 소스, 게이트 대 드레인 및 드레인 대 소스 캐패시턴스입니다(아래 참조).제조업체는 C, Coss 및rss C를 트랜지스터에서 직접 측정할 수 있기 때문에 견적을iss 내는 것을 선호합니다.다만, C, CGDDS, C는 물리적인 의미에 가깝기GS 때문에, 이 문서의 나머지 부분에서는 이러한 의미를 사용합니다.

게이트에서 소스까지의 캐패시턴스

CGS 캐패시턴스는 C, CoxP 및oxm C의 병렬oxN+ 연결로 구성됩니다(그림 4 참조).N영역과 P영역은 고도로+ 도핑되므로 앞의 2개의 캐패시턴스는 일정하다고 간주할 수 있습니다.C는oxm (폴리실리콘) 게이트와 (금속) 소스 전극 사이의 캐패시턴스이므로 일정합니다.따라서 C를 정전용량으로 간주하는GS 것이 일반적입니다. 즉, C의 값은 트랜지스터 상태에 따라 달라지지 않습니다.

게이트에서 배출 캐패시턴스

CGD 캐패시턴스는 2개의 기본 캐패시턴스의 직렬 연결로 볼 수 있습니다.첫 번째는 게이트 전극, 이산화규소 및 N 에피택셜 층의 상단으로 구성된 산화물 캐패시턴스(CoxD)입니다.값이 일정합니다.두 번째 캐패시턴스(CGDj)는 MOSFET가 오프 상태일 때 공간 차지 영역의 확장에 의해 발생합니다.따라서 드레인-소스 전압에 따라 달라집니다.이를 통해 C의 값은GD 다음과 같습니다.

공간 전하 영역의 폭은 다음과[33] 같습니다.

여기서 _는 실리콘의 유전율, q는 전자 전하, N은 도핑 수준입니다.C 값은GDj 평면 캐패시터의 식을 사용하여 근사할 수 있습니다.

여기서GD A는 게이트 배수 오버랩의 표면적입니다.그 때문에, 다음과 같이 됩니다.

CGDj(따라서GD C)는 게이트-드레인 전압에 따라 값이 달라지는 캐패시턴스임을 알 수 있습니다.이 전압이 증가하면 캐패시턴스가 감소합니다.MOSFET가 온 상태일 때는GDj C가 셰이딩되므로 게이트에서 드레인까지의 캐패시턴스는 일정한 값인 C와 동일하게oxD 유지됩니다.

소스 캐패시턴스에 대한 방전

소스 메탈라이제이션이 P웰에 겹치므로(그림 1 참조), 드레인 단자와 소스 단자는 P-N 접합부에 의해 분리됩니다.따라서 C는DS 접점 캐패시턴스입니다.이것은 비선형 캐패시턴스이며, 그 값은 C와GDj 동일한 방정식을 사용하여 계산할 수 있습니다.

기타 동적 요소

패키징 인덕턴스

작동하려면 MOSFET를 외부 회로에 연결해야 합니다. 대부분의 경우 와이어 본딩을 사용합니다(대안 기법이 조사됩니다).이러한 접속은 기생 인덕턴스를 나타내며, 이는 MOSFET 테크놀로지에 고유하지 않지만 높은 전류 속도로 인해 중요한 영향을 미칩니다.기생 인덕턴스는 트랜지스터가 꺼지는 동안 전류를 일정하게 유지하고 과전압을 발생시켜 결과적으로 전류 손실을 증가시키는 경향이 있습니다.

MOSFET의 각 단자에 기생 인덕턴스를 관련지을 수 있다.효과는 다양합니다.

- 게이트 인덕턴스는 게이트의 전류 구배가 상대적으로 느리기 때문에 거의 영향을 미치지 않습니다(몇 백 나노헨리보다 낮습니다).그러나 경우에 따라서는 게이트 인덕턴스와 트랜지스터의 입력 캐패시턴스가 발진기를 구성할 수 있다.이것은 (디바이스 파괴까지) 매우 높은 전류 손실을 초래하기 때문에 피해야 합니다.일반적인 설계에서는 기생 인덕턴스는 이 현상을 방지할 수 있을 정도로 낮게 유지됩니다.

- 드레인 인덕턴스는 MOSFET가 켜질 때 드레인 전압을 낮추는 경향이 있기 때문에 켜짐 손실을 줄입니다.단, 전원 끄기 중에 과전압이 생성되므로 전원 끄기 손실이 증가합니다.

- 소스 기생 인덕턴스는 드레인 인덕턴스와 동일한 동작을 가지며, 더 긴 회전을 지속시키는 피드백 효과를 가지며, 따라서 변환 손실을 증가시킵니다.

- 소스 인덕턴스로 인해 소스(다이)의 전압은 게이트 전압과 함께 상승할 수 있습니다. 내부GS V 전압이 더 오랫동안 낮은 상태로 유지되므로 켜기가 지연됩니다.

- 빠른 꺼짐 시작 시 소스 인덕턴스를 통한 전류가 급격히 감소하면 인덕턴스 전체의 전압이 음의 전압(패키지 외부의 리드선에 대해)으로 바뀌어 내부 VGS 전압이 상승하고 MOSFET가 켜진 상태로 유지되므로 꺼짐이 지연됩니다.

동작 제한

게이트 산화물 파괴

게이트 산화물은 매우 얇기 때문에(100nm 이하) 제한된 전압만 유지할 수 있습니다.데이터 시트에서 제조업체는 종종 최대 게이트 대 소스 전압을 약 20V로 명시하고 있으며, 이 한계를 초과하면 구성 요소가 파괴될 수 있습니다.또한 게이트 대 소스 전압이 높으면 MOSFET의 수명이 크게 단축되고 R 감소에 대한 이점은DSon 거의 또는 전혀 없습니다.

이 문제를 해결하기 위해 게이트 드라이버 회로가 자주 사용됩니다.

소스 전압에 대한 최대 방전

전원 MOSFET에는 최대 지정 드레인 대 소스 전압(오프 시)이 있으며, 이 값을 초과하면 고장이 발생할 수 있습니다.고장 전압을 초과하면 장치가 전도되어 과도한 전력 소진으로 인해 장치 및 기타 회로 요소가 손상될 수 있습니다.

최대 방전 전류

배출 전류는 일반적으로 지정된 값(최대 연속 배출 전류) 미만으로 유지되어야 합니다.매우 짧은 시간 동안 더 높은 값에 도달할 수 있습니다(최대 펄스 드레인 전류, 때로는 다양한 펄스 지속 시간에 대해 지정됨).드레인 전류는 본드 와이어와 같은 내부 구성요소의 저항성 손실 및 금속 층의 일렉트로마이그레이션과 같은 기타 현상으로 인해 가열에 의해 제한됩니다.

최고 온도

장치가 안정적으로 작동하려면 MOSFET의 접합 온도(TJ)가 지정된 최대값 미만으로 유지되어야 하며, MOSFET 다이 레이아웃 및 포장 재료에 의해 결정됩니다.포장은 종종 성형 화합물 및 (사용되는 경우) 에폭시 특성 때문에 최대 접합 온도를 제한합니다.

동작시의 최대 온도는, 소비 전력의 소산과 열저항에 의해서 결정됩니다.케이스 간 접합부 열저항은 디바이스와 패키지에 내재되어 있습니다.케이스 간 열저항은 주로 보드/장착 레이아웃, 히트싱크 영역 및 공기/유체 흐름에 따라 달라집니다.

연속적이든 펄스적이든 전력 손실의 유형은 열질량 특성에 따라 최대 동작 온도에 영향을 미칩니다.일반적으로 소정의 전력 손실의 펄스 주파수가 낮을수록 장치의 냉각 간격이 길어지기 때문에 최대 동작 온도가 높아집니다.Foster 네트워크와 같은 모델을 사용하여 과도 전력으로부터 온도 역학을 분석할 수 있습니다.

안전한 작동 영역

안전 작동 영역에서는 MOSFET가 손상 없이 처리할 수 있는 방전 전류와 방전 대 소스 전압의 결합 범위를 정의합니다.이 두 파라미터에 의해 정의된 평면의 영역으로 그래픽으로 표현됩니다.드레인 전류와 드레인 투 소스 전압은 각각 최대값 이하로 유지되어야 하지만, 해당 제품은 장치가 처리할 수 있는 최대 전력 소산량 이하로 유지되어야 합니다.따라서 장치를 최대 전류와 최대 전압으로 [34]동시에 작동할 수 없습니다.

래치업

전원 MOSFET의 등가 회로는 기생 BJT와 병렬로 1개의 MOSFET로 구성됩니다.BJT가 켜지면 게이트에서 BJT를 제어할 수 없기 때문에 끌 수 없습니다.이 현상은 "래치업"으로 알려져 있으며, 이는 장치 파괴로 이어질 수 있습니다.BJT는 P형 차체 영역의 전압 강하로 인해 켜질 수 있습니다.래치업을 방지하기 위해 일반적으로 본체와 소스는 디바이스 패키지 내에서 단락됩니다.

테크놀로지

레이아웃

세포구조

위와 같이 전력 MOSFET의 전류 처리 능력은 게이트 채널 폭에 의해 결정된다.게이트 채널 폭은 그림에 표시된 단면의 세 번째(Z축) 치수입니다.

비용과 크기를 최소화하려면 트랜지스터의 다이 영역 크기를 가능한 작게 유지하는 것이 중요합니다.따라서 최적화는 채널 표면적의 폭을 증가시키기 위해 개발되었습니다. 즉, "채널 밀도"를 증가시킵니다.주로 MOSFET 다이의 전체 영역에 걸쳐 반복되는 셀 구조를 생성하는 것으로 구성됩니다.이러한 셀에 대해 여러 가지 모양이 제안되었으며, 가장 유명한 것은 국제 정류기의 HEXFET 장치에 사용된 육각형 모양입니다.

채널 밀도를 높이는 또 다른 방법은 기본 구조의 크기를 줄이는 것입니다.이를 통해 특정 표면 영역에 더 많은 셀을 사용할 수 있으므로 채널 폭이 넓어집니다.다만, 셀의 사이즈가 작아짐에 따라, 모든 셀의 적절한 접점을 확보하는 것은 더욱 어려워집니다.이를 극복하기 위해 종종 "스트립" 구조가 사용됩니다(그림 참조).채널 밀도 면에서 동등한 분해능의 셀 구조보다 효율은 떨어지지만 더 작은 피치에 대처할 수 있습니다.평면 스트라이프 구조의 또 다른 장점은 기생 바이폴라 트랜지스터가 충분한 전방 바이어스로부터 점등하는 눈사태 파괴 이벤트 중에 고장이 발생하기 쉽다는 것입니다.셀 구조에서 한쪽 셀의 소스 단자가 제대로 접촉하지 않으면 눈사태 파괴 이벤트 중에 기생 바이폴라 트랜지스터가 래치될 가능성이 훨씬 높아진다.이로 인해 평면 스트라이프 구조를 이용하는 MOSFET는 극심한 [35]열응력에 의해 눈사태 파괴 시에만 고장날 수 있다.

구조물들

P기판 전력 MOSFET

P-기판 MOSFET(종종 PMOS)는 도핑 유형이 반대인 MOSFET입니다(그림 1의 단면에서 P 대신 N, P 대신 P).이 MOSFET는 P 에피택시와− 함께 P형 기판을 사용하여 만들어집니다.채널이 N 영역에 있을 때 이 트랜지스터는 음의 게이트 대 소스 전압에 의해 켜집니다.따라서 스위치의 단자 중 하나가 입력전압의 높은 쪽에 연결되어 있는 벅컨버터에서는 바람직합니다.N-MOSFET의 경우 이 구성은 에 V + G({in}+GS의 전압을 인가해야 합니다., N_style V_은 과전압이 없습니다.는 P-MOSFET에 필요합니다.

이런 유형의 MOSFET의 주요 단점은 전자보다 이동성이 훨씬 낮은 구멍을 전하 운반체로 사용하기 때문에 온스테이트 성능이 떨어진다는 것입니다.저항률은 이동성과 직접 관련이 있기 때문에 특정 PMOS 디바이스는 같은 치수의 N-MOSFET보다 3배 높은 n(\ R_을 .

VMOS

VMOS 구조는 게이트 영역에 V홈이 있으며 최초의 상용 장치에 [36]사용되었습니다.

UMOS

트렌치-MOS라고도 불리는 이 파워 MOSFET 구조에서 게이트 전극은 실리콘에 식각된 트렌치에 묻힙니다.그 결과 수직 채널이 됩니다.이 구조의 주요 관심사는 JFET 효과가 없다는 것입니다.구조물의 이름은 트렌치의 U자형에서 유래했다.

초접합 딥트렌치 테크놀로지

특히 500V 이상의 전압에 대해서는 CoolMOS 제품을 탑재한 Infineon Technologies를 비롯한 일부 제조업체에서 충전 보상 원칙을 적용하기 시작했습니다.이 기술을 통해 고전압 MOSFET의 디바이스 저항의 최대 기여자(95% 이상)인 에피택셜층의 저항을 5배 이상 줄일 수 있다.

Renesas Electronics는 초접합 MOSFET의 제조 효율과 신뢰성을 향상시키기 위해 딥트렌치 공정 기법을 사용한 초접합 구조를 개발했습니다.이 기술은 저순도 N형 재료에 트렌치를 식각하여 P형 영역을 형성합니다.이 프로세스는 다단계 에피택셜 성장 접근법에 내재된 문제를 극복하고 매우 낮은 온저항과 내부 캐패시턴스 감소를 초래합니다.

p-n접합면적이 증가하기 때문에 슈퍼접합구조는 기존의 평면전력 MOSFET에 비해 역회복시간은 짧지만 역회복전류가 크다.

「 」를 참조해 주세요.

레퍼런스

- ^ IRLZ24N, 55V N채널 전원 MOSFET, TO-220AB 패키지인피니온

- ^ Irwin, J. David (1997). The Industrial Electronics Handbook. CRC Press. p. 218. ISBN 9780849383434.

- ^ a b c "Power MOSFET Basics" (PDF). Alpha & Omega Semiconductor. Retrieved 29 July 2019.

- ^ a b Duncan, Ben (1996). High Performance Audio Power Amplifiers. Elsevier. pp. 178–81. ISBN 9780080508047.

- ^ "Rethink Power Density with GaN". Electronic Design. 21 April 2017. Retrieved 23 July 2019.

- ^ Oxner, E. S. (1988). Fet Technology and Application. CRC Press. p. 18. ISBN 9780824780500.

- ^ a b c d "Advances in Discrete Semiconductors March On". Power Electronics Technology. Informa: 52–6. September 2005. Archived (PDF) from the original on 22 March 2006. Retrieved 31 July 2019.

- ^ Tarui, Y.; Hayashi, Y.; Sekigawa, Toshihiro (September 1969). "Diffusion Self-Aligned MOST; A New Approach for High Speed Device". Proceedings of the 1st Conference on Solid State Devices. doi:10.7567/SSDM.1969.4-1. S2CID 184290914.

- ^ McLintock, G. A.; Thomas, R. E. (December 1972). Modelling of the double-diffused MOST's with self-aligned gates. 1972 International Electron Devices Meeting. pp. 24–26. doi:10.1109/IEDM.1972.249241.

- ^ a b c d Duncan, Ben (1996). High Performance Audio Power Amplifiers. Elsevier. pp. 177–8, 406. ISBN 9780080508047.

- ^ a b Baliga, B. Jayant (2005). Silicon RF Power MOSFETS. World Scientific. ISBN 9789812561213.

- ^ a b Asif, Saad (2018). 5G Mobile Communications: Concepts and Technologies. CRC Press. p. 134. ISBN 9780429881343.

- ^ "SEMI Award for North America". SEMI. Archived from the original on 5 August 2016. Retrieved 5 August 2016.

- ^ a b "International Rectifier's Alex Lidow and Tom Herman Inducted Into Engineering Hall of Fame". Business Wire. 14 September 2004. Retrieved 31 July 2019.

- ^ Baliga, B. Jayant (2015). The IGBT Device: Physics, Design and Applications of the Insulated Gate Bipolar Transistor. William Andrew. pp. xxviii, 5–11. ISBN 9781455731534.

- ^ a b "MDmesh: 20 Years of Superjunction STPOWER MOSFETs, A Story About Innovation". STMicroelectronics. 11 September 2019. Retrieved 2 November 2019.

- ^ 미국 특허 4,754,310

- ^ "Power Transistor Market Will Cross $13.0 Billion in 2011". IC Insights. June 21, 2011. Retrieved 15 October 2019.

- ^ Carbone, James (September–October 2018). "Buyers can expect 30-week lead times and higher tags to continue for MOSFETs" (PDF). Electronics Sourcing: 18–19.

- ^ Williams, Richard K.; Darwish, Mohamed N.; Blanchard, Richard A.; Siemieniec, Ralf; Rutter, Phil; Kawaguchi, Yusuke (23 February 2017). "The Trench Power MOSFET: Part I—History, Technology, and Prospects". IEEE Transactions on Electron Devices. 64 (3): 674–691. Bibcode:2017ITED...64..674W. doi:10.1109/TED.2017.2653239. S2CID 20730536.

- ^ a b "MOSFET". Infineon Technologies. Retrieved 24 December 2019.

- ^ "Infineon EiceDRIVER gate driver ICs" (PDF). Infineon. August 2019. Retrieved 26 December 2019.

- ^ "RF DMOS Transistors". STMicroelectronics. Retrieved 22 December 2019.

- ^ "AN1256: Application note – High-power RF MOSFET targets VHF applications" (PDF). ST Microelectronics. July 2007. Retrieved 22 December 2019.

- ^ Emadi, Ali (2017). Handbook of Automotive Power Electronics and Motor Drives. CRC Press. p. 117. ISBN 9781420028157.

- ^ "Infineon Solutions for Transportation" (PDF). Infineon. June 2013. Retrieved 23 December 2019.

- ^ "HITFETs: Smart, Protected MOSFETs" (PDF). Infineon. Retrieved 23 December 2019.

- ^ "CMOS Sensors Enable Phone Cameras, HD Video". NASA Spinoff. NASA. Retrieved 6 November 2019.

- ^ Veendrick, Harry J. M. (2017). Nanometer CMOS ICs: From Basics to ASICs. Springer. p. 245. ISBN 9783319475974.

- ^ Korec, Jacek (2011). Low Voltage Power MOSFETs: Design, Performance and Applications. Springer Science+Business Media. pp. 9–14. ISBN 978-1-4419-9320-5.

- ^ "Automotive Power MOSFETs" (PDF). Fuji Electric. Retrieved 10 August 2019.

- ^ Williams, R. K.; Darwish, M. N.; Blanchard, R. A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. (2017). "The Trench Power MOSFET—Part II: Application Specific VDMOS, LDMOS, Packaging, Reliability". IEEE Transactions on Electron Devices. 64 (3): 692–712. Bibcode:2017ITED...64..692W. doi:10.1109/TED.2017.2655149. ISSN 0018-9383. S2CID 38550249.

- ^ Simon M. Sze, Modern 반도체 디바이스 물리학, John Wiley and Sons, Inc, 1998 ISBN 0-471-15237-4

- ^ Pierre Alosisi, Les trangisters MOS de puances in Interrupteurs electroniques de puances, traite EGEM, 2003 [프랑스어] ISBN 2-7462-0671-4 지시로

- ^ Murray, Anthony F. J.; McDonald, Tim; Davis, Harold; Cao, Joe; Spring, Kyle. "Extremely Rugged MOSFET Technology with Ultra-low RDS(on) Specified for A Broad Range of EAR Conditions" (PDF). International Rectifier. Retrieved 26 April 2022.

- ^ 던컨 AGrant, John Gowar POWER MOSFETS: 이론과 응용, John Wiley and Sons, Inc. ISBN 0-471-82867-X, 1989

추가 정보

- "Power Semiconductor Devices", B. Jayant Baliga, PWS 출판사, 보스턴.ISBN 0-534-94098-6

실리콘의

실리콘의