플립플롭(전자)

Flip-flop (electronics)

전자학에서 플립플롭과 래치는 상태 정보를 저장할 수 있는 두 가지 안정적인 상태를 가진 회로로, 즉 쌍안정 멀티 진동기입니다. 회로는 하나 이상의 제어 입력에 적용되는 신호에 의해 상태를 변경할 수 있으며 상태를 출력합니다(종종 논리적 보완과 함께). 순차 논리의 기본 저장 요소입니다. 플립플롭과 래치는 컴퓨터, 통신 및 기타 여러 유형의 시스템에 사용되는 디지털 전자 시스템의 기본 구성 요소입니다.

플립플롭과 래치는 단일 비트(2진수)의 데이터를 저장하는 데이터 저장 요소로 사용됩니다. 두 상태 중 하나는 "하나"를 나타내고 다른 하나는 "0"을 나타냅니다. 이러한 데이터 저장은 상태 저장을 위해 사용될 수 있으며, 이러한 회로는 전자공학에서 순차 논리로 설명됩니다. 유한 상태 기계에서 사용되는 경우 출력 및 다음 상태는 현재 입력뿐만 아니라 현재 상태(따라서 이전 입력)에 따라 달라집니다. 펄스의 계수 및 가변 타이밍 입력 신호를 일부 기준 타이밍 신호에 동기화하는 데에도 사용할 수 있습니다.

플립플롭이라는 용어는 일반적으로 게이트를 사용하여 단일 비트의 데이터를 저장하는 레벨-트리거 회로(비동기, 투명 또는 불투명)와 에지-트리거 회로(동기 또는 클록킹)를 모두 지칭합니다.[1] 현대의 저자들은 플립플롭이라는 용어를 에지 트리거 스토리지 요소만을 위한 것과 레벨 트리거 스토리지 요소를 위한 래치만을 위한 것으로 예약합니다.[2][3] 모호성을 피하기 위해 "edge-triggered" 및 "level-triggered"라는 용어를 사용할 수 있습니다.[4]

레벨 트리거된 래치가 활성화되면 투명해지지만, 에지 트리거된 플립플롭의 출력은 클럭 에지에서만 변경됩니다(양의 이동 또는 음의 이동).

다양한 유형의 플립플롭 및 래치가 집적 회로로 사용할 수 있으며 일반적으로 칩당 여러 요소가 있습니다. 예를 들어 74HC75는 7400 시리즈의 4중 투명 래치입니다.

히스토리

최초의 전자 걸쇠는 1918년 영국 물리학자 윌리엄 에클스와 F에 의해 발명되었습니다. W. Jordan.[5][6] 처음에는 에클레스-요르단 트리거 회로라고 불렸고 두 개의 능동 소자(진공관)로 구성되었습니다.[7] 이 디자인은 1943년 영국의 거상 코드브레이킹 컴퓨터에[8] 사용되었으며 이러한 회로는 집적 회로가 도입된 후에도 컴퓨터에서 트랜지스터화된 버전이 일반적이었지만 현재는 로직 게이트로 만든 래치와 플립플롭도 일반적입니다.[9][10] 초기 래치는 트리거 회로 또는 멀티 진동기로 다양하게 알려져 있었습니다.

미국 제트 추진 연구소의 엔지니어인 P. L. 린들리(P. L. Lindley)에 따르면 아래에 자세히 설명된 플립플롭 유형(SR, D, T, JK)은 1954년 몽고메리 피스터(Montgomery Phister)의 컴퓨터 디자인에 관한 UCLA 과정에서 처음 논의되었고, 그 후 그의 책 디지털 컴퓨터의 논리적 디자인(Logical Design of Digital Computers)에 등장했습니다.[11][12] 당시 린들리는 Hughes Aircraft에서 엘드레드 넬슨(Eldred Nelson) 밑에서 일을 하고 있었는데, 그는 두 입력이 모두 켜져 있을 때 상태를 바꾸는 플립플롭에 대한 JK라는 용어를 만들었습니다(논리적인 "하나"). 다른 이름들은 피스터가 만들었습니다. 그들은 아래에 주어진 일부 정의와 약간 다릅니다. 린들리는 휴즈 에어크래프트에서 근무하면서 JK 플립플롭에 대한 이야기를 임기를 만든 책임이 있는 엘드레드 넬슨으로부터 들었다고 설명합니다. 당시 휴즈에서 사용되던 플립플롭은 모두 J-K로 알려지게 된 유형이었습니다. 논리 시스템을 설계할 때 넬슨은 플립플롭 입력에 다음과 같은 문자를 할당했습니다: #1: A & B, #2: C & D, #3: E & F, #4: G & H, #5: J & K. 넬슨은 1953년에 출원된 특허 출원에서 "j 입력"과 "k 입력"이라는 표기법을 사용했습니다.[13]

실행

일반적인 회로에서는 진공관, 바이폴라 트랜지스터, 전계효과 트랜지스터, 인버터, 반전 로직 게이트 등의 단일 쌍의 교차 결합된 반전 소자를 중심으로 투명 또는 비동기 래치를 형성할 수 있습니다.

클럭드 플립플롭은 동기식 시스템을 위해 특별히 설계되었습니다. 이러한 장치는 전용 클럭 신호의 전환(클럭킹, 펄싱 또는 스트로빙이라고 함)을 제외하고는 입력을 무시합니다. 클록킹은 플립플롭이 전환 시 입력 신호 값에 따라 변경되거나 출력 신호를 유지하도록 합니다. 일부 플립플롭은 시계의 상승 에지에서 출력을 변경하고, 다른 플립플롭은 하강 에지에서 출력을 변경합니다.

기본 증폭 단계는 반전이므로 두 단계를 연속적으로 연결하여(캐스케이드로) 필요한 비반전 증폭기를 형성할 수 있습니다. 본 실시예에서, 각 증폭기는 다른 반전 증폭기에 대한 능동 반전 피드백 네트워크로 간주될 수 있습니다. 따라서 회로 다이어그램은 일반적으로 대칭 교차 결합 쌍으로 그려지지만 두 단계는 비반전 루프로 연결됩니다(두 도면은 처음에 에클레스-요르단 특허에 소개됨).

종류들

플립플롭 및 래치는 SR("set-reset"), D("data"), T("toggle") 및 JK(위의 이력 섹션 참조)와 같은 일반적인 유형으로 나눌 수 있습니다. 특정 유형의 동작을 특성 방정식이라고 하는 것으로 설명할 수 있습니다. 특성 방정식은 "다음"(즉, 다음 클럭 펄스 이후) 을 입력 신호 및/또는 인 Q displaystyle Q로 유도합니다

간단한 세트 리셋 래치

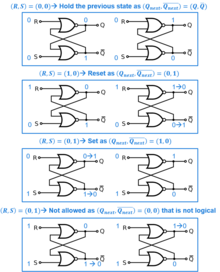

스태틱 게이트를 빌딩 블록으로 사용할 때 가장 기본적인 래치는 단순한 SR 래치로, S와 R은 설정과 리셋을 의미합니다. 즉, 세트 S=1은 비트를 1로 설정하고, 리셋 R=1은 비트를 0으로 설정합니다. 또는 두 입력 세트를 세트 1과 세트 0이라고 부를 수도 있습니다(세트라는 용어만 사용하면 비트를 세트에 제공되는 입력으로 설정하는 것으로 오해될 수 있음). 이 이름을 사용하면 아래 설명에서 0과 1을 동시에 설정하려고 하면 SR 래치가 예측 불가능하게 작동한다는 것을 직관적으로 알 수 있습니다.

SR 래치는 교차 결합된 NOR 또는 NAND 논리 게이트 쌍으로 구성할 수 있습니다. 저장된 비트는 Q로 표시된 출력에 존재합니다. 아래의 회로 구현에 대한 이해를 돕기 위해 NAND, NOR, OR을 제어된 동작으로 생각하는 것이 편리합니다. 즉, 이들 게이트는 모두 입력이 대칭이지만, 제어 상태에 따라 한 비트는 우리가 선택한 제어 비트로 선택하고 다른 비트는 처리할 입력으로 선택하는 것이 편리합니다. 아래에서 볼 수 있듯이, 이 게이트들은 모두 입력을 무시하고 일정한 값을 출력하는 하나의 제어 값을 가지고 있는 반면, 다른 제어 값들은 입력을 통과하게 합니다(보완될 수 있음). x를 입력이라고 부르고 다른 비트는 컨트롤이 됩니다.

기본적으로 이들은 모두 특정 값을 설정하거나 입력 값을 통과시키는 스위치로 사용될 수 있습니다.

SR NOR 래치

- S = 1, R = 0: Set

- S = 0, R = 0: Hold

- S = 0, R = 1: Reset

- S = 1, R = 1: 허용되지 않음

SR NOR 래치는 그림과 같이 각 NOR의 출력이 다른 NOR의 한 입력으로 팬아웃되는 두 개의 병렬 NOR 게이트로 구성됩니다. 우리는 피드백 입력을 호출하거나 단순히 이러한 출력 대 입력 연결을 피드백합니다. 나머지 입력은 위에서 설명한 대로 제어 입력으로 사용할 것입니다. 이 시점에서는 모든 것이 대칭이기 때문에 출력이 어떤 입력에 연결되는지는 중요하지 않습니다. 이제 나머지 제어 입력 중 어떤 것이 설정 및 재설정이 될 것인지 선택함으로써 대칭성을 깨뜨리고, 설정 컨트롤을 사용하여 NOR 게이트를 "set NOR", 리셋 컨트롤을 사용하여 "reset NOR"이라고 부를 수 있습니다. 그림에서 set NOR은 하단이고, reset NOR은 상단입니다. 리셋 NOR의 출력은 저장된 비트 Q가 될 것이고, 우리는 세트 NOR의 출력이 그 보어 Q를 저장하는 것을 볼 것입니다.

SR NOR 래치의 동작을 유도하기 위해 S와 R을 제어 입력으로 간주하고 위의 식에서 제어 1을 사용한 설정 및 재설정 NOR은 출력을 0으로 고정하고 제어 0을 사용한 설정 및 재설정 NOR은 NOT 게이트로 작동합니다. 이를 통해 SR 래치의 동작을 단순한 조건으로 유도할 수 있습니다(예를 들어 각 라인에 값을 할당하는 대신 전파 방법을 확인할 수 있습니다).

- R과 S가 모두 0이지만 RNOR과 SNOR 모두 출력의 보완인 피드백을 부과할 뿐이지만, 이는 출력이 서로 보완적인 경우에만 충족됩니다. 따라서 출력 Q와 Q는 Q=0이든 Q=1이든 일정한 상태로 유지됩니다.

- S=1이고 R=0인 경우 세트 NOR은 Q=0을 고정하고 리셋 NOR은 Q=1을 조정하여 설정합니다. S가 0으로 다시 설정되면 위에서 설명한 대로 값이 유지됩니다.

- 마찬가지로, R=1인 경우 S=0인 경우 리셋 NOR은 Q=0을 고정하고 세트 NOR은 적응 Q=1로 고정합니다. R이 0으로 다시 설정되면 다시 상태가 유지됩니다.

- R=S=0인 경우 NOR은 두 출력을 모두 0으로 고정합니다. 이는 상보적인 값을 저장하는 유효한 상태가 아닙니다.

SR 래치 작동[4]

특성표 들뜸표 S R 큐next 액션. Q 큐next S R 0 0 Q 홀드 상태 0 0 0 X 0 1 0 재설정 0 1 1 0 1 0 1 세트 1 0 0 1 1 1 X 허용되지 않음 1 1 X 0

참고: X는 상관 없음을 의미합니다. 즉, 0 또는 1 중 하나가 유효한 값입니다.

R = S = 1 조합을 제한 조합 또는 금지 상태라고 하는데, 이는 두 NOR 게이트가 0을 출력할 때 Q가 아닌 논리 방정식 Q = 를 깨뜨리기 때문입니다. 또한 두 입력이 동시에 낮을 수 있는 회로(즉, 제한 상태에서 유지 상태로 전환)에서는 이 조합이 부적절합니다. 출력은 게이트 간의 전파 시간 관계(레이스 조건)에 따라 1 또는 0에서 잠깁니다.

제한된 조합을 극복하기 위해 변환할 입력에 게이트를 추가할 수 있습니다. (S, R) = (1, 1) restrict가 아닌 조합 중 하나에. 다음과 같습니다.

- Q = 1 (1, 0) – S(지배)-라고 함

- Q = 0 (0, 1) – R(지배적)이라고 함-

이것은 거의 모든 프로그래밍 가능한 로직 컨트롤러에서 수행됩니다.

- 상태 유지(0, 0) – E-래치라고 함

또는 출력을 전환하기 위해 제한된 조합을 만들 수 있습니다. 결과는 JK 래치입니다.

SR 래치의 특성 방정식은 다음과 같습니다.

- = Q+ R ¯ S Q_{\text{bar {Q+{\bar {R}S} 또는 Q ext= R ¯(Q + S) {\displaystyle Q_{\text{nxt}}={\bar {R}(Q + S)}

여기서 A + B는 (A 또는 B), AB는 (A 및 B)를 의미합니다.

또 다른 표현은 다음과 같습니다.

- =+ R ¯ Q {\displaystyle Q_{\text{net}} = Sbar {R}Q SR = 0 {\displaystyl SR = 0}

SR NAND 래치

아래에 표시된 회로는 기본 NAND 래치입니다. 또한 입력은 일반적으로 Set과 Reset 각각에 대해 S와 R로 지정됩니다. 일반적으로 NAND 입력은 논리 1이어야 래치 동작에 영향을 주지 않기 때문에 이 회로에서는 입력이 반전된 것으로 간주됩니다(또는 활성 로우).

회로는 제어 입력 신호가 변경된 후에도 "기억"하고 논리 상태를 유지하기 위해 SR NOR과 동일한 피드백을 사용합니다. 다시 말하지만, 1-제어 NAND는 항상 0을 출력하는 반면, 0-제어 NAND는 NOT 게이트의 역할을 합니다. S 입력과 R 입력이 모두 높으면 피드백은 Q 출력을 이전 상태로 유지합니다. 둘 중 하나가 0이면 출력 비트를 0으로 고정하고 다른 비트는 보형물에 적응합니다. S=R=0이 잘못된 상태를 생성합니다.

|  |

SRAND-OR 래치

교습적인 관점에서 보면, 크로스 커플링된 한 쌍의 부품(트랜지스터, 게이트, 튜브 등)으로 그려진 SR 래치는 초보자에게는 이해하기 어려운 경우가 많습니다. 사실 더 쉬운 설명은 크로스 커플링 대신 래치를 단일 피드백 루프로 그리는 것입니다. 다음은 한 번의 반전 입력과 OR 게이트가 있는 AND 게이트로 구축된 SR 래치입니다. 인버터는 래치 기능을 위해 필요한 것이 아니라 두 입력 모두를 High-active 상태로 만드는 데 필요합니다.

SRAND-OR 래치 작동 S R 액션. 0 0 변경 없음, 랜덤 초기 1 0 Q = 1 X 1 Q = 0

SR AND-OR 래치는 S = 1, R = 1이 잘 정의된다는 이점이 있습니다. 위 버전의 SR AND-OR 래치에서는 S 신호보다 R 신호에 우선 순위를 부여합니다. R보다 S의 우선순위가 필요한 경우 AND 게이트의 출력 대신 출력 Q를 OR 게이트의 출력에 연결하여 이를 달성할 수 있습니다.

SR AND-OR 래치는 위에서 AND와 OR의 제어 뷰를 통해 두 게이트를 분리하여 설명할 수 있기 때문에 이해하기가 더 쉽습니다. S나 R이 모두 설정되지 않으면 OR 게이트와 AND 게이트가 모두 "홀드 모드"에 있습니다. 즉, 입력을 통과시키고 출력은 피드백 루프에서 입력됩니다. 입력 S = 1이면 OR 게이트는 피드백 루프("설정 모드")로부터의 다른 입력에 관계없이 1을 출력합니다. 입력 R = 1이면 AND 게이트는 피드백 루프(" reset 모드")의 다른 입력과 상관없이 0을 출력합니다. 그리고 AND 게이트는 OR 게이트의 출력을 입력으로 받기 때문에 R이 S보다 우선합니다. 교차 결합 게이트로 그려진 래치는 한 게이트의 동작이 다른 게이트와 얽혀 있는 것처럼 보이기 때문에 덜 직관적으로 보일 수 있습니다. 표준 NOR 또는 NAND 래치를 피드백 루프로 다시 그릴 수도 있지만, 피드백 루프의 경우 전체 피드백 루프에서 동일한 신호 값을 표시하지 않습니다. 그러나 SR AND-OR 래치는 반전 Q 출력이 필요한 경우 추가 인버터가 필요하다는 단점이 있습니다.

논리 변환을 사용하여 SR AND-OR 래치를 SR NOR 래치로 변환할 수 있습니다. 논리 변환: OR 게이트의 출력과 AND 게이트의 두 번째 입력을 반전시키고 추가된 두 인버터 사이에 반전된 Q 출력을 연결합니다. 두 입력이 모두 반전된 AND 게이트는 De Morgan의 기준에 따라 NOR 게이트와 동일합니다.법률

JK래치

JK 래치는 JK 플립플롭보다 훨씬 덜 자주 사용됩니다. JK 래치는 다음 상태 테이블을 따릅니다.

JK 래치 진리표 J K 큐next 댓글 0 0 Q 잔돈 없음 0 1 0 재설정 1 0 1 세트 1 1 Q 토글

따라서 JK 래치는 입력 조합 11을 통과하면 출력이 0과 1 사이에서 진동하도록 만들어진 SR 래치입니다.[16] JK 플립플롭과 달리 JK 래치용 11 입력 조합은 토글링을 지시하는 클럭이 없기 때문에 그다지 유용하지 않습니다.[17]

게이트 래치 및 조건부 투명도

래치는 투명하게 설계되었습니다. 즉, 입력 신호 변화는 출력의 즉각적인 변화를 야기합니다. 다른 입력("활성화" 입력)이 인수되지 않을 때 단순 투명 래치에 추가 논리를 추가하여 투명하지 않거나 불투명하게 만들 수 있습니다. 여러 투명 래치가 동일한 활성화 신호를 사용하여 서로를 따라가면 신호가 한 번에 모든 래치를 통해 전파될 수 있습니다. 그러나 투명-로우 래치(또는 그 반대)에 의해 투명-하이 래치를 수행하면 상태와 출력이 클럭 에지에서만 변경되어 마스터-슬레이브 플립플롭이라고 하는 것이 형성됩니다.

게이트 SR 래치

게이트 SR 래치는 반전 SR 래치에 두 번째 레벨의 NAND 게이트를 추가하여 만들 수 있습니다. 추가 NAND 게이트는 입력을 반전시켜 SR 래치가 게이티드 SR 래치가 됩니다(SR 래치는 반전 활성화된 게이티드 SR 래치로 변환됩니다).

또는 SR 래치에 두 번째 레벨의 AND 게이트를 추가하여 게이트된 SR 래치(비반전 활성화)를 만들 수 있습니다.

E가 높으면 신호가 입력 게이트를 통과하여 캡슐화된 래치로 전달됩니다. (0, 0) = 홀드를 제외한 모든 신호 조합이 즉시 (Q, Q) 출력에 재현됩니다. 즉, 래치가 투명합니다.

Elow(enable false)를 사용하면 래치가 닫히고(불투명) E가 마지막으로 하이 상태로 유지됩니다.

활성화 입력은 때때로 클럭 신호이지만 더 자주 읽기 또는 쓰기 스트로브입니다. 활성화 입력이 클럭 신호인 경우 래치는 아래 플립플롭과 같이 에지에 민감한 것과 달리 (클럭 신호의 레벨에 대해) 레벨에 민감하다고 합니다.

|  |

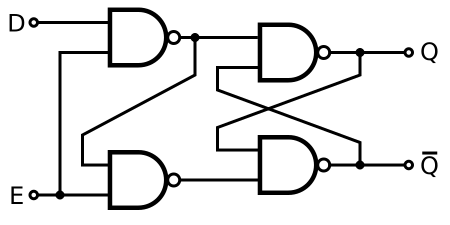

게이트 D 래치

이 래치는 게이티드 SR 래치의 두 개의 능동 입력 조합(01과 10)에서 R이 S의 보체라는 사실을 이용합니다. 입력 NAND 스테이지는 데이터 입력 신호를 반전시켜 다음 SR 래치를 위해 두 개의 D 입력 상태(0과 1)를 이 두 개의 입력 조합으로 변환합니다. 활성화 신호의 낮은 상태는 비활성화된 "11" 조합을 생성합니다. 따라서 게이티드 D-래치는 단일 입력 동기 SR 래치로 간주될 수 있습니다. 이 구성은 제한된 입력 조합의 적용을 방지합니다. 투명 래치, 데이터 래치 또는 간단히 게이트 래치라고도 합니다. 데이터 입력과 활성화 신호(때로는 클럭 또는 컨트롤이라는 이름도 있음)가 있습니다. 투명이라는 단어는 인에이블 입력이 켜져 있을 때 신호가 입력 D에서 출력 Q로 직접 회로를 통해 전파된다는 사실에서 비롯됩니다. 게이트 D 래치는 또한 클럭이나 활성화 신호의 레벨에 따라 레벨에 민감합니다.

투명 래치는 일반적으로 I/O 포트 또는 비동기 시스템 또는 동기식 2상 시스템(2상 클럭을 사용하는 동기식 시스템)에서 사용되며, 여기서 서로 다른 클럭 위상에서 작동하는 2개의 래치가 마스터-슬레이브 플립플롭에서와 같이 데이터 투명성을 방지합니다.

아래 참표는 활성화/클럭 입력이 0일 때 D 입력은 출력에 영향을 미치지 않음을 보여줍니다. E/C가 높으면 출력은 D와 같습니다.

|  |

- SR NAND 래치를 기반으로 한 게이티드 D 래치

- SRNOR 래치를 기반으로 한 Gated D 래치

- 애니메이션 게이트 D 래치입니다. 검은색과 흰색은 각각 논리적인 '1'과 '0'을 의미합니다.

- D = 1, E = 1: set

- D = 1, E = 0: hold

- D = 0, E = 0: hold

- D = 0, E = 1: reset

얼래치

고전적인 게이트 래치 디자인에는 몇 가지 바람직하지 않은 특성이 있습니다.[18] 더블 레일 로직 또는 인버터가 필요합니다. 입출력 전파에는 최대 3개의 게이트 지연이 소요될 수 있습니다. 입력 대 출력의 전파는 일정하지 않습니다. 어떤 출력은 두 번의 게이트 지연이 발생하고 다른 출력은 세 번의 게이트 지연이 발생합니다.

디자이너들은 대안을 찾았습니다.[19] 성공적인 대안은 이어 래치입니다. 한 번의 데이터 입력만 필요하며 출력은 지속적으로 두 번의 게이트 지연이 발생합니다. 또한, 많은 일반적인 계산 회로에는 마지막 두 레벨로 OR 계층과 AND 계층이 뒤따르기 때문에 얼 래치의 두 게이트 레벨은 래치를 구동하는 회로의 마지막 두 게이트 레벨과 병합될 수 있습니다. 래치 기능을 병합하면 추가 게이트 지연 없이 래치를 구현할 수 있습니다.[18] 이 병합은 일반적으로 파이프라인 컴퓨터의 설계에 활용되며, 사실은 원래 IBM System/360 Model 91에 사용하기 위해 John G. Earle에 의해 개발되었습니다.[20]

Earle 래치는 위험 요소가 없습니다.[21] 중간 NAND 게이트가 생략되면 논리가 덜 필요하기 때문에 일반적으로 사용되는 극성 홀드 래치를 얻습니다.[21][22] 그러나 논리적 위험에 노출되기 쉽습니다. 의도적으로 클럭 신호를 왜곡하면 위험을 피할 수 있습니다.[22]

- 얼 래치는 상보적인 인에이블 입력을 사용합니다: 활성 로우(E_L) 활성화 및 활성 하이(E_H) 활성화

- 애니메이션 이어 래치입니다. 검은색과 흰색은 각각 논리적인 '1'과 '0'을 의미합니다.

- D = 1, E_H = 1: set

- D = 0, E_H = 1: reset

- D = 1, E_H = 0: hold

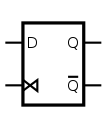

디플립플롭

D 플립플롭은 널리 사용되며 "데이터" 플립플롭으로 알려져 있습니다. D 플립플롭은 클럭 주기의 특정 부분(예: 클럭의 상승 에지)에서 D 입력 값을 캡처합니다. 캡처된 값이 Q 출력이 됩니다. 다른 경우에는 출력 Q가 변경되지 않습니다.[23][24] D 플립플롭은 메모리 셀, 0차 홀드 또는 지연 라인으로 볼 수 있습니다.[25]

진리표:

시계 D 큐next 상승엣지 0 0 상승엣지 1 1 논라이징 X Q

(X는 Don't care 상태를 의미하며, 이는 신호와 무관함을 의미합니다.)

IC의 대부분의 D형 플립플롭은 SR 플립플롭과 마찬가지로 설정 또는 재설정 상태(D 및 클럭 입력을 무시함)로 강제되는 기능을 가지고 있습니다. 일반적으로 불법 S = R = 1 조건은 D타입 플립플롭에서 해결됩니다. S = R = 0으로 설정하면 플립플롭이 위에서 설명한 대로 작동합니다. 다음은 가능한 다른 S 및 R 구성에 대한 진리표입니다.

인풋 출력물 S R D > Q Q 0 1 X X 0 1 1 0 X X 1 0 1 1 X X 1 1

이 플립플롭은 많은 전자 장치의 필수 부분인 시프트 레지스터의 기초를 형성하기 때문에 매우 유용합니다. D형 "투명 래치"에 비해 D 플립플롭의 장점은 플립플롭이 클럭되는 순간 D 입력 핀의 신호가 캡처되고, D 입력의 후속 변경 사항은 다음 클럭 이벤트까지 무시된다는 것입니다. 예외는 일부 플립플롭에 "리셋" 신호 입력이 있어 Q가 (0으로) 재설정되고 클럭과 비동기 또는 동기화될 수 있습니다.

위의 회로는 레지스터의 내용을 오른쪽으로 이동합니다. 클럭의 활성 전환마다 한 비트씩 위치합니다. 입력 X는 가장 왼쪽 비트 위치로 이동됩니다.

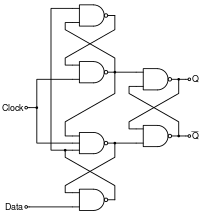

고전적인 양의 에지 트리거 D 플립플롭

이 회로는[26] SR NAND 래치로 구현되는 두 단계로 구성됩니다. 입력 스테이지(왼쪽의 두 래치)는 클럭 및 데이터 신호를 처리하여 출력 스테이지(오른쪽의 단일 래치)에 대한 올바른 입력 신호를 보장합니다. 클럭이 낮으면 데이터 입력과 상관없이 입력단의 출력 신호가 모두 높고 출력 래치는 영향을 받지 않으며 이전 상태를 저장합니다. 클럭 신호가 로우에서 하이로 변경되면 출력 전압(데이터 신호에 대한 depending) 중 하나만 로우가 되어 출력 래치를 설정/resets합니다. D = 0이면 로우 출력이 되고 D = 1이면 로우 출력이 됩니다. 클럭 신호가 계속 하이 상태를 유지하면 데이터 입력에 관계없이 출력이 상태를 유지하고 클럭이 하이 상태인 동안 입력 논리 0(출력 스테이지의)이 활성 상태를 유지하기 때문에 출력 래치가 해당 상태를 유지하도록 합니다. 따라서 출력 래치의 역할은 클럭이 낮을 때에만 데이터를 저장하는 것입니다.

두 회로 모두 데이터 입력 신호를 반전시켜 출력 SR 래치를 위해 두 D 입력 상태(0 및 1)를 두 입력 조합(01 및 10)으로 변환하므로 회로는 게이트된 D 래치와 밀접하게 관련되어 있습니다(두 회로 모두 단일 D 신호를 두 개의 상보적인 S 및 R 신호로 분할). 차이점은 게이트된 D 래치에서는 단순한 NAND 논리 게이트가 사용되는 반면, 포지티브 에지 트리거된 D 플립플롭 SR NAND 래치는 이러한 목적으로 사용된다는 점입니다. 이러한 래치의 역할은 저전압(논리적 0)을 생성하는 능동 출력을 "잠금"하는 것입니다. 따라서 양 에지 트리거 D 플립플롭은 래치된 입력 게이트가 있는 게이트 D 래치로 간주될 수도 있습니다.

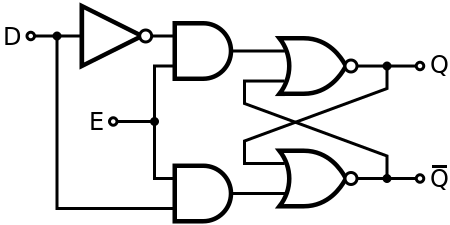

마스터-슬레이브 에지 트리거 D 플립플롭

마스터-슬레이브 D 플립플롭은 두 개의 게이트된 D 래치를 직렬로 연결하고 이들 중 하나에 대한 인에이블 입력을 반전시켜 생성됩니다. 슬레이브 래치는 항상 마스터 래치로부터 새로운 값을 복사하고 마스터 래치와 클럭 신호의 값의 변화에 따라서만 값을 변경하기 때문에, 마스터 래치는 슬레이브 래치의 출력 값 Q를 제어하고 슬레이브 래치가 활성화될 때마다 값을 유지하도록 강제하기 때문에 마스터-슬레이브라고 불립니다.

포지티브 에지 트리거된 마스터-슬레이브 D 플립플롭의 경우 클럭 신호가 로우(논리 0)일 때 첫 번째 또는 "마스터" D 래치(역전 클럭 신호)가 하이(논리 1)일 때 "활성화"됩니다. 이를 통해 "마스터" 래치는 클럭 신호가 로우에서 하이로 전환될 때 입력 값을 저장할 수 있습니다. 클럭 신호가 하이(0~1)가 되면 첫 번째 래치의 반전 "활성화"가 로우(1~0)가 되고 마스터 래치의 입력에서 보이는 값이 "잠김"이 됩니다. 거의 동시에 두 번째 또는 "슬레이브" D 래치의 두 번 반전된 "활성화"가 클럭 신호와 함께 로우에서 하이(0에서 1)로 전환됩니다. 이를 통해 이제 "잠김" 마스터 래치에 의해 시계의 상승 에지에서 캡처된 신호가 "슬레이브" 래치를 통과할 수 있습니다. 클럭 신호가 로우(1~0)로 돌아오면 "슬레이브" 래치의 출력이 "잠김" 상태가 되고, "마스터" 래치가 다음 상승 클럭 에지에 대비하여 새로운 값을 수용하기 시작하는 동안 클럭의 마지막 상승 에지에서 보이는 값이 유지됩니다.

회로에서 가장 왼쪽 인버터를 제거하면 클럭 신호의 하강 에지에서 스트로브를 이루는 D형 플립플롭이 생성됩니다. 이것은 다음과 같은 진리표를 가지고 있습니다.

D Q > 큐next 0 X 빠지는 것 0 1 X 빠지는 것 1

듀얼 에지 트리거 D 플립플롭

시계의 상승 에지와 하강 에지에서 새로운 값으로 읽는 플립플롭을 듀얼 에지 트리거 플립플롭이라고 합니다. 이러한 플립플롭은 2개의 단일 에지 트리거된 D-타입 플립플롭 및 멀티플렉서를 사용하거나, 2개의 단일 에지 트리거된 D-타입 플립플롭 및 3개의 XOR 게이트를 사용하여 구축될 수 있습니다.

에지 트리거 동적 D 스토리지 요소

D 플립플롭의 효율적인 기능적 대안은 동적 회로(정보가 캐패시턴스에 저장됨)를 통해 충분히 자주 클럭되는 한 만들 수 있습니다. 그러나 진정한 플립플롭은 아니지만 기능적 역할 때문에 여전히 플립플롭이라고 불립니다. 마스터-슬레이브 D 요소는 시계의 가장자리에서 트리거되지만 구성 요소는 각각 시계 레벨에 의해 트리거됩니다. "edge-triggered D 플립플롭"은 진정한 플립플롭이 아님에도 불구하고, 마스터-슬레이브 속성이 없습니다.

에지 트리거 D 플립플롭은 동적 로직을 사용한 통합 고속 동작에서 구현되는 경우가 많습니다. 즉, 장치가 전환되지 않는 동안 디지털 출력이 기생 장치 캐패시턴스에 저장됩니다. 이러한 동적 플립플롭 설계는 하나 이상의 내부 노드를 방전하는 것만으로 재설정 작업을 수행할 수 있기 때문에 간단한 재설정도 가능합니다. 일반적인 동적 플립플롭 유형은 전력이 거의 없고 고속으로 플립플롭 작동을 수행하는 TSPC(True Single Phase Clock) 유형입니다. 그러나 동적 플립플롭은 일반적으로 정적 또는 낮은 클럭 속도에서는 작동하지 않습니다. 충분한 시간이 주어지면 누출 경로는 플립플롭이 비활성 상태로 진입할 수 있을 만큼 충분히 기생 커패시턴스를 방출할 수 있습니다.

플립플롭

T 입력이 높으면 T 플립플롭은 클럭 입력을 쓰다듬을 때마다 상태("토글")를 바꿉니다. T 입력이 낮으면 플립플롭이 이전 값을 유지합니다. 이 동작은 특성 방정식으로 설명됩니다.

- QT{\ (XOR 연산자 )

진리표에서 설명할 수 있습니다.

플립플롭[27] 조작

특성표 들뜸표 댓글 댓글 0 0 0 홀드 상태(시계 없음) 0 0 0 잔돈 없음 0 1 1 홀드 상태(시계 없음) 1 1 0 잔돈 없음 1 0 1 토글 0 1 1 보형물 1 1 0 토글 1 0 1 보형물

T가 높게 유지되면 토글 플립플롭은 클럭 주파수를 2로 분할합니다. 즉, 클럭 주파수가 4MHz이면 플립플롭에서 얻은 출력 주파수는 2MHz가 됩니다. 이 "분할 기준" 기능은 다양한 유형의 디지털 카운터에 적용됩니다. T 플립플롭은 JK 플립플롭(J & K 핀이 서로 연결되어 T 역할을 함) 또는 D 플립플롭(T 입력 XOR Q가previous D 입력을 구동함)을 사용하여 구축할 수도 있습니다.

JK flip-flop

JK 플립플롭은 J = K = 1 조건을 "flip" 또는 토글 명령으로 해석하여 SR 플립플롭의 동작(J: Set, K: Reset)을 증가시킵니다. 구체적으로, 조합 J = 1, K = 0은 플립플롭을 설정하기 위한 명령이고, 조합 J = 0, K = 1은 플립플롭을 재설정하기 위한 명령이며, 조합 J = K = 1은 플립플롭을 전환하기 위한 명령, 즉 출력을 현재 값의 논리적인 보표로 변경하기 위한 명령입니다. J = K = 0 을 설정하면 현재 상태가 유지됩니다. D 플립플롭을 합성하기 위해 K를 J의 여집합과 같게 설정하기만 하면 됩니다(입력 J는 입력 D로 동작합니다). 마찬가지로 T 플립플롭을 합성하기 위해 K를 J와 같게 설정합니다. 따라서 JK 플립플롭은 SR 플립플롭, D 플립플롭 또는 T 플립플롭으로 작동하도록 구성할 수 있으므로 범용 플립플롭입니다.

JK 플립플롭의 특성 방정식은 다음과 같습니다.

그에 상응하는 진리표는 다음과 같습니다.

JK 플립플롭 조작[27]

특성표 들뜸표 J K 댓글 큐next Q 큐next 댓글 J K 0 0 홀드 상태 Q 0 0 잔돈 없음 0 X 0 1 재설정 0 0 1 세트 1 X 1 0 세트 1 1 0 재설정 X 1 1 1 토글 Q 1 1 잔돈 없음 X 0

타이밍 고려사항

타이밍 파라미터

입력은 조리개로 알려진 시계의 상승 에지 주변의 주기로 일정하게 유지되어야 합니다. 백합 패드에 개구리 사진을 찍는 것을 상상해 보세요.[28] 그러면 개구리가 물 속으로 뛰어 든다고 가정해 보겠습니다. 개구리가 물속으로 뛰어드는 모습을 사진으로 찍으면 물속으로 뛰어드는 모습이 흐릿하게 나옵니다. 개구리가 어느 상태에 있었는지는 분명하지 않습니다. 하지만 개구리가 패드 위에 착실히 앉아 있는 동안(또는 물속에 착실히 있는 동안) 사진을 찍으면 선명한 사진을 얻을 수 있습니다. 마찬가지로, 플립플롭에 대한 입력은 플립플롭의 조리개 동안 일정하게 유지되어야 합니다.

설정 시간은 데이터 입력이 클럭 이벤트 전에 안정적으로 유지되어야 하는 최소 시간이므로 클럭에 의해 데이터가 안정적으로 샘플링됩니다.

홀드 시간은 데이터 입력이 클럭 이벤트 후 안정적으로 유지되어야 하는 최소 시간으로, 클럭에 의해 데이터가 안정적으로 샘플링됩니다.

조리개는 설정 및 유지 시간의 합입니다. 데이터 입력은 이 기간 동안 안정적으로 유지되어야 합니다.[28]

복구 시간은 비동기 세트 또는 리셋 입력이 클럭 이벤트 전에 비활성화되어야 하는 최소 시간으로, 데이터가 클럭에 의해 신뢰성 있게 샘플링됩니다. 따라서 비동기 세트 또는 리셋 입력에 대한 복구 시간은 데이터 입력에 대한 설정 시간과 유사합니다.

제거 시간은 클럭 이벤트 후 비동기 세트 또는 리셋 입력이 비활성화되어야 하는 최소 시간으로, 데이터가 클럭에 의해 신뢰성 있게 샘플링됩니다. 따라서 비동기 세트 또는 리셋 입력에 대한 제거 시간은 데이터 입력에 대한 홀드 시간과 유사합니다.

비동기 입력(설정, 재설정)에 적용되는 짧은 임펄스를 복구-제거 기간 내에 완전히 적용해서는 안 됩니다. 그렇지 않으면 플립플롭이 적절한 상태로 전환될지 여부가 완전히 결정되지 않습니다. 또 다른 경우, 비동기 신호가 단순히 복구/제거 시간 사이에 발생하는 하나의 전환을 수행하는 경우, 결국 플립플롭은 적절한 상태로 전환되지만, 동기 입력 신호에 따라 출력에 매우 짧은 글리치가 나타날 수도 있고 나타나지 않을 수도 있습니다. 이 두 번째 상황은 회로 설계에 중요성을 가질 수도 있고 그렇지 않을 수도 있습니다.

설정 및 재설정(및 기타) 신호는 동기식 또는 비동기식일 수 있으며, 따라서 설정/보류 또는 복구/제거 시간 중 하나로 특징지어질 수 있으며, 동기식은 플립플롭의 설계에 매우 의존적입니다.

동기 신호보다 비동기 신호가 덜 중요한 것으로 판명될 수 있기 때문에 더 큰 회로의 타이밍을 확인할 때 설정/보류 및 복구/제거 시간을 구별해야 하는 경우가 많습니다. 미분은 회로 설계자에게 이러한 유형의 신호에 대한 검증 조건을 독립적으로 정의할 수 있는 기능을 제공합니다.

준안정성

플립플롭은 준안정성이라는 문제의 대상이 되는데, 이는 데이터와 클럭 또는 클럭과 리셋과 같은 두 입력이 거의 동시에 변화할 때 발생할 수 있습니다. 순서가 명확하지 않거나 적절한 타이밍 제약 내에서 출력이 예측 불가능하게 작동하여 한 상태 또는 다른 상태로 정착하는 데 정상보다 몇 배나 더 오래 걸리거나 정착하기 전에 몇 번이나 진동할 수도 있습니다. 이론적으로 정착하는 시간은 제한되어 있지 않습니다. 컴퓨터 시스템에서, 이 준안정성은 다른 회로가 그 값을 사용하기 전에 상태가 안정적이지 않으면 데이터의 손상이나 프로그램의 충돌을 야기할 수 있습니다. 특히, 두 개의 다른 논리 경로가 플립플롭의 출력을 사용하는 경우, 하나의 경로는 0으로 해석하고, 다른 하나는 안정적인 상태로 해결되지 않았을 때 1로 해석할 수 있습니다. 기계를 일정하지 않은 상태로 만드는 것.[29]

플립플롭의 준안정성은 데이터와 제어 입력이 각각 설정 시간(tsu)과 유지 시간(th)이라고 불리는 클럭 펄스 전후의 지정된 기간 동안 유효하고 일정하게 유지되도록 보장함으로써 방지할 수 있습니다. 이러한 시간은 장치의 데이터 시트에 명시되어 있으며 일반적으로 현대 장치의 경우 몇 나노초에서 수백 피코초 사이입니다. 플립플롭의 내부 조직에 따라 설정 또는 유지 시간이 0(또는 음)인 장치를 만들 수 있지만 동시에 둘 다는 아닙니다.

불행히도, 플립플롭이 설계자의 제어 밖에서 언제든지 변경될 수 있는 실시간 신호에 연결될 수 있기 때문에 설정 및 유지 기준을 항상 충족할 수 있는 것은 아닙니다. 이 경우 설계자가 할 수 있는 최선의 방법은 회로의 요구되는 신뢰성에 따라 오류 확률을 일정 수준으로 낮추는 것입니다. 준안정성을 억제하기 위한 한 가지 기술은 두 개 이상의 플립플롭을 체인으로 연결하여 각 플립플롭의 출력이 다음 데이터 입력을 공급하고 모든 장치가 공통 클럭을 공유하도록 하는 것입니다. 이 방법을 사용하면 준안정 이벤트의 확률을 무시할 수 있는 값으로 줄일 수 있지만 0으로 줄일 수는 없습니다. 직렬로 연결되는 플립플롭의 수가 증가할수록 준안정성 확률은 점점 0에 가까워집니다. 캐스케이드되는 플립플롭의 수를 "랭킹"이라고 합니다. "듀얼 랭킹" 플립플롭(연속적으로 두 개의 플립플롭)이 일반적인 상황입니다.

설정 및 유지 시간을 최대한 줄여 작동하는 소위 준안정성 강화 플립플롭을 사용할 수 있지만 이마저도 문제를 완전히 제거할 수는 없습니다. 준안정성은 단순히 회로 설계의 문제가 아니기 때문입니다. 시계의 전이와 데이터가 시간에 따라 서로 가까워지면 플립플롭은 어떤 이벤트가 먼저 발생했는지 결정해야 합니다. 장치가 아무리 빨리 만들어지더라도 입력 이벤트가 너무 가까워 어떤 이벤트가 먼저 발생했는지 감지할 수 없을 가능성이 항상 있습니다. 따라서 완벽한 준안정성을 갖는 플립플롭을 구축하는 것은 논리적으로 불가능합니다. 플립플롭은 최대 안착 시간(지정된 조건에서 준안정 상태를 유지할 수 있는 최대 시간) 동안 특성화되기도 합니다. 이 경우 최대 허용 준안정성 시간보다 느리게 클록킹되는 듀얼 랭크 플립플롭은 비동기(예: 외부) 신호에 대한 적절한 컨디셔닝을 제공할 것입니다.

전파지연

플립플롭의 또 다른 중요한 타이밍 값은 클럭 대 출력 지연(데이터 시트의 공통 기호: tCO) 또는 전파 지연(tP)으로, 이는 플립플롭이 클럭 에지 후 출력을 변경하는 데 걸리는 시간입니다. 하이에서 로우로의 전환 시간PHL(t)은 로우에서 하이로의 전환 시간(tPLH)과 다를 수 있습니다.

(시프트 레지스터에서와 같이) 동일한 클럭을 공유하는 플립플롭을 캐스케이드할 때는 이전 플립플롭의 t가CO 다음 플립플롭의 유지 시간(th)보다 더 긴지 확인하는 것이 중요합니다. 따라서 다음 플립플롭의 입력에 존재하는 데이터가 클럭의 활성 에지를 따라 적절하게 "시프트 인"됩니다. 플립플롭이 물리적으로 동일한 경우 t와CO t 사이의h 이러한 관계는 일반적으로 보장됩니다. 또한 올바른 작동을 위해서는 클럭 주기가 합su + t보다h 커야 함을 쉽게 확인할 수 있습니다.

일반화

플립플롭은 적어도 두 가지 방법으로 일반화할 수 있습니다. 즉, 1/2이 아닌 1/N으로 만들고, 두 개 이상의 상태를 가진 논리에 적응시키는 것입니다. 3중 1 인코딩, 또는 다중 값 3차 논리의 특별한 경우들에서, 그러한 요소는 플립-플랩-플롭(flip-flap-flop)으로 지칭될 수 있습니다.[30]

기존의 플립플롭에서는 두 개의 보완 출력 중 하나가 정확히 높습니다. 이는 N개의 출력을 갖는 메모리 요소로 일반화될 수 있으며, 그 중 하나는 정확히 하이(또는 N개 중 하나는 로우)입니다. 따라서 출력은 항상 1-핫(각각 1-콜드) 표현입니다. 이 구조는 기존의 교차 결합 플립플롭과 유사합니다. 각 출력이 높으면 다른 모든 출력을 억제합니다.[31] 또는 출력당 하나씩 다소 기존의 플립플롭을 사용할 수 있으며, 한 번에 하나만 참일 수 있도록 추가 회로를 사용할 수 있습니다.[32]

기존 플립플롭의 또 다른 일반화는 다중 값 로직을 위한 메모리 요소입니다. 이 경우 제어 입력이 변경을 유도할 때까지 메모리 요소는 로직 상태 중 하나를 그대로 유지합니다.[33] 또한, 다중 가치 시계도 사용할 수 있어 새로운 가능한 시계 전환을 유도합니다.[34]

참고 항목

참고문헌

- ^ 예를 들어, Digital Equipment Corporation의 Logic Handfook Flip Chip™ Modules 1969 에디션은 투명 RS 래치를 "R/S Flip Flops"(http://www.bitsavers.org/pdf/dec/handbooks/Digital_Logic_Handbook_1969.pdf 페이지 44)라고 부릅니다.

- ^ Pedroni, Volnei A. (2008). Digital electronics and design with VHDL. Morgan Kaufmann. p. 329. ISBN 978-0-12-374270-4.

- ^ Latch and Flip Flops (E42/100 Berkeley 강의 24) "...때로는 플립플롭과 래치라는 용어가 혼용되기도 합니다.."

- ^ a b Roth, Charles H. Jr. (1995). "Latches and Flip-Flops". Fundamentals of Logic Design (4th ed.). PWS. ISBN 9780534954727.

- ^ GB 148582, Eccles, William Henry & Jordan, Frank Wilfred, "이온 릴레이의 개선", 1920-08-05 출판

- ^ 참조:

- Eccles, W.H.; Jordan, F.W. (19 September 1919). "A trigger relay utilizing three-electrode thermionic vacuum tubes". The Electrician. 83: 298.

- 재인쇄:

- 요약 위치:

- ^ Pugh, Emerson W.; Johnson, Lyle R.; Palmer, John H. (1991). IBM's 360 and early 370 systems. MIT Press. p. 10. ISBN 978-0-262-16123-7.

- ^ Flowers, Thomas H. (1983), "The Design of Colossus", Annals of the History of Computing, 5 (3): 249, doi:10.1109/MAHC.1983.10079, S2CID 39816473

- ^ Gates, Earl D. (2000). Introduction to electronics (4th ed.). Delmar Thomson (Cengage) Learning. p. 299. ISBN 978-0-7668-1698-5.

- ^ Fogiel, Max; Gu, You-Liang (1998). The Electronics problem solver, Volume 1 (revised ed.). Research & Education Assoc. p. 1223. ISBN 978-0-87891-543-9.

- ^ Lindley, P.L. (August 1968). "letter dated June 13, 1968". EDN.

- ^ Phister, Montgomery (1958). Logical Design of Digital Computers. Wiley. p. 128. ISBN 9780608102658.

- ^ US 2850566, 넬슨, 엘드레드 C, "고속 인쇄 시스템" 출판, 1958-09-02, 휴즈 에어크래프트사에 할당.

- ^ Langholz, Gideon; Kandel, Abraham; Mott, Joe L. (1998). Foundations of Digital Logic Design. World Scientific. p. 344. ISBN 978-981-02-3110-1.

- ^ "플립플롭 동작의 유형에 대한 요약". 2018년 4월 16일에 회수되었습니다.

- ^ Hinrichsen, Diederich; Pritchard, Anthony J. (2006). "Example 1.5.6 (R–S latch and J–K latch)". Mathematical Systems Theory I: Modelling, State Space Analysis, Stability and Robustness. Springer. pp. 63–64. ISBN 9783540264101.

- ^ Farhat, Hassan A. (2004). Digital design and computer organization. Vol. 1. CRC Press. p. 274. ISBN 978-0-8493-1191-8.

- ^ a b Kogge, Peter M. (1981). The Architecture of Pipelined Computers. McGraw-Hill. pp. 25–27. ISBN 0-07-035237-2.

- ^ Cotten, L. W. (1965). "Circuit Implementation of High-Speed Pipeline Systems". AFIPS Proc. Fall Joint Computer Conference: 489–504. doi:10.1145/1463891.1463945. S2CID 15955626.

- ^ Earle, John G. (March 1965). "Latched Carry-Save Adder". IBM Technical Disclosure Bulletin. 7 (10): 909–910.

- ^ a b Omondi, Amos R. (1999). The Microarchitecture of Pipelined and Superscalar Computers. Springer. pp. 40–42. ISBN 978-0-7923-8463-2.

- ^ a b Kunkel, Steven R.; Smith, James E. (May 1986). "Optimal Pipelining in Supercomputers". ACM SIGARCH Computer Architecture News. ACM. 14 (2): 404–411 [406]. CiteSeerX 10.1.1.99.2773. doi:10.1145/17356.17403. ISSN 0163-5964. S2CID 2733845.

- ^ "The D Flip-Flop". Archived from the original on 2014-02-23. Retrieved 2016-06-05.

- ^ "Edge-Triggered Flip-flops". Archived from the original on 2013-09-08. Retrieved 2011-12-15.

- ^ 디지털 컴퓨터 메모리 시스템의 실태조사

- ^ SN7474 TI 데이터시트

- ^ a b Mano, M. Morris; Kime, Charles R. (2004). Logic and Computer Design Fundamentals, 3rd Edition. Upper Saddle River, NJ, USA: Pearson Education International. p. 283. ISBN 0-13-191165-1.

- ^ a b Harris, S; Harris, D (2016). Digital Design and Computer Architecture - ARM Edition. Morgan Kaufmann, Waltham, MA. ISBN 978-0-12-800056-4.

- ^ Chaney, Thomas J.; Molnar, Charles E. (April 1973). "Anomalous Behavior of Synchronizer and Arbiter Circuits". IEEE Transactions on Computers. C-22 (4): 421–422. doi:10.1109/T-C.1973.223730. ISSN 0018-9340. S2CID 12594672.

- ^ Often attributed to Don Knuth (1969) (see Midhat J. Gazalé (2000). Number: from Ahmes to Cantor. Princeton University Press. p. 57. ISBN 978-0-691-00515-7.), the term flip-flap-flop actually appeared much earlier in the computing literature, for example, Bowdon, Edward K. (1960). The design and application of a "flip-flap-flop" using tunnel diodes (Master's thesis). University of North Dakota., and in Alexander, W. (Feb 1964). "The ternary computer". Electronics and Power. IET. 10 (2): 36–39. doi:10.1049/ep.1964.0037.

- ^ "Ternary "flip-flap-flop"". Archived from the original on 2009-01-05. Retrieved 2009-10-17.

- ^ US 6975152, Lapidus, Peter D., "원 핫 버스 및 방법에서 글리치리스 작동을 지원하는 플립플롭", 2005-12-13, Advanced Micro Devices Inc.에 할당되었습니다.

- ^ Irving, Thurman A.; Shiva, Sajjan G.; Nagle, H. Troy (March 1976). "Flip-Flops for Multiple-Valued Logic". IEEE Transactions on Computers. C-25 (3): 237–246. doi:10.1109/TC.1976.5009250. S2CID 34323423.

- ^ Wu, Haomin; Zhuang Nan (July 1991). "Research into ternary edge-triggered JKL flip-flop". Journal of Electronics (China). 8 (3): 268–275. doi:10.1007/BF02778378. S2CID 61275953.

외부 링크

- Wayback Machine의 FlipFlop Hierarchy Archive 2015-04-08, 대화형 FlipFlop 회로를 보여줍니다.

- J-K 플립플롭

- Shirriff, Ken (August 2022). "Reverse-engineering a 1960s hybrid flip flop module with X-ray CT scans".