인버터(로직 게이트)

Inverter (logic gate)| 입력 | 산출량 |

| A | A가 아니다 |

| 0 | 1 |

| 1 | 0 |

디지털 로직에서 인버터 또는 NOT 게이트는 논리 부정을 구현하는 논리 게이트입니다.수리논리에서는 논리부정연산자(¬)와 같다.진실 표가 오른쪽에 표시됩니다.

전자 도입

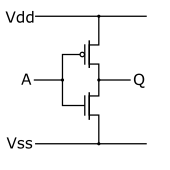

인버터회로는 그 입력에 대해 반대논리레벨을 나타내는 전압을 출력한다.주요 기능은 적용된 입력 신호를 반전시키는 것입니다.적용된 입력이 낮으면 출력이 높아지며 그 반대도 마찬가지입니다.인버터는 단일 NMOS 트랜지스터 또는 저항기와 결합된 단일 PMOS 트랜지스터를 사용하여 구성할 수 있습니다.이 '저항 드레인' 방식은 단일 유형의 트랜지스터만 사용하기 때문에 저렴한 비용으로 제작할 수 있습니다.단, 전류는 2가지 상태 중 하나로 저항을 통과하기 때문에 저항 드레인 구성은 소비 전력과 처리 속도에 불리합니다.또는 CMOS 구성의 2개의 상보 트랜지스터를 사용하여 인버터를 구성할 수 있다.이 구성은 두 [1]로직 상태 모두에서 트랜지스터 중 하나가 항상 꺼지기 때문에 전력 소비를 크게 줄입니다.또한 NMOS 전용 또는 PMOS 전용 장치에 비해 저항이 상대적으로 낮기 때문에 처리 속도가 향상될 수 있습니다.인버터는 저항-트랜지스터 로직(RTL) 또는 트랜지스터-트랜지스터 로직(TTL) 구성으로 양극 접합 트랜지스터(BJT)를 사용하여 구성할 수도 있습니다.

디지털 전자 회로는 논리 0 또는 1에 해당하는 고정 전압 레벨에서 작동합니다(이진 참조).인버터 회로는 이들 2개의 전압레벨을 교환하기 위한 기본 로직게이트 역할을 한다.실장에 따라 실제 전압이 결정되지만 TTL 회선의 공통 레벨에는 (0, +5V)가 포함됩니다.

NMOS 논리 인버터

PMOS 논리 인버터

정적 CMOS 로직 인버터

NPN 저항 트랜지스터 로직 인버터

NPN 트랜지스터-트랜지스터 로직 인버터

디지털 빌딩 블록

인버터는 디지털 전자제품의 기본 구성 요소입니다.멀티플렉서, 디코더, 스테이트 머신 및 기타 고도의 디지털 디바이스에서는 인버터를 사용할 수 있습니다.

육각 인버터는 6개의 인버터를 포함하는 집적회로입니다.예를 들어 14핀을 가진 7404 TTL 칩과 16핀을 가진 4049 CMOS 칩(이 중 2핀은 전원/기준에 사용되며 12핀은 6개의 인버터(4049는 2핀이 접속되지 않음)의 입출력에 의해 사용됩니다.

해석적 표현

( - { f)=는 NOT 게이트의 해석 표현입니다.

대체 수단

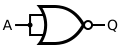

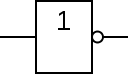

특정 NOT 게이트를 사용할 수 없는 경우 범용 NAND 또는 NOR [2]게이트로 만들 수 있습니다.

| 원하는 게이트 | NAND 구조 | NOR 구조 |

|---|---|---|

|  |  |

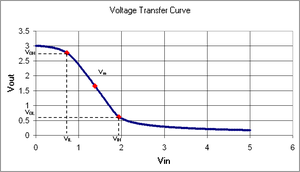

퍼포먼스 측정

디지털 인버터 품질은 종종 전압전송곡선(VTC)을 사용하여 측정됩니다.VTC는 출력 대 입력전압의 그래프입니다.이러한 그래프로부터 노이즈 톨러런스, 게인 및 동작 로직 레벨을 포함한 디바이스 파라미터를 얻을 수 있다.

이상적으로는 VTC는 반전 스텝 기능으로 나타나며, 이는 온/오프를 정확하게 전환할 수 있음을 나타냅니다.그러나 실제 디바이스에서는 점진적인 이행 영역이 존재합니다.VTC는 낮은 입력 전압의 경우 회로가 고전압을 출력하고, 높은 입력의 경우 출력이 낮은 레벨로 테이퍼링됨을 나타냅니다.이 전이 영역의 기울기는 품질의 척도입니다. 급경사(무한에 가까운)는 정밀한 스위칭을 산출합니다.

노이즈에 대한 허용 오차는 각 작동 영역에 대한 최소 입력과 최대 출력을 비교하여 측정할 수 있습니다(ON/OFF).

「 」를 참조해 주세요.

레퍼런스

- ^ Nair, B. Somanathan (2002). Digital electronics and logic design. PHI Learning Pvt. Ltd. p. 240. ISBN 9788120319561.

- ^ M. Morris, Mano; R. Kime, Charles (2004). Logic and computer design fundamentals (3 ed.). Prentice Hall. p. 73. ISBN 0133760634.

NOT 게이트의 해석 표현입니다.

NOT 게이트의 해석 표현입니다.