NAND 게이트

NAND gate| 입력 | 산출량 | |

| A | B | A NAND B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

디지털 전자제품에서 NAND 게이트(NOT-AND)는 모든 입력이 참일 경우에만 거짓 출력을 생성하는 논리 게이트입니다. 따라서 출력은 AND 게이트의 출력을 보완합니다.LOW(0) 출력은 게이트에 대한 모든 입력이 HIGH(1)인 경우에만 생성되며, LOW(0) 입력이 있으면 HIGH(1) 출력이 생성됩니다.NAND 게이트는 트랜지스터 및 접합 다이오드를 사용하여 만들어진다.De Morgan의 법칙에 따르면, 2입력 NAND 게이트의 논리는 A • B=A+B로 표현될 수 있으며, NAND 게이트는 인버터에 상당하며, 그 뒤에 OR 게이트가 뒤따른다.

NAND 게이트는 NAND 게이트의 조합을 사용하여 부울 함수를 구현할 수 있기 때문에 중요합니다.이 속성을 기능 완전성이라고 합니다.NOR 게이트와 이 속성을 공유합니다.특정 논리회로를 사용하는 디지털 시스템은 낸드의 기능적 완성도를 활용합니다.

NAND(a1, a2, ..., an) 함수는 논리적으로 NOT(a1 AND2 AND...)와 동등합니다. An)

NAND B를 표현하는 한 가지 방법은 A B B 여기서 기호는 AND를 나타내고, 바(\displaystyle {\land})는AND를 나타내고 바(\는 AND B를 나타냅니다.

2개 이상의 입력을 가진 NAND 게이트는 트랜지스터-트랜지스터 로직, CMOS 및 기타 로직 패밀리의 집적회로로 사용할 수 있습니다.

기호

NAND 게이트에는 MIL/ANSI 기호, IEC 기호 및 사용되지 않는 DIN 기호의 세 가지 기호가 있습니다.자세한 내용은 로직 게이트 기호를 참조하십시오.NAND 게이트의 ANSI 기호는 반전 버블이 연결된 표준 AND 게이트입니다.

|  |  |

| MIL/ANSI 기호 | IEC 기호 | DIN 기호 |

하드웨어 설명 및 핀 배치

NAND 게이트는 기본적인 논리 게이트이며, TTL 및 CMOS IC에서 인식됩니다.

CMOS 버전

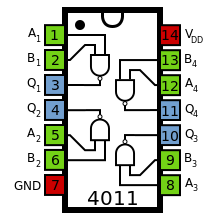

표준 4000 시리즈 CMOS IC는 4011로, 4개의 독립된 2 입력 NAND 게이트를 포함합니다.

유용성

이들 소자는 페어차일드 반도체, 필립스, 텍사스 인스트루먼트 등 대부분의 반도체 제조사에서 구입할 수 있다.일반적으로 스루홀 DIL과 SOIC 형식으로 제공됩니다.데이터시트는 대부분의 데이터시트 데이터베이스에서 쉽게 사용할 수 있습니다.

표준 2-, 3-, 4- 및 8 입력 NAND 게이트를 사용할 수 있습니다.

- CMOS

- 4011: 쿼드2 입력 NAND 게이트

- 4023: 트리플 3입력 NAND 게이트

- 4012: 듀얼 4입력 NAND 게이트

- 4068: 모노8 입력 NAND 게이트

- TTL

- 7400: 쿼드2 입력 NAND 게이트

- 7410: 트리플 3입력 NAND 게이트

- 7420: 듀얼 4입력 NAND 게이트

- 7430: 모노8 입력 NAND 게이트

실장

NMOS NAND 게이트 |  PMOS NAND 게이트 |  CMOS NAND 게이트 |  TTL NAND 게이트 |

CMOS NAND의 물리적 레이아웃 |

기능의 완전성

NAND 게이트는 NOR 게이트와 공유되는 기능적 완전성의 특성을 가지고 있습니다.즉, NAND 게이트만을 사용하여 다른 논리 함수(AND, OR [1]등)를 구현할 수 있습니다.NAND 게이트만으로 프로세서 전체를 만들 수 있습니다.다중 이미터 트랜지스터를 사용하는 TTL IC에서는 NOR 게이트보다 필요한 트랜지스터 수도 적습니다.

NOR 게이트도 기능적으로 완전하기 때문에 특정 NAND 게이트가 없을 경우 NOR [1]논리로 NOR 게이트를 만들 수 있다.

| 원하는 게이트 | NOR 건설 |

|---|---|

|  |

AND B를 나타냅니다.

AND B를 나타냅니다.