MOS 테크놀로지 6502

MOS Technology 6502 | |

| 일반 정보 | |

|---|---|

| 개시. | 전 ( |

| 공통 제조원 | |

| 성능 | |

| 최대 CPU 클럭 속도 | 1MHz~3MHz |

| 데이터 폭 | 8 |

| 주소 폭 | 16 |

| 아키텍처 및 분류 | |

| 명령 집합 | MOS 6502 |

| 지침들 | 56 |

| 물리 사양 | |

| 트랜지스터 | |

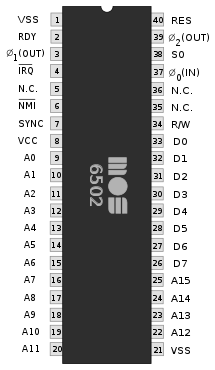

| 패키지 |

|

| 역사 | |

| 전임자 |

|

| 후계자 | |

MOS 테크놀로지 6502(일반적으로 '6xty-5-o-2' 또는 '6-5-o-2'[3]로 발음)는 MOS 테크놀로지 담당 Chuck Peddle이 이끄는 소규모 팀이 설계한 8비트 마이크로프로세서입니다.디자인 팀은 이전에 Motorola 6800 프로젝트에서 Motorola에서 일한 적이 있습니다. 6502는 기본적으로 그 디자인의 단순하고 저렴한 고속 버전입니다.

1975년 출시 당시 6502는 시장에서 가장 저렴한 마이크로프로세서였습니다.당초 6800이나 인텔 8080 등 대기업의 경쟁사 설계보다 6분의 1도 안 되는 가격에 판매되었습니다.그 도입으로 프로세서 시장 전체에서 가격이 급격히 하락했습니다.Zilog Z80과 함께 1980년대 초반 가정용 컴퓨터 혁명을 일으킨 일련의 프로젝트를 촉발시켰다.

아타리 2600, 아타리 8비트 패밀리, 애플 II, 닌텐도 엔터테인먼트 시스템, 코모도어 64, 아타리 링스, BBC 마이크로 등과 같은 인기 있는 비디오 게임 콘솔과 컴퓨터들은 6502 또는 기본 디자인의 변형을 사용합니다.6502가 출시된 직후, MOS Technology는 Commodore International에 의해 완전히 매입되었고, Commodore International은 마이크로프로세서와 라이선스를 다른 제조업체에 계속 판매했습니다.6502년 초기에는 Rockwell과 Synertek에 의해 세컨드 소싱되었으며, 이후 다른 회사에도 라이선스되었습니다.

1981년, 웨스턴 디자인 센터는 CMOS 버전인 65C02의 개발을 시작했습니다.이는 임베디드 시스템에서 계속 널리 사용되고 있으며, 생산량은 수억 [4]개에 달할 것으로 예상됩니다.

이력 및 사용방법

Motorola에서 시작

6502는 Motorola 6800 마이크로프로세서 [5]패밀리를 설계한 많은 엔지니어들에 의해 설계되었습니다.모토로라는 1971년 톰 베넷을 주 설계자로 하여 6800 마이크로프로세서 프로젝트를 시작했습니다.칩 레이아웃은 1972년 말에 시작되었고, 최초의 6800 칩은 1974년 2월에 제작되었으며, 1974년 [6][7]11월에 정식 출시되었습니다.존 뷰캐넌은 6800[8][9] 칩의 설계자였고, 로드 오르길은 나중에 6501을 설계하여 뷰캐넌의 회로 분석과 칩 레이아웃을 지원했습니다.[10]빌 멘슈는 애리조나 대학교 졸업(26세)[11] 후 1971년 6월 모토로라에 입사했다.그의 첫 번째 임무는 6800 패밀리의 주변기기의 IC를 정의하는 것이었습니다.이후 6820 주변기기의 인터페이스 어댑터(PIA)[12]의 수석 설계자가 되었습니다.Motorola의 엔지니어들은 IBM 370-165 메인프레임 [13]컴퓨터에서 아날로그 및 디지털 시뮬레이션을 실행할 수 있었습니다.Bennett은 1973년에 Chuck Peddle을 고용하여 이미 [14]진행 중인 6800개의 패밀리 제품에 대한 건축 지원 작업을 수행했습니다.6850 ACIA(시리얼 인터페이스)[15]의 설계 등, 많은 분야에 공헌했습니다.

모토로라의 타깃 고객은 휴렛패커드, 테크트로닉스, TRW,[16] 크라이슬러 등 기존 전자업체였다.1972년 5월, Motorola의 엔지니어들은 엄선된 고객들을 방문하여 ROM, RAM, 병렬 및 시리얼 인터페이스를 [17]갖춘 제안된 8비트 마이크로프로세서 시스템의 세부 사항을 공유하기 시작했습니다.1974년 초, 그들은 고객들이 디자인을 프로토타입으로 만들 수 있도록 칩의 엔지니어링 샘플을 제공했습니다.모토로라의 "토탈 프로덕트 패밀리" 전략은 마이크로프로세서의 가격이 아니라 고객의 총 설계 비용을 절감하는 데 초점을 맞췄다.그들은 타임셰어 컴퓨터 개발 소프트웨어, "엑소시저" 디버깅 시스템, 현장 교육 및 현장 애플리케이션 엔지니어 [18][19]지원을 제공했습니다.인텔과 모토로라는 마이크로프로세서 [20][21]하나에 360달러라는 가격을 발표했다.실제 생산 수량의 가격은 훨씬 낮았다.모토로라는 6800과 6개의 지원 칩이 포함된 디자인 키트를 [22]300달러에 내놓았다.

Peddle은 고객 방문에 영업 사원과 동행하여 고객이 마이크로프로세서 [23]칩의 고비용에 당황하고 있음을 알게 되었습니다.동시에, 이러한 방문으로 인해 그는 6800에 [24]포함된 "이 모든 화려한 지시"보다 훨씬 작은 필수 지시 목록을 작성하게 되었습니다.Peddle과 다른 팀원들은 개선된 기능, 축소된 크기의 마이크로프로세서의 설계에 대해 설명하기 시작했습니다.당시 텍사스주 오스틴에 있는 모토로라의 새로운 반도체 제조 공장은 MOS 칩 생산에 어려움을 겪고 있었으며, 1974년 중반은 반도체 산업의 1년 동안의 불황의 시작이었다.또한 많은 애리조나 메사 직원들은 곧 텍사스 [25]오스틴으로 이전하는 것에 대해 불쾌해 했습니다.

모토로라의 반도체 제품 부문 경영진은 문제투성이였고 페들의 저가 마이크로프로세서 제안에는 전혀 관심을 보이지 않았다.결국 페들은 그에게 시스템 작업을 중단하라는 [26]공문을 받았다.페들은 모토로라에게 이 서한은 "프로젝트 포기"의 공식 선언을 의미하며, 그에 따라 그가 지금까지 개발한 지적재산은 현재 그의 [27]것이 되었다고 말했다.1975년 11월 인터뷰에서 모토로라의 로버트 갤빈 회장은 결국 페들의 컨셉이 훌륭했고 사업부가 기회를 놓쳤다고 동의했습니다. "우리는 반도체 제품 부문에서 적절한 리더를 선택하지 않았습니다."부서가 재편성되고 경영진이 교체되었다.존 웰티 신임 그룹 부사장은 반도체 판매 조직이 고객 요구에 대한 민감성을 잃고 신속한 [28]결정을 내리지 못했다고 말했다.

MOS 테크놀로지

Peddle은 이 새로운 프로젝트를 위한 자금원을 모토로라 외부에서 찾기 시작했습니다.그는 처음에 Mostek CEO L. J. Sevin과 접촉했지만 거절했습니다.세빈은 나중에 이것이 모토로라가 그들을 [29]고소할까 봐 두려워서라고 인정했다.

Peddle이 판매차 포드 자동차 회사를 방문했을 때, 후에 Ford의 엔진 자동화 부문 책임자인 Bob Johnson은 그들의 전 동료 John Paivinen이 제너럴 인스트루먼트로 옮겨져 반도체 [30]설계를 독학했다고 언급했다.Paivinen은 1969년 General Instrument의 다른 임원 Mort Jaffe와 Don McLaughlin과 함께 펜실베니아 밸리 포지에 MOS Technology를 설립했습니다.전자 부품 및 산업 제어 공급업체인 Allen-Bradley는 1970년에 [31]과반수의 지분을 취득했습니다.이 회사는 고객을 위한 맞춤 IC를 설계하고 제작했으며 계산기 [32]칩 라인을 개발했습니다.

모스텍의 노력이 수포로 돌아간 후, 페들은 페이비넨에게 접근했고, 페이비넨은 "즉각 이해했다"[33]고 말했다.1974년 8월 19일 척 페들, 빌 멘쉬, 로드 오길, 해리 바우콤, 레이 하르트, 테리 홀트, 윌 매티스가 모토로라를 떠나 모토로라에 합류했다.마이크 제인은 나중에 합류했다.6800팀의 17명의 칩 설계자와 레이아웃 담당자 중 8명이 남았습니다.팀의 목표는 임베디드 애플리케이션용 저비용 마이크로프로세서를 설계 및 생산하고 가능한 한 폭넓은 고객층을 공략하는 것이었습니다.이것은 마이크로프로세서가 저비용이고,[34] 팀이 대량으로 가격 목표를 5달러로 설정한 경우에만 가능할 것이다.Mensch는 나중에 프로세서 가격 자체가 아니라 비슷한 완전한 [35]칩셋으로 29달러에 팔린 최근 출시된 인텔 4040과 경쟁하기 위해 20달러에 팔릴 수 있는 칩 세트를 만드는 것이 목표라고 밝혔다.

칩은 순도가 높은 실리콘의 얇은 디스크인 "웨이퍼" 표면에 칩 설계의 여러 복사본을 인쇄하여 생산됩니다.크기가 작은 칩은 같은 웨이퍼에 더 많은 수의 인쇄가 가능하기 때문에 상대적으로 가격이 낮아집니다.또한 웨이퍼에는 항상 표면에 흩어져 있는 몇 가지 미세한 물리적 결함이 포함됩니다.그 위치에 인쇄된 칩은 모두 고장나 폐기해야 합니다.칩이 작을수록 단일 복사본이 결함에 인쇄될 가능성이 낮아집니다.이 두 가지 이유로 최종 제품의 비용은 칩 [36]설계의 크기에 크게 좌우됩니다.

원래 6800 칩은 1억8000만 x 1억8000만[a] x 4.6mm로 설계되었지만 레이아웃은 212만 x 212만 x 5.4mm 또는 29.0mm의2 [37]면적에 완료되었습니다.새로운 설계의 경우, 비용 목표는 153 mils × 168 mils(3.9 mm × 4.3 mm) 또는 16.6 [38]mm의2 면적을 필요로 했다.이 목표를 달성하려면 몇 가지 새로운 기술이 필요할 것이다.

NMOS로의 이행

6502가 설계되었을 때 시장에 두 가지 중요한 진보를 통해 비용을 대폭 절감할 수 있었습니다.첫 번째는 고갈 부하 NMOS로의 이행이었습니다.6800은 3개의 전원 전압을 필요로 하는 초기 NMOS 프로세스를 사용했지만 칩의 기능 중 하나는 +5, -5, +12 V에 대해 단일 +5 V 전원을 내부적으로 사용할 수 있는 온보드 전압 더블러였습니다.이는 인텔 8080과 같은 시대의 다른 칩이 3개의 전원 [39]핀을 필요로 하는 것과는 다릅니다.이 기능은 전원장치와 핀 레이아웃의 복잡성을 줄였지만 칩의 다양한 게이트에 별도의 파워 레일이 필요했기 때문에 복잡성과 크기가 증가했습니다.새로운 고갈 부하 설계로 전환하면 +5V 전원 하나만 공급하면 되므로 이러한 [40]복잡성이 모두 해소됩니다.

더 실용적인 장점은 이전 CPU의 클럭 신호가 회로를 통과할 때 발생하는 모든 소산에도 충분히 견딜 수 있을 정도로 강해야 한다는 것입니다.이 때문에 강력한 신호를 공급할 수 있는 별도의 외부 칩이 거의 항상 필요했습니다.NMOS의 전력 요건이 줄어들면 클럭을 칩 위로 이동시켜 전체적인 컴퓨터 설계를 단순화할 수 있습니다.이러한 변경으로 복잡성이 대폭 감소하고 전체 시스템 [40]구현 비용이 대폭 절감되었습니다.

또 다른 변화는 프로젝션 마스킹의 도입이었습니다.기존에는 웨이퍼 표면에 마스크를 씌운 후 밝은 빛을 비추는 방식으로 웨이퍼 표면에 칩을 무늬화했다.마스크는 칩에서 꺼낼 때 종종 작은 먼지 조각이나 포토 레지스트(사진 저항)를 주워 다음 마스킹 시 그 위치에 흠집을 냈다.CPU와 같은 복잡한 설계에서는 5단계 또는 6단계 마스킹 단계가 사용되며, 이들 단계 중 적어도 1단계에서 결함이 발생할 가능성은 매우 높았다.대부분의 경우 이러한 설계 중 90%가 결함이 있어 10%의 수율을 달성했습니다.작업 예제의 가격은 [41]폐기된 90%의 생산 비용을 충당해야 했습니다.

1973년 Perkin-Elmer는 직접 접촉할 필요 없이 마스크의 이미지를 웨이퍼에 투영하는 Micralign 시스템을 도입했습니다.마스크는 더 이상 웨이퍼의 먼지를 제거하지 않고 10회 사용에서 10회 사용으로 지속되었습니다.이를 통해 단계별 실패와 복잡한 설계에서 이전에 볼 수 있었던 높은 결함률을 제거할 수 있었습니다.CPU의 수율은 10%에서 60% 또는 70%로 즉시 상승했습니다.이것은 CPU의 가격이 거의 같은 양으로 하락하고 마이크로프로세서가 갑자기 상용 [41]장치가 되었다는 것을 의미합니다.

MOS 테크놀로지의 기존 제조 라인은 구식 PMOS 기술을 기반으로 하고 있으며, 팀이 도착했을 때 NMOS와의 작업을 아직 시작하지 않았습니다.Paivinen은 새로운 CPU 생산을 시작하기 위해 NMOS를 제때에 라인업하여 가동시키기로 약속했습니다.그는 1975년 [42]6월까지 새로운 라인이 준비되었다는 약속을 이행했다.

설계 노트

Chuck Peddle, Rod Orgill 및 Wil Mathys가 새로운 프로세서의 초기 아키텍처를 설계했습니다.1975년 9월 EDN 매거진의 기사에는 다음과 같은 설계의 [43]개요가 기재되어 있습니다.

MOS Technology 650X 패밀리는 6800 시스템 개발에 참여한 8명의 전직 Motorola 직원이 6800을 대체하고 성능을 능가하는 부품을 내놓으면서도 판매량을 낮추기 위해 의도적으로 시도한 것입니다.6800프로젝트에서 얻은 후견으로 Chuck Peddle이 이끄는 MOS Technology 팀은 Motorola CPU에 다음과 같은 아키텍처 변경을 가했습니다.

칩 사이즈에 관한 주요 변경은 어드레스 버스 출력에서 트라이스테이트 드라이버가 삭제되었다는 것입니다.이것은 6800에 포함되어 있어 다이 스페이스의 대폭적인 비용을 들여 다이렉트 메모리 액세스(DMA) 및 코프로세싱 역할의 다른 칩과 연동할 수 있었습니다.실제로 이러한 시스템을 사용하려면 다른 장치도 마찬가지로 복잡해야 했고, 설계자들은 오프칩 시스템을 사용하여 이러한 액세스를 조정하는 경향이 있었습니다.6502는 특정 태스크에 사용되는 저렴한 컨트롤러로서 심플한 디바이스와 통신하는 설계에 따라 이 기능을 삭제했습니다.Peddle은 이러한 접근 방식을 실제로 필요로 하는 사람은 74158 하나로 [44][b]구현할 수 있다고 제안했습니다.

그 다음으로 큰 차이는 레지스터를 단순화하는 것이었습니다.우선 축전지 두 개 중 하나를 제거했습니다.축전기와 같은 범용 레지스터는 명령 디코더의 많은 부분에서 액세스해야 하므로 데이터를 저장소로 이동하거나 저장소에서 이동하려면 상당한 양의 배선이 필요합니다.축전지 2개를 사용하면 많은 코딩 작업이 쉬워지지만 칩 설계 자체가 상당히 [43]복잡해집니다.또한 스택 레지스터를 16비트에서8비트로 줄임으로써 스택의 길이는 256바이트로 마이크로컨트롤러로서의 역할에 충분했습니다.[43]

16비트 IX 인덱스 레지스터는 2개로 분할되어 X와 Y가 되었습니다.더 중요한 것은 접근 방식이 바뀌었다는 것입니다. 6800에서는 IX가 16비트 주소를 유지했지만 명령과 함께 제공된 8비트 번호로 상쇄되어 두 개의 주소가 추가되어 최종 주소가 생성되었습니다.6502(및 기타 대부분의 설계)에서는 명령어에 16비트 베이스 주소가 저장되어 있으며,[44] 여기에 X 또는 Y가 추가되어 있습니다.

마지막으로 명령 세트가 간소화되어 디코더 및 제어 로직의 공간이 확보되었습니다.6800의 원래 72개의 명령 중 56개가 남아 있었다.제거된 명령어 중에는 6800의 두 어큐뮬레이터 간에 데이터를 이동하는 명령어와 PDP-11에서 영감을 받은 여러 분기 명령어(두 수치 값을 직접 비교하는 기능 등)가 포함되어 있습니다.6502는 축전지에 대해 계산을 수행한 다음 [44]결과 플래그를 검사하여 비교를 처리하는 더 단순한 시스템을 사용했습니다.

칩의 고급 디자인은 트랜지스터와 인터커넥트의 도면으로 바뀌어야 했다.MOS Technology에서 "레이아웃"은 색연필과 벨룸 페이퍼로 이루어지는 매우 수동적인 프로세스였습니다.레이아웃은 제작 프로세스의 각 레이어당 하나씩, 6개의 서로 다른 도면에 있는 수천 개의 폴리곤 도형으로 구성되었습니다.크기 제한을 고려할 때 칩 설계 전체를 항상 고려해야 했습니다.Mensch와 Paivinen은 명령[46] 디코더 작업을 했고 Mensch, Peddle, Orgill은 ALU와 레지스터 작업을 했다.ALU의 크기를 [47]줄일 수 있도록 내부 배선의 일부를 공유하는 방법으로, 당사자가 개발한 추가 진전은 ALU의 크기를 줄일 수 있도록 하는 것이었습니다.

그들의 최선의 노력에도 불구하고, 최종 디자인은 5백만 개의 [48]폭이 너무 넓어졌습니다.최초의 6502 칩은 168 × 183 밀(4.3 × 4.7 mm) 또는 19.8 mm2 면적이었습니다.ROR(Rotate Right Instruction)는 첫 번째 실리콘에서는 작동하지 않았기 때문에 발행된 문서에서는 일시적으로 명령이 누락되었지만, 다음 번 설계의 반복으로 칩이 축소되어 Rotate Right 명령이 수정되어 수정된 [49]문서에 포함되었습니다.

6501 및 6502 소개

MOS는 동일한 기본 설계에 기반한 두 개의 마이크로프로세서를 도입할 것입니다. 6501은 Motorola 6800과 동일한 소켓에 연결되고 6502는 핀 배치를 조정하여 온칩 클럭 오실레이터를 지원합니다.둘 다 6800용으로 설계된 다른 지원 칩과 함께 작동합니다.명령 집합이 다르고 레지스터가 다르고 [50]어드레싱 모드가 대부분 다르기 때문에 6800 소프트웨어는 실행되지 않습니다.Rod Orgill은 6501 설계를 담당했습니다.그는 6800에서 Motorola의 John Buchanan을 지원했습니다.Bill Mensch는 Motorola에서 6820 Peripheral Interface Adapter(PIA; 페리페럴 인터페이스 어댑터)를 설계한 6502를 만들었습니다.Harry Bawcom, Mike Janes, Sydney-Anne Holt가 레이아웃을 도왔습니다.

MOS Technology의 마이크로프로세서 도입은 수개월에 걸친 기존의 제품 출시와는 달랐다.새로운 집적회로의 첫 번째 동작은 일반적으로 내부 테스트에 사용되며 엄선된 고객과 "엔지니어링 샘플"로 공유됩니다.이들 칩에는 종종 사소한 설계 결함이 한두 개 있으며, 생산 시작 전에 수정될 것입니다.Chuck Peddle의 목표는 1975년 9월 16일부터 샌프란시스코에서 열리는 Wescon 무역 박람회에서 처음으로 6501과 6502 칩을 참가자들에게 판매하는 것이었습니다.Peddle은 매우 효과적인 대변자였으며, MOS Technology 마이크로프로세서는 업계 언론에서 광범위하게 다루어졌습니다.가장 초기의 것 중 하나는 1975년 7월 24일자 Electronics [51]매거진에서 MCS6501 및 MCS6502 마이크로프로세서에 관한 전면 기사입니다.EE 타임즈(1975년 [52]8월 24일), EDN(1975년 9월 20일), 일렉트로닉 뉴스(1975년 11월 3일), 바이트(1975년 [53]11월), 마이크로컴퓨터 다이제스트(1975년 [54]11월)에도 기사가 실렸다.6501에 대한 광고는 1975년 8월 첫째 주에 여러 출판물에 실렸다.6501은 웨스콘에서 [55]개당 20달러에 판매될 것이다.1975년 9월 광고에는 6501 마이크로프로세서와 6502 마이크로프로세서가 모두 포함되었습니다.6502는 단돈 25달러(2021년 [56]126달러 상당)이다.

MOS Technology가 Wescon에 도착했을 때, 그들은 전시장에서 전시자들이 어떤 것도 팔 수 없다는 것을 알았다.그들은 세인트루이스에서 맥아더 스위트를 빌렸다. Francis Hotel에서 고객에게 프로세서를 구매하도록 안내했습니다.스위트에서는, 프로세서가 큰 병에 보존되어 있어, 칩이 실가동중이며, 곧바로 입수할 수 있는 것을 나타내고 있습니다.고객들은 각 병의 하단 절반에 기능하지 않는 [57]칩이 들어 있다는 것을 알지 못했다.칩은 20달러와 25달러였고 서류 패키지는 10달러였습니다.사용자들은 MOS Technology가 제품 정보를 배포하기 위한 저렴한 방법인 문서의 복사본을 만들도록 권장받았습니다.예비 데이터 시트에는 이 초기 칩에서 제대로 작동하지 않는 ROR(Rotate Right) 명령을 제외하고 55개의 명령만 나와 있습니다.바이트와 EDN의 리뷰는 ROR 명령의 부족을 지적했다.레이아웃의 다음 개정에서는 이 문제를 수정하고 1976년 5월 데이터 시트에는 56가지 지침이 기재되어 있습니다.Peddle은 관심 있는 엔지니어 및 취미 생활자가 모두 칩과 문서에 액세스할 수 있기를 원했지만, 다른 반도체 회사들은 "진지한" 고객만을 상대하기를 원했습니다.예를 들어, 시그네틱스는 2650 마이크로프로세서를 선보였고, 그 광고는 독자들에게 회사 [58]레터헤드에 정보를 쓰도록 요구했습니다.

| 핀 | 6800 | 6501 | 6502 |

|---|---|---|---|

| 2 | 정지 | 준비가 되어 있습니다! | 준비가 되어 있습니다! |

| 3 | 1 1 (in) | 1 1 (in) | 1 1 (출력) |

| 5 | 유효한 메모리 주소 | 유효한 메모리 주소 | N.C. |

| 7 | 버스 이용 가능 | 버스 이용 가능 | 동기 |

| 36 | 데이터 버스 활성화 | 데이터 버스 활성화 | N.C. |

| 37 | 22 (in) | 22 (in) | 0파운드 (in) |

| 38 | N.C. | N.C. | 오버플로 플래그 설정 |

| 39 | 3스테이트 컨트롤 | N.C. | 22 (출력) |

모토로라 소송

6501/6502는 인쇄 및 Wescon에서 큰 성공을 거두었습니다.단점은 광범위한 언론 보도가 모토로라의 관심을 끌었다는 것이다.1975년 10월 모토로라는 6800 마이크로프로세서 한 대 가격을 175달러에서 69달러로 인하했다.300달러짜리 시스템 설계 키트는 150달러로 줄었고, 현재는 프린트 [59]기판과 함께 제공되고 있습니다.1975년 11월 3일 Motorola는 연방법원에 MOS Technology의 마이크로프로세서 제품 제조 및 판매를 중지하라는 가처분 신청을 냈다.특허 침해 및 영업비밀 유용 청구소송도 제기했다.모토로라는 7명의 전직 직원들이 MOS 테크놀로지에 입사하여 회사의 마이크로프로세서 [60]제품을 만들었다고 주장했다.

모토로라는 그럴듯한 사례와 변호사를 가진 수십억 달러 규모의 회사였다.1974년 10월 30일, Motorola는 마이크로프로세서 패밀리에 대해 수많은 특허를 출원하여 25개의 특허를 부여받았다.첫 번째는 1976년 6월에 있었고, 두 번째는 1976년 7월 6일에 6820 PIA 칩 레이아웃을 위한 Bill Mensch에 대한 것이었습니다.이들 특허는 6800버스와 주변기기의 칩이 마이크로프로세서와 [61]어떻게 접촉하는지를 대상으로 하고 있습니다.모토로라는 1950년에 트랜지스터를 만들기 시작했고 반도체 특허 포트폴리오를 가지고 있었다.Allen-Bradley는 이 소송에 맞서지 않기로 결심하고 MOS Technology에 대한 그들의 관심을 설립자들에게 되팔았다.전 모토로라 엔지니어 중 4명이 소송에서 이름을 올렸다.척 페들, 윌 매티스, 빌 멘쉬, 로드 오길.이들은 모두 6800개의 특허출원에서 발명가로 이름을 올렸다.발견 과정에서 Motorola는 Mike Janes라는 엔지니어가 Peddle의 지시를 무시하고 6800개의 [62]설계 문서를 MOS Technology에 가져간 것을 발견했습니다.1976년 3월, 현재 독립한 MOS Technology는 자금이 바닥나 사건을 해결해야 했다.그들은 6501 프로세서를 폐기하고, 모토로라에게 20만 달러를 지불하고, 모토로라가 기밀이라고 주장한 문서를 반환하기로 합의했다.양사는 마이크로프로세서 [63]특허를 크로스 라이선스하기로 합의했다.그 해 5월 모토로라는 6800 마이크로프로세서 한 대 가격을 35달러로 내렸다.11월에 코모도어는 MOS [64][65]테크놀로지를 인수했다.

컴퓨터와 게임

MOS는 법적인 문제를 뒤로 한 채 개발자들에게 프로세서를 시험하게 하는 문제를 남겨두고 척 페들(Chuck Peddle)이 MDT-650 ('마이크로컴퓨터 개발단말기') 싱글보드 컴퓨터를 설계하도록 촉구했습니다.회사 내부의 또 다른 그룹은 KIM-1을 설계했는데, KIM-1은 반완전 판매되었으며 타사 컴퓨터 단자와 소형 카세트 드라이브를 추가하여 사용 가능한 시스템으로 전환될 수 있었다.놀랍게도 KIM-1은 애호가들과 양철업자들뿐만 아니라 목표물이었던 기술자들에게도 잘 팔렸다.관련된 Rockwell AIM 65 제어/훈련/개발 시스템도 잘 수행되었습니다.AIM 65의 소프트웨어는 MDT의 소프트웨어를 기반으로 했습니다.또 다른 거의 유사한 제품은 Synertek SYM-1이었습니다.

이 디자인의 첫 번째 "공용" 용도 중 하나는 1976년에 도입된 애플 I 마이크로컴퓨터였다.6502는 1977년에 출시된 코모도어 PET와 애플 [66]II에 사용되었다.나중에 아타리 8비트 패밀리와 아콘 아톰 가정용 컴퓨터, BBC 마이크로,[66] 코모도어 VIC-20 및 오하이오 사이언티픽과 오릭과 같은 가정용 컴퓨터 및 비즈니스용 디자인에 사용되었습니다.6510은 디지털 I/O 포트와 3스테이트 주소 버스를 갖춘 6502의 직접 후계 기종으로 가장 많이[67][68] 팔린 코모도어 64 가정용 컴퓨터에 사용된 CPU입니다.6502 또는 6502의 다양한 CPU가 PET 라인에서 코모도어 64를 포함한 코모도어 128D에 이르는 8비트 컴퓨터용 모든 코모도어의 플로피 디스크 드라이브(일부는 6502 기반 CPU 2개 포함), 그리고 8비트 컴퓨터 라인인 400Xe에 이르는 모든 Atari의 디스크 드라이브에 사용되었습니다.

6500 가족의 또 다른 중요한 용도는 비디오 게임이었다.프로세서 설계를 최초로 사용한 것은 Atari VCS로, 나중에 Atari 2600으로 이름이 변경되었습니다.VCS는 6502의 변형 모델인 6507을 사용했습니다. 6507은 핀 수가 적기 때문에 8KB의 메모리만 처리할 수 있습니다.수백만 개의 아타리 콘솔이 판매될 것이며, 각 콘솔에는 MOS 프로세서가 탑재되어 있습니다.또 다른 중요한 용도는 닌텐도 엔터테인먼트 시스템과 패미컴이다.NES에 사용된 6502는 Ricoh의 두 번째 소스 버전입니다.이 버전에는 바이너리 코드 10진수 모드가 없지만 사운드 생성, 조이패드 읽기, 스프라이트 리스트 DMA를 위한 22개의 메모리 매핑 레지스터와 온다이 하드웨어가 추가되었습니다.NTSC 콘솔에서는 2A03으로 불리며, PAL Divider 콘솔에서는 2A07로 불리며, PAL Divider에서는 2A07로 불린다.오디오 샘플 레이트에 대한 룩업 테이블)이 있습니다.이 프로세서는 닌텐도 전용으로 제작되었습니다.Atari Lynx는 4MHz 버전의 칩인 65SC02를 사용했습니다.

1980년대에 유명한 전자 잡지 Elektor/Elektuur는 마이크로프로세서 개발 보드 주니어 컴퓨터에 이 프로세서를 사용했습니다.

- 6502 또는 그 변종을 사용하는 가정용 컴퓨터 및 비디오 게임 콘솔

기술 설명

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | (비트 위치) |

| 메인 레지스터 | ||||||||||||||||

| A | 어큐뮬레이터 | |||||||||||||||

| 인덱스 레지스터 | ||||||||||||||||

| X | X 지수 | |||||||||||||||

| Y | Y지수 | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | SP | 스택 포인터 | |||||||

| 프로그램 카운터 | ||||||||||||||||

| PC | 프로그램 카운터 | |||||||||||||||

| 상태 레지스터 | ||||||||||||||||

| N | V | - | B | D | I | Z | C | 프로세서 플래그 | ||||||||

6502는 16비트 어드레스 버스를 탑재한 리틀엔디안 8비트 프로세서입니다.원래 버전은 다이 크기가 3.9mm × 4.3mm인 8µm[70] 공정 기술 칩을 사용하여 제작되었으며, 총 면적은 16.6mm입니다2.[38]

내부 로직은 외부 클럭 레이트와 같은 속도로 동작하지만 클럭 속도가 낮음에도 불구하고(일반적으로 1~2MHz 정도), 6502의 성능은 상당히 빠른 클럭을 사용하는 다른 동시대 CPU에 비해 경쟁력이 있었습니다.이는 부분적으로 다른 많은 설계보다 훨씬 더 많은 조합(클럭리스) 논리에 의해 구현된 단순한 상태 기계에 기인합니다. 따라서 2상 클럭(사이클당 2개의 동기화를 제공)이 기계 사이클을 직접 제어할 수 있습니다.6502의 일반적인 설명서는 현재의 설계에 비해 절반의 사이클이 소요될 수 있습니다.동적인 NMOS 6502 칩은 당시의 대부분의 단순한 CPU와 마찬가지로 마이크로코드[clarification needed] ROM에 의해 시퀀싱되지 않고 명령 디코딩 및 시퀀싱에 PLA(칩 영역의 약 15%를 차지)를 사용합니다.대부분의 8비트 마이크로프로세서와 마찬가지로 칩은 페칭과 실행의 제한된 중복을 수행합니다.

클럭 주파수가 낮기 때문에 CPU에 접속되어 있는 메모리와 주변기기의 속도 요건이 완화되었습니다(비동기 설계에 의해 이 부분은 칩 버전에 따라 크게 다릅니다).이는 저렴한 메모리의 액세스 시간이 250~450ns인 시기에 매우 중요했습니다.

칩은 클럭 사이클의 특정 부분에서만 메모리에 액세스하고 이러한 사이클은 PHI2 로우 클럭아웃 핀으로 나타나기 때문에 6502가 버스에서 꺼졌을 때 시스템의 다른 칩이 메모리에 액세스 할 수 있었습니다.이것은 「숨겨진 액세스」라고 불리기도 합니다.이 기술은 컴퓨터 시스템에서 널리 사용되었습니다. 컴퓨터 시스템은 2MHz에서 액세스할 수 있는 메모리를 사용하고 1MHz에서 CPU를 실행합니다.이것에 의해, CPU 와 비디오 하드웨어가 액세스를 인터리브 할 수 있게 [71]되어, 메모리 디바이스와 같은 합계 퍼포먼스가 실현됩니다.1980년대에 더 빠른 메모리를 사용할 수 있게 되었을 때, BBC Micro의 2MHz CPU와 같이 새로운 기계는 더 높은 클럭 속도로 작동할 수 있었고, 여전히 버스 공유 기술을 사용할 수 있었습니다.

레지스터

그 선구자인 6800과 마찬가지로 6502는 레지스터가 거의 없습니다.6502의 레지스터에는 8비트 어큐뮬레이터 레지스터 1개(A), 8비트 인덱스 레지스터 2개(X 및 Y), 7개의 프로세서 상태 플래그 비트(P)가 포함됩니다.비트 7에서 비트 0까지는 마이너스(N), 오버플로우(V), 예약됨(B), 10진수(D), 인터럽트 비활성화(I), 제로(Z) 및 캐리(C) 플래그 8비트입니다.이는 같은 시대의 일반적인 디자인인 Z80과 비교됩니다.Z80은 8개의 범용 8비트 레지스터를 갖추고 있으며, 4개의 16비트 레지스터로 결합할 수 있습니다.Z80은 또한 총 16개의 범용 레지스터를 만들었던 완전한 대체 레지스터 세트를 가지고 있었다.

레지스터의 부족을 어느 정도 보충하기 위해 6502는 명령에서 64KB의 메모리를 모두 처리하는 데 필요한 두 개의 주소 바이트 대신 하나의 주소 바이트를 사용하는 제로 페이지 주소 지정 모드를 포함했습니다.그러면 더 짧은 명령을 사용하여 처음 256바이트의 RAM에 빠르게 액세스할 수 있습니다.Chuck Peddle은 인터뷰에서 이러한 최초의 256바이트 RAM을 [citation needed]레지스터처럼 사용할 수 있도록 하는 것이 목적이라고 말했습니다.

스택 주소 공간은 메모리 페이지에 유선 연결되어 있습니다.$01(예: 주소 범위)$0100–$01FF(256–511스택에 대한 소프트웨어 액세스는 4개의 암묵적인 어드레싱 모드 명령을 통해 이루어집니다.이 명령어의 기능은 어큐뮬레이터 또는 프로세서 상태 레지스터를 푸시 또는 팝(풀)하는 것입니다.JSR(Jump to Subroutine) 및 RTS(Return from Subroutine) 명령을 통한 서브루틴 콜 및 인터럽트 처리에도 동일한 스택이 사용됩니다.

주소 지정

이 칩은 PDP-8과 같은 고속 "다이렉트 페이지" 또는 "제로 페이지" 모드를 포함한 여러 어드레싱 모드로 인덱스 및 스택레지스터를 효과적으로 사용합니다.이 모드는 주소 0부터255까지의 메모리 위치에 1개의 8비트주소로 액세스 합니다(주소의 상위 바이트를 취득하는데 통상 필요한 사이클을 절약합니다).e 6502는 다른 프로세서의 코드가 레지스터를 사용하는 것과 마찬가지로 제로 페이지를 많이 사용합니다.운영체제를 탑재한 6502 기반의 일부 마이크로컴퓨터에서는 운영체제는 제로 페이지의 대부분을 사용하며 사용자가 사용할 수 있는 위치는 극히 적습니다.

어드레싱 모드에는 암묵(1바이트 명령), 절대(3바이트), 인덱스 절대(3바이트), 인덱스 제로 페이지(2바이트), 상대(2바이트), 어큐뮬레이터(1) 간접, x 및 간접, y(2) 및 즉시(2)도 포함됩니다.절대 모드는 범용 모드입니다.브런치 명령에서는 브런치 뒤의 명령에 대해 부호 있는8비트 오프셋을 사용합니다.숫자 범위는 -128 입니다.따라서 127은 브런치명령어 뒤에 있는 명령어로부터128바이트, 127바이트로 변환됩니다(브런치명령어 시작부터129바이트).어큐뮬레이터 모드에서는, 어큐뮬레이터를 유효 주소로서 사용하고, 오퍼랜드 데이터는 필요 없습니다.즉시 모드에서는 8비트 리터럴피연산자가 사용됩니다.

간접 주소 지정

간접 모드는 배열 처리 및 기타 루프에 유용합니다.5/6 사이클(간접, y) 모드에서는 8비트 Y 레지스터가 0페이지에서 읽은 16비트 기본 주소에 추가됩니다. 이 주소는 opcode 뒤에 1바이트씩 위치합니다.따라서 Y 레지스터는 실제 인덱스를 유지하기 위해 사용된다는 의미에서 인덱스 레지스터입니다(기본 주소가 직접 저장되고 즉시 오프셋이 추가될 수 있는6800의 X 레지스터와는 반대).인덱스 레지스터를 증가시켜 어레이를 바이트 단위로 이동하는 데 두 번의 추가 사이클만 소요됩니다.빈도가 낮은 (간접,x) 모드에서는, X 레지스터의 컨텐츠에 명령의 제2 바이트를 더하는 것에 의해서 형성되는 제로 페이지 주소에서 동작의 유효 주소를 찾을 수 있다.인덱스 모드를 사용하면 제로 페이지는 최대 128개의 추가(매우 느리지만) 주소 레지스터 세트로 효과적으로 기능합니다.

6502는 2진수 또는 2진수 코드 10진수로 더하기 및 빼기를 수행할 수 있습니다.를 사용하여 CPU를 BCD 모드로 설정하다SED(set D flag) 명령에서는 10진수 산술이 실행됩니다.$99 + $01이 될 것이다$00캐리어(C) 플래그를 설정합니다.바이너리 모드(CLD, Clear D flag)를 사용하면, 같은 조작으로,$9A그리고 운반 깃발을 제거한다.Atari BASIC을 제외하고 BCD 모드는 가정용 컴퓨터 애플리케이션에서는 거의 사용되지 않았습니다.

6502 어셈블리 언어의 단순하지만 특징적인 예는 Hello world! 기사를 참조하십시오.

설명 및 조작 코드

6502 명령 동작 코드(opcode)는 8비트 길이로 일반적인 AAABBCC 형식을 가지고 있습니다.여기서 AAA와 CC는 opcode를 정의하고 BBB는 어드레싱 [73]모드를 정의합니다.

예를 들어,ORA명령 - 다른 값을 사용하여 축적기의 비트에 대해 비트 단위 OR을 수행합니다.명령어 opcode는 000bbb01 형식으로, bbb는 즉시 모드 값(정수), 001은 제로 페이지 고정 주소, 011은 절대 주소 등입니다.[73]

이 패턴은 절대적이지 않으며 몇 가지 예외가 있습니다.단, 이것이 적용되는 경우에는 opcode 값을 어셈블리 니모닉으로 쉽게 재구성하여 대부분의 명령에서 특수 목적 [73]코드로 엣지 케이스를 처리할 수 있습니다.

8비트 패턴을 사용하여 사용할 수 있는 256개의 가능한 opcode 중 원본 6502는 151개를 사용하며, 복수의 어드레싱 모드를 가진 56개의 명령으로 구성되어 있습니다.명령어 및 어드레싱 모드에 따라 opcode에는 0, 오퍼랜드에1바이트 또는 2바이트가 더 필요할 수 있습니다.따라서 6502 기계 명령의 길이는 1바이트에서 [74][75]3바이트까지 다양합니다.피연산자는 6502의 일반적인 리틀 엔디언 형식으로 저장됩니다.

6502의 16비트 CMOS의 후속인 65C816도 24비트 어드레싱을 지원하므로 명령어는 3바이트 오퍼랜드로 조립되며 리틀엔디안 형식으로 배열됩니다.

나머지 105개의 opcode는 정의되어 있지 않습니다.원래 설계에서는 하위 4비트(니블)가 3, 7, B 또는 F인 명령은 사용되지 않아 향후 확장의 여지가 있습니다.마찬가지로 $2x 컬럼에는 엔트리가 1개밖에 없습니다.LDX #constant나머지 25개의 빈 슬롯이 분배되었습니다.빈 슬롯의 일부는 65C02에서 새로운 명령과 새로운 어드레싱 모드를 가진 기존 슬롯의 바리에이션을 모두 제공하기 위해 사용되었습니다.$Fx 명령어는 처음에는 서드파티 벤더가 자체 명령을 추가할 수 있도록 무료였지만, 이후 버전의 65C02는 Rockwell Semiconductor가 개발한 일련의 비트 조작 명령을 표준화했습니다.

어셈블리 언어

6502 어셈블리의 언어문은 3글자의 명령어 니모닉과 그 후에 임의의 오퍼랜드로 구성됩니다.어드레싱 모드에 따라 별도의 오퍼랜드를 취하지 않고 단일 레지스터를 타깃으로 하는 명령은 명령 니모닉에 타깃 레지스터를 결합하므로 어셈블러는 다음을 사용합니다.INX와는 반대로INC XX 레지스터를 증가시킵니다.

지시표

| 6502 명령 집합의 Opcode 매트릭스 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 주소 지정 모드:A – 어큐뮬레이터, # – immediate, zpg – 제로 페이지, abs – 절대, ind – 간접, X – X – Y – Y – Y 레지스터, rel – 상대 인덱스 | ||||||||||||

| 하이 니블 | 로우 니블 | |||||||||||

| 0 | 1 | 2 | 4 | 5 | 6 | 8 | 9 | A | C | D | E | |

| 0 | BRK | ORA(ind,X) | ORA zpg | ASL zpg | PHP | ORA 번호 | ASL A | ORA 복근 | ASL 복근 | |||

| 1 | BPL 릴 | ORA(ind), Y | ORA zpg,X | ASL zpg,X | CLC | ORA 복근, Y | ORA 복근, X | ASL 복근, X | ||||

| 2 | JSR 복근 | AND(ind,X) | 비트 zpg | AND zpg | ROL zpg | PLP | 그리고 # | 롤 A | BIT 복근 | AND 복근 | 롤 복근 | |

| 3 | BMI 릴 | AND(ind), Y | AND zpg,X | ROL zpg,X | 초 | 그리고 복근, Y | 그리고 복근,X | ROL 복근, X | ||||

| 4 | RTI | EOR(ind,X) | EOR zpg | LSR zpg | PHA | EOR 번호 | LSR A | JMP 복근 | EOR 복근 | LSR 복근 | ||

| 5 | BVC 릴 | EOR(ind), Y | EOR zpg,X | LSR zpg,X | CLI | EOR 복근, Y | EOR 복근,X | LSR 복근,X | ||||

| 6 | RTS | ADC(ind,X) | ADC zpg | ROR zpg | PLA | ADC 번호 | ROR A | JMP(ind) | ADC 복근 | ROR 복근 | ||

| 7 | BVS 릴 | ADC(ind), Y | ADC zpg,X | ROR zpg,X | SEI | ADC 복근, Y | ADC 복근, X | ROR 복근,X | ||||

| 8 | STA(ind,X) | STY zpg | STA zpg | STX zpg | DEY | TXA | SY 복근 | STA 복근 | STX 복근 | |||

| 9 | BCC 릴 | STA(ind), Y | STY zpg,X | STA zpg,X | STX zpg,Y | 타이아 | STA 복근, Y | TXS | STA 복근, X | |||

| A | LDY 번호 | LDA(ind,X) | LDX 번호 | LDY zpg | LDA zpg | LDX zpg | 타이 | LDA 번호 | 세금 | LDY 복근 | LDA 복근 | LDX 복근 |

| B | BCS 릴 | LDA(ind), Y | LDY zpg,X | LDA zpg,X | LDX zpg,Y | CLV | LDA 복근, Y | TSX | LDY 복근, X | LDA 복근,X | LDX 복근, Y | |

| C | CPY 번호 | CMP(ind,X) | CPY zpg | CMP zpg | DEC zpg | INY | CMP 번호 | DEX | CPY 복근 | CMP 복근 | DEC 복근 | |

| D | BNE 릴 | CMP(ind), Y | CMP zpg,X | DEC zpg,X | CLD | CMP 복근, Y | CMP 복근,X | DEC 복근, X | ||||

| E | CPX 번호 | SBC(ind,X) | CPX zpg | SBC zpg | INC zpg | INX | SBC 번호 | NOP | CPX 복근 | SBC 복근 | INC 복근 | |

| F | BEQ 릴 | SBC(ind), Y | SBC zpg,X | INC zpg,X | SED | SBC 복근, Y | SBC 복근, X | INC 복근,X | ||||

| 6502 명령 집합에는 빈 연산 코드(예: F2)와 낮은 니블이 3, 7, B 및 F인 모든 연산 코드가 정의되어 있지 않습니다. | ||||||||||||

상세동작동

프로세서의 Non-Maskable Interrupt(NMI; 마스크 불가능 인터럽트) 입력은 에지에 민감합니다.즉, 인터럽트는 레벨이 아닌 신호의 하강 에지에 의해 트리거됩니다.이 기능의 의미는 유선 OR 인터럽트 회선이 쉽게 지원되지 않는다는 것입니다.단, 하드웨어에 의해 NMI 입력이 다시 비활성화될 때까지 중첩된 NMI 인터럽트가 발생하지 않도록 합니다(대부분은 NMI 인터럽트 핸들러의 제어 하에 있습니다).

NMI 및 IRQ(마스크 가능) 하드웨어 인터럽트 회선의 동시 어설션으로 인해 IRQ가 무시됩니다.다만, NMI 의 서비스 후에도 IRQ 의 회선이 어설션 된 채로 있으면, IRQ 는 레벨에 민감하기 때문에, 프로세서는 IRQ 에 즉석에서 응답합니다.따라서 6502 설계에서는 일종의 삽입 인터럽트 우선순위가 확립되었습니다.

B 플래그는 6502가 NMI 에지 검출기의 출력과 IRQ 입력을 주기적으로 샘플링하여 설정합니다.IRQ가 I 플래그로 허용된 경우에만 로우로 구동되는 IRQ 신호가 인식됩니다.이와 같이 NMI 요구 또는 (마스크 가능) IRQ가 검출되면 B 플래그는 0으로 설정되며, 프로그램 [76][77]카운터에 근거해 다음 명령을 실행하는 대신 프로세서가 BRK 명령을 다음 번에 실행하도록 한다.

다음으로 BRK 명령은 B 플래그 비트가 0으로 설정된 상태에서 프로세서 상태를 스택에 푸시합니다.실행이 끝나면 BRK 명령은 B 플래그 값을 1로 재설정합니다.이것이 B 플래그를 변경할 수 있는 유일한 방법입니다.BRK 명령 이외의 명령이 프로세서 상태의[78] 일부로 B 플래그를 스택에 푸시할 경우 B 플래그는 항상 값 1을 가집니다.

SO 입력 핀을 하이에서 로우로 전환하면 프로세서의 오버플로 상태 비트가 설정됩니다.외부 하드웨어에 대한 신속한 응답에 사용할 수 있습니다.예를 들어 고속 폴링 디바이스 드라이버는 Branch-on-oVerflow-Clear를 사용하여 3 사이클에 한 번만 하드웨어를 폴링할 수 있습니다.BVC SO 하강 천이에 의해 오버플로가 설정될 때까지 분기하는 명령입니다.Commodore 1541 및 기타 Commodorefloppy 디스크 드라이브는 이 기술을 사용하여 시리얼라이저가 다른 바이트의 디스크 데이터를 전송할 준비가 되었는지 여부를 감지합니다.시스템 하드웨어 및 소프트웨어 설계에서는 산술 처리 중에 SO가 발생하여 계산이 중단되지 않도록 해야 합니다.

변형 및 파생상품

오리지널 NMOS 6502에는 수많은 변종이 있었습니다.

| 회사 | 모델 | 묘사 |

|---|---|---|

| 6502A | 소행성 디럭스에 사용되는 1.5MHz 칩입니다. | |

| 6502B | 1이 아닌 2MHz의 최대 속도로 실행할 수 있는 6502 버전.B는 Apple III, BBC Micro에서 사용되었으며 초기 Atari 8비트 컴퓨터에서 1.79MHz로 측정되었습니다. | |

| 6502C | "공식" 6502C는 최대 4MHz로 구동할 수 있는 원래 6502의 버전이었다. SALLY와 혼동하지 마십시오.Atari용으로 설계된 커스텀 6502(때로는 「6502C」[79]라고도 불립니다) 또는 유사한 이름의 65C02와 혼동하지 마십시오. | |

| SALLY / C014806 / "6502C" | Atari용으로 설계된 커스텀 6502 베리안트. 이후 Atari 8비트 컴퓨터 및 Atari 5200 및 Atari 7800 콘솔에서 사용됩니다. 핀 35에 HALT 신호가 있고 핀 36에 R/W 신호가 있습니다(표준 6502에는 이러한 핀이 연결되어 있지 않습니다(N/C).HALT 로우 래치를 당기면 클럭이 래치되어 CPU가 일시 정지됩니다.이것은, 비디오 회로 다이렉트 메모리 액세스(DMA)[80]를 허가하기 위해서 사용되었습니다. Atari 문서에서는 "6502C"라고 부르기도 하지만 이는 "공식" 6502C와 동일하지 않으며 칩 자체도 그렇게 [79]표시되지 않습니다. | |

| MOS | 6503 | 메모리 어드레싱 기능(4KB), RDY 입력 없음(단계 1(OUT), SYNC, 용장 Vss 및 SO 핀도 생략).[81] |

| MOS | 6504 | 28 핀 DIP 패키지의 메모리어드레싱 기능(8KB), NMI 및 RDY 입력 없음(단계 1(OUT), SYNC, 용장 Vss 및 SO 핀도 [81]생략). |

| MOS | 6505 | 메모리 어드레싱 기능(4KB), NMI 없음(단계 1(OUT), SYNC, 용장 Vss 및 SO 핀도 생략).[81] |

| MOS | 6506 | 메모리 어드레싱 기능(4KB), NMI 및 RDY 입력 없음, 단 28핀 DIP 패키지의 6502 클럭 핀(즉, 2상 출력 클럭)의 3개 모두(6502의 SYNC, 용장 Vss 및 SO 핀도 제외).[81] |

| MOS | 6507 | 28핀 DIP 패키지로 메모리어드레싱 기능(8KB)이 저하되어 인터럽트가 없습니다(6502의 단계1(OUT), SYNC, 용장 Vss 및 SO 핀도 제외).[81]이 칩은 아타리 2600 비디오 게임 시스템에 사용되었습니다. |

| MOS | 6508 | 내장 8비트 입출력 포트와 256바이트의 내장 스태틱 RAM을 탑재. |

| MOS | 6509 | 64KB의 16개의 뱅크로서 최대 1MB의 RAM 주소를 지정할 수 있으며 Commodore CBM-II 시리즈에서 사용되었습니다. |

| MOS | 6510 | 내장형 6비트 프로그램 가능 입력/출력 포트가 있으며 Commodore 64에서 사용되었습니다.8500은 사실상 6510의 HMOS 버전이며 이후 버전의 C64로 대체되었습니다. |

| MOS | 6512 6513 6514 6515 | MOS 테크놀로지 6512, 6513, 6514 및 6515는 각각 650x 등의 내부 클럭 제너레이터를 사용하는 대신 외부 클럭에 의존합니다.이는 클럭이 비대칭으로 동작할 수 있는 설계에 따라 전체적인 CPU 퍼포먼스가 향상될 수 있습니다. 6512는 온보드 클럭 [81]오실레이터가 아닌 외부 클럭 오실레이터용 2상 클럭 입력이 가능한 6502입니다.6513, 6514 및 6515는 (각각) 동일한 2상 클럭 [81]입력의 6503, 6504 및 6505와 동등합니다. |

| 리코 | 2A03 | 오디오 프로세싱 유닛을 포함하며 BCD 모드가 없는 6502 변종, 닌텐도 엔터테인먼트 시스템에 사용됩니다. |

| MOS | 6591 6592 | 48핀 DIP [82][83]패키지로 완전한 Atari 2600을 사용하는 칩 설계 시스템. |

| WDC | 65C02 | Western Design Center(WDC)의 Bill Mensch에 의해 설계된 NMOS 6502의 CMOS 버전은 소비전력 절감, 훨씬 빠른 클럭 속도 지원, 새로운 명령, 일부 기존 명령의 새로운 어드레싱 모드 및 NMOS 에러타 수정을 특징으로 합니다.JMP ($xxFF)버그 |

| WDC | 65SC02 | 개별 비트 조작(RMB, SMB, BBR 및 BBS)[84]이 없는 WDC 65C02의 바리안트.4MHz로 작동하는 이 코어는 아타리 링스의 메인 시스템 IC에 사용되었습니다. |

| CSG/MOS | 65CE02 | CMOS 파생상품은 Commodore Semiconductor Group(CSG; 코모도어 반도체 그룹)에 의해 개발되었습니다.이전의 MOS 테크놀로지입니다. |

| 록웰 | R6511Q R6500/11, R6500/12, R6500/15 "원칩 마이크로컴퓨터" | 6502 기반 프로세서의 확장 버전(개별 비트 조작(RMB, SMB, BBR 및 BBS), 온칩192 바이트 제로 페이지 RAM, UART 등)[85][86] |

| 록웰 | R65F11 R65F12 | Rockwell R65F11(1983년에 도입)과 그 이후의 R65F12는 6502 기반 프로세서의 확장 버전으로 개별 비트 조작(RMB, SMB, BBR 및 BBS), 온칩 제로 페이지 RAM, 온칩 포스 커널 ROM,[87][88][89][90][91] UART 등을 포함합니다. |

| GTE | G65SC102 | 65C02와 호환되지만 핀 배치 및 오실레이터 회로가 약간 다릅니다.BBC 마스터 터보는 이 CPU의 4MHz 버전을 코프로세서 카드에 포함시켰습니다.코프로세서 카드도 별도로 구입하여 마스터 128에 추가할 수 있습니다. |

| 록웰 | R65C00 R65C21 R65C29 | R65C00, R65C21 및 R65C29는 1개의 칩에 2개의 확장 CMOS 6502를 탑재하고 있으며, R65C00 및 R65C21에는 마스크 프로그래밍 가능한 [92][93]ROM이 2KB 탑재되어 있습니다. |

| CM630 | 6502의 1MHz 동부 블록 클론이며, Apple [94]// 시리즈의 불가리아 클론인 Pravetz 8A 및 8C에 사용되었습니다. | |

| MOS | 7501 8501 | 1984년에 [95]도입된 6510(확장판 6502).I/O 포트 핀의 수를 6개에서 7개로 늘렸지만 마스크 불가능한 인터럽트 및 클럭 [96]출력에 대해서는 핀을 생략했습니다.Commodore의 C-16, C-116 및 Plus/4 컴퓨터에 사용됩니다.7501 CPU와 8501 CPU의 주요 차이점은 7501은 HMOS-1 프로세스로 제조되었으며 8501은 HMOS-2로 [95]제조되었다는 것입니다. |

| MOS | 8500 | 1985년에 6510의 HMOS 버전으로 도입되었습니다(6502에 근거하고 있습니다).프로세스 변경 이외에는 8500은 6510의 NMOS 버전과 거의 동일합니다.이것은 코모도어 64의 최신 버전에서 6510을 대체했다. |

| MOS | 8502 | MOS 테크놀로지에 의해 설계되어 Commodore 128에서 사용됩니다.Commodore 64에서 사용되는 MOS 6510을 기반으로 8502는 6510의 [97]2배의 클럭 속도로 동작할 수 있었습니다.8502 패밀리에는 MOS 7501, 8500 및 8501도 포함되어 있습니다. |

| 허드슨 소프트 | HuC6280 | 일본 비디오 게임 회사 허드슨 소프트의 개량형 WDC 65C02.SuperGrafx용 Seiko Epson과 NEC에 의해 제조되었습니다.HuC6280을 사용한 가장 주목할 만한 제품은 NEC의 TurboGrafx-16 비디오 게임기입니다. |

16비트 파생 모델

Western Design Center는 W65C816S 프로세서를 설계하여 현재 생산하고 있습니다.W65C816S 프로세서는 65C02의 16비트 스태틱코어 후속 제품입니다.W65C816S는 애플 IIGS 컴퓨터의 핵심이자 슈퍼 닌텐도 엔터테인먼트 시스템을 구동하는 리코 5A22 프로세서의 기반인 65C816의 새로운 변형이다.W65C816S는 65C816보다 약간 개선된 기능을 탑재하고 있기 때문에 새로운 칩은 이전 칩과 완전히 호환되는 하드웨어가 아닙니다.이러한 개선점 중에는 스태틱코어로의 변환이 있어 레지스터가 데이터를 잃지 않고 어느 단계에서나 클럭을 정지할 수 있습니다.2020년 3월 현재 전자제품 유통업체를 통해 판매되고 있는 W65C816S는 공식적으로 14MHz 작동에 대한 정격입니다.

또한 Western Design Center는 65C802를 설계 및 생산했습니다.이것은 65C816 코어로 65(C)02 핀 호환 패키지에 64킬로바이트 주소 공간을 포함하고 있습니다.65C802는 6502 보드에 장착할 수 있으며 전원을 켤 때 65C02로 기능하며 "에뮬레이션 모드"로 작동합니다.65C816과 마찬가지로 2개의 명령 시퀀스는 65C802를 "네이티브 모드" 동작으로 전환하여 16비트 어큐뮬레이터와 인덱스 레지스터 및 기타 65C816 기능을 노출시킵니다.65C802는 널리 사용되지 않았고 생산이 중단되었다.

코드 예시

다음 6502 어셈블리 언어 소스 코드는 서브루틴에 대한 것입니다.TOLOWER 는 늘 종단 문자열의 위치를 복사하여 대문자 문자를 소문자로 변환합니다.복사되는 문자열이 "source"이고 변환된 소스가 저장되는 문자열이 "destination"입니다.

0080 0080 00 04 0082 00 05 0600 0600 A0 00 0602 지하 1층 80 0604 F0 11 0606 C9 41 0608 90 06 060A C9 5B 060C B0 02 060E 09 20 0610 91 82 0612 C8 0613 D0 ED 0615 38 0616 60 0617 91 82 0619 18 061A 60 061B | ; 톨로워: ; ; null 끝 문자열은 모두 소문자로 변환합니다. ; 최대 문자열 길이는 255자 + null-term-입니다. ; inator. ; ; 파라미터: ; ; SRC {{snd}} 소스 문자열 주소 ; DST {{snd}}: 수신인 문자열 주소 ; 조직 $0080 ; SRC .단어 $0400 ;소스 문자열 포인터 DST .단어 $0500 ;대상 문자열 포인터 ; 조직 $0600 ;개시 주소 표시 ; 톨루 LDY #$00 시작 지수 ; 고리 LDA (SRC),Y ;소스 문자열에서 가져오기 BEQ 다 했어요. 스트링의 끝 ; CMP #'A' ;UC알파벳보다 낮은 경우... BCC 건너뛰다. ;변경하지 않고 복사 ; CMP #'Z'+1 ;UC알파벳보다 큰 경우... BCS 건너뛰다. ;변경하지 않고 복사 ; ORA #%00100000 ;소문자 구분 ; 건너뛰다. 스타 (DST),Y ;대상 문자열에 저장 INY 지표 BNE 고리 ;다음 문자 ; 메모: Y 가 랩 하면, 행선지 문자열은 미정의인 채로 남습니다. ; 상태.이것을 호출 함수에 나타내기 위해서, carry 를 설정합니다. ; 초 ;report 문자열이 너무 깁니다.오류... RTS 발신자에게 되돌아가다 ; 다 했어요. 스타 (DST),Y ;수신처 스트링의 경우 CLC ;리포트 변환 완료... RTS 발신자에게 되돌아가다 ; .끝. |

버그와 기묘한 일

6502에는 몇 가지 버그와 기호가 있어 프로그래밍 시 고려해야 했습니다.

- 일부 KIM-1 컴퓨터에 동봉된 것과 같은 6502의 초기 리비전은 ROR(Rotate Right Memory or accumulator) 명령에서 심각한 오류가 발생했습니다.이러한 칩에서의 ROR 동작은 상태 레지스터의 반송 비트에 영향을 주지 않는 사실상 ASL(산술적 좌측 이동) 명령입니다.MOS는 1976년부터 [98]6502개의 칩에 ROR이 표시될 것이라고 약속하면서 이 결함 때문에 이 명령을 칩 문서에서 제외했습니다.현재 존재하는 6502 칩의 대부분은 이 오류를 나타내지 않습니다.

- NMOS 6502 패밀리는 칩 제조원에 따라 다양한 미등록 명령어가 있습니다.6502 명령 디코딩은 사용 가능한 256개의 opcode 중 151개에 대해서만 정의된 유선 로직 어레이(프로그래머블 로직 어레이와 유사)로 구현됩니다.나머지 105는 프로세서의 크래시, 2개의 유효한 명령의 연속 실행, 2개의 명령의 이상 혼합 실행, 또는 전혀 아무것도 하지 않는 등 이상하고 예측하기 어려운 액션을 트리거합니다.Eastern House Software는 프로세서와 소켓 사이에 꽂아 구현되지 않은 운영 코드를 BRK(소프트웨어 인터럽트) [citation needed]명령으로 변환하는 장치인 "Trap65"를 개발했습니다.일부 프로그래머는 이 기능을 사용하여 BRK 명령의 0xFFE [99][100]벡터에서 가로채는 특수하게 작성된 소프트웨어를 사용하여 구현되지 않은 opcode에 대한 기능을 제공함으로써 6502 명령 집합을 확장했습니다.정의되지 않은 모든 opcode는 바이트 크기와 실행 시간은 다르지만 6502의 확장 CMOS 버전인 65C02에서는 NOP 명령으로 대체되었습니다.65C802/65C816에서는 모든 256개의 opcode가 정의된 동작을 수행합니다.

- 6502의 메모리 간접 점프 명령,

JMP (<address>)의 일부가 파손되어 있습니다.한다면<address>16진수 xxFF(즉, 로 끝나는 임의의 단어FF)에 저장되어 있는 주소로 프로세서가 점프하지 않습니다.xxFF그리고.xxFF+1예상대로지만, 오히려 에 의해 정의된 것이다.xxFF그리고.xx00(예를 들어,JMP ($10FF)는, 10FF 와 1100 에 보존되어 있는 주소가 아니고, 10FF 와 1000 에 보존되어 있는 주소로 점프합니다.이 결함은 NMOS 라인 전체에 걸쳐 계속되었지만 CMOS 파생 제품에서는 수정되었습니다. - 페이지 경계를 넘나드는 NMOS 6502 인덱스주소 지정에서는, 무효 주소의 추가 판독이 실행됩니다.이 특성은 타이머 또는 IRQ 플래그의 클리어, I/O핸드쉐이크 송신 등 읽기 시 동작하는 하드웨어에 액세스함으로써 랜덤한 문제를 일으킬 수 있습니다.이 결함은 NMOS 라인 전체에 걸쳐 계속되었지만 CMOS 파생 모델에서 수정되었습니다.CMOS 파생 모델에서는 프로세서가 마지막 명령 바이트를 추가로 읽습니다.

- 6502 읽기-수정-쓰기 명령에서는 읽기 사이클과 쓰기 사이클이 각각1개씩 실행됩니다.먼저 읽은 수정되지 않은 데이터를 다시 쓴 다음 수정한 데이터를 다시 씁니다.이 특성으로 인해 쓰기 작업에 사용되는 하드웨어에 두 번 액세스하면 문제가 발생할 수 있습니다.이 문제는 NMOS 라인 전체에 걸쳐 계속되었지만 CMOS 파생 모델에서는 수정되었습니다.이 파생 모델에서는 프로세서가 2개의 읽기 및1개의 쓰기 사이클을 수행합니다.방어적 프로그래밍 연습에서는 일반적으로 하드웨어 레지스터에서 읽기/수정/쓰기 명령을 실행하지 않음으로써 이 문제를 피할 수 있습니다.

- 프로세서가 BCD 모드일 때 N(결과 음), V(사인 비트 오버플로) 및 Z(결과 0) 상태 플래그는 BCD 결과가 아닌 이진 결과를 반영하므로 일반적으로 산술 연산을 수행할 때 의미가 없습니다.CMOS 파생 모델에서는 이 제한이 삭제되었습니다.따라서 이 기능은 CMOS 프로세서와 NMOS 버전을 [101]구별하기 위해 사용할 수 있습니다.

- 하드웨어 인터럽트가 발생했을 때 6502가 BCD 모드일 경우 바이너리모드로 돌아가지 않습니다.이 특성으로 인해 산술 연산을 수행하기 전에 BCD 모드를 클리어하지 못하면 인터럽트 서비스 루틴에 불분명한 버그가 발생할 수 있습니다.예를 들어 Commodore 64의 KERNAL은 이 프로세서의 특성을 올바르게 처리하지 않았기 때문에 BCD 연산 중에 IRQ를 비활성화하거나 재벡터링해야 합니다.이 문제는 CMOS 파생 모델에서도 해결되었습니다.

- 6502 명령어 세트에는 소프트웨어 인터럽트인 BRK(opcode $00)가 포함되어 있습니다(Motorola 6800 및 ARM 프로세서의 SWI 니모닉과 정신적으로 유사합니다).BRK는 소프트웨어 개발 중 프로그램 실행을 중단하고 테스트 및 디버깅을 위해 기계어 모니터를 시작하는 데 가장 많이 사용됩니다.BRK는 단순한 점프 테이블을 사용하여 프로그램 실행을 라우팅하기 위해서도 사용할 수 있습니다(인텔 8086 및 파생 모델이 소프트웨어 인터럽트를 번호로 처리하는 방식과 유사합니다).그러나 프로세서가 BRK 명령을 가져올 때 하드웨어 인터럽트가 발생하면 NMOS 버전의 프로세서는 BRK를 실행하지 못하고 하드웨어 인터럽트만 발생한 것처럼 처리됩니다.이 장애는 프로세서의 CMOS 구현으로 수정되었습니다.

- JSR(Jump to Subroutine) 및 RTS(Return from subroutine) 명령을 실행할 때 JSR에 의해 스택에 푸시되는 리턴 주소는 다음 명령의 주소가 아니라 JSR 오퍼랜드의 마지막 바이트(서브루틴 주소의 최상위 바이트)입니다.이는 실제 복사(프로그램 카운터에서 스택으로, 그리고 반대로)가 모든 [102]명령의 마지막에 발생하는 프로그램 카운터의 자동 증가 전에 발생하기 때문입니다.이 특성은 코드 스트림(ProDOS 8 테크니컬 레퍼런스 매뉴얼에 기재된 6502 프로그래밍 관용어)의 파라미터를 취득하기 위해 코드가 리턴 주소를 검사하지 않는 한 눈에 띄지 않습니다.이는 현재까지 6502 파생상품의 특징 중 하나이다.

「 」를 참조해 주세요.

- 6502 조립자 목록

- MOS 테크놀로지 6502 기반 가정용 컴퓨터

- 65xx 프로세서의 인터럽트

- 트랜지스터 카운트

- Apple II 액셀러레이터

- cc65 – 6502 매크로 어셈블러 및 C 컴파일러

메모들

레퍼런스

인용문

- ^ "The MOS 6502 and the Best Layout Guy in the World". swtch.com. 2011-01-03. Retrieved 2014-08-09.

- ^ "MOnSter6502 A complete, working discrete transistors (i.e. not integrated all on a single chip) replica of the classic MOS 6502 microprocessor". monster6502.com. 2017. Retrieved 2017-05-01.

- ^ William Mensch, Rob Walker (October 9, 1995). Interview with William Mensch (Web video). Atherton, California: Silicon Genesis, Stanford University Libraries. Archived from the original on May 8, 2012. Retrieved June 4, 2012. William Mensch와 모델레이터는 모두 6502 마이크로프로세서를 "6505-2"라고 선언합니다.

- ^ "Western Design Center (WDC) Home of 65xx Microprocessor Technology". www.westerndesigncenter.com. Retrieved 2019-04-08.

- ^ "Motorola Sues MOS Technology" (PDF). Microcomputer Digest. Cupertino CA: Microcomputer Associates. 2 (6): 11. December 1975. Archived from the original (PDF) on July 4, 2009.

- ^ "Motorola joins microprocessor race with 8-bit entry". Electronics. New York: McGraw-Hill. 47 (5): 29–30. March 7, 1974.

- ^ Motorola 6800 구술사 (2008), 9페이지

- ^ Buchanan, John K., "MOS DC 전압 부스터 회로", 미국 특허 3942047, 1976년 3월 2일 발행.

- ^ Buchanan, John K., "MOS 집적회로 마이크로프로세서 칩용 칩 지형", 미국 특허 3987418, 1976년 10월 19일 발행.

- ^ Motorola 6800 구술 이력 (2008년), 페이지 8

- ^ 멘슈 구술사(1995) 멘슈는 1966년 템플 대학에서 어소시에이트 학위를 취득한 후 애리조나 대학에 입학하기 전에 전자 기술자로 필코 포드에서 일했습니다.

- ^ Mensch, William D., "MOS 인터페이스 회로를 위한 칩 지형", 미국 특허 3968478은 1976년 7월 6일에 발행되었습니다.

- ^ Jenkins, Francis; Lane, E.; Lattin, W.; Richardson, W. (November 1973). "MOS-device modeling for computer implementation". IEEE Transactions on Circuit Theory. IEEE. 20 (6): 649–658. doi:10.1109/tct.1973.1083758. ISSN 0018-9324. 저자들은 모두 모토로라의 반도체 제품 부문 소속이었다.

- ^ Donohue, James F. (October 27, 1988). "The microprocessor first two decades: The way it was". EDN. Cahners Publishing. 33 (22A): 18–32. ISSN 0012-7515. 페이지 30.베넷은 이미 6800을 만드는 일을 하고 있었다.Peddle은 Bennett에 대해 "그는 이미 시작한 제품의 아키텍처 지원 작업을 하기 위해 저를 고용했습니다." …Peddle은 말합니다."모토롤라는 여러 번 그것을 죽이려 했습니다.Bennett이 없었다면 6800은 일어나지 않았을 것이고 많은 업계도 일어나지 않았을 것입니다."

- ^ 헵워스, 에드워드 C, 로드니 J. 민스, 찰스 1세Peddle, "비동기 통신 인터페이스 어댑터", 특허 3975712, 1976년 8월 17일 발행.주의: Motorola는 보통 발명가를 알파벳 순으로 나열했습니다.

- ^ Motorola (August 5, 1976). "They stay out front with Motorola's M6800 Family". Electronics. McGraw-Hill. 49 (16): 51. TRW, HP 및 RUSCO의 3가지 임베디드 어플리케이션을 보여주는 광고.

- ^ 페이지 89 Motorola 6800 구술사 (2008), 89

- ^ "It's the total product family". Electronics. New York: McGraw Hill. 48 (1): 37. January 9, 1975. 주변기기의 칩과 개발 툴의 완전한 세트를 강조하는 모토로라 광고.이것에 의해, 고객의 제품 설계 사이클이 단축됩니다.

- ^ Motorola 18 Motorola 6800 (2008) 18

- ^ "Motorola microprocessor set is 1 MHz n-MOS". Control Engineering. 21 (11): 11. November 1974. MC6800 마이크로프로세서 가격은 360달러였다.MC6850 비동기 통신 인터페이스 어댑터(ACIA)는 1975년 1분기에 도입될 예정입니다.

- ^ Intel Corporation (1984). Kaye, Glynnis Thompson (ed.). A Revolution in Progress – A History to Date of Intel (PDF). Intel Corporation. p. 14. Order number:231295. Archived (PDF) from the original on 23 October 2012. Retrieved 30 December 2016. "Shima는 약 1년 만에 8080을 구현했고 새로운 기기는 1974년 4월에 360달러에 소개되었습니다."

- ^ "Motorola mounts M6800 drive". Electronics. New York: McGraw-Hill. 48 (8): 25. April 17, 1975. 「디스트리뷰터에는 M6800 패밀리가 재고되어 있습니다.또, 이 부문에서는, 패밀리의 초기 6개의 부품과 애플리케이션, 프로그래밍 메뉴얼을 포함한 입문 키트도 300달러에 제공하고 있습니다.」

- ^ 2014년 인터뷰 52:30

- ^ 인터뷰 2014, 54:45

- ^ Bagnall(2010), 11.페들Peddle)은 6800년텍사스 그들은 텍사스의 오스틴에 가고 싶어하지 않았습니다."라고 Mensch는 설명합니다.

- ^ 인터뷰 2014, 54:40

- ^ 인터뷰 2014, 55:50

- ^ Waller, Larry (November 13, 1975). "Motorola seeks to end skid". Electronics. New York: McGraw-Hill. 48 (23): 96–98. 개요: 반도체 제품은 집적회로와 개별 컴포넌트의 두 부분으로 나뉩니다.지난 4분기 반도체 손실은 3천만 달러를 넘어섰다.판매 조직은 고객의 요구에 대한 민감성을 잃었고, "가격 인하에 대한 대응이 늦어진다는 것은 고객이 다른 곳에서 구매했다는 것을 의미합니다."기술적인 문제가 IC 생산에 영향을 미쳤다.문제는 "설계가 아니라 칩 앤 다이 수율"입니다.문제가 해결되었습니다.MC6800 마이크로프로세서는 "1974년 11월에 도착했다.

- ^ 인터뷰 2014, 56:30.

- ^ 인터뷰 2014, 55:00.

- ^ Bagnall (2010), 13페이지.

- ^ MOS Technology (November 14, 1974). "The First Single Chip Scientific Calculator Arrays". Electronics. McGraw-Hill. 47 (23): 90–91.

- ^ 2014년 57:00 인터뷰

- ^ 2014년 58:30 인터뷰

- ^ Cass, Stephen (16 September 2021). "Q&A With Co-Creator of the 6502 Processor". IEEE Spectrum.

- ^ Ho, Joshua (9 October 2014). "An Introduction to Semiconductor Physics, Technology, and Industry". Anandtech.

- ^ Motorola 6800 구술사(2008년), 페이지 10.

- ^ a b c 쿠시먼 1975, 페이지 40

- ^ "8080A microprocessor – DIP 40 package". CPU World.

- ^ a b 쿠시먼 1975, 페이지 38

- ^ a b "Moore's Law Milestones". IEEE.

- ^ Bagnall(2010), 페이지 19: "Paivinen은 Peddle에게 N채널 프로세스를 준비하겠다고 약속했습니다.그는 약속을 지켰다.

- ^ a b c 쿠시먼 1975, 36페이지

- ^ a b c 쿠시먼 1975, 페이지 41

- ^ Purcaru, John (2014). Games vs. Hardware. The History of PC video games: The 80's. p. 317.

- ^ 2014년 1:01:00 인터뷰

- ^ 2014년 1시 2분 인터뷰

- ^ 2014년 인터뷰 1시 2분 30초

- ^ 1975년 8월 데이터 시트에는 ROR이 없는 55개의 명령이 있고 1976년 5월 데이터 시트에는 ROR과 56개의 명령이 있습니다.파일: MCS650x Instruction Set.jpg

- ^ 스탠퍼드대 실리콘 제네시스 프로젝트: Willam Mensch 구술사 인터뷰 녹화

- ^ "Microprocessor line offers 4, 8, 16 bits". Electronics. New York: McGraw-Hill. 48 (15): 118. July 24, 1975. 이 문서에서는 6501 및 6502 및 4K 메모리만을 취급하는28 핀 버전에 대해 설명합니다.또한 "페들이 의사 16이라고 부르는 디자인"과 같은 미래 기기들도 다루었다.

- ^ Sugarman, Robert (25 August 1975). "Does the Country Need A Good $20 Microprocessor?" (PDF). EE Times. Manhasset, New York: CMP Publications: 25. Archived from the original (PDF) on 3 February 2007. Retrieved 5 February 2008.

- ^ Fylstra, Daniel (November 1975). "Son of Motorola (or the $20 CPU Chip)". Byte. Peterborough, NH: Green Publishing. 1 (3): 56–62. 6502 마이크로프로세서와 6800 마이크로프로세서의 비교.저자는 1975년 8월에 MOS Technology를 방문했다.

- ^ "3rd Generation Microprocessor" (PDF). Microcomputer Digest. Cupertino, CA: Microcomputer Associates. 2 (2): 1–3. August 1975. Archived from the original (PDF) on 2009-07-04. Retrieved 2009-11-27.

- ^ "MOS 6501 Microprocessor beats 'em all". Electronics. New York: McGraw-Hill. 48 (16): 60–61. August 7, 1975.

- ^ "MOS 6502 the second of a low cost high performance microprocessor family". Computer. IEEE Computer Society. 8 (9): 38–39. September 1975. doi:10.1109/C-M.1975.219074.

- ^ Bagnall (2010), 페이지 33-35.

- ^ Signetics (October 30, 1975). "Easiest-to-use microprocessor". Electronics. McGraw-Hill. 48 (22): 114–115.

- ^ Motorola (October 30, 1975). "All this and unbundled $69 microprocessor". Electronics. McGraw-Hill. 48 (22): 11. MC6800의 수량은 $175에서 $69로 인하되었습니다.이전 50~99대의 가격은 125달러였습니다.

- ^ 월러, 래리(11월 13일, 1975년)."뉴스 팬티:모토로라 마이크로 프로세서 막으려는 자가 저기 foe".전자.뉴욕:맥그로힐. 48(23):38."모토로라 지난주에 즉각적인 명령을 팔고 그 MCS6500을 포함한 마이크로 프로세서 제품을 만드는 것부터 MOS테크놀로지사, 노리스 타운:미국 Pennsylvania주 동남부, 펜실베이니아, 멈출 계획이라고 밝혔다."(이 문제 11월 7일에 출판되었다.).

- ^ Motorola는 6800 마이크로프로세서 패밀리에 대해 3962682, 3968478, 3975712, 3979730, 3979732, 3987418, 4003028, 4004281, 4004283, 4006457, 4010448, 4016546, 4020472, 40300, 4032896, 40354의 미국 특허를 취득했습니다.

- ^ Bagnall (2010), 53-54페이지."그는 (Mike Janes) 6800에서 모든 오리지널 작품을 모토로라에 숨겼습니다.

- ^ "Motorola, MOS Technology settle patent suit". Electronics. New York: McGraw-Hill. 49 (7): 39. April 1, 1975. 미국 펜실베이니아주 노리스타운의 MOS테크놀로지사는 MCS6501 마이크로프로세서를 시장에서 철수시키고 모토로라사에 지불하기로 합의했다.20만달러..." "MOS 테크놀로지와 8명의 전직 모토로라 직원들이 모토로라가 주장하는 기밀문서라는 법원 명령에 따라 반환했다." "…양사는 마이크로프로세서 분야의 특허에 관한 크로스 라이선스에 합의했다."

- ^ Bagnall (2010), 55-56페이지

- ^ Commodore International은 MOS 테크놀로지(PA, Norristown)를 인수합니다"Mergers and Acquisitions". Mini-Micro Systems. Cahners. 9 (11): 19. November 1976..이로써 6년 된 반도체 회사가 임박한 재난으로부터 구조되었습니다."

- ^ a b Goodwins, Rupert (December 4, 2010). "Intel's victims: Eight would-be giant killers". ZDNet. Archived from the original on May 5, 2013. Retrieved March 7, 2012.

- ^ Reimer, Jeremy. "Personal Computer Market Share: 1975-2004". Archived from the original on 6 June 2012. Retrieved 2009-07-17.

- ^ "How many Commodore 64 computers were sold?". Archived from the original on 2016-03-06. Retrieved 2011-02-01.

- ^ "Code Execution on a Tamagotchi". kwartzlab.ca. 7 May 2013. Archived from the original on 2018-08-31. Retrieved 2018-12-23.

- ^ Corder, Mike (Spring 1999). "Big Things in Small Packages". Pioneers' Progress with picoJava Technology. Sun Microelectronics. Archived from the original on 2006-03-12. Retrieved April 23, 2012.

The first 6502 was fabricated with 8 micron technology, ran at one megahertz and had a maximum memory of 64k.

- ^ "How to implement bus sharing / DMA on a 6502 system".

- ^ "PROGRAMMING MODEL MCS650X". MOS MICROCOMPUTERS PROGRAMMING MANUAL. MOS TECHNOLOGY, INC. January 1976.

- ^ a b c Parker, Neil. "The 6502/65C02/65C816 Instruction Set Decoded". Neil Parker's Apple II page.

- ^ 6502 명령어세트

- ^ NMOS 6502 동작 코드2016-01-14 Wayback Machine에 보관.

- ^ "INTERRUPT HANDLING". ogamespec. Retrieved 2021-05-15.

FLAG B CONTROL; FLAG B

- ^ "6502 BRK and B bit". VisualChips. Archived from the original on 2021-04-05. Retrieved 2021-05-15.

- ^ "FLAGS". ogamespec. Retrieved 2021-05-15.

B_OUT; INTERNAL DATA BUS (DB)

- ^ a b "FAQ 400 800 XL XE : What are SALLY, ANTIC, CTIA/GTIA/FGTIA, POKEY, and FREDDIE?". Archived from the original on 19 July 2020.

named SALLY by Atari engineers, but [support documents call it] "6502 (Modified)", "6502 Modified", "Custom 6502", or "6502C". [..] SALLY 6502 chips are never marked "6502C" but, other than the UMC UM6502I, always [marked] C014806. [..] [Other] chips marked "6502C" [..] are NOT the Atari "6502C" but [standard 6502] certified for 4MHz

- ^ "6502 (modified) CPU Microprocessor". ATARI 1200 XL HOME COMPUTER FIELD SERVICE MANUAL. ATARI. February 1983.

- ^ a b c d e f g 1982년 MOS 테크놀로지 데이터 카탈로그 (PDF는 bitsavers.org에서 입수)

- ^ Atariage:A2600 클론, 6591 칩 핀 할당

- ^ 해커데이:역대 가장 작은 Atari 2600

- ^ Zaks, Rodnay. Programming the 6502. p. 348.

- ^ "Rockwell R6511Q". Retrieved 30 Apr 2020.

- ^ "Rockwell R6500/11, R6500/12 and R6500/15 One-Chip Microcomputers". 7 Jun 1987. Retrieved 30 Apr 2020.

- ^ Randy M. Dumse. "The R65F11 and F68K Single-Chip Forth Computers". [1][permanent dead link] [2] Archived 2014-12-02 at the Wayback Machine 1984.

- ^ Ed Schmauch. "A Computerized Corrosion Monitoring System"[permanent dead link]. 1986.

- ^ Lawrence P. Forsley. "Embedded systems: 1990 Rochester Forth Conference : June 12 – 16th, 1990 University of Rochester". p. 51.

- ^ Rockwell. "RSC-Forth User's Manual". 1983.

- ^ "Rockwell R65F11 R65F12 Forth Based Microcomputers" (PDF). June 1987. Retrieved 28 Apr 2020.

- ^ "Archived copy" (PDF). Archived from the original (PDF) on 2016-05-15. Retrieved 2014-10-26.

{{cite web}}: CS1 maint: archived copy as title (link) - ^ "rockwell :: dataBooks :: 1985 Rockwell Data Book" – via Internet Archive.

- ^ "East-European Home-Computer: Bulgaria". HCM: Home Computer Museum. Retrieved 3 October 2020.

- ^ a b http://plus4world.powweb.com/hardware/MOS_75018501 Hardware – MOS 7501/8501

- ^ https://ist.uwaterloo.ca/~schepers/MJK/7501.html CPU 7501 / 8501

- ^ Service Manual C-128/C128D Computer, Commodore Business Machines, PN-314001-08, November 1987

- ^ "Measuring the ROR Bug in the Early MOS 6502". Retrieved 8 May 2011.

- ^ Moser, Carl W. (January 1979). "Add a Trap Vector for Unimplemented 6502 Opcodes" (PDF). Dr. Dobb's Journal of Computer Calisthenics and Orthodontia. No. 31. Menlo Park, California. p. 32. Retrieved 2017-01-07.

- ^ Harrod, Dennette A. (October 1980). "The 6502 Gets Microprogrammable Instructions". BYTE. Vol. 5, no. 10. Peterborough, New Hampshire. p. 282. Retrieved 2017-01-07.

- ^ Draco (19 June 1997). "65c02, 6502, 65816 ??? CPU sells but who's buying..." Archived from the original on 2 January 2008.

- ^ Andrews, Mark (1984). "6". Atari Roots – A Guide To Atari Assembly Language. ISBN 0-88190-171-7.

Bibliography

- Peddle, Chuck (12 June 2014). "Oral History of Chuck Peddle" (Interview). Interviewed by Doug Fairbairn and Stephen Diamond. Archived from the original on 2021-11-18.

- Bagnall, Brian (2010). Commodore, a company on the edge (2nd ed.). Winnipeg, Manitoba: Variant Press. ISBN 978-0-9738649-6-0.

- Bennett, Thomas; Ekiss, John; Lattin, William (Bill); Lavell, Jeff (28 March 2008). "Motorola 6800 Oral History Panel" (PDF) (Interview). Interviewed by David Laws.

- Cushman, Robert H. (September 20, 1975). "2-1/2 Generation μP's -$10 Parts That Perform Like Low-End Mini's" (PDF). EDN. Boston: Cahners Publishing. 20 (17): 36–42. Archived from the original (PDF) on 24 April 2016.

- Interview with William Mensch Stanford and the Silicon Valley Project, October 9, 1995. Transcript

Further reading

- Datasheets and manuals

- 6500 Series Datasheet; MOS Technology; 12 pages; 1976.

- 6500 Series Hardware Manual; 2nd Ed; MOS Technology; 182 pages; 1976.

- 6500 Series Programming Manual; 2nd Ed; MOS Technology; 262 pages; 1976.

- Books

- 6502 Applications Book; 1st Ed; Rodnay Zaks; Sybex; 281 pages; 1979; ISBN 978-0895880154. (archive)

- 6502 Assembly Language Programming; 2nd Ed; Lance Leventhal; Osborne/McGraw-Hill; 650 pages; 1986; ISBN 978-0078812163. (archive)

- 6502 Assembly Language Subroutines; 1st Ed; Lance Leventhal and Winthrop Saville; Osborne/McGraw-Hill; 550 pages; 1982; ISBN 978-0931988592. (archive)

- 6502 Games; 1st Ed; Rodnay Zaks; Sybex; 292 pages; 1980; ISBN 978-0895880222. (archive)

- 6502 User's Manual; 1st Ed; Joseph Carr; Reston; 288 pages; 1984; ISBN 978-0835970020. (archive)

- Advanced 6502 Programming; 1st Ed; Rodnay Zaks; John Wiley & Sons; 292 pages; 1982; ISBN 978-0895880895. (archive)

- Machine Language For Beginners – Personal Computer Machine Language Programming For Atari, VIC, Apple, C64, and PET Computers; 1st Ed; Richard Mansfield; Compute! Publications; 350 pages; 1983; ISBN 978-0942386110. (archive)

- Programming the 6502; 4th Ed; Rodnay Zaks; Sybex; 408 pages; 1983; ISBN 978-0895881359. (archive)

- Programming the 65816 – including the 6502, 65C02, 65802; 1st Ed; David Eyes and Ron Lichty; Prentice Hall; 636 pages; 1986; ISBN 978-0893037895. (archive)

- Reference cards

- 6502 Microprocessor Instant Reference Card; James Lewis; Micro Logic; 2 pages; 1980. (archive)

External links

- 6502.org – the 6502 microprocessor resource – repository

- The Rise of MOS Technology & The 6502 – Commodore archive

- 650x information – Concise description, photos of MOS and second source chips; at cpu-collection.de

- mdfs.net – 6502 instruction set

- Clever, Eric. "6502 – the first RISC µP". Archived from the original on 24 May 2012.

- Harrod, Dennette A. (October 1980). "6502 Gets Microprogrammable Instructions". BYTE. Vol. 5, no. 10. McGraw Hill. pp. 282–285. ISSN 0360-5280. Archived from the original on 2006-05-25. Retrieved 2006-05-14.

- Simulators / Emulators

- Online 6502 compatible assembler and emulator, written in JavaScript Archived 2011-02-08 at the Wayback Machine

- List of 6502 software emulators – Zophar's Domain

- 6502 simulator for Windows – Atari Gaming Headquarters

- Visual Transistor-level Simulation of 6502 CPU

- MCL65 6502 CPU core – C code – MicroCore Labs GitHub

- Boards

- Grant's 7/8-chip 6502 board

- 6502 microprocessor training board

- Build your own KIM-1 training board – see KIM-1

- 6502 home computer

- PE6502 single board computer

- BE6502 single board computer – based on Ben Eater videos

- FPGA

- cpu6502_tc 6502 CPU core – VHDL source code – OpenCores

- ag_6502 6502 CPU core – Verilog source code – OpenCores

- M65C02 65C02 CPU core – Verilog source code – OpenCores

- MCL65 6502 CPU core – Verilog – MicroCore Labs GitHub

![Tamagotchi digital pet[69]](http://upload.wikimedia.org/wikipedia/commons/thumb/f/f2/Tamagotchi_0124_ubt.jpeg/120px-Tamagotchi_0124_ubt.jpeg)