7nm 공정

7 nm process이 기사는 대부분의 독자들이 이해하기에는 너무 기술적인 것일 수 있습니다.(2020년 1월)(이 를 및 |

| 반도체 장치 날조 |

|---|

|

| MOSFET 스케일링 (프로세스 노드) |

| 미래.

|

반도체 제조에서, 국제 반도체 기술 로드맵은 7nm 공정을 10nm 노드 다음의 MOSFET 기술 노드로 정의합니다.멀티게이트 모스펫 기술의 일종인 핀펫(FinFET, 핀 전계효과 트랜지스터) 기술을 기반으로 합니다.

대만 반도체 제조회사(TSMC)는 2016년 6월에 N7이라고 불리는 7nm 공정을 이용한 256 Mbit SRAM 메모리 칩을 생산하기 시작했고,[1] 삼성은 2018년에 7LPP라고 불리는 7nm 공정을 양산하기 시작했습니다.[2]애플 A12 바이오닉은 2018년 9월 애플의 행사에서 처음으로 대중 시장용으로 개발된 7nm 모바일 프로세서입니다.[3]2018년 8월 31일 애플 A12 바이오닉 기린 980 이전에 화웨이가 자체적으로 7nm 프로세서를 발표했지만 애플 A12 바이오닉은 기린 980 이전에 소비자들에게 대중적, 대량 시장용으로 출시되었습니다.두 칩 모두 TSMC에서 제조하였습니다.[4]

2017년 AMD는 서버 및 데이터 센터용 "Rome"(EPYC 2) 프로세서를 출시했는데, 이 프로세서는 TSMC의 N7 노드를[5] 기반으로 하며 최대 64개의 코어와 128개의 스레드를 지원합니다.또한 최대 16개의 코어와 32개의 스레드를 갖춘 "Matise" 소비자용 데스크톱 프로세서도 출시했습니다.그러나 로마 멀티칩 모듈(MCM)의 입출력 다이는 글로벌파운드리의 14nm(14HP) 공정으로 제작된 반면, 마티스의 입출력 다이는 글로벌파운드리의 12nm(12LP+) 공정으로 제작되었습니다.라데온 RX 5000 시리즈 역시 TSMC의 N7 프로세스를 기반으로 합니다.

그러나 적어도 1997년부터 "노드"는 게이트 길이, 금속 피치 또는 게이트 피치와 관련 없이 새로운 세대의 공정 기술을 나타내는 마케팅 목적의[6] 상용 명칭이 되었습니다.[7][8][9]그러나 개별 트랜지스터 내에서 가장 작은 치수인 핀 폭은 7nm가 될 수 있습니다.[10]트랜지스터 밀도에서 TSMC와 삼성의 10nm(10LPE) 공정은 인텔의 14nm와 10nm 공정 사이에 있습니다.

역사

기술 데모

7nm 스케일의 MOSFET은 2000년대 초반에 연구자들에 의해 처음으로 입증되었습니다.2002년에 브루스 도리스, 오메르 도쿠마시, 메이케이 이영 그리고 안다 모쿠타를 포함한 IBM 연구팀은 6 nm 실리콘 온 인슐레이터(SOI) MOSFET을 만들었습니다.[11][12]2003년, 와카바야시 히토시와 야마가미 시게하루가 이끄는 NEC의 연구팀은 5 nm 모스펫을 만들었습니다.[13][14]

2015년 7월, IBM은 실리콘 게르마늄 공정을 사용하여 7nm 기술을 적용한 최초의 기능성 트랜지스터를 개발했다고 발표했습니다.[15][16][17][18]

2016년 6월, TSMC는 7nm 공정에서 256 Mbit SRAM 메모리 셀을 생산했으며 [1]셀 면적은 0.027평방 마이크로미터(550F2)[spelling?]로 합리적인 위험 생산 수율을 보였습니다.[19]

예상되는 상용화 및 기술

2016년 4월, TSMC는 2017년 상반기에 7nm 시험 생산을 시작할 것이라고 발표했습니다.[20]2017년 4월, TSMC는 극자외선 리소그래피([1]EUV)를 이용한 7nm(N7FF+) 공정을 이용한 256 Mbit SRAM 메모리 칩의 위험 생산을 시작했습니다.[21]TSMC의 7nm 생산 계획은 2017년 초에 이 프로세스 노드(N7FF)에 최초로 DUV(딥 자외선) 침지 리소그래피를 사용하고 2017년 2분기부터 2018년 2분기까지 리스크에서 상업용 볼륨 제조로 전환하는 것이었습니다.또한, 그들의 후기 세대 7nm(N7FF+) 생산은 EUV 다중 패터닝을 사용하고 2018년에서 2019년 사이에 위험에서 대량 제조로 예상 전환할 계획입니다.[22]

2016년 9월, GlobalFoundrys는 2017년 하반기에 시험 생산을, 2018년 초에 위험 생산을 발표했으며 테스트 칩은 이미 실행 중입니다.[23]

2017년 2월, 인텔은 애리조나주 챈들러(Chandler)에서 7nm(Intel 4[24]) 제조 공정을 사용하여 마이크로프로세서를 생산할 것이라고 발표했습니다.[25]회사는 이 프로세스 노드에서 피쳐 길이에 대한 예상 값을 게시하지 않았습니다.

2018년 4월, TSMC는 7nm(CLN7FF, N7) 칩의 대량 생산을 발표했습니다.2018년 6월, 그 회사는 대량 생산 증가를 발표했습니다.[2]

2018년 5월, 삼성은 올해 7nm(7LPP) 칩 생산을 발표했습니다.ASML Holding NV는 EUV 리소그래피 기계의 주요 공급업체입니다.[26]

2018년 8월, 글로벌파운드리는 비용을 이유로 7nm 칩의 개발을 중단한다고 발표했습니다.[27]

2018년 10월 28일, 삼성은 2세대 7nm 공정(7LPP)이 위험 생산에 들어갔으며 2019년에 양산에 들어갈 것이라고 발표했습니다.

2019년 1월 17일, TSMC는 2018년 4분기 실적 발표에서 고객마다 7nm의 2세대 "다른 맛"을 가질 것이라고 언급했습니다.[28]

2019년 4월 16일, TSMC는 2021년부터 양산될 것으로 예상되는 6nm 공정(CLN6FF, N6)을 발표했습니다.[29]N6는 EUVL을 최대 5 계층으로 사용하는데 비해 N7+ 프로세스에서는 최대 4 계층으로 사용합니다.[30]

2019년 7월 28일, TSMC는 N7 공정과 마찬가지로 DUV 기반인 N7P라고 불리는 두 번째 7세대 공정을 발표했습니다.[31]N7P는 원래의 7nm와 완전히 IP 호환되는 반면 N7+(EUV 사용)는 그렇지 않기 때문에 N7+(이전에 '7nm+'로 발표됨)는 '7nm'와 별개의 프로세스입니다.EUV 기반의 또 다른 공정인 N6('6nm')은 TSMC의 5nm(N5) 공정보다도 늦게 출시될 예정이며, N7과 IP 호환성이 있습니다.TSMC는 2019년 1분기 실적 발표에서 N7+가 2019년에 10억 달러 미만의 수익을 창출할 것이라고 2018년 4분기 발표했습니다[28].[32]

2019년 10월 5일, AMD는 TSMC의 N7+ 프로세스를 사용하여 제작된 밀라노 칩을 특징으로 하는 EPYC Roadmap을 발표했습니다.[33]

2019년 10월 7일, TSMC는 N7+ 제품을 대량으로 시장에 공급하기 시작했다고 발표했습니다.[34]

2021년 7월 26일, 인텔은 향후 프로세스 노드의 이름을 모두 변경하는 새로운 제조 로드맵을 발표했습니다.[24]TSMC의 N7 공정과 거의 맞먹는 인텔의 10nm Enhanced SuperF(10ESF)는 이제 인텔 7로 불리고, 그들의 초기 7nm 공정은 이제 인텔 4로 불립니다.[24][35]이에 따라 인텔 7을 기반으로 한 인텔의 첫 번째 프로세서는 2022년 하반기에 출시될 예정이며, 인텔은 앞서 2023년에 7nm 프로세서를 출시할 것이라고 발표했습니다.[36]

기술사업화

2018년 6월 AMD는 2018년 하반기에 7nm 라데온 인스팅트 GPU를 출시한다고 발표했습니다.[37]2018년 8월, 이 회사는 GPU의 출시를 확정했습니다.[38]

2018년 8월 21일, 화웨이는 자사의 하이실리콘 기린 980 SoC를 TSMC의 7nm(N7) 공정을 이용하여 제조한 화웨이 메이트 20 및 메이트 20 프로에 사용할 것이라고 발표했습니다.

2018년 9월 12일, 애플은 아이폰 XS와 아이폰 XR에 TSMC의 7nm(N7) 공정으로 만들어진 A12 바이오닉 칩을 발표했습니다.A12 프로세서는 화웨이 메이트 20보다 먼저 출시되면서 대량 시장에 사용되는 최초의 7nm 칩이 되었습니다.[39][40]2018년 10월 30일, 애플은 TSMC의 7nm(N7) 공정으로 제작된 아이패드 프로에 사용되는 A12X 바이오닉 칩을 발표했습니다.[41]

2018년 12월 4일, Qualcomm은 TSMC의 7nm(N7) 공정을 사용하여 만들어진 스냅드래곤 855 및 8cx를 발표했습니다.[42]2018년 12월 18일에 발표된 레노버 Z5 프로 GT는 스냅드래곤 855를 탑재한 최초의 양산품입니다.[43]

2019년 5월 29일 미디어Tek는 TSMC 7nm 공정을 이용해 구축한 5G SoC를 발표했습니다.[44]

2019년 7월 7일, AMD는 TSMC 7nm 공정과 젠2 마이크로아키텍처를 기반으로 한 라이젠 3000 시리즈의 중앙 처리 장치를 공식 출시했습니다.

2019년 8월 6일, 삼성은 자사의 7LPP 공정을 이용하여 제작된 최초의 칩인 엑시노스 9825 SoC를 발표했습니다.엑시노스 9825는 EUVL을 탑재한 최초의 대중 시장용 칩입니다.[45]

2019년 9월 6일, 화웨이는 TSMC의 N7 및 N7+ 공정을 사용하여 구축된 HiSilicon Kirin 990 4G 및 990 5G SoC를 발표했습니다.[46]

2019년 9월 10일, 애플은 TSMC의 2세대 N7P 공정을 이용하여 제조된 아이폰 11과 아이폰 11 프로에 사용되는 A13 바이오닉 칩을 발표했습니다.[47]

2020년 2분기 TSMC 매출은 7nm(N7노드) 제조가 36%를 차지했습니다.[48]

2020년 8월 17일, IBM은 파워10 프로세서를 발표했습니다.[47]

2021년 7월 26일, 인텔은 올더레이크 프로세서를 10nm 인핸스드 슈퍼핀(10nm Enhanced SuperFin)이라는 새로운 브랜드의 인텔 7 공정을 사용하여 제조할 것이라고 발표했습니다.[24]이 프로세서들은 2021년 하반기에 출시될 예정입니다.이 회사는 앞서 현재 인텔 4로 불리는 [24]7nm 마이크로프로세서 제품군인 '메트로 레이크'가 2023년에 출시될 예정입니다.[49][50]

7nm 패터닝 어려움

7nm 주조 공장 노드는 피치 분할, 자체 정렬 패터닝 및 EUV 리소그래피와 같은 패터닝 기술 중 하나 또는 이들의 조합을 활용할 것으로 예상됩니다.이러한 각각의 기술은 주변 기능을 모두 포함하는 패턴 배치뿐만 아니라 임계 치수(CD) 제어에 있어서 상당한 과제를 안고 있습니다.

피치 분할

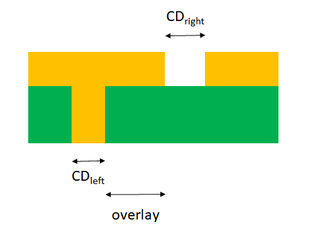

피치 분할(pitch spliting)은 너무 가까이 있는 특징들을 서로 다른 마스크들에 분할하는 것을 수반하며, 이 마스크들은 연속적으로 노출되고, 이어서 리소-에칭 처리가 뒤따릅니다.서로 다른 노출을 사용하기 때문에 두 노출 사이에는 항상 오버레이 오류가 발생할 위험이 있으며 다른 노출로 인해 발생하는 서로 다른 CD도 있습니다.

스페이서패턴

스페이서 패터닝은 미리 패터닝된 피처들 상에 층을 증착하고, 그 피처들의 측벽들 상에 스페이서들(core feature)을 형성하기 위해 다시 에칭하는 것을 포함합니다.핵심 특징을 제거한 후 스페이서를 식각 마스크로 사용하여 기본 레이어의 트렌치를 정의합니다.스페이서 CD 제어는 일반적으로 우수하지만, 트렌치 CD는 코어 피쳐가 위치한 곳에 위치하거나 나머지 갭에 위치할 수 있는 두 가지 가능성으로 인해 두 모집단 중 하나에 속할 수 있습니다.이것은 'pitch walking' 이라고 알려져 있습니다.[51]일반적으로 피치 = 코어 CD + 갭 CD + 2 * 스페이서 CD를 사용하지만 코어 CD = 갭 CD를 보장하지는 않습니다.게이트 또는 활성 영역 격리(예컨대, 핀)와 같은 FEOL 특징들의 경우, 트렌치 CD는 스페이서 정의 CD만큼 중요하지 않으며, 이 경우 스페이서 패터닝이 실제로 바람직한 패터닝 방법입니다.

SAQP(self-aligned quadruple patterning)를 사용하는 경우, 첫 번째 스페이서를 대체하는 두 번째 스페이서가 사용됩니다.이 경우, Core CD는 Core CD - 2* 2차 스페이서 CD로 대체되며, Gap CD는 Gap CD - 2* 2차 스페이서 CD로 대체됩니다.따라서 일부 피쳐 치수는 두 번째 스페이서 CD에 의해 엄격하게 정의되고 나머지 피쳐 치수는 코어 CD, 코어 피치 및 첫 번째 및 두 번째 스페이서 CD에 의해 정의됩니다.코어 CD와 코어 피치는 종래의 리소그래피에 의해 정의되는 반면, 스페이서 CD는 리소그래피와 독립적입니다.이는 실제로 추가 노출이 직접 또는 오버레이를 통해 자신의 CD를 정의하는 피치 분할보다 변동이 적을 것으로 예상됩니다.

스페이서 정의 선 또한 절단이 필요합니다.절단된 스폿이 노출 시 이동하여 라인 끝이 왜곡되거나 인접 라인에 침입할 수 있습니다.

7 nm BEOL 패터닝을 위해 자가 정렬된 리소에치 리소에치(SALLE)가 구현되었습니다.[52]

EUV 리소그래피

극자외선 리소그래피(EUV 또는 EUVL이라고도 함)는 일반적인 리소그래피 스타일에서 20 nm 미만의 특성을 해결할 수 있습니다.그러나 EUV 마스크의 3D 반사 특성으로 인해 영상에 새로운 이상이 발생합니다.한 가지 특별한 골칫거리는 동일한 막대 모양의 한 쌍이 동일하게 초점을 맞추지 않는 두 개의 막대 효과입니다.한 기능은 본질적으로 다른 기능의 '그림자'에 있습니다.따라서 두 기능은 일반적으로 초점을 통해 변화하는 서로 다른 CD를 가지고 있으며 이러한 기능은 초점을 통해 위치를 이동합니다.[53][54][55]이러한 효과는 피치 분할 시 발생할 수 있는 것과 유사할 수 있습니다.이와 관련된 문제는 서로 다른 구종의 특징들 간의 최상의 초점 차이입니다.[56]

EUV는 또한 많은 수의 모든 기능을 안정적으로 인쇄하는 데 문제가 있습니다. 일부 연락처가 완전히 없거나 회선이 연결되어 있을 수도 있습니다.이를 확률적 인쇄 실패라고 합니다.[57][58]불량수준은 1K/mm2 수준입니다.[59]

EUV의 경우 주로 조명 제약으로 인해 팁-투-팁 갭을 제어하기가 어렵습니다.[60]절단선에 대해서는 별도의 노출이 좋습니다.

감쇠된 위상 이동 마스크는 ArF 레이저 파장(193 nm)과 임의로 피치된 접촉을 위한 적절한 포커스 윈도우를 위해 90 nm 노드에 대해 생산에 사용되었지만,[61][62] EUV에서는 이러한 해상도 향상을 사용할 수 없습니다.[63][64]

2021년 SPIE의 EUV 리소그래피 컨퍼런스에서 TSMC 고객은 EUV 접촉 수율이 몰입 멀티패터닝 수율과 유사하다고 보고했습니다.[65]

이전 노드와의 비교

이러한 문제로 인해, 7nm는 BEOL(Back End of Line)에서 전례 없는 패터닝 어려움을 야기합니다.이전의 대용량, 수명이 긴 파운드리 노드(Samsung 10 nm, TSMC 16 nm)는 더 단단한 피치 금속층을 위해 피치 분할을 사용했습니다.[66][67][68]

주기 시간: 몰입 대 EUV

| 과정 | 침지 (≥ 275 WPH) | EUV(1,500 웨이퍼/일)[70] |

|---|---|---|

| 단일 패턴 레이어: 침지에 의한 1일 | 웨이퍼/일 6000장 | 웨이퍼/일 1500장 |

| 이중 패턴 레이어: 침지로 2일 완료 | 6000 웨이퍼/2일 | 3000 웨이퍼/2일 |

| 3중 패턴 레이어: 3일간 침지 완료 | 6000 웨이퍼/3일 | 웨이퍼 4500장/3일 |

| 쿼드 패턴 레이어: 침지로 4일 완료 | 웨이퍼 6000장/4일 | 웨이퍼 6000장/4일 |

현재 몰입 도구의 속도가 빨라졌기 때문에, 다중 패턴화는 여전히 대부분의 층에서 사용됩니다.몰입 쿼드-패터닝이 필요한 층들에서, EUV에 의한 층 완성 처리량은 유사합니다.다른 층들에서는, 몰입이 멀티패터닝을 통해서도 층을 완성하는데 더 생산적일 것입니다.

7nm 설계 규칙 관리(양적 생산 시)

TSMC가 현재 실행하고 있는 7nm 금속 패터닝은 셀 높이를 줄이기 위해 필요에 따라 별도의 마스크의 셀 내에 컷이 삽입된 자가 정렬 이중 패터닝(SADP) 라인을 포함합니다.[71]그러나 성능에 가장 중요한 요소인 핀을 형성하기 위해 SAQP(self-aligned quad patterning)가 사용됩니다.[72]또한 설계 규칙 검사를 통해 다중 패턴화를 방지할 수 있으며 절단 마스크가 하나만 필요할 만큼 충분한 간격을 확보할 수 있습니다.[72]

7nm 프로세스 노드 및 프로세스 제품

이 부분의 사실적 정확성은 논란의 여지가 있습니다.(2023년 9월)(이 를 및 |

4개의 다른 제조업체(TSMC, 삼성, SMIC, Intel)가 프로세스 노드를 명명하는 것은 부분적으로 마케팅 중심이며 칩 상의 측정 가능한 거리와 직접적인 관련이 없습니다. 예를 들어, TSMC의 7nm 노드는 Intel이 추가 반복을 발표하기 전에 Intel의 계획된 10nm 노드와 일부 주요 차원에서 유사했습니다.10nm Enhanced SuperFin의 Tating은 마케팅의 이유로 나중에 인텔 7로 이름이 변경되었습니다.[73][74]

7nm에서의 EUV 구현은 여전히 제한적이기 때문에, 멀티패터닝은 여전히 비용과 수율에 중요한 역할을 합니다. EUV는 추가적인 고려 사항을 추가합니다.대부분의 중요 계층의 해상도는 여전히 다중 패터닝에 의해 결정됩니다.예를 들어, 삼성의 7nm의 경우 EUV 단일 패턴의 36nm 피치 레이어를 사용하더라도 44nm 피치 레이어는 여전히 4중 패턴으로 처리됩니다.[75]

| 삼성 | TSMC | 인텔 | SMIC | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 공정명 | 7LPP[76][77] | 6LPP[78] | N7[79] | N7P[31] | N7+[80] | N6 | 인텔 7[24][disputed ] (10nm)[81] | N+1 (>7nm) | N+2 (7nm) | 7nm EUV |

| 트랜지스터밀도(MTR/mm2) | 95.08–100.59[82][83] | 112.79 | 91.2–96.5[84][85] | 113.9[84] | 114.2[29] | 100.76–106.1[86][87] 60.41[88] | 89[89] | 113.6[90] | 알 수 없는 | |

| SRAM 비트셀 크기 | 0.0262 μm2[91] | 알 수 없는 | 0.027 μm2[91] | 알 수 없는 | 알 수 없는 | 0.0312 μm2 | 알 수 없는 | 알 수 없는 | 알 수 없는 | |

| 트랜지스터 게이트 피치 | 54nm | 알 수 없는 | 57nm | 알 수 없는 | 알 수 없는 | 54nm | 알 수 없는 | 알 수 없는 | 알 수 없는 | |

| 트랜지스터 핀 피치 | 27nm | 알 수 없는 | 해당 없음 | 알 수 없는 | 알 수 없는 | 34nm | 알 수 없는 | 알 수 없는 | 알 수 없는 | |

| 트랜지스터 핀 높이 | 알 수 없는 | 알 수 없는 | 해당 없음 | 알 수 없는 | 알 수 없는 | 53nm | 알 수 없는 | 알 수 없는 | 알 수 없는 | |

| 최소(금속) 피치 | 46nm | 알 수 없는 | 40nm | < 40nm | 알 수 없는 | 40nm[92] | 알 수 없는 | 42nm | 알 수 없는 | |

| EUV 이행 | 36 nm 피치 금속,[75] 전체 레이어 세트의 20% | 알 수 없는 | 없음, SAQP(self-aligned quad patterning) 대신 사용 | 4단 | 5단 | 없어요 SAQP에 많이 의존했어요 | 없음. | 없음. | 예(N+2 이후) | |

| EUV 제한 웨이퍼 출력 | 웨이퍼/일[70] 1500장 | 알 수 없는 | 해당 없음 | ~ 1,000 웨이퍼/일[93] | 알 수 없는 | 해당 없음 | 알 수 없는 | 알 수 없는 | 알 수 없는 | |

| 멀티패터닝 (≥ 마스크 2장을 겹겹이) | 핀 게이트 비아(이중패턴)[94] 메탈1(트리플패턴)[94] 44nm 피치 금속 (quad-patterned) | 알 수 없는 | 핀 게이트 연락처/비아(4각형 패턴)[95] 가장 낮은 10개의 금속 층 | N7과 동일, 4개의 EUV 계층에서 축소 | N7과 동일, 5개의 EUV 계층에서 감소 | DUV를 사용한 다중 패턴화 | DUV를 사용한 다중 패턴화 | 알 수 없는 | ||

| 출고여부 | 2018년 리스크 생산 2019년생산 | 2020년 생산 | 2017년 리스크 생산 2018년생산[1] | 2019년생산 | 2018년 리스크 생산[1] 2019년생산 | 2020년 리스크 생산 2020년 생산 | 2021년 생산량[24] | 2021년 4월 리스크 생산, 양산 미상 | 2021년 후반 리스크 생산, 2021년[96] 7월 이후 조용히 생산 | 미국 금수 조치로 인해 연기됨 |

GlobalFoundries의 7nm 7LP(Leading Performance) 공정은 밀도가 2배 증가하고 다이당 비용이 14nm 공정에 비해 30-45% 이상 낮으면서 40% 더 높은 성능 또는 60% 이상 더 낮은 전력을 제공했을 것입니다.접촉된 폴리 피치(CPP)는 56 nm, 최소 금속 피치(MMP)는 40 nm로 SADP(Self-Aligned Double Patterning)로 제조되었을 것입니다.6T SRAM 셀의 크기는 0.269 제곱 마이크론일 것입니다.GlobalFoundrys는 EUV 리소그래피를 7LP+[97]라는 개선된 공정에 사용할 계획이었습니다.이후 GlobalFoundrys는 7nm 이상의 모든 공정 개발을 중단했습니다.[98]

이전에 10nm Enhanced SuperF(10ESF)로 알려진 인텔의 새로운 "인텔 7" 프로세스는 이전의 10nm 노드를 기반으로 합니다.노드는 와트당 성능이 10-15% 향상됩니다.한편, 현재 "인텔 4"라고 불리는 그들의 오래된 7nm 공정은 2023년에 출시될 것으로 예상됩니다.[99]인텔 4 노드에 대한 세부 정보는 거의 공개되지 않았지만, 트랜지스터 밀도는 제곱 밀리미터당 최소 2억 2백만 개의 트랜지스터로 추정됩니다.[24][100]2020년 현재 인텔은 폰테 베키오 GPU의 생산을 아웃소싱할 정도로 인텔 4 프로세스에 문제를 겪고 있습니다.[101][102]

참고문헌

- ^ a b c d e "7nm Technology". TSMC. Retrieved June 30, 2019.

- ^ a b Chen, Monica; Shen, Jessie (June 22, 2018). "TSMC ramping up 7nm chip production". DigiTimes. Retrieved September 17, 2022.

- ^ Shankland, Stephen (September 12, 2018). "Apple's A12 Bionic CPU for the new iPhone XS is ahead of the industry moving to 7nm chip manufacturing tech". CNET. Retrieved September 16, 2018.

- ^ Summers, N. (September 12, 2018). "Apple's A12 Bionic is the first 7-nanometer smartphone chip". Engadget. Retrieved September 20, 2018.

- ^ Smith, Ryan (July 26, 2018). "AMD "Rome" EPYC CPUs to Be Fabbed By TSMC". AnandTech. Retrieved June 18, 2019.

- ^ Morris, Kevin (July 23, 2020). "No More Nanometers: It's Time for New Node Naming". Electronic Engineering Journal. Retrieved September 17, 2022.

- ^ Shukla, Priyank. "A Brief History of Process Node Evolution". Design-Reuse. Retrieved July 9, 2019.

- ^ Hruska, Joel (June 23, 2014). "14nm, 7nm, 5nm: How low can CMOS go? It depends if you ask the engineers or the economists…". ExtremeTech. Retrieved September 17, 2022.

- ^ Pirzada, Usman (September 16, 2016). "Exclusive: Is Intel Really Starting To Lose Its Process Lead? 7nm Node Slated For Release in 2022". Wccftech. Retrieved September 17, 2022.

- ^ Kanter, David (June 12, 2022). "Intel 4 Process Scales Logic with Design, Materials, and EUV". realworldtech.com. Retrieved September 24, 2023.

- ^ "IBM claims world's smallest silicon transistor - TheINQUIRER". Theinquirer.net. December 9, 2002. Archived from the original on May 31, 2011. Retrieved December 7, 2017.

- ^ Doris, Bruce B.; Dokumaci, Omer H.; Ieong, Meikei K.; Mocuta, Anda; Zhang, Ying; Kanarsky, Thomas S.; Roy, R. A. (December 2002). "Extreme scaling with ultra-thin Si channel MOSFETs". Digest. International Electron Devices Meeting. pp. 267–270. doi:10.1109/IEDM.2002.1175829. ISBN 0-7803-7462-2. S2CID 10151651.

- ^ "NEC test-produces world's smallest transistor". The Free Library. Retrieved December 7, 2017.

- ^ Wakabayashi, Hitoshi; Yamagami, Shigeharu; Ikezawa, Nobuyuki; Ogura, Atsushi; Narihiro, Mitsuru; Arai, K.; Ochiai, Y.; Takeuchi, K.; Yamamoto, T.; Mogami, T. (December 2003). "Sub-10-nm planar-bulk-CMOS devices using lateral junction control". IEEE International Electron Devices Meeting 2003. pp. 20.7.1–20.7.3. doi:10.1109/IEDM.2003.1269446. ISBN 0-7803-7872-5. S2CID 2100267.

- ^ Dignan, Larry. "IBM Research builds functional 7nm processor". ZDNet.

- ^ Markoff, John (July 9, 2015). "IBM Discloses Working Version of a Much Higher-Capacity Chip". The New York Times.

- ^ "Beyond silicon: IBM unveils world's first 7nm chip – Ars Technica". arstechnica.com. July 9, 2015.

- ^ "Seven Advancements for Beyond 7nm Chips". IBM Research Blog. February 27, 2017.

- ^ Chang, J.; Chen, Y.; Chan, W.; Singh, S. P.; Cheng, H.; Fujiwara, H.; Lin, J.; Lin, K.; Hung, J.; Lee, R.; Liao, H. (February 2017). "12.1 a 7nm 256Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-VMIN applications". 2017 IEEE International Solid-State Circuits Conference (ISSCC). pp. 206–207. doi:10.1109/ISSCC.2017.7870333. ISBN 978-1-5090-3758-2. S2CID 19930825.

- ^ Parish, Kevin (April 20, 2016). "Watch out Intel and Samsung: TSMC is gearing up for 7 nm processing with trial production". Digital Trends. Retrieved September 17, 2022.

- ^ "TSMC Tips 7+, 12, 22nm Nodes EE Times". EETimes. Retrieved March 17, 2017.

- ^ Shilov, Anton (May 5, 2017). "Samsung and TSMC Roadmaps: 8 and 6 nm Added, Looking at 22ULP and 12FFC". AnandTech. Retrieved September 17, 2022.

- ^ "GLOBALFOUNDRIES to Deliver Industry's Leading-Performance Offering of 7 nm FinFET Technology". GlobalFoundries (Press release). September 15, 2016. Retrieved April 8, 2017.

- ^ a b c d e f g h Cutress, Ian. "Intel's Process Roadmap to 2025: with 4nm, 3nm, 20A and 18A?!". www.anandtech.com. Retrieved July 27, 2021.

- ^ "Intel Supports American Innovation with $7 Billion Investment in Next-Generation Semiconductor Factory in Arizona". Intel Newsroom. February 8, 2017. Retrieved September 17, 2022.

- ^ King, Ian (May 22, 2018). "Samsung Says New 7-Nanometer Chip Production Starting This Year". Bloomberg. Retrieved September 17, 2022.

- ^ Dent, Steve (August 28, 2018). "Major AMD chip supplier will no longer make next-gen chips". Engadget. Retrieved September 17, 2022.

- ^ a b 2018년 4분기 TSMC 실적 콜 녹취록, 2019년 1월 17일

- ^ a b Schor, David (April 16, 2019). "TSMC Announces 6-Nanometer Process". WikiChip Fuse. Retrieved May 31, 2019.

- ^ Shilov, Anton (May 1, 2019). "TSMC: Most 7nm Clients Will Transition to 6nm". AnandTech. Retrieved May 31, 2019.

- ^ a b Schor, David (July 28, 2019). "TSMC Talks 7nm, 5nm, Yield, And Next-Gen 5G And HPC Packaging". WikiChip Fuse. Retrieved September 13, 2019.

- ^ C. C. Wei, TSMC 2019년 1분기 실적 발표(4월 18일) 녹취록

- ^ Alcorn, Paul (October 5, 2019). "AMD Dishes on Zen 3 and Zen 4 Architecture, Milan and Genoa Roadmap". Tom's Hardware. Retrieved October 8, 2019.

- ^ "TSMC's N7+ Technology is First EUV Process Delivering Customer Products to Market in High Volume Planet 3DNow!" (in German). October 7, 2019. Retrieved October 8, 2019.

- ^ "Accelerating Process Innovation" (PDF). Intel. July 26, 2021.

- ^ Jones, Ryan (March 27, 2021). "Ctrl+Alt+Delete: Why you should be excited for Intel's 7nm processor". Trusted Reviews. Retrieved March 30, 2021.

- ^ "Pushing Boundaries for CPUs and GPUs, AMD Shows Next-Generation of Ryzen, Radeon and EPYC Product Leadership at Computex 2018" (Press release). June 5, 2018.

- ^ Martin, Dylan (August 23, 2018). "AMD CTO: 'We Went All In' On 7nm CPUs". CRN. Retrieved September 17, 2022.

- ^ "Apple Announces 'iPhone Xs' and 'iPhone Xs Max' With Gold Color, Faster Face ID, and More". September 12, 2018.

- ^ Freedman, Andrew E. (September 12, 2018). "Apple Introduces 7nm A12 Bionic CPU for iPhone XS". Tom's Hardware. Retrieved September 12, 2018.

- ^ Axon, Samuel (November 7, 2018). "Apple walks Ars through the iPad Pro's A12X system on a chip". Ars Technica. Retrieved November 18, 2018.

- ^ Cutress, Ian (December 4, 2018). "Qualcomm Tech Summit, Day 1: Announcing 5G Partnerships and Snapdragon 855". AnandTech. Retrieved May 31, 2019.

- ^ Frumusanu, Andrei (December 18, 2018). "Lenovo First to a Snapdragon 855 Phone with Announcement of Z5 Pro GT". AnandTech. Retrieved May 31, 2019.

- ^ "MediaTek 5G". MediaTek. Retrieved May 31, 2019.

- ^ Siddiqui, Aamir (August 7, 2019). "Samsung announces Exynos 9825 prior to Galaxy Note 10 launch". XDA-Developers. Retrieved September 13, 2019.

- ^ Cutress, Ian. "Huawei Announces Kirin 990 and Kirin 990 5G: Dual SoC Approach, Integrated 5G Modem". AnandTech. Retrieved September 13, 2019.

- ^ a b "IBM Reveals Next-Generation IBM POWER10 Processor". IBM Newsroom. August 17, 2020. Retrieved August 17, 2020.

- ^ "TSMC Plots an Aggressive Course for 3nm Lithography and Beyond - ExtremeTech".

- ^ "Intel CEO Announces 'IDM 2.0' Strategy for Manufacturing, Innovation". Intel Newsroom. March 23, 2021. Retrieved September 17, 2022.

- ^ "Intel Unleashed: Engineering the Future (Replay)". Intel Newsroom. March 23, 2021. Retrieved September 17, 2022.

- ^ M. J. 매슬로우 외, Proc.SPIE 10587, 1058704 (2018).

- ^ 7nm 및 5nm 노드에 대한 SALLE 이중 패터닝

- ^ "IMEC EUVL 2018 Workshop" (PDF).

- ^ Y. 나카지마 외, EUVL 심포지엄 2007, 삿포로.

- ^ L. de Winter et al., Proc.SPIE 9661, 96610A (2015).

- ^ M. 버크하르트와 A.라구나탄, 프록.SPIE 9422, 94220X (2015).

- ^ P. 드 비숍과 E.헨드릭스, 프록.SPIE 10583, 105831K (2018).

- ^ "EUV's Stochastic Valley of Death". linkedin.com.

- ^ S. Larivière et al., Proc.SPIE 10583, 105830U (2018).

- ^ E. 반 세튼 외, 프록.SPIE 9661. 96610G (2015).

- ^ C-H. Chang 등, Proc.SPIE 5377, 902 (2004).

- ^ T. Devoivre et al., MTD 2002.

- ^ S-S. Yu 외, Proc.SPIE 8679, 86791L (2013).

- ^ A. Erdmann et al., Proc.SPIE 10583, 1058312 (2018).

- ^ 치 리 외, 프록.SPIE 11609, 116090V (2021).

- ^ Jeong, W. C.; Ahn, J. H.; Bang, Y. S.; Yoon, Y. S.; Choi, J. Y.; Kim, Y. C.; Paek, S. W.; Ahn, S. W.; Kim, B. S.; Song, T. J.; Jung, J. H.; Do, J. H.; Lim, S. M.; Cho, H.-; Lee, J. H.; Kim, D. W.; Kang, S. B.; Ku, J.-; Kwon, S. D.; Jung, S.-; Yoon, J. S. (June 23, 2017). "10nm 2nd generation BEOL technology with optimized illumination and LELELELE". 2017 Symposium on VLSI Technology. pp. T144–T145. doi:10.23919/VLSIT.2017.7998156. ISBN 978-4-86348-605-8. S2CID 43207918 – via IEEE Xplore.

- ^ "TSMC Symposium: "10nm is Ready for Design Starts at This Moment" - Industry Insights - Cadence Blogs - Cadence Community". community.cadence.com.

- ^ Wu, S.; Lin, C. Y.; Chiang, M. C.; Liaw, J. J.; Cheng, J. Y.; Yang, S. H.; Liang, M.; Miyashita, T.; Tsai, C. H.; Hsu, B. C.; Chen, H. Y.; Yamamoto, T.; Chang, S. Y.; Chang, V. S.; Chang, C. H.; Chen, J. H.; Chen, H. F.; Ting, K. C.; Wu, Y. K.; Pan, K. H.; Tsui, R. F.; Yao, C. H.; Chang, P. R.; Lien, H. M.; Lee, T. L.; Lee, H. M.; Chang, W.; Chang, T.; Chen, R.; Yeh, M.; Chen, C. C.; Chiu, Y. H.; Chen, Y. H.; Huang, H. C.; Lu, Y. C.; Chang, C. W.; Tsai, M. H.; Liu, C. C.; Chen, K. S.; Kuo, C. C.; Lin, H. T.; Jang, S. M.; Ku, Y. (December 23, 2013). "A 16nm FinFET CMOS technology for mobile SoC and computing applications". 2013 IEEE International Electron Devices Meeting. pp. 9.1.1–9.1.4. doi:10.1109/IEDM.2013.6724591. ISBN 978-1-4799-2306-9 – via IEEE Xplore.

- ^ "Products & services - Supplying the semiconductor industry". asml.com.

- ^ a b "Samsung Ramps 7nm EUV Chips". EETimes. October 17, 2018.

- ^ "7 nm lithography process - WikiChip".

- ^ a b "A Heuristic Approach to Fix Design Rule Check (DRC) Violations in ASIC Designs @7nm FinFET Technology". Design And Reuse.

- ^ Merrit, Rick (January 16, 2017). "15 Views from a Silicon Summit". EETimes. Retrieved September 16, 2022.

- ^ Hill, Brandon (March 28, 2017). "Intel Details Cannonlake's Advanced 10nm FinFET Node, Claims Full Generation Lead Over Rivals". HotHardware. Archived from the original on June 12, 2018. Retrieved August 30, 2018.

- ^ a b c J. Kim 등, Proc.SPIE 10962, 1096204 (2019).

- ^ "VLSI 2018: Samsung's 2nd Gen 7nm, EUV Goes HVM". WikiChip. August 4, 2018. Retrieved September 16, 2022.

- ^ "Samsung Electronics Starts Production of EUV-based 7nm LPP Process". Samsung Newsroom. October 18, 2018. Retrieved September 16, 2022.

- ^ "Samsung Starts Mass Production at V1: A Dedicated EUV Fab for 7nm, 6nm, 5nm, 4nm, 3nm Nodes".

- ^ IEDM 2016

- ^ "TSMC Goes Photon to Cloud". EETimes. October 4, 2018.

- ^ Bonshor, Gavin (October 20, 2022). "Intel Core i9-13900K and i5-13600K Review: Raptor Lake Brings More Bite". AnandTech. Retrieved September 28, 2023.

- ^ "Can TSMC Maintain Their Process Technology Lead". July 18, 2023.

- ^ "Samsung 3nm GAAFET Enters Risk Production; Discusses Next-Gen Improvements". July 5, 2022.

- ^ a b Jones, Scotten (May 3, 2019). "TSMC and Samsung 5nm Comparison". Semiwiki. Retrieved July 30, 2019.

- ^ "N3E Replaces N3; Comes in Many Flavors". September 4, 2022.

- ^ Jones, Scotten (July 18, 2023), Can TSMC Maintain Their Process Technology Lead

- ^ "Intel's Process Roadmap to 2025: With 4nm, 3nm, 20A and 18A?!".

- ^ Schor, David (June 19, 2022). "A Look At Intel 4 Process Technology". WikiChip Fuse.

- ^ SMIC Mass Produces 14nm Nodes, Advances To 5nm, 7nm, September 16, 2022

- ^ "百度安全验证". wappass.baidu.com. Retrieved September 6, 2023.

- ^ a b "VLSI 2018: Samsung's 2nd Gen 7nm, EUV Goes HVM". WikiChip Fuse. August 4, 2018. Retrieved May 31, 2019.

- ^ Smith, Ryan (June 13, 2022). "Intel 4 Process Node In Detail: 2x Density Scaling, 20% Improved Performance". AnandTech. Retrieved September 17, 2022.

- ^ "TSMC Q1 2018 earnings call transcript, p.12" (PDF). Archived from the original (PDF) on October 14, 2018. Retrieved October 14, 2018.

- ^ a b W. C. 정 외, VLSI Technology 2017

- ^ Dillinger, Tom (March 23, 2017). "Top 10 Updates from the TSMC Technology Symposium, Part II". SemiWiki. Retrieved September 16, 2022.

- ^ Paul Alcorn (July 21, 2022). "China's SMIC Shipping 7nm Chips, Reportedly Copied TSMC's Tech". Tom's Hardware.

- ^ Jones, Scotten (July 8, 2017). "Exclusive - GLOBALFOUNDRIES discloses 7nm process detail". SemiWiki. Retrieved September 16, 2022.

- ^ Shilov, Anton; Cutress, Ian (August 27, 2018). "GlobalFoundries Stops All 7nm Development: Opts To Focus on Specialized Processes". AnandTech. Retrieved July 27, 2021.

- ^ "Intel: Sorry, But Our 7nm Chips Will Be Delayed to 2022, 2023". PCMAG. Retrieved July 27, 2021.

- ^ "7 nm lithography process - WikiChip".

- ^ "Intel's 7nm Process Six Months Behind Schedule - News".

- ^ "As 7nm schedule continues slipping, Intel contemplates 3rd-party fabs". July 24, 2020.

외부 링크

| 앞에 10nm | MOSFET 반도체 소자 제작 공정 | 승계인 5nm |