인텔 QuickPath 인터커넥트

Intel QuickPath Interconnect이 문서는 갱신할 필요가 있습니다.(2014년 1월) |

인텔 QuickPath Interconnect (QPI)[1][2]는 인텔이 개발한 포인트 투 포인트 프로세서 인터커넥트로 2008년부터 Xeon, Itanium 및 특정 데스크톱 플랫폼의 프론트 사이드 버스 (FSB)를 대체하였습니다.확장성과 사용 가능한 대역폭이 향상되었습니다.이 명칭이 발표되기 전에 인텔에서는 Common System Interface (CSI;[3] 공통 시스템 인터페이스)라고 불렀습니다.이전에는 Yet Another Protocol(YAP) 및 YAP+로 알려져 있었습니다.

QPI 1.1은 Sandy Bridge-EP(Romley 플랫폼)[4]에서 대폭 개량된 버전입니다.

QPI는 LGA 3647 [5]소켓 기반의 Skylake-SP Xeon 프로세서에서 Intel Ultra Path Interconnect(UPI)로 대체되었습니다.

배경

QPI는 '버스'라고도 불리지만 포인트 투 포인트인터커넥트입니다2003년경부터 Advanced Micro Devices(AMD)에서 사용되고 있는 HyperTransport와 경쟁하도록 설계되었습니다.[6][7]인텔은 MMDC(Massachusetts Microprocessor Design Center)에서 인텔이 Compaq와 HP로부터 인수하여 원래 Digital Equipment Corporation(DEC)[8]에서 온 알파 개발 그룹의 멤버들에 의해 QPI를 개발했습니다.그것의 개발은 [9]2004년에 이미 보고되었다.

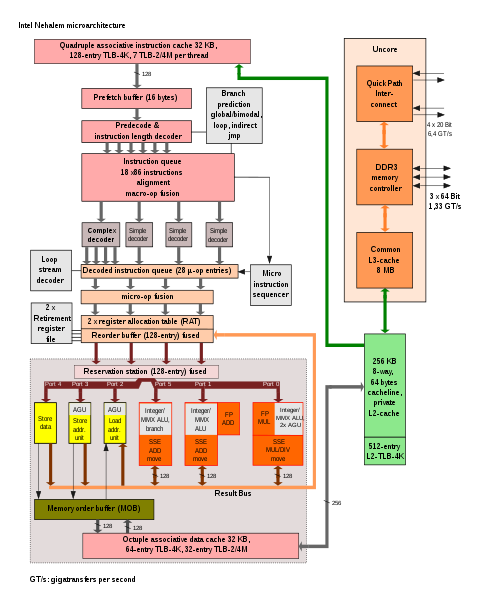

인텔은 2008년 11월에 인텔 Core i7-9xx 및 X58 칩셋으로 데스크톱 프로세서용으로 처음 제공하였습니다.2009년 3월에 Nehalem이라는 코드명 Xeon 프로세서와 2010년 2월에 Itanium 프로세서(코드명 Tukwila)[10]로 출시되었습니다.

2017년부터 Xeon Skylake-SP 플랫폼에서 인텔 Ultra Path Interconnect로 대체되었습니다.[11]

실행

QPI는 인텔이 QuickPath [12]테크놀로지를 구현하는 QuickPath 아키텍처라고 부르는 시스템 아키텍처의 요소입니다.싱글 프로세서 메인보드에서 가장 심플한 형태로 프로세서를 IO 허브에 접속하기 위해1개의 QPI를 사용합니다(예를 들어 인텔 Core i7을 X58에 접속하기 위해).아키텍처의 보다 복잡한 인스턴스에서는 다른 QPI 링크 쌍이 메인보드 상의 네트워크 내의 1개 이상의 프로세서와 1개 이상의 IO 허브 또는 라우팅 허브를 연결하여 모든 컴포넌트가 네트워크를 통해 다른 컴포넌트에 액세스할 수 있도록 합니다.HyperTransport와 마찬가지로 QuickPath 아키텍처는 프로세서가 메모리 컨트롤러를 내장하고 있는 것을 전제로 하고 NUMA(Non-Uniform Memory Access) 아키텍처를 유효하게 합니다.

각 QPI는 2개의 20레인 포인트 투 포인트 데이터 링크(각 방향(전이중)에 1개씩 포함)와 각 방향으로 별도의 클럭쌍을 사용하여 총 42개의 신호를 전송합니다.각 신호는 차동 쌍이므로 총 핀 수는 84개입니다.20개 데이터 레인은 각각 5개 레인의 4개 "사분원"으로 나뉩니다.전송의 기본 단위는 80비트 플릿으로 오류 검출용 8비트, "링크 레이어 헤더"용 8비트, 데이터용 64비트가 있습니다.1개의 80비트 플릿은 2개의 클럭사이클로 전송됩니다(20비트 전송은 4개, 클럭틱마다 2개).QPI 대역폭은 각 [8]방향의 2 클럭사이클마다 64비트(8바이트)의 데이터 전송을 계산함으로써 애드버타이즈 됩니다.

초기 실장에서는 단일 4 사분원링크를 사용하지만 QPI 사양에서는 다른 실장을 허용합니다.각 사분면은 독립적으로 사용할 수 있습니다.신뢰성이 높은 서버에서는 QPI 링크가 성능 저하 모드로 동작할 수 있습니다.20+1 신호 중 하나 이상이 실패하면 인터페이스는 [8]10+1 또는 5+1 남은 신호를 사용하여 작동하며 클럭이 실패하면 클럭을 데이터 신호에 재할당합니다.초기 Nehalem 실장에서는 풀4 사분원 인터페이스를 사용하여 25.6 GB/s를 실현했습니다.이는 X48 칩셋에 사용되는 인텔의 이론상 1600 MHz FSB의 2배의 대역폭을 제공합니다.

일부 하이엔드 Core i7 프로세서는 QPI를 공개하고 있지만 싱글 소켓 보드용 기타 "메인스트림" Nehalem 데스크톱 및 모바일 프로세서(LGA 1156 Core i3, Core i5, Lynfield/Clarksfield 및 후계 프로세서의 Core i7 프로세서 등)는 외부 프로세서에 QPI를 공개하지 않습니다.n 멀티패키지 시스템

단, QPI는 메모리 컨트롤러, CPU 측 PCI Express 및 GPU(존재하는 경우)를 포함한 칩의 일부인 "uncore"와 통신하기 위해 내부적으로 사용됩니다.예를 들어 Westmere 기반의 Clarkdale/[13][14][15][16]: 3 Alrand에서 Uncore는 CPU 코어와 동일한 다이 상에 있을 수도 있고 아닐 수도 있습니다.

Lynfield, Clarksfield, Clarkdale 및 Arrandale에서 시작된 2009년 이후의 싱글 소켓 칩에서는 기존의 Northbridge 기능이 이들 프로세서에 통합되어 있기 때문에 속도가 느린 DMI 및 PCI Express 인터페이스를 통해 외부로 통신합니다.

따라서 프로세서 [17]소켓을 통해 (이전) 프론트 사이드 버스 인터페이스를 노출하는 비용이 들지 않습니다.

코어/언코어 QPI 링크는 데스크톱 및 모바일 Sandy Bridge 프로세서에는 없지만(예를 들어 Clarkdale과 같이), 온다이 코어 간의 내부 링 인터커넥트도 적어도 캐시 일관성에 [16]: 10 관한 한 QPI의 이면에 있는 원칙에 기초하고 있습니다.

주파수 사양

동기회선으로서 QPI는 2.4GHz, 2.93GHz, 3.2GHz, 3.6GHz, 4.0GHz 또는 4.8GHz(3.6GHz 및 4.0GHz 주파수는 Sandy Bridge-E/EP 플랫폼에 도입되어 4.8GHz의 클럭환율로 동작합니다.특정 링크의 클럭환율은 링크 양 끝에 있는 컴포넌트의 기능과 프린트 회로 기판상의 신호 패스의 신호 특성에 따라 달라집니다.Non-Extreme Core i7 9xx 프로세서는 재고 참조 클럭에서 2.4GHz 주파수로 제한됩니다.

비트 전송은 클럭의 상승 에지 및 하강 에지 모두에서 발생하므로 전송 속도는 클럭환율의 2배가 됩니다.

인텔은 각 80비트 플릿에 64비트 데이터 페이로드만 카운트하여 데이터 스루풋(GB/s)을 기술합니다.단, 단방향 송수신 링크쌍을 동시에 활성화할 수 있기 때문에 인텔은 그 결과를 2배로 높입니다.따라서 인텔은 3.2GHz 클럭을 갖춘 20레인 QPI 링크 페어(송수신)의 데이터 레이트를 25.6GB/s로 기술하고 있습니다.클럭 레이트가 2.4GHz일 경우 데이터 레이트는 19.2GB/s입니다.보다 일반적으로 이 정의에 따르면 2링크 20레인 QPI는 클럭사이클당 8바이트(각 방향으로 4바이트)를 전송합니다.

환율은 다음과 같이 계산됩니다.

- 3.2GHz

- × 2비트/Hz (이중 데이터 레이트)

- × 16(20) (데이터 비트/Q)PI 링크 폭)

- × 2(단방향 송수신 동시 동작)

- 8 8 (비트/바이트)

- = 25.6 GB/s

프로토콜 계층

QPI는 물리층, 링크층,[1] 라우팅층, 트랜스포트층 및 프로토콜층이 다른 5계층 아키텍처로 지정됩니다.Core i7-9xx 및 Xeon DP 프로세서 등 포워딩 없이 포인트 투 포인트QPI만을 사용하는 디바이스에서는 트랜스포트 레이어는 존재하지 않고 라우팅 레이어는 최소입니다.

- 물리층

- 물리층은 실제 배선과 차동 송신기 및 수신기와 더불어 물리층 유닛을 송수신하는 최저 수준의 로직으로 구성됩니다.물리층 유닛은 20비트의 "피트"입니다.물리층에서는 20개 레인이 모두 사용 가능한 경우 20개 레인으로, 장애로 인해 QPI가 재구성된 경우 10개 또는 5개 레인으로 단일 클럭에지를 사용하여 20비트 "피트"를 전송합니다.데이터 신호와 더불어 클럭 신호는 송신기에서 수신기로 전송됩니다(이를 통해 핀을 추가해도 클럭 복구가 간소화됩니다).

- 링크 레이어

- 링크 레이어는 80비트 플릿 송수신을 담당합니다.각 플릿은 4개의 20비트 피트로 물리층으로 전송됩니다.각 플릿에는 링크층 송신기에 의해 생성된8비트 CRC와 72비트 페이로드가 포함됩니다.링크층 수신기가 CRC 에러를 검출하면, 수신기는 페어의 리턴 링크상의 플릿을 개입시켜 송신기에 통지하고, 송신기는 플릿을 재발송한다.링크 레이어는 수신자의 버퍼 오버플로를 방지하기 위해 신용/직불 방식을 사용하여 흐름 제어를 구현합니다.링크 레이어는 주로 캐시 일관성을 유지하기 위해 상위 레이어가 데이터 플릿과 비데이터 메시지를 구분할 수 있도록 6가지 다른 클래스의 메시지를 지원합니다.QuickPath 아키텍처의 복잡한 구현에서는 다른 클래스에 대해 개별 흐름과 흐름 제어를 유지하도록 링크 계층을 구성할 수 있습니다.싱글 프로세서 및 듀얼 프로세서의 실장에 이것이 필요한지, 또는 실장되는지는 불명확합니다.

- 라우팅 레이어

- 라우팅 레이어는 8비트헤더와 64비트payload로 구성된72비트 유닛을 전송합니다.헤더에는 수신처와 메시지유형이 포함됩니다.라우팅 레이어는 유닛을 수신하면 라우팅 테이블을 조사하여 유닛이 수신처에 도달했는지 여부를 판단합니다.이 경우 다음 상위 계층으로 전달됩니다.그렇지 않으면 올바른 발신 QPI로 전송됩니다.QPI가 1개뿐인 디바이스에서는 라우팅 레이어는 최소입니다.구현이 더 복잡한 경우 라우팅 레이어의 라우팅 테이블은 더 복잡하며 QPI 링크 장애를 피하기 위해 동적으로 변경됩니다.

- 트랜스포트 레이어

- 트랜스포트 레이어는 불필요하며 포인트 투 포인트 접속 전용 디바이스에는 존재하지 않습니다.여기에는 Core i7이 포함됩니다.트랜스포트 레이어는 직접 접속되어 있지 않을 가능성이 있는 다른 디바이스(즉, 데이터가 개입 디바이스를 경유해 라우팅 되었을 가능성이 있다) 상의 피어로부터 QPI 네트워크를 개입시켜 데이터를 송수신 합니다.전송 레이어는 데이터가 완전한 것을 확인하고, 그렇지 않은 경우는 피어로부터 재발송신을 요구합니다.

- 프로토콜 계층

- 프로토콜 계층은 장치 대신 패킷을 보내고 받습니다.일반적인 패킷은 메모리 캐시 행입니다.프로토콜 계층은 또한 관련 메시지를 보내고 수신함으로써 캐시 일관성의 유지에 참여합니다.

「 」를 참조해 주세요.

레퍼런스

- ^ a b "An Introduction to the Intel QuickPath Interconnect" (PDF). Intel Corporation. January 30, 2009. Retrieved June 14, 2011.

- ^ DailyTech 보고서 Archived 2013-10-17 at the Wayback Machine, 2007년 8월 21일 취득

- ^ Eva Glass (May 16, 2007). "Intel CSI name revealed: Slow, slow, quick quick slow". The Inquirer. Archived from the original on June 10, 2012. Retrieved September 13, 2013.

{{cite news}}: CS1 유지보수: 부적합한 URL(링크) - ^ David Kanter (2011-07-20). "Intel's Quick Path Evolved". Realworldtech.com. Retrieved 2014-01-21.

- ^ SoftPedia:인텔은 Xeon을 새로운 Skylake 기반의 "Purley" 슈퍼 플랫폼으로 대체할 계획이다.

- ^ Gabriel Torres (August 25, 2008). "Everything You Need to Know About The QuickPath Interconnect (QPI)". Hardware Secrets. Retrieved January 23, 2017.

- ^ Charlie Demerjian (December 13, 2005). "Intel Intel gets knickers in a twist over Tanglewood". The Inquirer. Archived from the original on September 3, 2010. Retrieved September 13, 2013.

{{cite news}}: CS1 유지보수: 부적합한 URL(링크) - ^ a b c David Kanter (August 28, 2007). "The Common System Interface: Intel's Future Interconnect". Real World Tech. Retrieved August 14, 2014.

- ^ Eva Glass (December 12, 2004). "Intel's Whitefield takes four core IA-32 shape". The Inquirer. Archived from the original on May 24, 2009. Retrieved September 13, 2013.

{{cite news}}: CS1 유지보수: 부적합한 URL(링크) - ^ David Kanter (May 5, 2006). "Intel's Tukwila Confirmed to be Quad Core". Real World Tech. Archived from the original on May 10, 2012. Retrieved September 13, 2013.

- ^ "Intel® Xeon® Processor Scalable Family Technical Overview".

- ^ "Intel Demonstrates Industry's First 32nm Chip and Next-Generation Nehalem Microprocessor Architecture". Archived from the original on 2008-01-02. Retrieved 2007-12-31.

- ^ Chris Angelini (2009-09-07). "QPI, Integrated Memory, PCI Express, And LGA 1156 - Intel Core i5 And Core i7: Intel's Mainstream Magnum Opus". Tomshardware.com. Retrieved 2014-01-21.

- ^ Published on 25th January 2010 by Richard Swinburne (2010-01-25). "Feature - Intel GMA HD Graphics Performance". bit-tech.net. Retrieved 2014-01-21.

- ^ "Intel Clarkdale 32nm CPU-and-GPU chip benchmarked (again) - CPU - Feature". HEXUS.net. 2009-09-25. Retrieved 2014-01-21.

- ^ a b Oded Lempel (2013-07-28). "2nd Generation Intel Core Processor Family: Intel Core i7, i5 and i3" (PDF). hotchips.org. Retrieved 2014-01-21.

- ^ Lily Loi, Stephan Jourdan, 인텔®차세대 마이크로아키텍처(Nehalem 및 Westmere)를 미드레인지로 전환, 2009년 8월 24일 핫칩스 21

외부 링크

- 인텔 QuickPath 인터커넥트 개요

- 인텔 QuickPath 인터커넥트 개요 (PDF)

- 인텔의 Nehalem CPU, Ars Technica, 2008년 4월 9일 Jon Stokes에 의해 필요한 정보

- Nehalem Microarchitecture : QPI Bus, 2008년 11월 2일 Ilya Gavrichenkov 기자

- 공통 시스템 인터페이스: Intel's Future Interconnect, 2007년 8월 28일, David Kanter에 의해