시온파이

Xeon Phi | |

| 일반 정보 | |

|---|---|

| 개시. | 2010 |

| 단종 | 2020년[1] |

| 성능 | |

| 최대 CPU 클럭 속도 | 1.053GHz~1.7GHz |

| 캐시 | |

| L1 캐시 | 코어당 32KB |

| L2 캐시 | 코어당 512KB |

| 아키텍처 및 분류 | |

| 테크놀로지 노드 | 22 nm 트랜지스터(트리게이트)~14 nm 트랜지스터(트리게이트) |

| 아키텍처 | x86-64 |

| 명령 집합 | x86-64 |

| 내선번호 | |

| 물리 사양 | |

| 코어 |

|

| 소켓 | |

| 모델 | |

| 역사 | |

| 후계자 | 시에라 포레스트 |

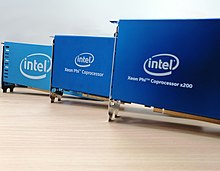

Xeon[2] Phi는 인텔이 설계 및 제조한 x86 manycore 프로세서 시리즈입니다.슈퍼컴퓨터, 서버 및 하이엔드 워크스테이션에서 사용하기 위한 것입니다.이 아키텍처는 OpenMP와 [3][4]같은 표준 프로그래밍 언어와 애플리케이션 프로그래밍 인터페이스(API)를 사용할 수 있게 했습니다.

Xeon Phi는 2010년에 출시되었습니다.2009년에 [6]취소된 인텔의 이전[5] GPU 설계(코드명 「래비」)에 근거하고 있었기 때문에, GPU와 애플리케이션 영역을 공유했습니다.Xeon Phi와 Nvidia Tesla와 같은 GPGPU의 주요 차이점은 Xeon Phi는 x86 호환 코어를 탑재하여 원래 표준 x86 CPU를 대상으로 한 소프트웨어를 적은 수정으로 실행할 수 있다는 것입니다.

처음에는 PCIe 기반 애드온 카드의 형태로 2013년 [7]6월에 코드네임 나이츠 랜딩이라는 2세대 제품이 발표되었습니다.이러한 2세대 칩은 단순한 애드인 카드가 아닌 독립형 CPU로 사용될 수 있습니다.

2013년 6월, 광저우의 국립 슈퍼 컴퓨터 센터(NSCC-GZ)의 Tianhe-2 슈퍼 컴퓨터가 세계에서 가장 빠른 슈퍼 컴퓨터(2018년 6월[update] 현재, 4위[9])로 발표되었습니다[8].인텔 Xeon Phi 코프로세서와 Ivy Bridge-EP Xeon 프로세서를 사용하여 33.86페타플롭스를 [10]달성했습니다.

Xeon Phi 제품 라인은 Nvidia의 Tesla 및 AMD Radeon Instent 제품 라인과 직접 경쟁했습니다.수요 부족과 인텔의 10nm [11]노드 문제로 단종됐다.

역사

| 코드명 | 테크놀로지 | 평. |

|---|---|---|

| 기사단 페리 | 45 nm | PCIe 카드로 제공, Larrabee 프로젝트에서 파생 |

| 나이트 코너 | 22 nm | P54C에서 파생된 벡터 처리 장치, Xeon Phi로 발표된 첫 번째 장치 |

| 나이트 랜딩 | 14 nm | Silvermont/Airmont (Intel Atom)[12]에서 파생, AVX-512 |

| 나이츠 밀 | 14 nm | 나이트 랜딩과 거의 동일하지만 딥 러닝에 최적화되어 있다 |

| 나이츠 힐 | 10 nm | 취소된 |

배경

Larrabee 마이크로아키텍처(2006년부터 개발[13])는 x86 아키텍처 기반의 프로세서 설계에 매우 넓은(512비트) SIMD 유닛을 도입하여 링 버스를 통해 메모리에 연결된 캐시 코히런트 멀티프로세서 시스템으로 확장하였습니다.각 코어는 4방향 멀티스레딩을 지원합니다.GPU 및 범용 컴퓨팅을 위한 설계이기 때문에 Larrabee 칩에는 텍스처 [14][15]샘플링을 위한 전용 하드웨어도 포함되어 있습니다.Larrabee 연구 프로젝트에서 직접 소매 GPU 제품을 생산하는 프로젝트는 2010년 [16]5월에 종료되었습니다.

현대의 또 다른 인텔 연구 프로젝트는 many-multicore 프로세서에서 x86아키텍처 구현은'Single-chip 클라우드 컴퓨터의(프로토 타입 2009[17]을 소개했다), 설계 시 여러 독립적인 중심부를 가지고는 하나의 칩에 클라우드 컴퓨팅 컴퓨터 datacentre를 모방함:프로토 타입 설계 칩당 하드웨어 지원과 함께 48코어 포함했다.위해서코어의 주파수와 전압을 선택적으로 제어하여 에너지 효율을 극대화하고 칩 간 메시징을 위한 메시 네트워크를 통합했습니다.이 설계에는 캐시 일관성이 결여되어 있으며, 설계를 더 많은 [18]코어로 확장할 수 있는 원리에 초점을 맞췄습니다.

Teraflops Research Chip (2007년 프로토타입 공개[19])는 x86 [20]아키텍처가 아닌 96비트 VLIW 아키텍처를 구현하는 코어당 2개의 부동소수점 유닛을 갖춘 실험용 80코어 칩입니다.이 프로젝트는 코어 간 통신 방법, 칩당 전력 관리를 조사하여 62 W의 [21][22]전력을 소비하는 3.16 GHz에서 1.01 TFLOPS를 달성했습니다.

기사단 페리

인텔의 많은 통합 코어(MIC) 시제품 보드(코드네임 오브리 섬)가 2010년 5월 31일에 발표되었습니다.이 제품은 Larrabee 프로젝트 및 싱글 칩 클라우드 [23][24]컴퓨터를 포함한 기타 인텔 연구의 파생 제품이라고 명시되어 있습니다.

이 개발 제품은 최대 1.2GHz의 32개의 순차 코어와 코어당 4개의 스레드, 2GB GDDR5 메모리 및 8MB의 일관성 있는 [25]L2 캐시(32KB L1 캐시가 있는 코어당 256KB)를 갖춘 PCIe 카드로 제공되었으며, 45nm [26]프로세스에서 구축된 최대 300W의 [25]전력 요건이 충족되었습니다.Oubrey Isl 코어에서는 1,024비트 링 버스(512비트 양방향)가 프로세서를 메인 [27]메모리에 연결합니다.싱글보드 퍼포먼스는 750GFLOPS를 [26]넘었습니다.프로토타입 보드는 단정도 부동소수점 [28]명령만 지원합니다.

초기 개발업체에는 CERN, 한국과학기술정보연구원(KISTI) 및 라이프니츠 슈퍼컴퓨팅 센터가 포함되었습니다.시제품 보드의 하드웨어 벤더에는 IBM, SGI, HP, 델 [29]등이 포함되어 있습니다.

나이트 코너

나이츠 코너 제품 라인은 22 nm 공정 크기로 제조되며 칩당 50개 이상의 코어를 가진 인텔의 Tri-gate 기술을 사용하여 인텔 최초의 다코어 상용 제품입니다.[23][26]

2011년 6월, SGI는 인텔과의 파트너십을 발표해, 하이 퍼포먼스 컴퓨팅 [30]제품에 MIC 아키텍처를 채용했습니다.2011년 9월, Texas Advanced Computing Center(TACC)는 10페타 FLOPS "Stampede" 슈퍼컴퓨터에 나이츠 코너 카드를 사용하여 8페타 FLOPS의 컴퓨팅 [31]파워를 제공한다고 발표했습니다.「Stampede: A Comprehensive Petascale Computing Environment」에 의하면, 「2세대 인텔(Knights Landing) MIC 가 발매되면 추가되어 Stampede의 합계 최고 퍼포먼스가 15 [32]PetaFLOPS 이상으로 향상합니다.

2011년 11월 15일, 인텔은 나이츠 코너 [33][34]프로세서의 초기 실리콘 버전을 공개했습니다.

2012년 6월 5일, 인텔은 나이츠 [35]코너에 관한 오픈 소스 소프트웨어와 문서를 발표했습니다.

2012년 6월 18일 인텔은 2012 Hamburg International Supercomputing Conference에서 Xeon Phi가 자사의 Many Integrated Core [2][36][37][38][39][40][41]아키텍처를 기반으로 모든 제품에 사용되는 브랜드명이 될 것이라고 발표했습니다.2012년 6월, Cray는 22 nm의 'Knight's Corner' 칩('Xeon Phi'라는 브랜드)을 'Cascade'[42][43] 시스템의 공동 프로세서로 제공할 것이라고 발표했습니다.

2012년 6월 ScaleMP는 Xeon Phi를 투과적인 프로세서 확장으로 사용할 수 있는 가상화 업데이트를 발표했습니다.이를 통해 레거시 MMX/SSE 코드를 코드 [44]변경 없이 실행할 수 있습니다.인텔 Xeon Phi 코어의 중요한 컴포넌트는 벡터 프로세싱 유닛(VPU)[45]입니다.VPU에는 새로운 512비트 SIMD 명령어 세트가 탑재되어 있습니다.이 명령어 세트는 공식적으로 인텔 초기 다수 코어 명령어(Intel IMCI)로 알려져 있습니다.따라서 VPU는 사이클당 16개의 Single Precision(SP; 단정도) 또는 8개의 Double Precision(DP; 배정도) 연산을 실행할 수 있습니다.VPU는 Fused Multi-Add(FMA) 명령도 지원하므로 사이클당 32개의 SP 또는 16DP 부동소수점 동작을 실행할 수 있습니다.또한 정수를 지원합니다.VPU에는 역수, 제곱근, 로그 등의 연산을 실행할 수 있는 Extended Math Unit(EMU; 확장 연산 유닛)도 탑재되어 있기 때문에 이러한 연산을 고대역폭으로 벡터 방식으로 실행할 수 있습니다.EMU는 이러한 함수의 다항식 근사치를 계산하여 작동합니다.

2012년 11월 12일, 인텔은 22 nm 프로세스 사이즈를 사용하는 Xeon Phi 코프로세서 패밀리 Xeon Phi 3100과 Xeon Phi 5110P를 [46][47][48]발표했습니다.Xeon Phi 3100은 300 [46][47][48]W에서 240 GB/s 메모리 대역폭으로 2 테라플롭스 이상의 배정도 부동소수점 명령을 지원할 수 있습니다.Xeon Phi 5110P는 225 [46][47][48]W에서 320 GB/s 메모리 대역폭을 가진 1.01 테라플롭스 배정도 부동소수점 명령을 지원합니다.Xeon Phi 7120P는 300 W에서 352 GB/s 메모리 대역폭으로 1.2 테라플롭스 배정도 부동소수점 명령을 사용할 수 있습니다.

2013년 6월 17일, Tianhe-2 슈퍼컴퓨터는 TOP500에 의해 세계에서[8] 가장 빠른 슈퍼컴퓨터로 발표되었습니다.Tianhe-2는 인텔 Ivy Bridge Xeon 및 Xeon Phi 프로세서를 사용하여 33.86페타플롭스를 달성했습니다.이는 2015년 11월에 마지막으로 2년 반 동안 가장 빠른 기록이었다.[49]

설계 및 프로그래밍

나이츠 코너의 코어는 오리지널 [50]Pentium에서 사용된 P54C 디자인의 수정 버전을 기반으로 합니다.인텔 MIC 아키텍처의 기본은 기존 병렬화 소프트웨어 [26]툴을 사용할 수 있는 x86 호환 멀티프로세서 아키텍처를 구축함으로써 x86 레거시를 활용하는 것입니다.프로그래밍 툴에는 OpenMP,[51] OpenCL,[52] Cilk/Cilk Plus 및 인텔의 Fortran,[54] C++[53] 및 수학 라이브러리의 특수 버전이 있습니다.

Larrabee 프로젝트에서 상속된 설계 요소에는 x86 ISA, 코어당 4-way SMT, 512비트 SIMD 유닛, 32KB L1 명령 캐시, 32KB L1 데이터 캐시, 일관성 있는 L2 캐시(코어당[55] 512KB), 프로세서 및 메모리 초광폭 링 버스 연결 등이 있습니다.

나이츠 코너 512비트 SIMD 명령어는 AVX-512 확장 기능과 많은 고유 기능을 공유합니다.명령어 세트의 설명서는 [56][57][58][59]KNC라는 확장명으로 인텔로부터 입수할 수 있습니다.

- Xeon Phi 모델

X100 시리즈

| 이름. | 시리얼 코드 | 코어 (4x 코어에서의 스레드) | 클럭(MHz) | L2 캐시 | GDDR5 ECC 메모리 | 피크 DP 컴퓨팅 (GFLOPS) | TDP (W) | 냉각 시스템. | 폼 팩터 | 방출된 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 기초 | 터보 | 양 | 채널 | BW GB/초 | |||||||||

| Xeon Phi 3110X[60] | SE3110X | 61 (244) | 1053 | - | 30.5 MB | 6 GB | 12 | 240 | 1028 | 300 | 베어보드 | PCIe 2.0 x16 카드 | 2012년 11월 |

| 8 GB | 16 | 320 | |||||||||||

| Xeon Phi 3120A[61] | SC3120A | 57 (228) | 1100 | - | 28.5 MB | 6 GB | 12 | 240 | 1003 | 300 | 팬/히트 싱크 | 2013년 6월 17일 | |

| Xeon Phi 3120P [62] | SC3120P | 57 (228) | 1100 | - | 28.5 MB | 6 GB | 12 | 240 | 1003 | 300 | 패시브 히트 싱크 | 2013년 6월 17일 | |

| Xeon Phi 31S1P[63] | BC31S1P | 57 (228) | 1100 | - | 28.5 MB | 8 GB | 16 | 320 | 1003 | 270 | 패시브 히트 싱크 | 2013년 6월 17일 | |

| Xeon Phi 5110P[64] | SC5110P | 060(240) | 1053 | - | 30.0 MB | 8 GB | 16 | 320 | 1011 | 225 | 패시브 히트 싱크 | 2012년 11월 12일 | |

| Xeon Phi 5120D[65] | SC5120D | 060(240) | 1053 | - | 30.0 MB | 8 GB | 16 | 352 | 1011 | 245 | 베어보드 | SFF 230 핀카드 | 2013년 6월 17일 |

| BC5120D | |||||||||||||

| Xeon Phi SE10P[66] | SE10P | 61 (244) | 1100 | - | 30.5 MB | 8 GB | 16 | 352 | 1074 | 300 | 패시브 히트 싱크 | PCIe 2.0 x16 카드 | 2012년 11월 12일 |

| Xeon Phi SE10X[67] | SE10X | 61 (244) | 1100 | - | 30.5 MB | 8 GB | 16 | 352 | 1074 | 300 | 베어보드 | 2012년 11월 12일 | |

| Xeon Phi 7110P[68] | SC7110P | 61 (244) | 1100 | 1250 | 30.5 MB | 16 GB | 16 | 352 | 1220 | 300 | 패시브 히트 싱크 | ??? | |

| Xeon Phi 7110X[69] | SC7110X | 61 (244) | 1250 | ??? | 30.5 MB | 16 GB | 16 | 352 | 1220 | 300 | 베어보드 | ??? | |

| Xeon Phi 7120A[70] | SC7120A | 61 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 300 | 팬/히트 싱크 | 2014년 4월 6일 | |

| Xeon Phi 7120D[71] | SC7120D | 61 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 270 | 베어보드 | SFF 230 핀카드 | 2014년 3월 ?일 |

| Xeon Phi 7120P[72] | SC7120P | 61 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 300 | 패시브 히트 싱크 | PCIe 2.0 x16 카드 | 2013년 6월 17일 |

| Xeon Phi 7120X[73] | SC7120X | 61 (244) | 1238 | 1333 | 30.5 MB | 16 GB | 16 | 352 | 1208 | 300 | 베어보드 | 2013년 6월 17일 | |

나이트 랜딩

인텔의 [32]2세대 MIC 아키텍처 제품의 코드명.인텔은 2013년 [10]6월 17일 2세대 인텔 Xeon Phi 제품의 세부사항을 공식적으로 발표했습니다.인텔은 차세대 인텔 MIC 아키텍처 기반의 제품이 코프로세서 또는 호스트 프로세서(CPU)로서 2가지 형태로 제공되며 인텔의 14 nm 프로세스 테크놀로지를 사용하여 제조될 것이라고 밝혔습니다.나이츠 랜딩 제품에는 내장 온패키지 메모리가 포함되어 있어 메모리 대역폭이 대폭 향상됩니다.

Knights Landing은 최대 72개의 Airmont(Atom) 코어와 [74][75]코어당 4개의 스레드를 탑재하여 최대 384GB의[76] "원거리" DDR4 2133 RAM 및 8~16GB의 "근처" 스택형 3D MCDRAM을 지원합니다.Hybrid Memory Cube 버전입니다.각 코어는 2개의 512비트 벡터 유닛을 갖추고 있으며 AVX-512 SIMD 명령, 특히 인텔 AVX-512 컨플릭트 검출 명령 (AVX-512 CD), 인텔 AVX-512 CD 및 상호 지수화를 지원합니다.IMCI 지원은 AVX-512를 위해 삭제되었습니다.[77]

국립에너지연구과학컴퓨팅센터는 자사의 최신 슈퍼컴퓨팅 시스템 "Cori"의 단계 2가 나이츠 랜딩 Xeon Phi [78]코프로세서를 사용할 것이라고 발표했다.

2016년 6월 20일 인텔은 나이츠 랜딩 아키텍처를 기반으로 한 인텔 Xeon Phi 제품 패밀리 x200을 출시하여 기존 시뮬레이션 워크로드뿐만 아니라 머신 [79][80]러닝에도 적용할 수 있음을 강조하였습니다.출시 당시 발표된 모델 라인업에는 부팅 가능한 폼 팩터의 Xeon Phi만 포함되어 있었습니다.단, 표준 프로세서와 내장 인텔 Omni-Path 아키텍처 [81]패브릭을 탑재한 프로세서입니다.후자는 모델 번호의 접미사 F로 표시됩니다.통합 패브릭은 개별 고성능 네트워크 [79]카드보다 낮은 비용으로 더 높은 지연 시간을 제공할 것으로 예상됩니다.

2016년 11월 14일, 48번째 TOP500 목록에는 나이트 랜딩 [citation needed]플랫폼을 사용하는 10개의 시스템이 포함되어 있습니다.

PCIe 기반의 Knight's Landing 보조 프로세서 변형은 일반 시장에 제공되지 않았으며 2017년 [82]8월에 단종되었습니다.여기에는 7220A, 7240P 및 7220P 코프로세서 카드가 포함되어 있습니다.

인텔은 2018년 [83]여름에 나이츠 랜딩을 중단한다고 발표했다.

- 모델

모든 모델은 코어 1~2개만 실행해도 기본 주파수에 200MHz를 추가하여 최고 속도로 가속할 수 있습니다.3개에서 최대 코어 수까지 동작하는 경우 칩은 기본 주파수보다 100MHz만 높일 수 있습니다.모든 칩은 200MHz [84]감소된 주파수로 고AVX 코드를 실행합니다.

| 시온파이 7200 시리즈 | 사양 번호 | 코어 (나사) | 클럭(MHz) | L2 캐시 | MCDRAM 메모리 | DDR4 메모리 | 피크 DP 컴퓨팅 | TDP (W) | 소켓 | 발매일 | 부품 번호 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 기초 | 터보 | 양 | BW | 용량. | BW | |||||||||

| Xeon Phi 7210[85] | SR2ME(B0) | 64 (256) | 1300 | 1500 | 32 MB | 16 GB | 400 GB 이상/초 | 384 GB | 102.4 GB/s | 2662 GPLOPS | 215 | SVLCLGA3647 | 2016년 6월 20일 | HJ8066702859300 |

| SR2X4(B0) | ||||||||||||||

| Xeon Phi 7210F[86] | SR2X5(B0) | 230 | HJ8066702975000 | |||||||||||

| Xeon Phi 7230[87] | SR2MF(B0) | 215 | HJ8066702859400 | |||||||||||

| SR2X3(B0) | ||||||||||||||

| Xeon Phi 7230F[88] | SR2X2(B0) | 230 | HJ8066702269002 | |||||||||||

| Xeon Phi 7250[89] | SR2MD(B0) | 68 (272) | 1400 | 1600 | 34 MB | 3046 GPLOPS[90] | 215 | HJ8066702859200 | ||||||

| SR2X1(B0) | ||||||||||||||

| Xeon Phi 7250F[91] | SR2X0(B0) | 230 | HJ8066702268900 | |||||||||||

| Xeon Phi 7290[92] | SR2WY(B0) | 72 (288) | 1500 | 1700 | 36 MB | 3456 GPLOPS | 245 | HJ8066702974700 | ||||||

| Xeon Phi 7290F[93] | SR2WZ(B0) | 260 | HJ8066702975200 | |||||||||||

나이츠 힐

나이츠 힐은 제3세대 MIC 아키텍처의 코드네임으로 인텔은 SC14에서 [94]첫 번째 세부사항을 발표했습니다.그것은 10 nm [95]공정으로 제조될 예정이었다.

나이츠 힐은 Argonne 국립 [96][97]연구소에 배치될 미국 에너지부의 Aurora 슈퍼컴퓨터에 사용될 것으로 예상되었습니다.그러나 Aurora는 기계 [98][99]학습에 초점을 맞춘 "고급 아키텍처"를 사용하는 것을 선호하여 지연되었습니다.

2017년 인텔은 Nights Hill이 미래의 Exascale 컴퓨팅을 가능하게 하기 위해 처음부터 구축된 또 다른 아키텍처를 위해 취소되었다고 발표했습니다.이 새로운 아키텍처는 2020-2021년에 [100][101]도입될 예정입니다.

나이츠 밀

나이츠 밀은 딥 러닝에 [102]특화된 Xeon Phi 제품의 인텔 코드네임으로 2017년 [103]12월에 처음 출시되었습니다.나이츠 밀은 나이츠 랜딩과 거의 동일한 사양으로 AVX-512 명령의 활용도를 높이기 위한 최적화 기능과 4방향 하이퍼스레딩을 지원합니다.단정도 부동소수점 및 가변정밀 부동소수점 성능은 2배 정밀도 부동소수점 성능을 희생하면서 향상되었습니다.

- 모델

| 시온파이 72x5 시리즈 | sSpec 번호 | 코어 (나사) | 클럭(MHz) | L2 캐시 | MCDRAM 메모리 | DDR4 메모리 | 피크 DP 컴퓨팅 | TDP (W) | 소켓 | 발매일 | 부품 번호 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 기초 | 터보 | 양 | BW | 용량. | BW | |||||||||

| Xeon Phi 7235 | SR3VF(A0) | 64 (256) | 1300 | 1400 | 32 MB | 16 GB | 400 GB 이상/초 | 384 GB | 102.4 GB/s | TBA | 250 | SVLCLGA3647 | 2017년 4분기 | HJ8068303823900 |

| Xeon Phi 7285 | SR3VE(A0) | 68 (272) | 1300 | 1400 | 34 MB | 115.2 GB/s | TBA | 250 | HJ8068303823800 | |||||

| Xeon Phi 7295 | SR3VD(A0) | 72 (288) | 1500 | 1600 | 36 MB | 115.2 GB/s | TBA | 320 | HJ8068303823700 | |||||

프로그래밍

Xeon Phi로 고성능을 달성하려면 여전히 프로그래머의 도움이 필요하며 기존 프로그래밍 모델의 컴파일러에만 의존하는 것은 여전히 현실과 동떨어진다고 저자들이 주장하는 성능 및 프로그래머빌리티 연구가 [104]연구자들에 의해 수행되었습니다.그러나 생명과학 [105]및 딥러닝과[106] 같은 다양한 분야의 연구는 Xeon Phi의 스레드와 SIMD 병렬성을 모두 활용하면 상당한 속도를 달성할 수 있다는 것을 보여주었다.

경쟁 제품

「 」를 참조해 주세요.

- Texas Advanced Computing Center – "Stampede" 슈퍼 컴퓨터에는 Xeon Phi [108]칩이 내장되어 있습니다.스탬피드는 10페타플롭스를 [108]사용할 수 있습니다.

- AVX-512

- 셀(마이크로프로세서)

- 인텔 테라 스케일

- 대규모 병렬화

- Xeon

레퍼런스

- ^ Ian Cutress & Anton Shilov (7 May 2019). "The Larrabee Chapter Closes: Intel's Final Xeon Phi Processors Now in EOL". Retrieved 12 March 2020.

- ^ a b Radek (18 June 2012). "Chip Shot: Intel Names the Technology to Revolutionize the Future of HPC - Intel Xeon Phi Product Family". Intel. Retrieved 12 December 2012.

- ^ robert-reed (4 February 2013). "Best Known Methods for Using OpenMP on Intel Many Integrated Core (Intel MIC) Architecture". software.intel.com.

- ^ Jeffers, James; Reinders, James (1 March 2013). Intel Xeon Phi Coprocessor High Performance Programming. Morgan Kaufmann. ISBN 978-0124104143.

- ^ Hruska, Joel (8 May 2019). "Intel Quietly Kills Off Xeon Phi". ExtremeTech.

- ^ "Intel scraps graphics chip based on Larrabee". Reuters. 6 December 2009.

- ^ Sodani, Avinash; et al. (2016). "Knights Landing: Second-Generation Intel Xeon Phi Product". IEEE Micro. 36 (2): 34–46. doi:10.1109/MM.2016.25. S2CID 28837176.

- ^ a b "TOP500 - June 2013". TOP500. Retrieved 18 June 2013.

- ^ "June 2018 TOP500 Supercomputer Sites". www.top500.org. Retrieved 22 July 2018.

- ^ a b "Intel Powers the World's Fastest Supercomputer, Reveals New and Future High Performance Computing Technologies". Retrieved 21 June 2013.

- ^ W1zzard (24 July 2018). "Intel is Giving up on Xeon Phi - Eight More Models Declared End-Of-Life". TechPowerUp.

- ^ Marc Sauter (20 June 2016). "Knights Landing: Intel veröffentlicht Xeon Phi mit bis zu 7 Teraflops - Golem.de". www.golem.de (in German).

- ^ Charlie Demerjian (3 July 2006), "New from Intel: It's Mini-Cores!", theinquirer.net, The Inquirer, archived from the original on 29 August 2009

{{citation}}: CS1 유지보수: 부적합한 URL(링크) - ^ Seiler, L.; Cavin, D.; Espasa, E.; Grochowski, T.; Juan, M.; Hanrahan, P.; Carmean, S.; Sprangle, A.; Forsyth, J.; Abrash, R.; Dubey, R.; Junkins, E.; Lake, T.; Sugerman, P. (August 2008). "Larrabee: A Many-Core x86 Architecture for Visual Computing" (PDF). ACM Transactions on Graphics. Proceedings of ACM SIGGRAPH 2008. 27 (3): 18:11. doi:10.1145/1360612.1360617. ISSN 0730-0301. S2CID 52799248. Retrieved 6 August 2008.

- ^ Tom Forsyth, SIMD Programming with Larrabee (PDF), Intel

- ^ Ryan Smith (25 May 2010), "Intel Kills Larrabee GPU, Will Not Bring a Discrete Graphics Product to Market\", www.anandtech.com, AnandTech

- ^ Tony Bradley (3 December 2009), "Intel 48-Core "Single-Chip Cloud Computer" Improves Power Efficiency", pcworld.com, PCWorld

- ^ "Intel Research : Single-Chip Cloud Computer", techresearch.intel.com, Intel

- ^ Ben Ames (11 February 2007), "Intel Tests Chip Design With 80-Core Processor", pcworld.com, IDG News

- ^ "Intel Details 80-Core Teraflops Research Chip - X-bit labs". xbitlabs.com. Archived from the original on 5 February 2015. Retrieved 27 August 2015.

- ^ "Intel's Teraflops Research Chip" (PDF), download.intel.com, Intel

- ^ Anton Shilov (12 February 2007), "Intel Details 80-Core Teraflops Research Chip", xbitlabs.com, Xbit laboratories, archived from the original on 5 February 2015

- ^ a b Rupert Goodwins (1 June 2010), "Intel unveils many-core Knights platform for HPC", zdnet.co.uk, ZDNet

- ^ "Intel News Release : Intel Unveils New Product Plans for High-Performance Computing", intel.com, Intel, 31 May 2010

- ^ a b Mike Giles (24 June 2010), "Runners and riders in GPU steeplechase" (PDF), people.maths.ox.ac.uk, pp. 8–10

- ^ a b c d Gareth Halfacree (20 June 2011), "Intel pushes for HPC space with Knights Corner", thinq.co.uk, Net Communities Limited, UK

- ^ "Intel Many Integrated Core Architecture" (PDF), many-core.group.cam.ac.uk, Intel, December 2010, archived from the original (PDF) on 2 April 2012

- ^ Rick Merritt (20 June 2011), "OEMs show systems with Intel MIC chips", EE Times

- ^ Tom R. Halfhill (18 July 2011), "Intel Shows MIC Progress", linleygroup.com, The Linley Group

- ^ Andrea Petrou (20 June 2011), "SGI wants Intel for super supercomputer", news.techeye.net, archived from the original on 16 September 2011

- ^ ""Stampede's" Comprehensive Capabilities to Bolster U.S. Open Science Computational Resources", tacc.utexas.edu, Texas Advanced Computing Center, 22 September 2011

- ^ a b "Stampede: A Comprehensive Petascale Computing Environment" (PDF). IEEE Cluster 2011 Special Topic. Archived from the original (PDF) on 26 September 2012. Retrieved 16 November 2011.

- ^ Yam, Marcus (16 November 2011), "Intel's Knights Corner: 50+ Core 22nm Co-processor", tomshardware.com, Tom's Hardware, retrieved 16 November 2011

- ^ Sylvie Barak (16 November 2011), "Intel unveils 1 TFLOP/s Knights Corner", EE Times, retrieved 16 November 2011

- ^ James Reinders (5 June 2012), Knights Corner: Open source software stack, Intel

- ^ Prickett Morgan, Timothy (18 June 2012), "Intel slaps Xeon Phi brand on MIC coprocessors", 222.theregister.co.uk

- ^ Intel Corporation (18 June 2012), "Latest Intel Xeon Processors E5 Product Family Achieves Fastest Adoption of New Technology on Top500 List", marketwatch.com, archived from the original on 20 June 2012, retrieved 18 June 2012,

Intel Xeon Phi is the new brand name for all future Intel Many Integrated Core Architecture based products targeted at HPC, enterprise, datacenters and workstations. The first Intel Xeon Phi product family member is scheduled for volume production by the end of 2012

- ^ Raj Hazra (18 June 2012). "Intel Xeon Phi coprocessors accelerate the pace of discovery and innovation". Intel. Retrieved 12 December 2012.

- ^ Rick Merritt (18 June 2012). "Cray will use Intel MIC, branded Xeon Phi". EETimes. Retrieved 12 December 2012.

- ^ Terrence O'Brien (18 June 2012). "Intel christens its 'Many Integrated Core' products Xeon Phi, eyes exascale milestone". Engadget. Retrieved 12 December 2012.

- ^ Jeffrey Burt (18 June 2012). "Intel Wraps Xeon Phi Branding Around MIC Coprocessors". eWeek. Retrieved 7 March 2022.

- ^ Merritt, Rick (8 June 2012), "Cray will use Intel MIC, branded Xeon Phi", eetimes.com

- ^ Latif, Lawrence (19 June 2012), "Cray to support Intel's Xeon Phi in Cascade clusters", theinquirer.net, archived from the original on 22 June 2012

{{citation}}: CS1 유지보수: 부적합한 URL(링크) - ^ "ScaleMP vSMP Foundation to Support Intel Xeon Phi", ScaleMP.com, ScaleMP, 20 June 2012

- ^ George Chrysos (12 November 2012). "Intel Xeon Phi X100 Family Coprocessor - the Architecture". software.intel.com.

- ^ a b c IntelPR (12 November 2012). "Intel Delivers New Architecture for Discovery with Intel Xeon Phi Coprocessors". Intel. Retrieved 12 December 2012.

- ^ a b c Agam Shah (12 November 2012). "Intel ships 60-core Xeon Phi processor". Computerworld. Retrieved 12 December 2012.

- ^ a b c Johan De Gelas (14 November 2012). "The Xeon Phi at work at TACC". AnandTech. Retrieved 12 December 2012.

- ^ "Tianhe-2 (MilkyWay-2)". Top500.org. 14 November 2015. Retrieved 6 May 2016.

- ^ Hruska, Joel (30 July 2012). "Intel's 50-core champion: In-depth on Xeon Phi". ExtremeTech. Ziff Davis, Inc. Retrieved 2 December 2012.

- ^ Barker, J; Bowden, J (2013). "Manycore Parallelism through OpenMP". OpenMP in the Era of Low Power Devices and Accelerators. IWOMP. Lecture Notes in Computer Science, vol 8122. Vol. 8122. Springer. pp. 45–57. doi:10.1007/978-3-642-40698-0_4. ISBN 978-3-642-40697-3.

- ^ Rick Merritt (20 June 2011), "OEMs show systems with Intel MIC chips", EE Times

- ^ Dokulil, Jiri; Bajrovic, Enes; Benkner, Siegfried; Pllana, Sabri; Sandrieser, Martin; Bachmayer, Beverly (23 November 2012), Efficient Hybrid Execution of C++ Applications using Intel Xeon Phi Coprocessor, arXiv:1211.5530, Bibcode:2012arXiv1211.5530D

- ^ "News Fact Sheet: Intel Many Integrated Core (Intel MIC) Architecture ISC'11 Demos and Performance Description" (PDF), newsroom.intel.com, Intel, 20 June 2011, archived from the original (PDF) on 24 March 2012

- ^ Tesla vs. Xeon Phi와 라데온. 컴파일러 라이터의 관점 // 포틀랜드 그룹(PGI), CUG 2013 프로시딩

- ^ "Intel Many Integrated Core Architecture (Intel MIC Architecture) - RESOURCES (including downloads)". Intel. Retrieved 6 January 2014.

- ^ "Intel Xeon Phi Coprocessor Instruction Set Architecture Reference Manual" (PDF). Intel. 7 September 2012. Retrieved 6 January 2014.

- ^ "Intel Developer Zone: Intel Xeon Phi Coprocessor". Intel. Retrieved 6 January 2014.

- ^ "Intel® Intrinsics Guide". software.intel.com. Retrieved 4 August 2020.

- ^ "Intel SE3110X Xeon Phi 3110X Knights Corner 6GB Coprocessor-No Cooling -SabrePC.com -SabrePC.com". www.sabrepc.com. Archived from the original on 22 February 2017. Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 3120A (6GB, 1.100 GHz, 57 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 3120P (6GB, 1.100 GHz, 57 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi 31S1P - BC31S1P". www.cpu-world.com. Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 5110P (8GB, 1.053 GHz, 60 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 5120D (8GB, 1.053 GHz, 60 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi SE10P". www.cpu-world.com. Retrieved 22 February 2017.

- ^ "Intel Xeon Phi SE10X". www.cpu-world.com. Retrieved 22 February 2017.

- ^ "Intel SC7110P Xeon Phi 7110P Knights Corner Coprocessor -SabrePC.com -SabrePC.com". www.sabrepc.com. Retrieved 22 February 2017.

- ^ "Intel SC7110X Xeon Phi 7110X Knights Corner Coprocessor -SabrePC.com -SabrePC.com". www.sabrepc.com. Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 7120A (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 7120D (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 7120P (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Coprocessor 7120X (16GB, 1.238 GHz, 61 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi 'Knights Landing' Features Integrated Memory With 500 GB/s Bandwidth and DDR4 Memory Support - Architecture Detailed". WCCFtech. 25 November 2013. Retrieved 27 August 2015.

- ^ Sebastian Anthony (26 November 2013), Intel unveils 72-core x86 Knights Landing CPU for exascale supercomputing, ExtremeTech

- ^ Tom's Hardware: 인텔 Xeon Phi Knights 랜딩 배송 중, Omni Path 업데이트도 2016년 6월 20일

- ^ James Reinders (23 July 2013), AVX-512 Instructions, Intel

- ^ "Cori". www.nersc.gov. Archived from the original on 17 May 2019. Retrieved 14 November 2018.

- ^ a b "2016 ISC High Performance: Intel's Rajeeb Hazra Delivers Keynote Address". Vimeo.

- ^ Pradeep Dubey (20 June 2016). "How Intel Xeon Phi Processors Benefit Machine Learning/Deep Learning Apps and Frameworks". software.intel.com.

- ^ 인텔 Xeon Phi 프로세서 소개– 보다 깊은 통찰력을 얻기 위한 길

- ^ Larabel, Michael (24 August 2017). "Intel Quietly Drops Xeon Phi 7200 Coprocessors". Phoronix. Retrieved 25 August 2017.

- ^ "Product Change Notification 116378 - 00" (PDF). Intel.com. Retrieved 25 July 2018.

- ^ "Intel Xeon Phi processor: Your Path to Deeper Insight" (PDF). Intel.com. Retrieved 25 February 2017.

- ^ "Intel Xeon Phi Processor 7210 (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processor 7210F (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processor 7230 (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processor 7230F (16GB, 1.30 GHz, 64 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processor 7250 (16GB, 1.40 GHz, 68 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processors". Intel. Retrieved 25 February 2017.

- ^ "Intel Xeon Phi Processor 7250F (16GB, 1.40 GHz, 68 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processor 7290 (16GB, 1.50 GHz, 72 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ "Intel Xeon Phi Processor 7290F (16GB, 1.50 GHz, 72 core) Product Specifications". Intel ARK (Product Specs). Retrieved 22 February 2017.

- ^ SC14: 2014년 슈퍼컴퓨팅, 2014년 하이 퍼포먼스 컴퓨팅, 네트워킹, 스토리지 및 분석 국제회의

- ^ Eric Gardner (25 November 2014), What public disclosures has Intel made about Knights Landing?, Intel Corporation

- ^ ALCF staff (9 April 2015), Introducing Aurora

- ^ ALCF staff (9 April 2015), Aurora

- ^ Hemsoth, Nicole (23 May 2017). "Some Surprises in the 2018 DoE Budget for Supercomputing". Next Platform. Retrieved 13 November 2017.

- ^ Brueckner, Rich (16 June 2017). "Is Aurora Morphing into an Exascale AI Supercomputer?". Inside HPC. Retrieved 13 November 2017.

- ^ Damkroger, Trish (13 November 2017). "Unleashing high performance computing today and tomorrow". Intel IT Peer Network.

- ^ Kampman, Jeff (13 November 2017). "Intel quietly kills off next-gen Knights Hill Xeon Phi chips". Tech Report. Retrieved 13 November 2017.

- ^ Smith, Ryan (17 August 2016). "Intel Announces Knight's Mill: A Xeon Phi for Deep Learning". Anandtech. Retrieved 17 August 2016.

- ^ Cutress, Ian (19 December 2017). "Intel Lists Knights Mill Xeon Phi on ARK: Up to 72 cores at 320W with QFMA and VNNI". Anandtech. Retrieved 19 December 2017.

- ^ Fang, Jianbin; Sips, Henk; Zhang, Lilun; Xu, Chuanfu; Yonggang, Che; Varbanescu, Ana Lucia (2014). Test-Driving Intel Xeon Phi (PDF). 2014 ACM/SPEC International Conference on Performance Engineering. Archived from the original (PDF) on 11 November 2017. Retrieved 30 December 2013.

- ^ Memeti, Suejb; Pllana, Sabri; Benkner, Siegfried; Pllana, Sabri; Sandrieser, Martin; Bachmayer, Beverly (29 June 2015), Accelerating DNA Sequence Analysis using Intel Xeon Phi, arXiv:1506.08612, Bibcode:2015arXiv150608612M

- ^ Viebke, Andre; Pllana, Sabri; Benkner, Siegfried; Pllana, Sabri; Sandrieser, Martin; Bachmayer, Beverly (30 June 2015), The Potential of the Intel Xeon Phi for Supervised Deep Learning, arXiv:1506.09067, Bibcode:2015arXiv150609067V

- ^ Jon Stokes (20 June 2011). "Intel takes wraps off 50-core supercomputing processor plans". Ars Technica.

- ^ a b Johan De Gelas (11 September 2012). "Intel's Xeon Phi in 10 Petaflops supercomputer". AnandTech. Retrieved 12 December 2012.

외부 링크

- 인텔 페이지:인텔 Xeon Phi 프로세서